## **Excellent Integrated System Limited**

Stocking Distributor

Click to view price, real time Inventory, Delivery & Lifecycle Information:

<u>Texas Instruments</u> <u>LM8333GGR8/NOPB</u>

For any questions, you can email us directly: sales@integrated-circuit.com

Datasheet of LM8333GGR8/NOPB - IC MOBILE I/O COMPANION 49-MIC

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

LM8333

www.ti.com

SNLS246K - SEPTEMBER 2006 - REVISED MAY 2013

# LM8333 Mobile I/O Companion Supporting Key-Scan, I/O Expansion, PWM, and ACCESS.bus Host Interface

Check for Samples: LM8333

#### **FEATURES**

- 8 x 8 Standard Keys

- 8 Special Function Keys (SF Keys) Providing a Total of 72 Keys for the Maximum Keyboard Matrix

- ACCESS.Bus (I<sup>2</sup>C-compatible) Communication Interface to the Host

- Four General Purpose Host Programmable I/O Pins with Two Optional (Slow) External Interrupts

- 15-byte FIFO Buffer to Store Key Pressed and Key Released Events

- Error Control with Error Reports on (FIFO Overrun, Keypad Overrun, Invalid Command)

- Host Programmable PWM

- Host Programmable Active Time and Debounce Time

#### **APPLICATIONS**

- Mobile Phones

- Personal Digital Assistants (PDAs)

- Smart Handheld Devices

- Personal Media Players

#### **DESCRIPTION**

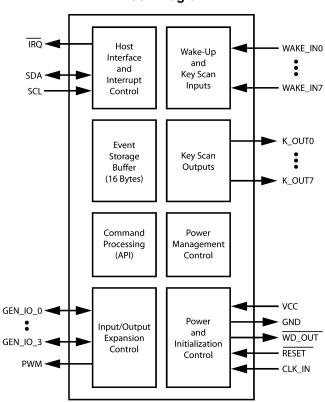

The LM8333 Mobile I/O Companion offloads the burden of keyboard scanning from the host, while providing extremely low power consumption in both operational and standby modes. It supports keypad matrices up to 8 × 8 in size (plus another 8 special-function keys), for portable applications such as cellphones, PDAs, games, and other handheld applications.

Key press and release events are encoded into a byte format and loaded into a FIFO buffer for retrieval by the host processor. An interrupt output (IRQ) is used to signal events such as keypad activity, a state change on either of two interrupt-capable general-purpose I/O pins, or an error condition. Interrupt and error codes are available to the host by reading dedicated registers.

Four general-purpose I/O pins are available, two of which have interrupt capability. A pulse-width modulated output based on a host-programmable internal timer is also available, which can be used as a general-purpose output if the PWM function is not required.

To minimize power, the LM8333 automatically enters a low-power standby mode when there is no keypad, I/O, or host activity.

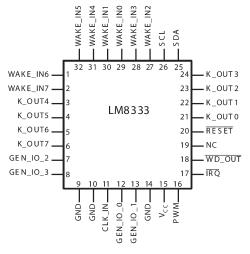

The device is packaged in a 32-pin WQFN and a 49-pin csBGA. Both are chip-scale packages.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

Datasheet of LM8333GGR8/NOPB - IC MOBILE I/O COMPANION 49-MIC Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

LM8333

SNLS246K - SEPTEMBER 2006-REVISED MAY 2013

www.ti.com

#### **Block Diagram**

#### **Pin Assignments**

Figure 1. 32-Lead WQFN (Top View) See Package Number NJE0032A

Submit Documentation Feedback

Copyright © 2006–2013, Texas Instruments Incorporated

www.ti.com

## Distributor of Texas Instruments: Excellent Integrated System Limited

Datasheet of LM8333GGR8/NOPB - IC MOBILE I/O COMPANION 49-MIC Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

LM8333

SNLS246K - SEPTEMBER 2006-REVISED MAY 2013

1 2 3 4 5 6 7 GND GEN\_IO\_3 K\_OUT7 K\_OUT6 K\_OUT4 WAKE\_IN6 WAKE\_IN5 Α CLK\_IN GND GEN\_IO\_2 K\_OUT5 WAKE\_IN7 WAKE\_IN4 NC В GND GND GND NC WAKE IN1 C GEN\_IO\_1 GEN\_IO\_0 GND GND GND WAKE\_IN3 WAKE\_IN0 D VCC VC C GND GND GND SCL WAKE IN2 Ε PWM **IRQ** RESET K OUT1 NC NC SDA K\_OUT2 K OUT3 WD OUT NC NC K OUT0 NC G

Figure 2. 49-Ball csBGA (Top View) See Package Number NYC0049A

Datasheet of LM8333GGR8/NOPB - IC MOBILE I/O COMPANION 49-MIC Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

## LM8333

SNLS246K - SEPTEMBER 2006-REVISED MAY 2013

www.ti.com

#### **SIGNAL DESCRIPTIONS**

| Name     | 32 Pins   | 49 Pins                                             | I/O    | Description                                                |

|----------|-----------|-----------------------------------------------------|--------|------------------------------------------------------------|

| WAKE_IN0 | 29        | D7                                                  | Input  | Wake-up input/Keyboard scanning input 0                    |

| WAKE_IN1 | 30        | C7                                                  | Input  | Wake-up input/Keyboard scanning input 1                    |

| WAKE_IN2 | 27        | E7                                                  | Input  | Wake-up input/Keyboard scanning input 2                    |

| WAKE IN3 | 28        | D6                                                  | Input  | Wake-up input/Keyboard scanning input 3                    |

| WAKE_IN4 | 31        | B6                                                  | Input  | Wake-up input/Keyboard scanning input 4                    |

| WAKE_IN4 | 32        | A7                                                  | Input  | Wake-up input/Keyboard scanning input 4                    |

| WAKE_INS | 1         | A6                                                  | Input  | Wake-up input/Keyboard scanning input 6                    |

| _        | 2         | _                                                   |        |                                                            |

| WAKE_IN7 |           | B5                                                  | Input  | Wake-up input/Keyboard scanning input 7                    |

| K_OUT0   | 21        | G3                                                  | Output | Keyboard scanning output 0                                 |

| K_OUT1   | 22        | F4                                                  | Output | Keyboard scanning output 1                                 |

| K_OUT2   | 23        | G4                                                  | Output | Keyboard scanning output 2                                 |

| K_OUT3   | 24        | G5                                                  | Output | Keyboard scanning output 3                                 |

| K_OUT4   | 3         | A5                                                  | Output | Keyboard scanning output 4                                 |

| K_OUT5   | 4         | B4                                                  | Output | Keyboard scanning output 5                                 |

| K_OUT6   | 5         | A4                                                  | Output | Keyboard scanning output 6                                 |

| K_OUT7   | 6         | A3                                                  | Output | Keyboard scanning output 7                                 |

| GEN_IO_0 | 12        | D2                                                  | I/O    | General-purpose I/O 0                                      |

| GEN_IO_1 | 13        | D1                                                  | I/O    | General-purpose I/O 1                                      |

| GEN_IO_2 | 7         | B3                                                  | I/O    | General-purpose I/O 2                                      |

| GEN_IO_3 | 8         | A2                                                  | I/O    | General-purpose I/O 3                                      |

| SDA      | 25        | F7                                                  | I/O    | ACCESS.bus data signal                                     |

| SCL      | 26        | E6                                                  | Input  | ACCESS.bus clock signal                                    |

| ĪRQ      | 17        | F2                                                  | Output | Interrupt request output                                   |

| PWM      | 16        | F1                                                  | Output | Pulse-width modulated output                               |

| WD_OUT   | 18        | G1                                                  | Output | Watchdog timer output (connect to RESET input)             |

| RESET    | 20        | F3                                                  | Input  | Reset input                                                |

| CLK_IN   | 11        | B1                                                  | Input  | Clock input (connect to ground through a 68k ohm resistor) |

| VCC      | 15        | E1, E2                                              | n.a.   | Vcc                                                        |

| GND      | 9, 10, 14 | A1, B2, C3,<br>C4, C5, D3,<br>D4, D5, E3,<br>E4, E5 | n.a.   | Ground                                                     |

| NC       | 19        | B7, C1, C2,<br>C6, F5, F6,<br>G2, G6, G7            | n.a.   | No connect                                                 |

Product Folder Links: LM8333

Submit Documentation Feedback

Copyright © 2006–2013, Texas Instruments Incorporated

Datasheet of LM8333GGR8/NOPB - IC MOBILE I/O COMPANION 49-MIC Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

LM8333

www.ti.com

SNLS246K - SEPTEMBER 2006-REVISED MAY 2013

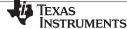

#### **Typical Application**

Figure 3. Typical Keypad Configuration

#### **FEATURES**

The following features are supported:

- 8 x 8 Standard Keys.

- 8 Special Function Keys (SF keys) with Wake-Up Capability by Forcing a WAKE\_INx Pin to Ground. Pressing a SF Key Overrides any other Key in the Same Row.

- · A Total of 72 Keys can be Scanned.

- ACCESS.Bus (I<sup>2</sup>C-Compatible) Interface for Communication with the Host.

- The Watchdog Timer is Mandatory, so WD\_OUT Must be Connected to RESET.

#### I/O EXPANSION OPTIONS

- One Host-Programmable PWM Output which also may be Used as a General-Purpose Output.

- Four Host-Programmable General-Purpose I/O Pins, GEN\_IO\_0, GEN\_IO\_1, GEN\_IO\_2, and GEN\_IO\_3. GEN\_IO\_0 and GEN\_IO\_1 can also be Configured for "Slow" Interrupts, in which any Transition will Trigger a Hardware Interrupt Event to the Host.

Product Folder Links: 1 M8333

Copyright © 2006-2013, Texas Instruments Incorporated

Submit Documentation Feedback

5

Datasheet of LM8333GGR8/NOPB - IC MOBILE I/O COMPANION 49-MIC Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

LM8333

SNLS246K - SEPTEMBER 2006-REVISED MAY 2013

www.ti.com

#### **WATCHDOG TIMER**

The watchdog timer is always enabled in hardware. To use the timer, connect the  $\overline{WD}$ \_OUT output to the RESET input.

#### **HALT MODE**

The fully static architecture of the LM8333 allows stopping the internal RC clock in Halt mode, which reduces power consumption to the minimum level.

Halt mode is entered when no key-press, key-release, or ACCESS.bus activity is detected for a certain period of time (by default, 500 milliseconds). The mechanism for entering Halt mode is always enabled in hardware, but the host can program the period of inactivity which triggers entry into Halt mode.

The LM8333 will remain in Active mode as long as a key event, or any other event, which causes the IRQ output to be asserted is not resolved.

#### **ACCESS.bus Activity**

When the LM8333 is in Halt mode, any activity on the ACCESS.bus interface will cause the LM8333 to exit from Halt mode. However, the LM8333 will not be able to acknowledge the first bus cycle immediately following wake-up from Halt mode. It will respond with a negative acknowledgement, and the host should then repeat the cycle.

The LM8333 will be prevented from entering Halt mode if it shares the bus with peripherals that are continuously active. For lowest power consumption, the LM8333 should only share the bus with peripherals that require little or no bus activity after system initialization.

#### **KEYPAD SCANNING**

The LM8333 starts new scanning cycles at fixed time intervals of about 4 ms. If a change in the state of the keypad is detected, the keypad is rescanned after a debounce delay. When the state change has been reliably captured, it is encoded and written to the FIFO buffer.

If more than two keys are pressed simultaneously, the pattern of key closures may be ambiguous, so pressing more than two keys asserts the Error Flag condition and the  $\overline{IRQ}$  output (if enabled). The host may attempt to interpret the events stored in the FIFO or discard them.

The SF keys connect the WAKE\_INx pins directly to ground. There can be up to eight SF-keys. If any of these keys are pressed, other key presses that use the same WAKE\_INx pin will be ignored.

#### **COMMUNICATION INTERFACE**

The two-wire ACCESS.bus interface is used to communicate with a host. The ACCESS.bus interface is fully compliant with the I<sup>2</sup>Cbus standard. The LM8333 operates as a bus slave at speeds up to 400 kHz.

An ACCESS.bus transfer starts with a byte that includes a 7-bit slave device address. The LM8333 responds to a fixed device address. This address is 0xA2, when aligned to the MSB (7-bit address mapped to bits 7:1, rather than bits 6:0). Bit 0 is a direction bit (0 on write, 1 on read).

Because it is a slave, the LM8333 never initiates an ACCESS.bus cycle, it only responds to bus cycles initiated by the host. The LM8333 may signal events to the host by asserting the IRQ interrupt request.

#### Interrupts Between the Host and LM8333

The IRQ output is used to signal unresolved interrupts, errors, and key-events to the host.

The host can use an available GEN\_IO\_0 or GEN\_IO\_1 pin to interrupt (or wake-up) the LM8333, if it is not being used for another function. The host can also wake-up the LM8333 by sending a Start Condition on the ACCESS.bus interface.

#### NOTE

The LM8333 it will not be able to acknowledge the first byte received from the host after wake-up. In this case, the host will have to resend the slave address.

Submit Documentation Feedback

Product Folder Links: I M8333

Datasheet of LM8333GGR8/NOPB - IC MOBILE I/O COMPANION 49-MIC Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

TEXAS INSTRUMENTS

LM8333

www.ti.com

SNLS246K - SEPTEMBER 2006-REVISED MAY 2013

### **Interrupt Sources**

The IRQ output is asserted on these conditions:

- · Any new key-event.

- Any error condition, which is indicated by the error code.

- Any enabled interrupt on either of the GEN\_IO\_0 or GEN\_IO\_1 pins that can be configured as external

interrupt inputs. When enabled, any rising or falling edge triggers an interrupt.

The IRQ output remains asserted until the interrupt code is read.

#### **Device Operation**

#### **EVENT CODE ASSIGNMENT**

After power-on reset, the LM8333 starts scanning the keypad. It stays active for a default time of about 500 ms after the last key is released, after which it enters a standby mode to minimize power consumption ( $<2 \mu A$  standby current).

Table 1 lists the codes assigned to the matrix positions encoded by the hardware. Key-press events are assigned the codes listed in Table 1, but with the MSB set. When a key is released, the MSB of the code is clear.

Table 1. Keypad Matrix Code Assignments

|          | K_OUT0 | K_OUT1 | K_OUT2 | K_OUT3 | K_OUT4 | K_OUT5 | K_OUT6 | K_OUT7 | SF Keys |

|----------|--------|--------|--------|--------|--------|--------|--------|--------|---------|

| WAKE_IN0 | 0x01   | 0x02   | 0x03   | 0x04   | 0x05   | 0x06   | 0x07   | 80x0   | 0x09    |

| WAKE_IN1 | 0x11   | 0x12   | 0x13   | 0x14   | 0x15   | 0x16   | 0x17   | 0x18   | 0x19    |

| WAKE_IN2 | 0x21   | 0x22   | 0x23   | 0x24   | 0x25   | 0x26   | 0x27   | 0x28   | 0x29    |

| WAKE_IN3 | 0x31   | 0x32   | 0x33   | 0x34   | 0x35   | 0x36   | 0x37   | 0x38   | 0x39    |

| WAKE_IN4 | 0x41   | 0x42   | 0x43   | 0x44   | 0x45   | 0x46   | 0x47   | 0x48   | 0x49    |

| WAKE_IN5 | 0x51   | 0x52   | 0x53   | 0x54   | 0x55   | 0x56   | 0x57   | 0x58   | 0x59    |

| WAKE_IN6 | 0x61   | 0x62   | 0x63   | 0x64   | 0x65   | 0x66   | 0x67   | 0x68   | 0x69    |

| WAKE_IN7 | 0x71   | 0x72   | 0x73   | 0x74   | 0x75   | 0x76   | 0x77   | 0x78   | 0x79    |

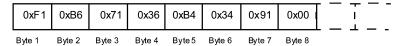

The codes are loaded into the FIFO buffer in the order in which they occurred. Table 2 shows an example sequence of events, and Figure 4 shows the resulting sequence of event codes loaded into the FIFO buffer.

**Table 2. Example Sequence of Events**

| Event Number | Event Code | Event on Input | Matrix Node | Description                    |

|--------------|------------|----------------|-------------|--------------------------------|

| 1            | 0xF1       | Wake_INP7      | K_OUT0      | Key is pressed                 |

| 2            | 0xB6       | Wake_INP3      | K_OUT5      | Key is pressed                 |

| 3            | 0x71       | Wake_INP7      | K_OUT0      | Key is released                |

| 4            | 0x36       | Wake_INP3      | K_OUT5      | Key is released                |

| 5            | 0xB4       | Wake_INP3      | K_OUT3      | Key is pressed                 |

| 6            | 0x34       | Wake_INP3      | K_OUT3      | Key is released33              |

| 7            | 0x91       | Wake_INP1      | K_OUT0      | Key is pressed                 |

| 8            | 0x00       | NA             | NA          | Indicates end of stored events |

#### FIFO Buffer

Figure 4. Example Event Codes Loaded in FIFO Buffer

#### I/O EXPANSION

In addition to keypad scanning, the LM8333 supports various I/O expansion options.

Product Folder Links: / M8333

Datasheet of LM8333GGR8/NOPB - IC MOBILE I/O COMPANION 49-MIC Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

LM8333

SNLS246K - SEPTEMBER 2006-REVISED MAY 2013

www.ti.com

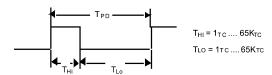

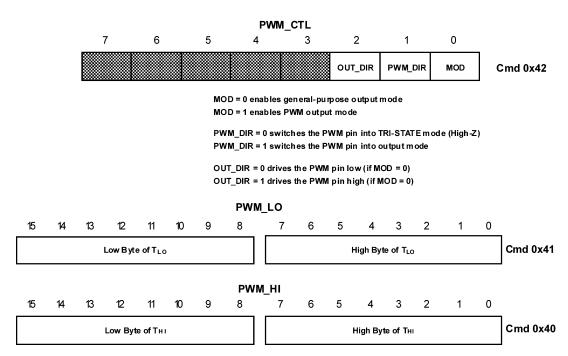

#### PWM Output with Programmable Duty Cycle

The PWM pin may be used either as a pulse-width modulated output driven by a 16-bit timer or as a general-purpose output pin. In the PWM mode, the low time ( $T_{LO}$ ) and high time ( $T_{HI}$ ) are programmable between 1 x t<sub>C</sub> and 65K x t<sub>C</sub> cycles in which t<sub>C</sub> is the cycle time (nominally 1 microsecond), as shown in Figure 5. The period  $T_{PD}$  is the sum of  $T_{HI}$  and  $T_{LO}$ . The PWM\_LO command writes  $T_{LO}$ , and the PWM\_HI command writes  $T_{HI}$ . Operational modes of the PWM pin are controlled by the PWM\_CTL command. Before activating the PWM output, the  $T_{LO}$  and  $T_{HI}$  times must be initialized. Figure 6 shows the command formats.

Figure 5. Programmable PWM

Figure 6. PWM Control Commands for Arbitrary Duty Cycle

**Table 3. Summary of PWM Control Bits**

| OUT_DIR Bit | PWM_DIR Bit | MOD BIT | Description       |

|-------------|-------------|---------|-------------------|

| 0           | 1           | 0       | Drive output low  |

| 1           | 1           | 0       | Drive output high |

| 0           | 0           | 0       | TRI-STATE® mode   |

| X           | X           | 1       | PWM timer output  |

#### General-Purpose I/O (GPIO)

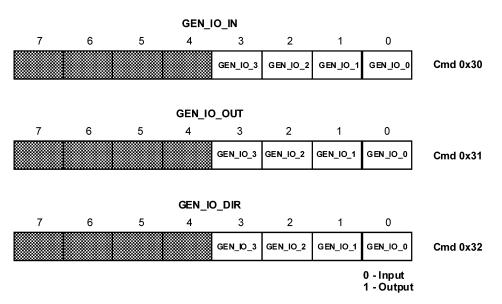

Figure 7 shows the commands to write, read and control the general-purpose I/O port pins, GEN\_IO\_0, GEN\_IO\_1, GEN\_IO\_2, and GEN\_IO\_3.

All general-purpose I/O pins can be programmed as inputs or outputs as shown in Table 4. The GEN\_IO\_0 and GEN\_IO\_1 pins provide an additional capability for programmable wake-up.

Product Folder Links: / M8333

Datasheet of LM8333GGR8/NOPB - IC MOBILE I/O COMPANION 49-MIC Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

LM8333

www.ti.com

SNLS246K - SEPTEMBER 2006-REVISED MAY 2013

Figure 7. General-Purpose I/O Control Commands

Table 4 shows the pin configuration for all four combinations of control bit settings (data output and direction) for the general-purpose I/O pins. GEN\_IO\_3 cannot be put into the high impedance (Hi-Z) input mode. When programmed as an input, it can only be configured as an input with a weak pullup.

Table 4. General Purpose I/O Pin Configuration

| GEN_IO_DIR Bit | GEN_IO_OUT Bit | Direction | State       |

|----------------|----------------|-----------|-------------|

| 0              | 0              | Input     | Hi-Z        |

| 0              | 1              | Input     | Weak Pullup |

| 1              | 0              | Output    | Drive Low   |

| 1              | 1              | Output    | Drive High  |

#### **External Interrupts**

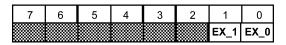

When the GEN\_IO\_0 or GEN\_IO\_1 pins are configured as inputs, a SET\_EXT\_INT command (0xD1) can be used to enable receiving external interrupts on either or both of these pins. Setting the EX\_0 or EX\_1 bits in the data byte of the SET\_EXT\_INT command (as shown in Figure 8) enables the corresponding pin as an external interrupt input. When enabled as an interrupt input, any rising or falling edge causes the IRQ output to be asserted. If the LM8333 was in Halt mode, it also wakes up into Active mode.

Figure 8. SET\_EXT\_INT Command Data Byte

When both GEN\_IO\_0 and GEN\_IO\_1 are configured as interrupt inputs, bits 1 and 2 of the interrupt code indicate which input asserted the interrupt. However, if only one of GEN\_IO\_0 or GEN\_IO\_1 is configured as an interrupt input, both bits 1 and 2 of the interrupt code will be set when an interrupt occurs.

Product Folder Links: LM8333

Datasheet of LM8333GGR8/NOPB - IC MOBILE I/O COMPANION 49-MIC Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

LM8333

SNLS246K - SEPTEMBER 2006-REVISED MAY 2013

www.ti.com

#### Table 5. Interface Commands for Controlling the LM8333

| Function      | Cmd  | Dir | Data Bits              | Data                     | Description                                                                                                                                                                                                                       |

|---------------|------|-----|------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |      |     |                        |                          | Read an event from the FIFO.                                                                                                                                                                                                      |

| EIEO DEAD     | 000  |     | 128                    | Event Codes from         | Maximum 14 event codes stored in the FIFO.                                                                                                                                                                                        |

| FIFO_READ     | 0x20 | R   |                        | FIFO                     | MSB = 1: key pressed.                                                                                                                                                                                                             |

|               |      |     |                        |                          | MSB = 0: key released.                                                                                                                                                                                                            |

|               |      |     |                        |                          | Repeats a FIFO read without advancing the FIFO pointer, for example to retry a read after an error.                                                                                                                               |

| RPT_FIFO_READ | 0x21 | R   | 128                    | Event Codes from<br>FIFO | Maximum 14 event codes stored in the FIFO.                                                                                                                                                                                        |

|               |      |     |                        | FIFO                     | MSB = 1: key pressed.                                                                                                                                                                                                             |

|               |      |     | MSB = 0: key released. |                          |                                                                                                                                                                                                                                   |

| DEBOUNCE      | 0x22 | W   | 8                      | 2222 2222                | Default is 10 ms. Valid range 1–255.                                                                                                                                                                                              |

| DEBOUNCE      | UXZZ | VV  | 0                      | nnnn nnnn                | Time ~ n x 3 ms                                                                                                                                                                                                                   |

| GEN_IO_IN     | 0x30 | R   | 8                      | 0000 nnnn                | Read port data.                                                                                                                                                                                                                   |

| GEN_IO_OUT    | 0x31 | W   | 8                      | 0000 nnnn                | Specify port mode. (Drive 0 or 1 when the port is configured as an output; select Hi-Z or pullup when the port is configured as an input.)                                                                                        |

| GEN_IO_DIR    | 0x32 | W   | 8                      | 0000 nnnn                | Select port direction (input or output).                                                                                                                                                                                          |

| PWM_HI        | 0x40 | W   | 16                     | $(n+1) \times t_C$       | Sets the low pulse time of the PWM signal.                                                                                                                                                                                        |

| PWM_LO        | 0x41 | W   | 16                     | $(n+1) \times t_C$       | Sets the high pulse time of the PWM signal.                                                                                                                                                                                       |

| PWM_CTL       | 0x42 | W   | 8                      | 0000 0nnn                | Activate, reactivate, or stop PWM.                                                                                                                                                                                                |

| READ_INT      | 0xD0 | R   | 8                      | 0000 nnnn                | Reads the interrupt code, acknowledges the interrupt, deasserts the IRQ output, and clears the code.                                                                                                                              |

| SET_EXT_INT   | 0xD1 | W   | 8                      | 0000 00nn                | Enables/disables external interrupts on GEN_IO_0 and GEN_IO_1.                                                                                                                                                                    |

| READ_STAT     | 0xE0 | R   | 8                      | 000n nnnn                | Status Information.                                                                                                                                                                                                               |

| SCAN_REQ      | 0xE3 | W   | 8                      |                          | Requests rescanning the keypad (for example, after an error was reported).                                                                                                                                                        |

| ACTIVE        | 0xE4 | W   | 8                      | nnnn nnnn                | Specifies the time after the last event during which the LM8333 stays active before entering Halt mode. The active time must be greater than the debounce time. Default is 500 msec Valid range for n is 1–255 Time ~ n x 3 msec. |

| READ_ERROR    | 0xF0 | R   | 8                      | Onnn nnnn                | Reads and clears the error code.                                                                                                                                                                                                  |

#### **HOST COMMAND EXECUTION**

#### **Command Structure**

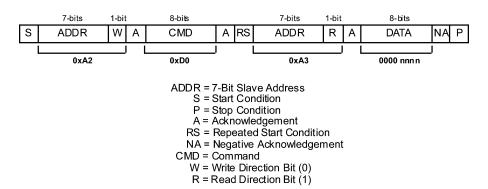

All communication with <u>the LM8333</u> over the ACCESS.bus interface is initiated by the host, usually in response to an interrupt request (IRQ low) asserted by the LM8333. Figure 9 shows a sequence of Start conditions, slave addresses, READ\_INT command (0xD0), acknowledge cycles, data bytes, and Stop condition for reading the interrupt code.

Submit Documentation Feedback

Copyright © 2006–2013, Texas Instruments Incorporated

Datasheet of LM8333GGR8/NOPB - IC MOBILE I/O COMPANION 49-MIC

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

LM8333

www.ti.com

SNLS246K - SEPTEMBER 2006-REVISED MAY 2013

Figure 9. Typical Command Sequence from Host

Every transfer is preceded by a Start condition (S) or a Repeated Start condition (RS). The latter occurs when a command follows immediately upon another command without an intervening Stop condition (P). A Stop condition indicates the end of transmission. Every byte is acknowledged (A) by the receiver.

The first byte in a write from the host to the LM8333 is 0xA2, and the first byte in a read is 0xA3. This byte is composed of a 7-bit slave address in bits 7:1 and a direction bit in bit 0. The direction bit is 0 on writes from the host to the slave and 1 on reads from the slave to the host.

The second byte sends the command. The commands are listed in Table 5. In the example, the READ\_INT command (0xD0) reads the interrupt code.

The slave address is repeated in the third byte, with the direction bit set to 1. The Start (or Repeated Start) condition must be repeated whenever the slave address or the direction bit is changed. In this case, the direction bit is changed.

The data is sent from the slave to the host in the fourth byte. When the master is the receiver, it sends a negative acknowledgement (NA) to indicate the end of the data.

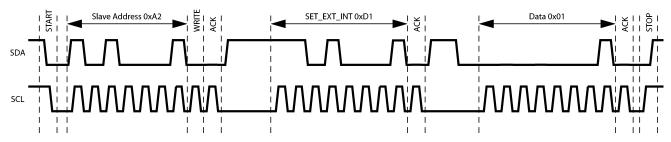

#### **HOST WRITE COMMANDS**

Some host commands include one or more data bytes written to the LM8333. Figure 10 shows a SET\_EXT\_INT command, which consists of an address byte, a command byte, and one data byte.

The first byte is composed of a 7-bit slave address in bits 7:1 and a direction bit in bit 0. The state of the direction bit is 0 on writes from the host to the slave and 1 on reads from the slave to the host.

The second byte sends the command. The commands are listed in Figure 11. The SET EXT INT command is 0xD1.

The third byte send the data, in this case configuring GEN IO 0 as an external interrupt input.

Figure 10. Host Write Command

#### **HOST READ COMMANDS**

NOTE: All NSIDs perform as described in this section. NSID LM8333GGR8AXS is an enhanced version which also allows the use of a STOP START sequence in addition to the REPEATED START sequence described in this section.

Product Folder Links: 1 M8333

Datasheet of LM8333GGR8/NOPB - IC MOBILE I/O COMPANION 49-MIC Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

LM8333

SNLS246K - SEPTEMBER 2006-REVISED MAY 2013

www.ti.com

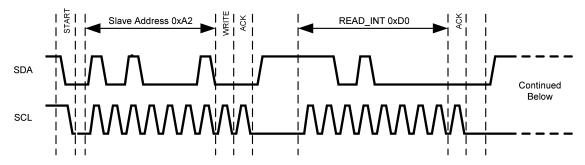

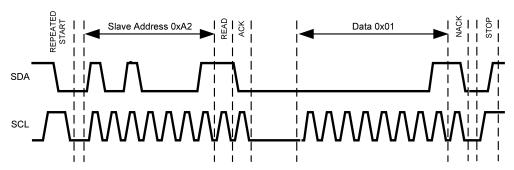

Some host commands include one or more data bytes read from the LM8333. Figure 11 shows a READ\_INT command which consists of an address byte, a command byte, a second address byte, and a data byte.

The first address byte is sent with the direction bit driven low to indicate a write transaction of the command to the LM8333. The second address byte is sent with the direction bit undriven (pulled high) to indicate a read transaction of the data from the LM8333.

The Repeated Start condition must be repeated whenever the slave address or the direction bit is changed. In this case, the direction bit is changed.

The data is sent from the slave to the host in the fourth byte. This byte ends with a negative acknowledgement (NACK) to indicate the end of the data.

Figure 11. Host Read Command

#### **WAKE-UP FROM HALT MODE**

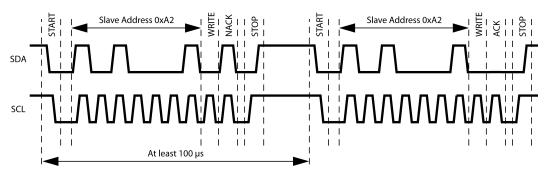

Any bus transaction initiated by the host may encounter the LM8333 device in Halt mode or busy with processing data, such as controlling the FIFO buffer or executing interrupt service routines.

Figure 12 shows the case in which the host sends a command while the LM8333 is in Halt mode (CPU clock is stopped). Any activity on the ACCESS.bus wakes up the LM8333, but it cannot acknowledge the first bus cycle immediately after wake-up.

The host drives a Start condition followed by seven address bits and a R/W bit. The host then releases SDA for one clock period, so that it can be driven by the LM8333.

If the LM8333 does not drive SDA low during the high phase of the clock period immediately after the R/W bit, the bus cycle terminates without being acknowledged (shown as NACK in Figure 12). The host then aborts the transaction by sending a Stop condition. After aborting the bus cycle, the host may then retry the bus cycle. On the second attempt, the LM8333 will be able to acknowledge the slave address, because it will be in Active mode.

Alternatively, the I<sup>2</sup>C specification allows sending a START byte (00000001), which will not be acknowledged by any device. This byte can be used to wake up the LM8333 from Halt mode.

The LM8333 may also stall the bus transaction by pulling the SCL low, which is a valid behavior defined by the  $I^2C$  specification.

Submit Documentation Feedback

Copyright © 2006–2013, Texas Instruments Incorporated

Datasheet of LM8333GGR8/NOPB - IC MOBILE I/O COMPANION 49-MIC

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

LM8333

www.ti.com

SNLS246K - SEPTEMBER 2006-REVISED MAY 2013

Figure 12. LM8333 Responds with NACK, Host Retries Command

#### Interrupts

#### INTERRUPT CODE

The interrupt code is read and acknowledged with the READ\_INT command (0xD0). This command clears the code and deasserts the IRQ output. Table 6 shows the format of the interrupt code.

Note that when only one of the interrupt-capable pins GEN\_IO\_0 or GEN\_IO\_1 is configured as an interrupt input, bits 1 and 2 are both set when an interrupt occurs. When both GEN\_IO\_0 and GEN\_IO\_1 pins are configured as interrupt inputs, only one bit corresponding to the interrupt source is set when an interrupt occurs.

#### **Table 6. Interrupt Code**

| 7 | 6 | 5 | 4 | 3     | 2    | 1    | 0      |

|---|---|---|---|-------|------|------|--------|

| 0 | 0 | 0 | 0 | ERROR | EX_1 | EX_0 | KEYPAD |

| Bit    | Description                                        |

|--------|----------------------------------------------------|

| ERROR  | An error condition occurred.                       |

| EX_1   | A rising or falling edge was detected on GEN_IO_1. |

| EX_0   | A rising or falling edge was detected on GEN_IO_0. |

| KEYPAD | A key-press or key-release event occurred.         |

#### **ERROR CODE**

If the LM8333 reports an error, the READ\_ERROR command (0xF0) is used to read and clear the error code. Table 7 shows the format of the error code.

#### Table 7. Error Code

| 7 | 6       | 5 | 4     | 3 | 2      | 1      | 0      |

|---|---------|---|-------|---|--------|--------|--------|

| 0 | FIFOOVR | 0 | NOINT | 0 | KEYOVR | CMDUNK | CMDOVR |

| Bit     | Description                                                       |

|---------|-------------------------------------------------------------------|

| FIFOOVR | Key event occurred while the FIFO was full.                       |

| NOINT   | Interrupt deasserted before it could be serviced.                 |

| KEYOVR  | More than two keys were pressed simultaneously.                   |

| CMDUNK  | Not a valid command.                                              |

| CMDOVR  | Command received before it could be accepted, e.g. after wake-up. |

Product Folder Links: 1 M8333

Copyright © 2006-2013, Texas Instruments Incorporated

Datasheet of LM8333GGR8/NOPB - IC MOBILE I/O COMPANION 49-MIC Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

LM8333

SNLS246K - SEPTEMBER 2006-REVISED MAY 2013

www.ti.com

#### STATUS CODES

The host can use the READ\_STAT command (0xE0) to read the status code, for example to synchronize after an error.

**Table 8. Status Codes**

| Status            | Code      | Description                           |

|-------------------|-----------|---------------------------------------|

| Reset             | 0000 0000 | Default after reset.                  |

| Wake Up Interrupt | 0000 0010 | Wake-up caused by external interrupt. |

| Ack               | 0000 0110 | Last host command was successful.     |

| NoAck             | 0001 0101 | Last host command was not successful. |

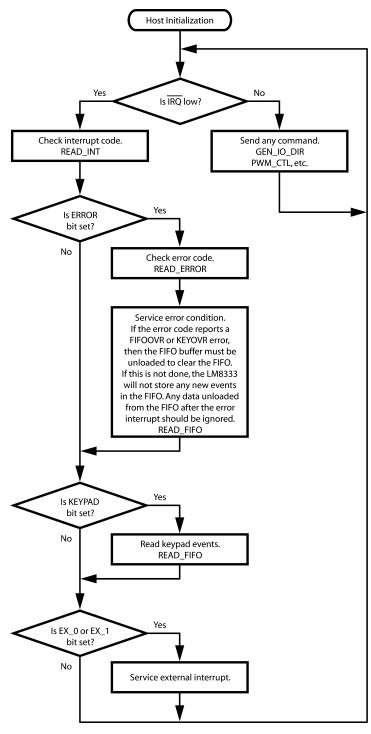

#### INTERRUPT PROCESSING

Unexpected states encountered during run-time, for example overrun of the FIFO buffer, are reported as errors. When the host receives an interrupt from the LM8333, it uses a READ\_INT command to read the interrupt code. If the code has a set ERROR bit, the host then uses a READ\_ERROR command to read the error code, as shown in Figure 13.

Product Folder Links: LM8333

Submit Documentation Feedback

Copyright © 2006–2013, Texas Instruments Incorporated

LM8333

www.ti.com

SNLS246K - SEPTEMBER 2006-REVISED MAY 2013

Figure 13. Interrupt Processing

Datasheet of LM8333GGR8/NOPB - IC MOBILE I/O COMPANION 49-MIC

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

#### LM8333

SNLS246K - SEPTEMBER 2006-REVISED MAY 2013

www.ti.com

#### **COMMAND EXECUTION SUMMARY**

- With the interrupt, status, and error codes, the LM8333 provides the features needed to support a reliable key-scan functionality.

- Up to 14 key-scan events can be stored in an internal FIFO buffer. The end of buffer is indicated with the 00 (empty character) code.

- The host can repeatedly read the FIFO without modifying the FIFO pointer using the RPT\_FIFO\_READ command (0x21), for example if an error is encountered during a read.

- The LM8333 asserts the IRQ output low when a new character is pressed after the last interrupt acknowledge

from the host. The IRQ output will be deasserted after the host has acknowledged the interrupt by reading the

interrupt code using the READ\_INT command (0xD0).

- The host can synchronize with the LM8333 by reading the status code with the READ\_STAT command (0xE0). The status code verifies whether the last command was successfully completed.

- Two GPIO pins on the LM8333 may be configured as external interrupt inputs. A rising or falling edge on an

enabled interrupt input triggers wake-up from Halt mode and asserts an interrupt to the host by pulling the

IRQ output low.

- The host can change the debounce time from the default time of 10 ms. This can be used for reliable scanning of keyboards with noisy contacts. The debounce time can be set to about 1 second in steps of 4 milliseconds. The debounce time is set with the DEBOUNCE command (0x22).

- The host can change the active time permitted before entering Halt mode from the default period of 500 ms. The active time is the time during which the keypad is scanned after the last key is released, before entering Halt mode. The active time must be longer than the debounce time.

- The host can program the direction and output state of four general-purpose I/O pins. The host can also read the states on these pins.

- The host can program a 16-bit timer for generating a PWM output. If the PWM function is not used, the PWM pin can be used as a general-purpose output.

Product Folder Links: / M8333

Datasheet of LM8333GGR8/NOPB - IC MOBILE I/O COMPANION 49-MIC Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

LM8333

SNLS246K - SEPTEMBER 2006-REVISED MAY 2013

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### **ABSOLUTE MAXIMUM RATINGS (1)(2)**

| Supply Voltage (V <sub>CC</sub> )     | 3.5V               |

|---------------------------------------|--------------------|

| Voltage at Any Pin                    | -0.3V to VCC +0.3V |

| Maximum Input Current Without Latchup | ±100 mA            |

| ESD Protection Level                  | •                  |

| Human Body Model                      | 2 kV               |

| Machine Model                         | 200V               |

| Total Current into VCC Pin (Source)   | 80 mA              |

| Total Current out of GND Pin (Sink)   | 60 mA              |

| Storage Temperature Range             | -65°C to +140°C    |

- Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not specified. For specifications and test conditions, see the Electrical Characteristics tables

- If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

#### DC ELECTRICAL CHARACTERISTICS

(Temperature:  $-40^{\circ}C \le TA \le +85^{\circ}C$ )

Data sheet specification limits are specified by design, test, or statistical analysis.

| Symbol            | Parameter                                 | Conditions                                                              | Min <sup>(1)</sup>  | Тур | Max (1)              | Units |

|-------------------|-------------------------------------------|-------------------------------------------------------------------------|---------------------|-----|----------------------|-------|

| V <sub>CC</sub>   | Operating Voltage                         |                                                                         | 2.25                |     | 2.9                  | V     |

|                   | Power Supply Rise Time from 0.0V          |                                                                         | 20 µs               |     | 10 ms                |       |

|                   | (On Chip Power-On Reset Selected)         |                                                                         |                     |     |                      |       |

| I <sub>DD</sub>   | Supply Current (2)                        | RC Clock = 10 MHz,                                                      |                     |     | 6                    | mA    |

|                   |                                           | $V_{CC} = 2.75V$ , $T_{C} = 1 \mu s^{(3)}$                              |                     |     |                      |       |

| I <sub>HALT</sub> | Standby Mode Current <sup>(4)</sup>       | $V_{CC} = 2.75V$ , $T_{C} = 0 \mu s$ , $^{(3)}$ , $T_{A} = 25^{\circ}C$ |                     | <2  | 15                   | μA    |

| V <sub>IL</sub>   | Logical 0 Input Voltage                   |                                                                         |                     |     | 0.25 V <sub>CC</sub> | V     |

| V <sub>IH</sub>   | Logical 1 Input Voltage                   |                                                                         | 0.8 V <sub>CC</sub> |     |                      | V     |

|                   | Hi-Z Input Leakage (TRI-STATE Output)     | V <sub>CC</sub> = 2.75V                                                 | -0.1                |     | 0.1                  | μΑ    |

|                   | Input PullupCurrent                       | $V_{CC} = 2.75V, V_{IN} = 0V$                                           | -15                 |     | -120                 | μΑ    |

|                   | Port Input Hysteresis <sup>(5)</sup>      |                                                                         | 0.1                 |     |                      | V     |

|                   | Output Current Source (Weak Pull-Up)      | V <sub>CC</sub> = 2.25V, V <sub>OH</sub> = 1.7V                         | -10                 |     | -80                  | μΑ    |

|                   | Output Current Source (Push-Pull Mode)    | V <sub>CC</sub> = 2.25V, V <sub>OH</sub> = 1.7V                         | -10                 |     |                      | mA    |

|                   | Output CurrentSink (Push-Pull Mode)       | V <sub>CC</sub> = 2.25V, V <sub>OL</sub> = 0.4V                         | 10                  |     |                      | mA    |

|                   | Allowable Sink and Source Current per Pin |                                                                         |                     |     | 16                   | mA    |

| C <sub>PAD</sub>  | Input Capacitance                         |                                                                         |                     |     | 8.5                  | pF    |

- Data sheet minimum and maximum limits are specified by design, test, or statistical analysis.

- Supply current is measured with inputs connected to V<sub>CC</sub> and outputs driven low but not connected to a load. (2)

- $T_C$  = instruction cycle time (min.  $0.7~\mu s$ ). In Halt mode, the internal clock is switched off. Supply current in Halt mode is measured with inputs connected to  $V_{CC}$  and outputs driven low but not connected to a load.

- Specified by design, not tested.

Product Folder Links: 1 M8333

Datasheet of LM8333GGR8/NOPB - IC MOBILE I/O COMPANION 49-MIC Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

LM8333

SNLS246K - SEPTEMBER 2006-REVISED MAY 2013

www.ti.com

#### **AC ELECTRICAL CHARACTERISTICS**

(Temperature:  $-40^{\circ}C \le T_A \le +85^{\circ}C$ )

Data sheet specification limits are specified by design, test, or statistical analysis.

| Parameter                                                                       | Conditions                                                                                                                                                                                                                                   | Min <sup>(1)</sup> | Тур        | Max <sup>(1)</sup> | Units    |

|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------|--------------------|----------|

| Internal Oscillator<br>System Oscillator (mclk)                                 | External R from CLK_IN to GND $(R = 68 \text{ k}\Omega)$<br>$2.25\text{V} \le \text{V}_{\text{CC}} \le 2.75\text{V}$<br>External R from CLK_IN to GND $(R = 68 \text{ k}\Omega)$<br>$2.25\text{V} \le \text{V}_{\text{CC}} \le 2.75\text{V}$ |                    | 0.75<br>75 |                    | μs<br>ns |

| System Oscillator and Internal Frequency Variation                              | 2.25V ≤ V <sub>CC</sub> ≤ 2.75V                                                                                                                                                                                                              |                    |            | ±30                | %        |

| Input Pulse Width Low                                                           |                                                                                                                                                                                                                                              | 0.7                |            |                    | μs       |

| Input Pulse Width High                                                          |                                                                                                                                                                                                                                              | 0.7                |            |                    |          |

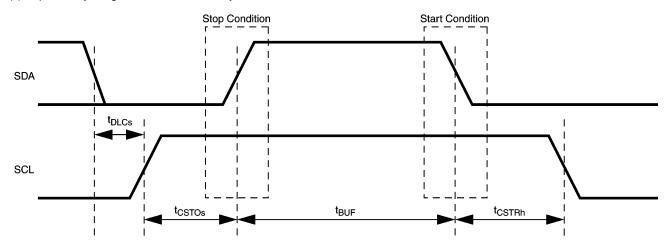

| ACCESS Bus Input Signals:                                                       |                                                                                                                                                                                                                                              |                    |            |                    |          |

| Bus Free time Between Stop and Start Condition $(I_{BUFI})^{(1)(2)}$            |                                                                                                                                                                                                                                              | 16                 |            |                    |          |

| SCL Setup Time (t <sub>CSTO</sub> si) (1)(2)                                    | Before Stop Condition                                                                                                                                                                                                                        | 8                  |            |                    |          |

| SCL Hold Time (t <sub>CSTR</sub> hi) (1)(2)                                     | After Stop Condition                                                                                                                                                                                                                         | 8                  |            |                    |          |

| SCL Setup Time (t <sub>CSTR</sub> si) (1)(2)                                    | Before Start Condition                                                                                                                                                                                                                       | 8                  |            |                    |          |

| Data High Setup Time (t <sub>DHCsi</sub> ) (1)(2)                               | Before SCL Rising Edge (RE)                                                                                                                                                                                                                  | 2                  |            |                    | mclk     |

| Data Low Setup Time (t <sub>DLCsi</sub> ) (1)(2)                                | Before SCL RE                                                                                                                                                                                                                                | 2                  |            |                    |          |

| SCL Low Time (t <sub>SCLlowi</sub> ) (1)                                        | After SCL Falling Edge (FE)                                                                                                                                                                                                                  | 12                 |            |                    |          |

| SCL High Time (t <sub>SCLhighi</sub> ) (1)(2)                                   | After SCL RE                                                                                                                                                                                                                                 | 12                 |            |                    |          |

| SDA Hold Time (t <sub>SDAhi</sub> ) <sup>(1)</sup>                              | After SCL FE                                                                                                                                                                                                                                 | 0                  |            |                    |          |

| SDA Setup Time (t <sub>SDAsi</sub> ) (1)(2)                                     | Before SCL RE                                                                                                                                                                                                                                | 2                  |            |                    |          |

| ACCESS Bus Output Signals<br>SDA Hold Time (t <sub>SDAho</sub> ) <sup>(3)</sup> | After SCL FE                                                                                                                                                                                                                                 | 7                  |            |                    | mclk     |

- Specified by design, test, or statistical analysis.

The ACCESS.bus interface implements and meets the timing necessary for interface to the I<sup>2</sup>C bus and SMBus protocol at logic levels. The bus drivers are designed with open-drain output as required for bidirectional operation. Due to System Oscillator (mclk) Variation, this specification may not meet the AC timing and current/voltage drive requirements of the full bus specification.

- Specified by design, test, or statistical analysis.

Note: In the timing tables the parameter name is appended with an "o" for output signal timing and "i" for input signal timing.

Figure 14. ACCESS.bus Start and Stop Condition Timing

Product Folder Links: LM8333

Datasheet of LM8333GGR8/NOPB - IC MOBILE I/O COMPANION 49-MIC Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

LM8333

|   | <b>,</b> | ۱A | ^   | ., | , | ŧi | i  | _ | o | n | n |  |

|---|----------|----|-----|----|---|----|----|---|---|---|---|--|

| ۰ | ν,       | ٧ı | , , | v  |   | u  | ٠. | u | v | ш | • |  |

SNLS246K - SEPTEMBER 2006-REVISED MAY 2013

#### **REVISION HISTORY**

| Changes from Revision J (May 2013) to Revision K |                                                    |      |  |  |  |  |  |

|--------------------------------------------------|----------------------------------------------------|------|--|--|--|--|--|

| •                                                | Changed layout of National Data Sheet to TI format | . 18 |  |  |  |  |  |

Product Folder Links: LM8333

Datasheet of LM8333GGR8/NOPB - IC MOBILE I/O COMPANION 49-MIC

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

PACKAGE OPTION ADDENDUM

8-Oct-2015

#### PACKAGING INFORMATION

| Orderable Device    | Status | Package Type |         | Pins | Package | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|---------------------|--------|--------------|---------|------|---------|----------------------------|------------------|---------------------|--------------|----------------|---------|

|                     | (1)    |              | Drawing |      | Qty     | (2)                        | (6)              | (3)                 |              | (4/5)          |         |

| LM8333FLQ8X/NOPB    | ACTIVE | WQFN         | NJE     | 32   | 2500    | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-3-260C-168 HR |              | LM8333F        | Samples |

| LM8333FLQ8Y/NOPB    | ACTIVE | WQFN         | NJE     | 32   | 250     | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-3-260C-168 HR |              | LM8333F        | Samples |

| LM8333GGR8/NOPB     | ACTIVE | csBGA        | NYC     | 49   | 1000    | Green (RoHS<br>& no Sb/Br) | CU SNAGCU        | Level-1-260C-UNLIM  | -40 to 85    | LM8333         | Samples |

| LM8333GGR8AXS/NOPB  | ACTIVE | csBGA        | NYC     | 49   | 1000    | Green (RoHS<br>& no Sb/Br) | CU SNAGCU        | Level-1-260C-UNLIM  |              | 8333AXS        | Samples |

| LM8333GGR8AXSX/NOPB | ACTIVE | csBGA        | NYC     | 49   | 3500    | Green (RoHS<br>& no Sb/Br) | CU SNAGCU        | Level-1-260C-UNLIM  |              | 8333AXS        | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available. **OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

Pb-Free/Green conversion plan has not been defined.

Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based filip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): Ti defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

(4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device

Addendum-Page 1

# **Distributor of Texas Instruments: Excellent Integrated System Limited**Datasheet of LM8333GGR8/NOPB - IC MOBILE I/O COMPANION 49-MIC

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

PACKAGE OPTION ADDENDUM

www.ti.com 8-Oct-2015

(6) Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information that way not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

Datasheet of LM8333GGR8/NOPB - IC MOBILE I/O COMPANION 49-MIC Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 2-Sep-2015

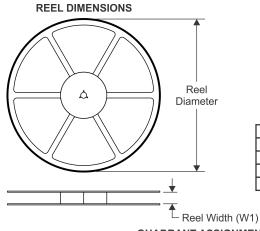

#### TAPE AND REEL INFORMATION

# TAPE DIMENSIONS + K0 + P1 + B0 W Cavity - A0 -

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

W Overall width of the carrier tape

P1 Pitch between successive cavity centers

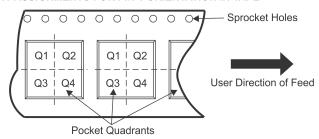

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device                  | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM8333FLQ8X/NOPB        | WQFN            | NJE                | 32 | 2500 | 330.0                    | 16.4                     | 6.3        | 6.3        | 1.5        | 12.0       | 16.0      | Q1               |

| LM8333FLQ8Y/NOPB        | WQFN            | NJE                | 32 | 250  | 178.0                    | 16.4                     | 6.3        | 6.3        | 1.5        | 12.0       | 16.0      | Q1               |

| LM8333GGR8/NOPB         | csBGA           | NYC                | 49 | 1000 | 178.0                    | 12.4                     | 4.3        | 4.3        | 1.5        | 8.0        | 12.0      | Q1               |

| LM8333GGR8AXS/NOPB      | csBGA           | NYC                | 49 | 1000 | 178.0                    | 12.4                     | 4.3        | 4.3        | 1.5        | 8.0        | 12.0      | Q1               |

| _M8333GGR8AXSX/NOP<br>B | csBGA           | NYC                | 49 | 3500 | 330.0                    | 12.4                     | 4.3        | 4.3        | 1.5        | 8.0        | 12.0      | Q1               |

Datasheet of LM8333GGR8/NOPB - IC MOBILE I/O COMPANION 49-MIC Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

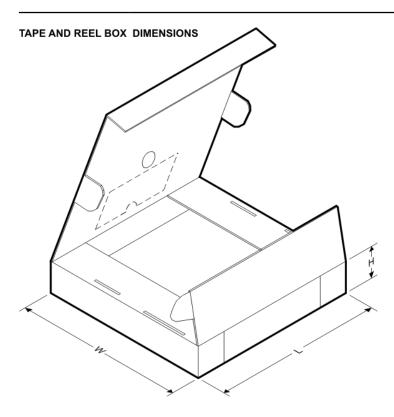

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 2-Sep-2015

#### \*All dimensions are nominal

| 7 III dilitoriolorio di o riorimidi |              |                 |      |      |             |            |             |  |  |  |  |

|-------------------------------------|--------------|-----------------|------|------|-------------|------------|-------------|--|--|--|--|

| Device                              | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |  |  |  |

| LM8333FLQ8X/NOPB                    | WQFN         | NJE             | 32   | 2500 | 367.0       | 367.0      | 38.0        |  |  |  |  |

| LM8333FLQ8Y/NOPB                    | WQFN         | NJE             | 32   | 250  | 213.0       | 191.0      | 55.0        |  |  |  |  |

| LM8333GGR8/NOPB                     | csBGA        | NYC             | 49   | 1000 | 210.0       | 185.0      | 35.0        |  |  |  |  |

| LM8333GGR8AXS/NOPB                  | csBGA        | NYC             | 49   | 1000 | 210.0       | 185.0      | 35.0        |  |  |  |  |

| LM8333GGR8AXSX/NOPB                 | csBGA        | NYC             | 49   | 3500 | 367.0       | 367.0      | 35.0        |  |  |  |  |

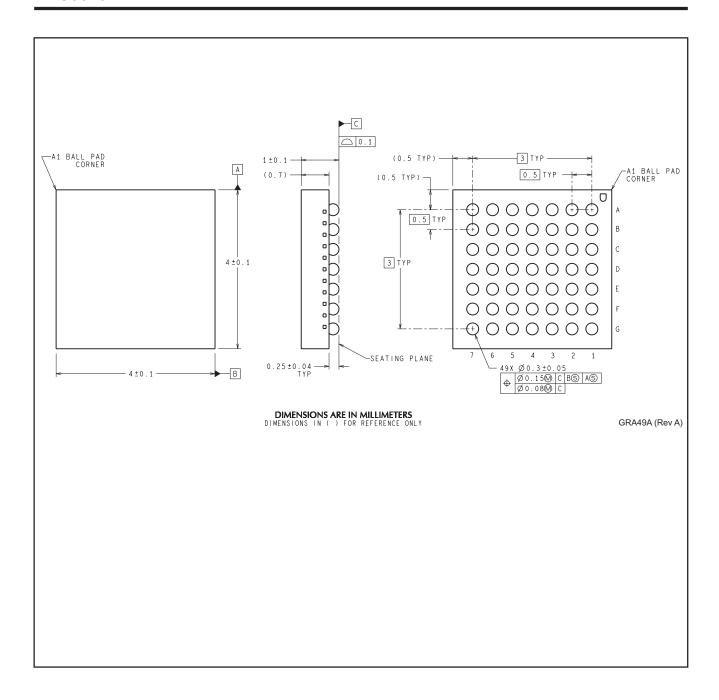

## **MECHANICAL DATA**

## NYC0049A

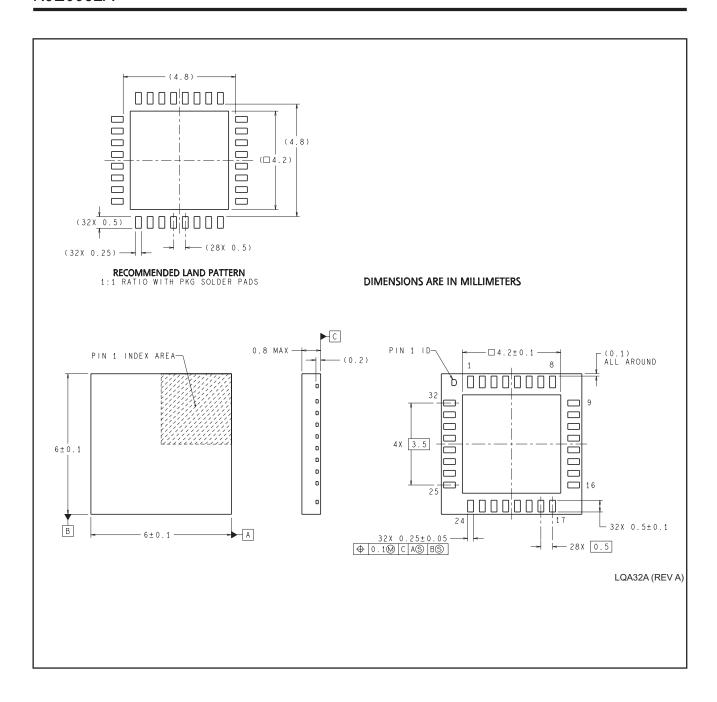

## **MECHANICAL DATA**

## **NJE0032A**

Datasheet of LM8333GGR8/NOPB - IC MOBILE I/O COMPANION 49-MIC

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have not been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

#### **Applications**

**Products** Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive **Amplifiers** amplifier.ti.com Communications and Telecom www.ti.com/communications Computers and Peripherals **Data Converters** dataconverter.ti.com www.ti.com/computers **DLP® Products** Consumer Electronics www.ti.com/consumer-apps www.dlp.com DSP dsp.ti.com **Energy and Lighting** www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Security www.ti.com/security

Power Mgmt Space, Avionics and Defense www.ti.com/space-avionics-defense power.ti.com

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

Logic

**OMAP Applications Processors TI E2E Community** www.ti.com/omap e2e.ti.com

www.ti.com/wirelessconnectivity Wireless Connectivity

> Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2015, Texas Instruments Incorporated