# **Excellent Integrated System Limited**

Stocking Distributor

Click to view price, real time Inventory, Delivery & Lifecycle Information:

Maxim Integrated MAX742EWP+

For any questions, you can email us directly: <u>sales@integrated-circuit.com</u>

**Distributor of Maxim Integrated: Excellent Integrated System Limited** Datasheet of MAX742EWP+ - IC REG CTRLR BST INV PWM 20-SOIC Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

19-3105; Rev 2; 8/96

# Switch-Mode Regulator with +5V to ±12V or ±15V Dual Output

#### \_General Description

The MAX742 DC-DC converter is a controller for dual-output power supplies in the 3W to 60W range. Relying on simple two-terminal inductors rather than transformers, the MAX742 regulates both outputs independently to within  $\pm 4\%$  over all conditions of line voltage, temperature, and load current.

The MAX742 has high efficiency (up to 92%) over a wide range of output loading. Two independent PWM currentmode feedback loops provide tight regulation and operation free from subharmonic noise. The MAX742 can operate at 100kHz or 200kHz, so it can be used with small and lightweight external components. Also ripple and noise are easy to filter. The MAX742 provides a regulated output for inputs ranging from 4.2V to 10V (and higher with additional components).

External power MOSFETs driven directly from the MAX742 are protected by cycle-by-cycle overcurrent sensing. The MAX742 also features undervoltage lockout, thermal shutdown, and programmable soft-start.

If 3W of load power or less is needed, refer to the MAX743 data sheet for a device with internal power MOSFETs.

#### Applications

DC-DC Converter Module Replacement Distributed Power Systems Computer Peripherals

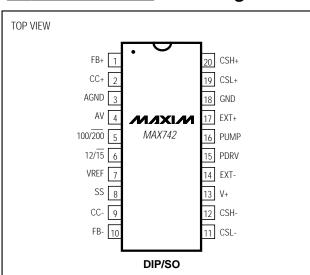

#### Pin Configuration

#### \_Features

- Specs Guaranteed for In-Circuit Performance

- Load Currents to ±2A

- 4.2V to 10V Input-Voltage Range

- Switches From ±15V to ±12V Under Logic Control

- ★ ±4% Output Tolerance Max Over Temp, Line, and Load

- 90% Typ Efficiency

- Low-Noise, Current-Mode Feedback

- Cycle-by-Cycle Current Limiting

- Undervoltage Lockout and Soft-Start

- 100kHz or 200kHz Operation

#### \_Ordering Information

| PART      | TEMP. RANGE     | PIN-PACKAGE    |

|-----------|-----------------|----------------|

| MAX742CPP | 0°C to +70°C    | 20 Plastic DIP |

| MAX742CWP | 0°C to +70°C    | 20 Wide SO     |

| MAX742C/D | 0°C to +70°C    | Dice*          |

| MAX742EPP | -40°C to +85°C  | 20 Plastic DIP |

| MAX742EWP | -40°C to +85°C  | 20 Wide SO     |

| MAX742MJP | -55°C to +125°C | 20 CERDIP      |

| *         |                 |                |

\* Contact factory for dice specifications

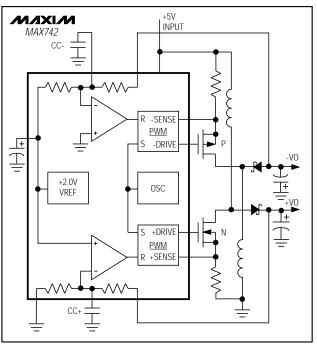

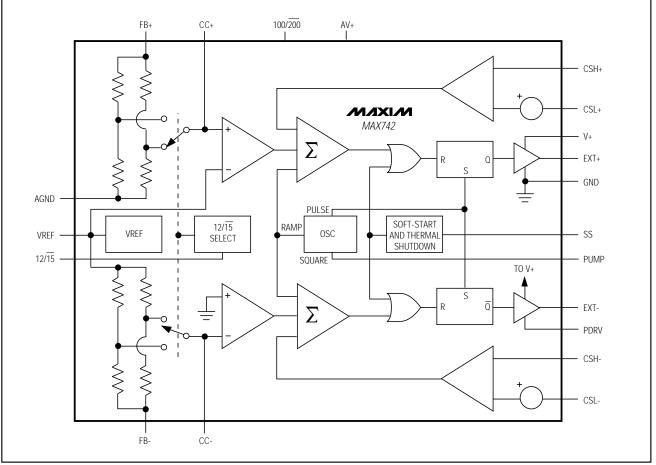

#### Simplified Block Diagram

#### M/IXI/M

\_ Maxim Integrated Products 1

For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800

**MAX742**

## Switch-Mode Regulator with +5V to ±12V or ±15V Dual Output

#### **ABSOLUTE MAXIMUM RATINGS**

| V+, AV+ to AGND, GND<br>PDRV to V+ |                     |

|------------------------------------|---------------------|

| FB+, FB- to GND                    |                     |

| Input Voltage to GND               |                     |

| (CC+, CC-, CSH+, CSL+, CSH-, CSL-, |                     |

| SS, 100/200, 12/15)                | 0.3V to (V+ + 0.3V) |

| Output Voltage to GND              |                     |

| (EXT+, PUMP)                       | 0.3V to (V+ + 0.3V) |

| EXT- to PDRV                       |                     |

Continuous Power Dissipation (any package)

| 0°C to +70°C   |

|----------------|

| 40°C to +85°C  |

| 55°C to +125°C |

| 65°C to +150°C |

| +300°C         |

|                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### ELECTRICAL CHARACTERISTICS

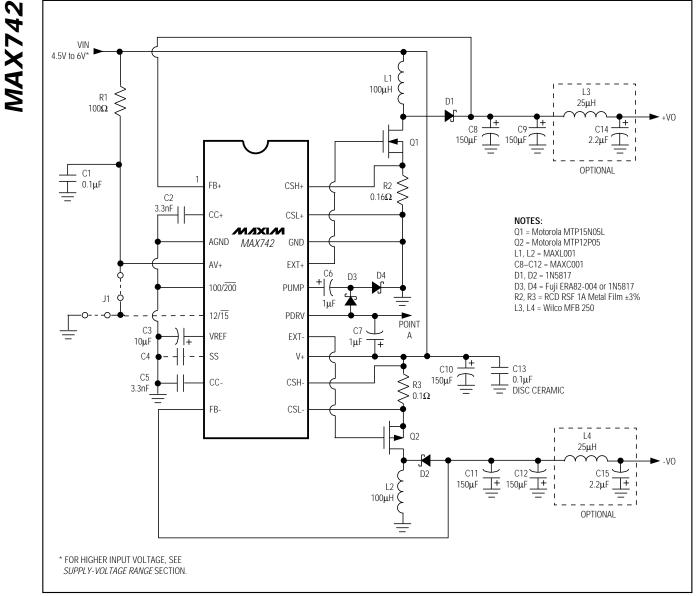

(Circuit of Figure 2, +4.5V < V + < +5.5V.)

| PARAMETER                 | SYMBOL | COND                          | ITIONS                       | MIN   | TYP | MAX   | UNITS |

|---------------------------|--------|-------------------------------|------------------------------|-------|-----|-------|-------|

| Output Voltage, ±15V Mode |        | 0mA < I <sub>L</sub> < 100mA, | $T_A = +25^{\circ}C$         | 14.55 |     | 15.45 | V     |

| (Notes 1, 2)              |        | 12/15 = 0V                    | $T_A = T_{MIN}$ to $T_{MAX}$ | 14.40 |     | 15.60 | v     |

| Output Voltage, ±12V Mode |        | 0mA < I <sub>L</sub> < 125mA, | $T_A = +25^{\circ}C$         | 11.64 |     | 12.36 | V     |

| (Notes 1, 2)              |        | $12/\overline{15} = V +$      | $T_A = T_{MIN}$ to $T_{MAX}$ | 11.52 |     | 12.48 | v     |

#### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 2, V+ = 5V,  $100/\overline{200} = 12/\overline{15} = 0V$ ; TA = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.)

| PARAMETER                                          | SYMBOL | CONDITIONS                         |           | MIN | TYP    | MAX  | UNITS |

|----------------------------------------------------|--------|------------------------------------|-----------|-----|--------|------|-------|

| Line Regulation                                    |        | V+ = 4.5V to 5.5V, PDRV from PUMP  |           |     | 0.01   | 0.05 | %/%   |

| Load Regulation (Note 2)                           |        | $I_{LOAD} = 0mA \text{ to } 100mA$ |           |     | 30     | 100  | mV    |

| No-Load Supply Current                             |        | No EXT- or PUMP load,              | V + = 5V  |     |        | 3    | mA    |

|                                                    |        | FB+ = FB- = open circuit           | V + = 10V |     |        | 10   |       |

| Undervoltage Lockout                               | UVLO   |                                    |           | 3.8 |        | 4.2  | V     |

| Undervoltage Lockout Hysteresis                    |        |                                    |           |     | 0.2    |      | V     |

| Reference Output Voltage                           |        |                                    |           |     | 2.0    |      | V     |

| Oscillator Frequency                               | face   | 100/200 = 0V                       |           | 170 | 200    | 230  | kHz   |

|                                                    | fosc   | $100/\overline{200} = V +$         |           | 75  | 100    | 125  |       |

| PUMP Frequency                                     |        |                                    |           |     | fosc/2 |      | kHz   |

| Duty-Cycle Limit (Note 3)                          |        | EXT+ or EXT-                       |           | 85  | 90     |      | %     |

| Positive Current-Limit Threshold<br>(CSH+ to CSL+) |        | CSL+ = 0V, FB+ = open circuit      |           | 150 | 225    | 300  | mV    |

| Negative Current-Limit Threshold<br>(CSH- to CSL-) |        | CSH- = V+, FB- = open circuit      |           | 150 | 225    | 300  | mV    |

#### ELECTRICAL CHARACTERISTICS (continued)

(Circuit of Figure 2, V+ = 5V,  $100/\overline{200} = 12/\overline{15} = 0V$ ; T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.)

| PARAMETER                    | SYMBOL | CONDITIONS                                         |                      | MIN | TYP  | MAX  | UNITS |

|------------------------------|--------|----------------------------------------------------|----------------------|-----|------|------|-------|

| Output Voltage High          | Voh    | EXT+, EXT-, IL = 1mA, V+ = 4.5V, PDRV= -3V         |                      | 4.3 |      |      | V     |

| Output Voltage Low           | Vol    | EXT+, EXT-, IL = -1mA,                             | V+ = 4.5V, PDRV= -3V |     |      | -2.8 | V     |

| Output Sink Current          |        | $V_{+} = 4.5V, PDRV = -3V, I_{A} = +25^{\circ}C$   | EXT + = 4.5V         | 100 | 200  |      | mA    |

| Output Sink Current          |        |                                                    | EXT- = 4.5V          | 200 | 350  |      |       |

| Output Source Current        |        | V + = 4.5V, PDRV = -3V,                            | EXT + = OV           |     | -200 | -100 |       |

|                              |        | $T_A = +25^{\circ}C$                               | EXT- = -3V           |     | -350 | -200 | – mA  |

|                              |        | $EXT+, C_{LOAD} = 2nF$                             |                      |     | 70   |      | ns    |

| Output Rise/Fall Time        |        | EXT-, $C_{LOAD} = 4nF$ , $PDRV = -3V$              |                      |     | 100  |      |       |

| PUMP Output Voltage (Note 4) |        | $V + = 4.5V$ , $I_L = -5mA$ , $T_A = +25^{\circ}C$ |                      |     |      | -3   | V     |

| Compensation Pin Impedance   |        | CC+, CC-                                           |                      |     | 10   |      | kΩ    |

| Thermal-Shutdown Threshold   |        |                                                    |                      |     | 190  |      | °C    |

| Soft-Start Source Current    |        | SS = 0V                                            |                      | 3   |      | 7    | μA    |

| Soft-Start Sink Current      |        | V+ = 3.8V, SS = 2V                                 |                      |     | -2   | -0.5 | mA    |

**Note 1:** Devices are 100% tested to these limits under 0mA to 100mA and to 125mA conditions using automatic test equipment. The ability to drive loads up to 1A is guaranteed by the current-limit threshold, output swing, and the output current source/sink tests. See Figures 2 and 3.

Note 2: Actual load capability of the circuit of Figure 2 is ±200mA in ±15V mode and ±250mA in ±12V mode. Load regulation is tested at lower limits due to test equipment limitations.

Note 3: Guaranteed by design.

Note 4: Measured at Point A, circuit of Figure 2, with PDRV disconnected.

(Circuit of Figure 2, V+ = 5V,  $T_A$  = +25°C, unless otherwise noted.)

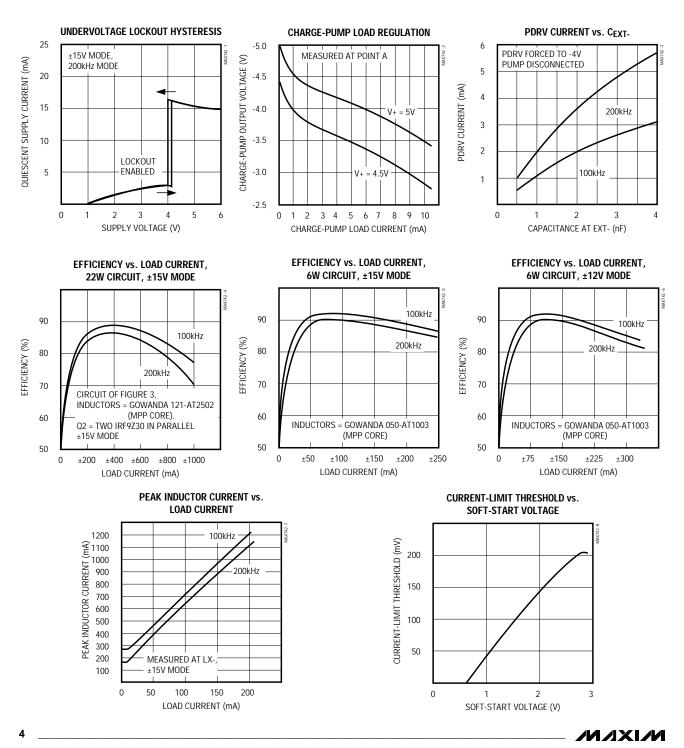

**Typical Operating Characteristics**

Typical Operating Characteristics (continued)

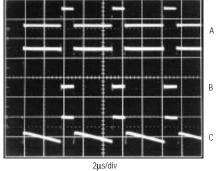

A = GATE DRIVE, 5V/div B = SWITCH VOLTAGE, 10V/div

C = SWITCH CURRENT, 0.2A/div

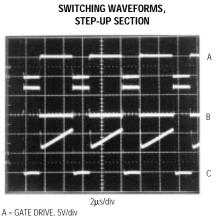

A = GATE DRIVE, 5V/div B = SWITCH VOLTAGE, 10V/div C = SWITCH CURRENT, 0.2A/div

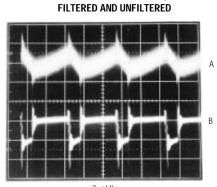

**OUTPUT-VOLTAGE NOISE**,

$\begin{array}{l} 2\mu s/div\\ A=\text{NOISE WITH i FILTER, 1mV/div}\\ B=\text{NOISE WITHOUT FILTER, 20mV/div}\\ MEASURED AT -V_{OUT}\\ V+=5V\\ BW=5MHz \end{array}$

N/IXI/N

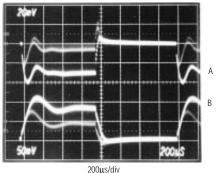

LOAD-TRANSIENT RESPONSE

A = +VO, 20mV/div B = -VO, 50mV/div

# MAX742

\_\_\_\_\_

**Pin Description**

| PIN | NAME    | FUNCTION                                                                  |

|-----|---------|---------------------------------------------------------------------------|

| 1   | FB+     | Step-Up Feedback Input                                                    |

| 2   | CC+     | Step-Up Compensation Capacitor                                            |

| 3   | AGND    | Analog Ground                                                             |

| 4   | AV+     | Analog Supply Voltage Input (+5V)                                         |

| 5   | 100/200 | Selects oscillator frequency. Ground for 200kHz, or tie to V+ for 100kHz. |

| 6   | 12/15   | Selects $V_{OUT}$ . Ground for ±15V, or tie to V+ for ±12V.               |

| 7   | VREF    | Reference Voltage Output (+2.00V). Force to GND or V+ to disable chip.    |

| 8   | SS      | Soft-Start Timing Capacitor (sources 5µA)                                 |

| 9   | CC-     | Inverting Compensation Capacitor                                          |

| 10  | FB-     | Inverting Section Feedback Input                                          |

| 11  | CSL-    | Current-Sense Low (inverting section)                                     |

| 12  | CSH-    | Current-Sense High (inverting section)                                    |

| 13  | V+      | Supply Voltage Input (+5V)                                                |

| 14  | EXT-    | Push-Pull Output—drives external P-channel MOSFET.                        |

| 15  | PDRV    | Voltage Input—negative supply for P-channel MOSFET driver.                |

| 16  | PUMP    | Charge-Pump Driver—clock output at 1/2 oscillator frequency.              |

| 17  | EXT+    | Push-Pull Output—drives external logic-level N-channel MOSFET.            |

| 18  | GND     | High-Current Ground                                                       |

| 19  | CSL+    | Current-Sense Low (step-up section)                                       |

| 20  | CSH+    | Current-Sense High (step-up section)                                      |

#### **Operating Principle**

Each current-mode controller consists of a summing amplifier that adds three signals: the current waveform from the power switch FET, an output-voltage error signal, and a ramp signal for AC compensation generated by the oscillator. The output of the summing amplifier resets a flip-flop, which in turn activates the power FET driver stage (Figure 1).

Both external transistor switches are synchronized to the oscillator and turn on simultaneously when the flipflop is set. The switches turn off individually when their source currents reach a trip threshold determined by the output-voltage error signal. This creates a dutycycle modulated pulse train at the oscillator frequency, where the on time is proportional to both the outputvoltage error signal and the peak inductor current. Low peak currents or high output-voltage error signals result in a high duty cycle (up to 90% maximum).

AC stability is enhanced by the internal ramp signal applied to the error amplifier. This scheme eliminates regenerative "staircasing" of the inductor current, which is otherwise a problem when in continuous current mode with greater than 50% duty cycle.

**MAX742**

Figure1. MAX742 Detailed Block Diagram

#### Detailed Description

#### 100kHz/200kHz Oscillator

The MAX742 oscillator frequency is generated without external components and can be set at 100kHz or 200kHz by pin strapping. Operating the device at 100kHz results in lower supply current and improved efficiency, particularly with light loads. However, component stresses increase and noise becomes more difficult to filter. For a given inductor value, the lower operating frequency results in slightly higher peak currents in the inductor and switch transistor (see *Typical Operating Characteristics*, Peak Inductor Current vs. Load Current graph). When the lower frequency is used in conjunction with an LC-type output filter (optional components in Figure 2), larger component values are required for equivalent filtering.

#### **Charge-Pump Voltage Inverter**

The charge-pump (PUMP) output is a rail-to-rail square wave at half the oscillator frequency. The square wave drives an external diode-capacitor circuit to generate a negative DC voltage (Point A in Figure 2), which in turn biases the inverting-output drive stage via PDRV. The charge pump thus increases the gate-source voltage applied to the external P-channel FET. The low on-resistance resulting from increased gate drive ensures high efficiency and guarantees start-up under heavy loads. If a -5V to -8V supply is already available, it can be tied directly to PDRV and all of the charge-pump components removed. For input voltages greater than 8V, ground PDRV to prevent overvoltage. Observe PDRV absolute maximum ratings.

7

**MAX742**

Figure 2. Standard 6W Application Circuit

M/IXI/M

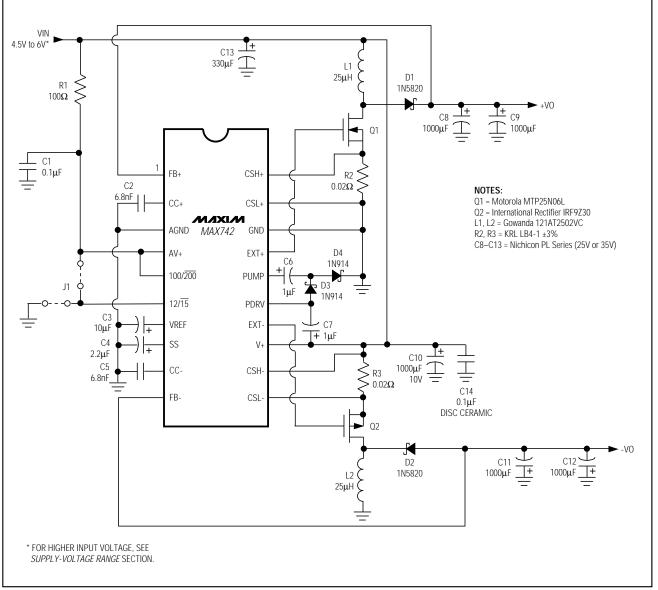

Figure 3. High-Power 22W Application Circuit

**MAX742**

#### Supply-Voltage Range

Although designed for operation from a +5V logic supply, the MAX742 works well from 4.2V (the upper limit of the undervoltage lockout threshold) to +10V (absolute maximum rating plus a safety margin). The upper limit can be further increased by limiting the voltage at V+ with a zener shunt or series regulator. To ensure AC stability, the inductor value should be scaled linearly with the nominal input voltage. For example, if Figure 3's application circuit is powered from a nominal 9V source, the inductor value should be increased to  $40\mu$ H or  $50\mu$ H. At high input voltage at PDRV. If the input can exceed 8V, ground PDRV and remove the capacitors and diodes associated with the charge pump.

#### In-Circuit Testing for Guaranteed Performance

Figure 2's circuit has been tested at all extremes of line, load, and temperature. Refer to the *Electrical Characteristics* table for guaranteed in-circuit specifications. Successful use of this circuit requires no component calculations.

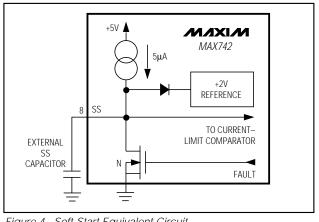

#### Soft-Start

A capacitor connected between Soft-Start (SS) and ground limits surge currents at power-up. As shown in the *Typical Operating Characteristics*, the peak switch current limit is a function of the voltage at SS. SS is internally connected to a 5 $\mu$ A current source and is diode-clamped to 2.6V (Figure 8). Soft-start timing is therefore set by the SS capacitor value. As the SS voltage ramps up, peak inductor currents rise until they reach normal operating levels. Typical values for the SS capacitor, when it is required at all, are in the range of 1 $\mu$ F to 10 $\mu$ F.

#### Fault Conditions Enabling SS Reset

In addition to power-up, the soft-start function is enabled by a variety of fault conditions. Any of the following conditions will cause an internal pull-down transistor to discharge the SS capacitor, triggering a soft-start cycle:

Undervoltage lockout Thermal shutdown VREF shorted to ground or supply VREF losing regulation

Figure 4. Soft-Start Equivalent Circuit

#### Design Procedure

#### Inductor Value

An exact inductor value isn't critical. The inductor value can be varied in order to make tradeoffs between noise, efficiency, and component sizes. Higher inductor values result in continuous-conduction operation, which maximizes efficiency and minimizes noise. Physically smallest inductors (where  $E = 1/2 LI^2$  is minimum) are realized when operating at the crossover point between continuous and discontinuous modes. Lowering the inductor value further still results in discontinuous current even at full load, which minimizes the output capacitor size required for AC stability by eliminating the right-half-plane zero found in boost and inverting topologies. Ideal current-mode slope compensation where  $m = 2 \times V/L$  is achieved if L (Henries) = RSENSE ( $\Omega$ ) x 0.001, but again the exact value isn't critical and the inductor value can be adjusted freely to improve AC performance. The following equations are given for continuous-conduction operation since the MAX742 is mainly intended for low-noise analog power supplies. See Appendix A in Maxim's Battery Management and DC-DC Converter Circuit Collection for crossover point and discontinuous-mode equations.

Boost (positive) output:

$$L = \frac{(V_{IN} - V_{SW})^2 (V_{OUT} + V_D - V_{IN})}{(V_{OUT} + V_D)^2 (I_{IOAD})(F)(LIR)}$$

Inverting (negative) output:

L =

$$\frac{(V_{IN} - V_{SW})^2}{(V_{OUT} + V_D)(I_{LOAD})(F)(LIR)}$$

where:

$V_{SW}$  is the voltage drop across the the switch transistor and current-sense resistor in the on state (0.3V typ).

$V_D$  is the rectifier forward voltage drop (0.4V typ).

LIR is the ratio of peak-to-peak ripple current to DC offset current in the inductor (0.5 typ).

#### **Current-Sense Resistor Value**

The current-sense resistor values are calculated according to the worst-case-low current-limit threshold voltage from the *Electrical Characteristics* table and the peak inductor current. The peak inductor current calculations that follow are also useful for sizing the switches and specifying the inductor current saturation ratings.

$$R_{SENSE} = \frac{150 \text{mV}}{\text{IPEAK}}$$

$$+\text{IPEAK (boost)} = \frac{\text{I}_{\text{LOAD}} (\text{VOUT} + \text{VD})}{\text{V}_{\text{IN}} - \text{V}_{\text{SW}}} + \frac{(\text{V}_{\text{IN}} - \text{V}_{\text{SW}}) (\text{VOUT} + \text{VD} - \text{V}_{\text{IN}})}{(2)(\text{F})(\text{L})(\text{VOUT} + \text{VD})}$$

$$\text{IPEAK (inverting)} = \frac{\text{I}_{\text{LOAD}} (\text{VOUT} + \text{VD} + \text{VIN})}{\text{V}_{\text{IN}} - \text{V}_{\text{SW}}}$$

$$\frac{(\text{V}_{\text{IN}} - \text{V}_{\text{SW}}) (\text{VOUT} + \text{VD} + \text{VIN})}{(2)(\text{F})(\text{L}) (\text{VOUT} + \text{VD} + \text{VIN})}$$

#### Filter Capacitor Value

The output filter capacitor values are generally determined by the effective series resistance (ESR) and voltage rating requirements rather than actual capacitance requirements for loop stability. In other words, the capacitor that meets the ESR requirement for noise purposes nearly always has much more output capacitance than is required for AC stability. Output voltage noise is dominated by ESR and can be roughly calculated by an Ohm's Law equation:

VNOISE (peak-to-peak) = IPEAK X RESR

where VNOISE is typically 0.15V.

Ensure the output capacitors selected meet the following minimum capacitance requirements:

Minimum CF =  $60\mu$ F per output or the following, whichever is greater:

| $CF = 0.015/R_{LOAD}$ | (in Farads, ±15V mode) |

|-----------------------|------------------------|

| $CF = 0.01/R_{LOAD}$  | (in Farads, ±12V mode) |

#### **Compensation Capacitor (CC) Value**

The compensation capacitors (CC+ and CC-) cancel the zero introduced by the output filter capacitors' ESR, improving phase margin, and AC stability. The compensation poles set by CC+ and CC- should be set to match the ESR zero frequencies of the output filter capacitors according to the following:

Resr x CF

CC (in Farads) = ——— (use 1000pF minimum)  $10k\Omega$

#### **Standard 6W Application**

The 6W supply (Figure 2) generates  $\pm 200$ mA at  $\pm 15$ V, or  $\pm 250$ mA at  $\pm 12$ V. Output capability is increased to 10W or more by heatsinking the power FETs, using cores with higher current capability (such as Gowanda #050AT1003), and using higher filter capacitance.

Ferrite and MPP inductor cores optimize efficiency and size. Iron-power toroids designed for high frequencies are economical, but larger.

Ripple is directly proportional to filter capacitor equivalent series resistance (ESR). In addition, about 250mV transient noise occurs at the LX switch transitions. A very short scope probe ground lead or a shielded enclosure is need for making accurate measurements of transient noise. Extra filtering, as shown in Figure 2, reduces both noise components.

#### **High-Power 22W Application**

The 22W application circuit (Figure 3) generates ±15V at ±750mA or ±12V at ±950mA. Noninductive wirewound resistors with Kelvin current-sensing connections replace the metal-film resistors of the previous (6W) circuit. Gate drive for the P-channel FET is bootstrapped from the negative supply via diode D6. The 2.7V zener (D5) is required in 15V mode to prevent overvoltage. The charge pump (D3, D4, and C6) may not be necessary if the circuit is lightly loaded (<100mA) on start-up. AIE part #415-0963 is a ferrite pot-core inductor that can be used in place of a smaller, more expensive moly-permalloy toroid inductor (L1, L2). Higher efficiencies can be achieved by adding extra MOSFETs in parallel. Load levels above 10W make it necessary to add heatsinks, especially to the Pchannel FET.

#### Table 1. Trouble-Shooting Chart

| SYMPTOM                                                                                                     | CORRECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Unstable Output.<br>Noise or jitter on<br>output ripple<br>waveform. Scope<br>may not trigger<br>correctly. | <ul> <li>Loop stability problem.</li> <li>A. CC+ or CC- disconnected.</li> <li>B. EMI: Move inductor away from IC or use shielded inductors. Keep noise sources away from CC- and CC+.</li> <li>C. Grounding: Tie AGND directly to the filter capacitor ground lead. Ensure that current spikes from GND do not cause noise at AGND or compensation capacitor or reference bypass ground leads. Use wide PC traces or a ground plane.</li> <li>D. Bypass: Tie 10µF or larger between AGND and VREF. Use 150µF to bypass the input right at AV+. If there is high source resistance, 1000µF or more may be required.</li> <li>E. Current limiting: Reduce load currents. Ensure that inductors are not saturating.</li> <li>F. Slope compensation: Inductor value not matched to sense resistor.</li> </ul> |

| Noisy Output.<br>Switching is<br>steady, but large<br>inductive spikes<br>are seen at the<br>outputs.       | <ul> <li>A. Ground noise: Probe ground is picking up switching EMI. Reduce probe ground lead length (use probe tip shield) or put circuit in shielded enclosure.</li> <li>B. Poor HF response: Add ceramic or tantalum capacitors in parallel with output filter capacitors.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Self-Destruction.<br>Transistors or IC<br>die on power-up.                                                  | <ul> <li>A. Input overvoltage: Never apply more<br/>than +12V.</li> <li>B. FB+ or FB- disconnected or shorted. This<br/>causes runaway and output overvoltage.</li> <li>C. CC+ or CC- shorted.</li> <li>D. Output filter capacitor disconnected.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Poor Efficiency.<br>Supply current is<br>high. Output will<br>not drive heavy<br>loads.                     | <ul> <li>A. Inductor saturation: Peak currents<br/>exceed coil ratings.</li> <li>B. MOSFET on-resistance too high.</li> <li>C. Switching losses: Diode is slow or has high<br/>forward voltage. Inductor has high DC resis-<br/>tance. Excess capacitance at LX nodes.</li> <li>D. Inductor core losses: Hysteresis losses<br/>cause self-heating in some core materials.</li> <li>E. Loop instability: See Unstable Output<br/>above.</li> </ul>                                                                                                                                                                                                                                                                                                                                                          |

| <b>No Output.</b> +VO<br>= 5V or lessVO<br>= 0V.                                                            | <ul> <li>A. Check connections. VREF should be +2V.</li> <li>B. When input voltage is less than +4.2V,<br/>undervoltage lockout is enabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| No Switching.<br>±VO are correct,<br>but no waveform is<br>seen at LX+ or LX                                | Output is unloaded. Apply ±30mA or greater load to observe waveform.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

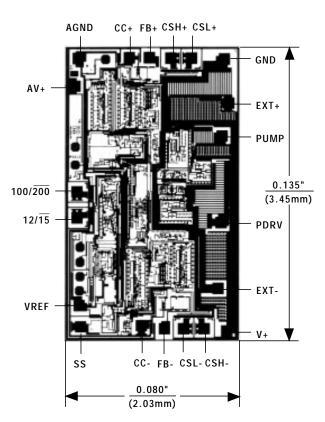

#### Chip Topography

TRANSISTOR COUNT: 375 SUBSTRATE CONNECTED TO V+