# **Excellent Integrated System Limited**

Stocking Distributor

Click to view price, real time Inventory, Delivery & Lifecycle Information:

Texas Instruments LM4931ITL/NOPB

For any questions, you can email us directly: sales@integrated-circuit.com

Datasheet of LM4931ITL/NOPB - IC AUDIO SUBSYSTEM 1.1W D 42BGA

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

LM4931

www.ti.com

SNAS251E - APRIL 2004-REVISED MAY 2013

# LM4931 Boomer<sup>™</sup> Audio Power Amplifier Series Audio Subsystem with Mono High Efficiency Loudspeaker and Stereo Headphone Amplifiers

Check for Samples: LM4931

### **FEATURES**

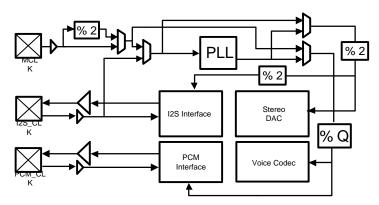

- 18-bit 44.1kHz or 48kHz Stereo DAC

- 16-bit 8kHz , 12kHz , 16kHz, or 24kHz Voice-Band Codec

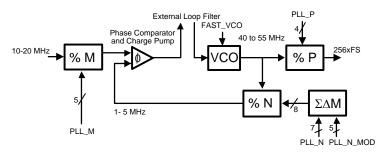

- PLL for Operation from Common System Clocks

- Either I<sup>2</sup>C or SPI Compatible Serial Interface

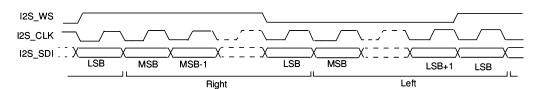

- I<sup>2</sup>S Digital Audio Data Serial Interface

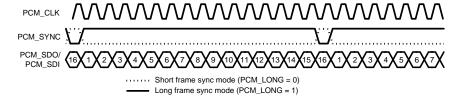

- PCM Voice Audio Data Serial Interface

- Differential Analog Microphone Input

- 26mW/Channel Stereo Headphone Amplifier

- 570mW Mono High Efficiency BTL 8Ω Amplifier

- 32-step Volume Control for Audio Output Amplifiers with 1.5dB Step Size.

- Unity-Gain Stable Headphone Amplifiers

- No Snubber Networks or Bootstrap Capacitors are Required by the Headphone or Hands-Free Amplifiers

- Adjustable Digital Side-Tone Attenuation

- 16-step Volume Control for Microphone Preamp with 2dB Step Size

- Configurable GPIO/Status Port

- Available in the 42 bump DSBGA Package

### **APPLICATIONS**

- 2.5 and 3G Mobile Phones and Multimedia Terminals

- PDAs, Internet Appliances and Portable Gaming

- Portable DVD/CD/AAC/MP3 Players

- Digital Cameras and Toys

### **KEY SPECIFICATIONS**

- P<sub>LS OUT</sub> at AV<sub>DD</sub> = 5V, 8Ω

- 1% THD+N, 1.1W (Typ)

- P<sub>LS OUT</sub> at AV<sub>DD</sub> = 3.3V, 8Ω

- 1% THD+N, 570mW (Typ)

- $P_{H/P OUT}$  at  $AV_{DD} = 5V \& AV_{DD} = 3.3V$ ,  $32\Omega$

- 1% THD+N, 26mW (Typ)

- Supply Voltage Range

- DV<sub>DD</sub>, 2.7V to 4.0V

- AV<sub>DD</sub>, 2.7V to 5.0V<sup>(1)</sup>

- Shutdown Current, 1.1µA

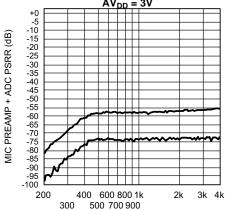

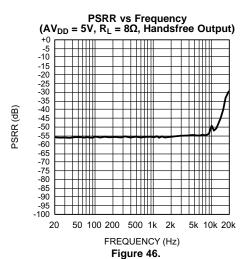

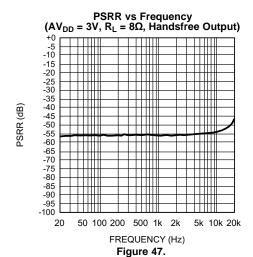

- PSRR at 217Hz, AV<sub>DD</sub> = 3V, 62dB (Typ)

- SNR (Voice Codec), 75dB (Typ)

- SNR (Audio DAC), 86dB (Typ)

# **DESCRIPTION**

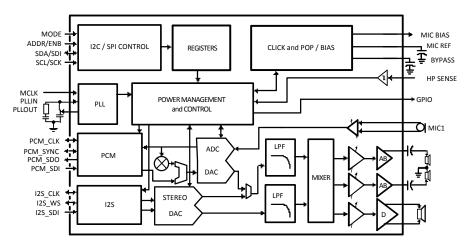

The LM4931 is an integrated audio subsystem that supports voice and digital audio functions. The LM4931 includes a high quality stereo DAC, voice band codec, a stereo headphone amplifier and a high-power high efficiency mono speaker amplifier. It is primarily designed for demanding applications in mobile phones and other portable devices.

The LM4931 features an I²S serial interface for full range audio, a 16-bit PCM bi-directional serial interface for the voice band codec and an I²C/SPI compatible interface for control. The full range music path features an SNR of 86dB with an 18-bit 48kHz input. The headphone amplifier delivers at least  $26\text{mW}_{RMS}$  to a  $32\Omega$  single-ended stereo load with less than 1% distortion (THD+N) when  $\text{AV}_{DD}=3.3\text{V}_{DC}.$  The mono speaker amplifier delivers up to  $570\text{mW}_{RMS}$  into an  $8\Omega$  load with less than 1% distortion when  $\text{AV}_{DD}=3.3\text{V}_{DC}.$

Best operation is achieved by maintaining 3.0V ≤ AV<sub>DD</sub> ≤ 5.0 and 3.0V ≤ DV<sub>DD</sub> ≤ 3.6V and AV<sub>DD</sub> ≥ DV<sub>DD</sub>.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Boomer is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

Datasheet of LM4931ITL/NOPB - IC AUDIO SUBSYSTEM 1.1W D 42BGA

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

LM4931

SNAS251E - APRIL 2004 - REVISED MAY 2013

www.ti.com

# **DESCRIPTION (CONTINUED)**

The LM4931 employs advanced techniques to reduce power consumption, to reduce controller overhead, and to eliminate click and pop. Boomer audio power amplifiers were designed specifically to provide high quality output power with a minimal amount of external components. It is therefore ideally suited for mobile phone and other low voltage applications where minimal power consumption, PCB area, and cost are primary requirements.

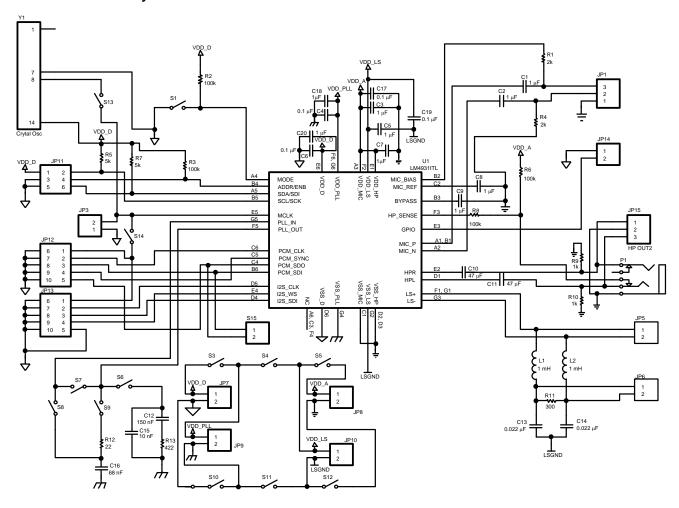

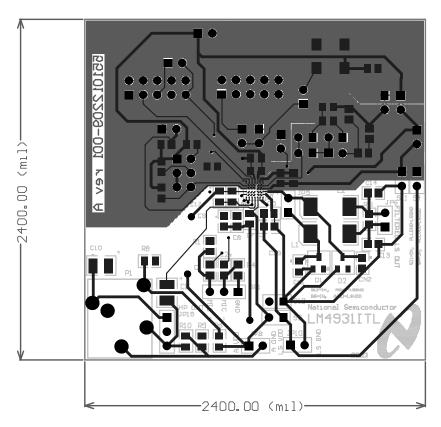

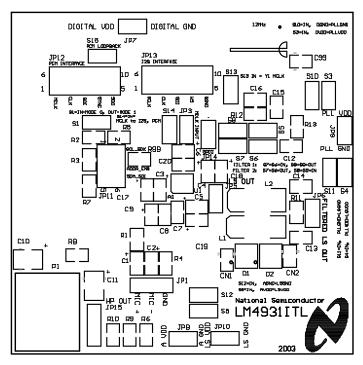

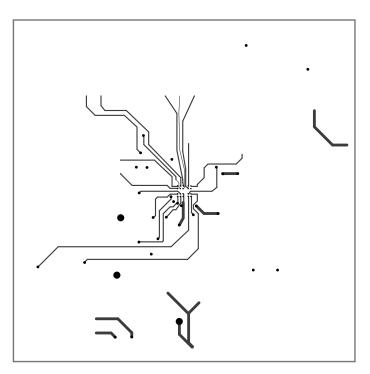

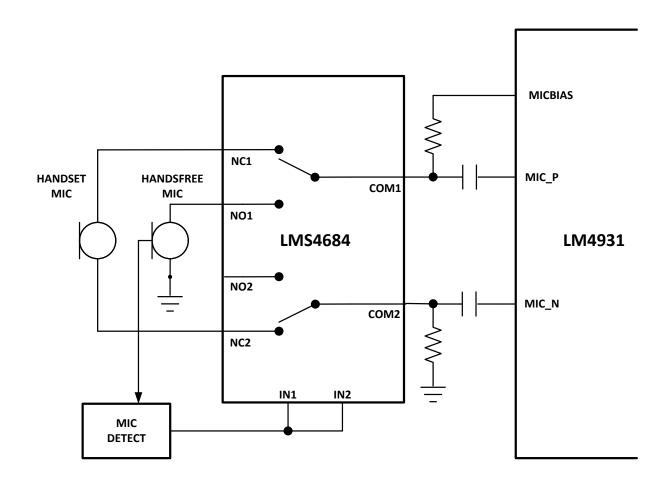

### **Typical Application**

Figure 1. Typical I<sup>2</sup>S + Voice codec application circuit for mobile phones

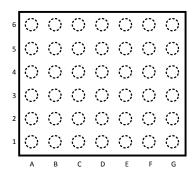

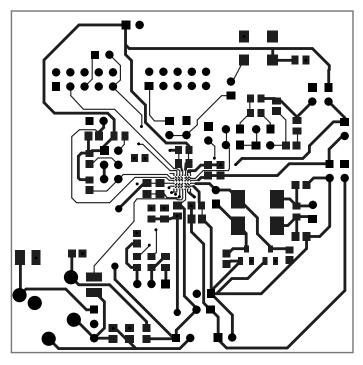

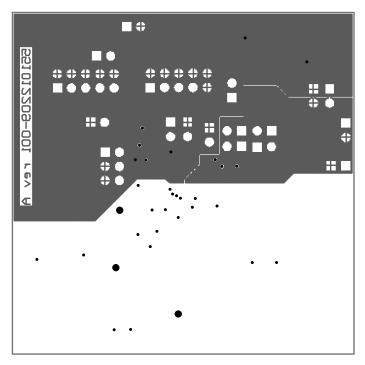

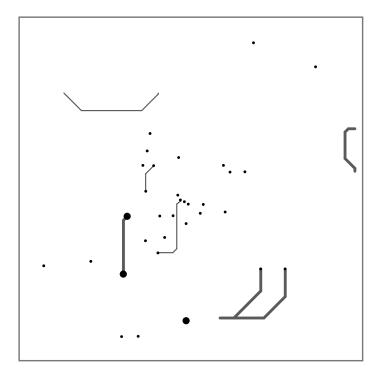

# **Connection Diagram**

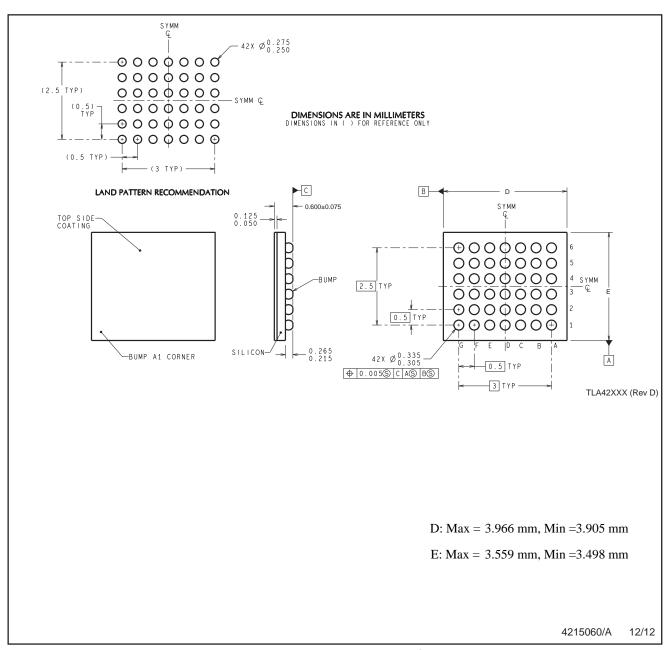

Figure 2. 42-Bump DSBGA (Top View) See Package Number YZR0042

Submit Documentation Feedback

Copyright © 2004–2013, Texas Instruments Incorporated

Datasheet of LM4931ITL/NOPB - IC AUDIO SUBSYSTEM 1.1W D 42BGA Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

LM4931

www.ti.com

SNAS251E - APRIL 2004-REVISED MAY 2013

### PIN DESCRIPTIONS

| PIN | PIN NAME             | D/A | I/O | DESCRIPTION                                                               |  |

|-----|----------------------|-----|-----|---------------------------------------------------------------------------|--|

| A1  | MIC_P                | Α   | I   | Microphone positive differential input                                    |  |

| A2  | MIC_N                | Α   | I   | Microphone negative differential input                                    |  |

| A3  | VDD(MIC)             | Α   | I   | Analog Vdd for microphone section                                         |  |

| A4  | MODE                 | D   | 1   | Selects between SPI and $I^2C$ control interfaces ( $I^2C = 0$ , SPI = 1) |  |

| A5  | SDA/SDI              | D   | I/O | I <sup>2</sup> C_SDA or SPI_SDI depending on the MODE control             |  |

| A6  | NC                   | N/A | N/A | No Connect                                                                |  |

| B1  | MIC_P                | Α   | I   | Microphone positive differential input                                    |  |

| B2  | MIC_BIAS             | Α   | 0   | 2V ultra clean power supply for microphones                               |  |

| B3  | BYPASS               | Α   | I   | Click and Pop / VDD/2 reference filter                                    |  |

| B4  | ADDR/ENB             | D   | I   | I <sup>2</sup> C_ADDR or SPI_ENB depending on the MODE control            |  |

| B5  | SCL/SCK              | D   | I   | I <sup>2</sup> C_SCL or SPI_SCK depending on the MODE control             |  |

| B6  | PCM_SDI              | D   | 1   | PCM_SDI voice data input                                                  |  |

| C1  | VSS(MIC)             | Α   | I   | Analog Vss for microphone section                                         |  |

| C2  | MIC_REF              | Α   | I   | Filter for microphone power supply                                        |  |

| C3  | NC                   | N/A | N/A | No Connect                                                                |  |

| C4  | PCM_SDO              | D   | 0   | PCM_SDO serial data output                                                |  |

| C5  | PCM_SYNC             | D   | I/O | PCM_SYNC pulse for the PCM bus                                            |  |

| C6  | PCM-CLK              | D   | I/O | PCM_SYNC pulse for the PCM bus                                            |  |

| D1  | HPL                  | А   | 0   | Left Headphone output                                                     |  |

| D2  | VSS(HP)              | Α   | I   | Analog Vss for Headphone and Mixer sections                               |  |

| D3  | VSS(HP)              | А   | 1   | Analog Vss for Headphone and Mixer sections                               |  |

| D4  | I <sup>2</sup> S_SDI | D   | 1   | I <sup>2</sup> S serial data input                                        |  |

| D5  | I <sup>2</sup> S_CLK | D   | I/O | I <sup>2</sup> S clock signal                                             |  |

| D6  | VSSD                 | D   | 1   | Digital Vss                                                               |  |

| E1  | VDD(HP)              | А   | 1   | Analog Vdd for Headphone and Mixer sections                               |  |

| E2  | HPR                  | Α   | 0   | Right Headphone output                                                    |  |

| E3  | GPIO                 | D   | 0   | Configurable multi purpose output                                         |  |

| E4  | I <sup>2</sup> S_WS  | D   | I/O | I <sup>2</sup> S word select signal                                       |  |

| E5  | MCLK                 | D   | 1   | Input clock from 10MHz - 24.576MHz                                        |  |

| E6  | VDDD                 | D   | I   | Digital Vdd                                                               |  |

| F1  | LS+                  | А   | 0   | Loudspeaker positive output                                               |  |

| F2  | VDD(LS)              | Α   | I   | Analog Vdd for Loudspeaker section                                        |  |

| F3  | HP_SENSE             | Α   | I   | Input for headphone connection sense circuit                              |  |

| F4  | NC                   | N/A | N/A | No Connect                                                                |  |

| F5  | PLL_OUT              | D   | 0   | PLL filter output                                                         |  |

| F6  | VDD(PLL)             | D   | 1   | Digital Vdd for PLL section                                               |  |

| G1  | LS+                  | Α   | 0   | Loudspeaker positive output                                               |  |

| G2  | VSS(LS)              | Α   | I   | Analog Vss for Loudspeaker section                                        |  |

| G3  | LS-                  | Α   | 0   | Loudspeaker negative output                                               |  |

| G4  | VSS(PLL)             | D   | I   | Digital Vss for PLL section                                               |  |

| G5  | PLL_IN               | D   | I   | PLL filter input                                                          |  |

| G6  | VDD(PLL)             | D   | 1   | Digital Vdd for PLL section                                               |  |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Datasheet of LM4931ITL/NOPB - IC AUDIO SUBSYSTEM 1.1W D 42BGA

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

# LM4931

SNAS251E - APRIL 2004 - REVISED MAY 2013

www.ti.com

# Absolute Maximum Ratings (1)(2)

| Analog Supply Voltage            |                                 | 6.0V               |

|----------------------------------|---------------------------------|--------------------|

| Digital Supply Voltage           |                                 | 6.0V               |

| Storage Temperature              |                                 | -65°C to +150°C    |

| Power Dissipation <sup>(3)</sup> |                                 | Internally Limited |

| ESD Susceptibility               | Human Body Model <sup>(4)</sup> | 2500V              |

|                                  | Machine Model (5)               | 200V               |

| Junction Temperature             |                                 | 150°C              |

| Thermal Resistance               | θ <sub>JA</sub> - YZR0042       | 105°C/W            |

|                                  |                                 |                    |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional but do not ensure specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which ensure specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not ensured for parameters where no limit is given, however, the typical value is a good indication of device performance.

- (2) All voltages are measured with respect to the relevant GND pin unless otherwise specified. All grounds should be coupled as close as possible to the device.

- (3) The maximum power dissipation must be derated at elevated temperatures and is dictated by T<sub>JMAX</sub> ,θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation is P<sub>DMAX</sub> = (T<sub>JMAX</sub> T<sub>A</sub>) / θ<sub>JA</sub> or the number given in Absolute Maximum Ratings, whichever is lower. For the LM4931, see power derating currents for more information.

- (4) Human body model: 100pF discharged through a  $1.5k\Omega$  resistor.

- 5) Machine model: 220pF 240pF discharged through all pins.

### **Operating Ratings**

| 1 0 0             |                                 |                                |

|-------------------|---------------------------------|--------------------------------|

| Temperature Range | $T_{MIN} \le T_A \le T_{MAX}$   | -40°C ≤ T <sub>A</sub> ≤ +85°C |

| Committee of      | DV <sub>DD</sub> <sup>(1)</sup> | 2.7V - 4.0V                    |

| Supply Voltage    | AV <sub>DD</sub> <sup>(1)</sup> | 2.7V - 5.0V                    |

Best operation is achieved by maintaining 3.0V ≤ AV<sub>DD</sub> ≤ 5.0 and 3.0V ≤ DV<sub>DD</sub> ≤ 3.6V and AV<sub>DD</sub> ≥ DV<sub>DD</sub>.

# Electrical Characteristics $DV_{DD} = 3V$ , $AV_{DD} = 3V$ , $R_{LHP} = 32\Omega$ , $R_{LHF} = 8\Omega^{(1)(2)}$

The following specifications apply for the circuit shown in Figure 62, unless otherwise specified. Limits apply for  $T_A = 25^{\circ}$ C.

| Symbol             | Parameter                    | Conditions                               | LM4                   | 1931                  | Units    |

|--------------------|------------------------------|------------------------------------------|-----------------------|-----------------------|----------|

|                    |                              |                                          | Typical <sup>(3</sup> | Limits <sup>(4)</sup> | (Limits) |

| Power              |                              |                                          | <u> </u>              |                       |          |

|                    |                              | Mode 0                                   |                       |                       |          |

| $DI_SD$            | Digital Shutdown Current     | f <sub>MLCK</sub> = 12MHz <sup>(5)</sup> | 400                   | 500                   | μA (max) |

|                    |                              | No MCLK                                  | 1                     | 2                     | μA (max) |

| DI <sub>ST</sub>   | Digital Standby Current      | Mode 1, f <sub>MCLK</sub> = 12MHz        | 400                   | 1200                  | μA (max) |

|                    |                              | f <sub>MLCK</sub> = 12MHz                |                       |                       |          |

| DI                 | Digital Power Supply Current | Mode 2, 3, 4                             | 1.3                   | 3.2                   | mA (max) |

| $DI_DD$            |                              | Mode 5, 6, 7                             | 2.8                   | 7                     | mA (max) |

|                    |                              | Mode 8, 9, 10                            | 3.2                   | 7.5                   | mA (max) |

| PLLI <sub>DD</sub> | PLL Quiescent Current        | f <sub>MCLK</sub> = 12MHz                | 2.8                   | 3.5                   | mA (max) |

| Al <sub>SD</sub>   | Analog Shutdown Current      | Mode 0, No load                          | 0.1                   | 2.5                   | μA (max) |

| Al <sub>ST</sub>   | Analog Standby Current       | Mode 1, No load                          | 100                   | 200                   | μA (max) |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional but do not ensure specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which ensure specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not ensured for parameters where no limit is given, however, the typical value is a good indication of device performance.

- (2) All voltages are measured with respect to the relevant GND pin unless otherwise specified. All grounds should be coupled as close as possible to the device.

- (3) Typicals are measured at 25°C and represent the parametric norm.

- (4) Limits are ensured to TI's AOQL (Average Outgoing Quality Level).

- (5) Digital shutdown current is measured with system clock set for PLL output while the PLL is disabled.

4 Submit Documentation Feedback

Copyright © 2004–2013, Texas Instruments Incorporated

Datasheet of LM4931ITL/NOPB - IC AUDIO SUBSYSTEM 1.1W D 42BGA

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

LM4931

www.ti.com

SNAS251E - APRIL 2004-REVISED MAY 2013

# Electrical Characteristics DV<sub>DD</sub> = 3V, AV<sub>DD</sub> = 3V, R<sub>LHP</sub> = $32\Omega$ , R<sub>LHF</sub> = $8\Omega^{(1)(2)}$ (continued)

The following specifications apply for the circuit shown in Figure 62, unless otherwise specified. Limits apply for  $T_A = 25$ °C.

| Symbol                 | Parameter                                                         | Conditions                                                                                                          | LM <sup>2</sup>       | 1931     | Units     |  |

|------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------|----------|-----------|--|

|                        |                                                                   | Typical <sup>(3</sup>                                                                                               | Limits <sup>(4)</sup> | (Limits) |           |  |

|                        |                                                                   | No Load                                                                                                             |                       |          |           |  |

|                        |                                                                   | Mode 2                                                                                                              | 7.8                   | 19       | mA (max)  |  |

|                        |                                                                   | Mode 3                                                                                                              | 5.3                   | 10       | mA (max)  |  |

| ٨١                     | Analog Power Supply Quiescent                                     | Mode 4                                                                                                              | 8.6                   | 15       | mA (max)  |  |

| Al <sub>DD</sub>       | Current                                                           | Mode 5                                                                                                              | 8.4                   | 15       | mA (max)  |  |

|                        |                                                                   | Mode 6                                                                                                              | 6.0                   | 15       | mA (max)  |  |

|                        |                                                                   | Mode 7                                                                                                              | 9.2                   | 15       | mA (max)  |  |

|                        |                                                                   | Mode 8, 9, 10                                                                                                       | 10.1                  | 16       | mA (max)  |  |

| Loudspeaker            | Amplifier                                                         |                                                                                                                     |                       |          |           |  |

| $V_{FS}$               | Full-Scale Output Voltage<br>Loudspeaker Amplifier)               | $8\Omega$ load, 0dB gain setting                                                                                    | 2.6                   |          | $V_{P-P}$ |  |

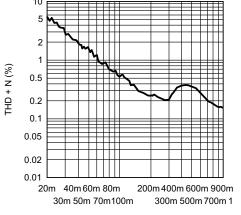

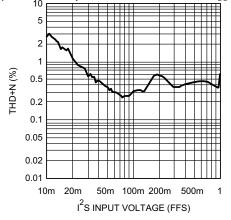

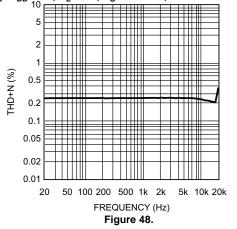

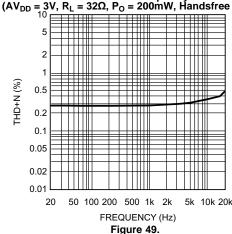

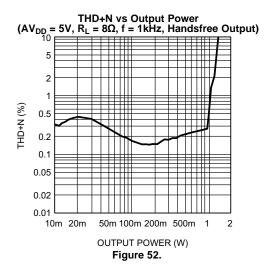

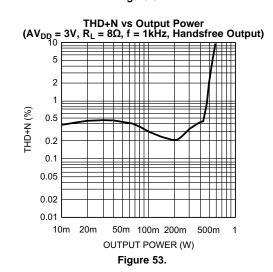

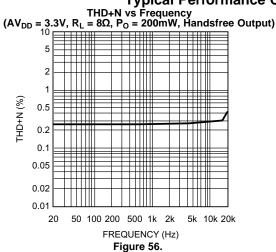

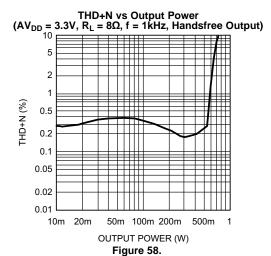

| THD+N                  | Total Harmonic Distortion + Noise                                 | f <sub>OUT</sub> = 1kHz, P <sub>OUT</sub> = 200mW                                                                   | 0.4                   |          | %         |  |

| P <sub>OLS</sub>       | Loudspeaker Amplifier Output Power                                | THD = 1% (max), f <sub>OUT</sub> = 1kHz                                                                             | 470                   | 350      | mW (min)  |  |

| PSRR                   | Power Supply Rejection Ratio (Loudspeaker Amplifier)              | y Rejection Ratio $C_B = 1.0 \mu F$                                                                                 |                       |          | dB        |  |

| SNR (Voice)            | Signal-to-Noise Ratio of Voice<br>Channel (Loudspeaker Amplifier) | Signal = V <sub>O</sub> at 0dBFS, f = 1kHz,<br>Noise = digital zero, A-weighted,<br>0dB gain setting <sup>(6)</sup> |                       |          |           |  |

|                        |                                                                   | f <sub>MCLK</sub> = 12.288MHz, PLL disabled                                                                         | 71                    |          | dB        |  |

|                        |                                                                   | f <sub>MCLK</sub> = 12MHz, PLL active                                                                               | 70                    |          | dB        |  |

| SNR (Music)            | Signal-to-Noise Ratio of Music<br>Channel (Loudspeaker Amplifier) | Signal = V <sub>O</sub> at 0dBFS, f = 1kHz,<br>Noise = digital zero, A-weighted,<br>0dB gain setting <sup>(6)</sup> |                       |          |           |  |

| J (                    | Output Noise                                                      | f <sub>MCLK</sub> = 12.288MHz, PLL disabled                                                                         | 78                    |          | dB        |  |

|                        |                                                                   | f <sub>MCLK</sub> = 12MHz, PLL active                                                                               | 76                    |          | dB        |  |

|                        |                                                                   | A-weighted filter, V <sub>in</sub> = digital zero <sup>(7)</sup>                                                    |                       |          |           |  |

| e <sub>N</sub> (Music) | Output Noise                                                      | f <sub>MCLK</sub> = 12.288MHz, PLL disabled                                                                         | 120                   |          | μV        |  |

|                        |                                                                   | f <sub>MCLK</sub> = 12MHz, PLL active                                                                               | 140                   |          | μV        |  |

| Vos                    | Offset Voltage                                                    |                                                                                                                     | 10                    |          | mV        |  |

| VCD                    | Volume Control Range (Loudspeaker                                 | Minimum Gain                                                                                                        | -34.5                 |          | dB        |  |

| VCR                    | Amplifier)                                                        | Maximum Gain                                                                                                        | 12                    |          | dB        |  |

| SS                     | Volume Control Step Size (Loudspeaker Amplifier)                  |                                                                                                                     | 1.5                   |          | dB        |  |

| Headphone A            | mplifier                                                          |                                                                                                                     |                       |          |           |  |

| V <sub>FS</sub>        | Full Scale Ouput Voltage<br>(Headphone Amplifier)                 | 32Ω load, 0dB gain setting                                                                                          | 2.6                   |          | $V_{P-P}$ |  |

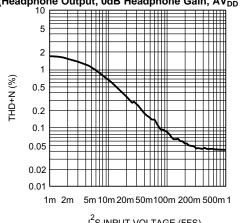

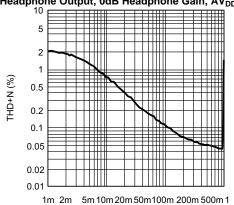

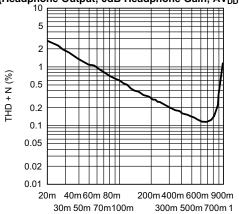

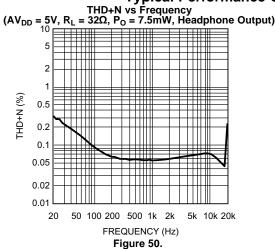

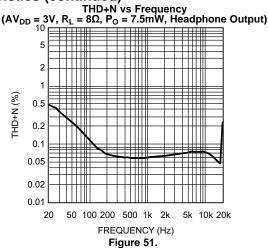

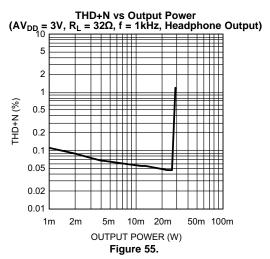

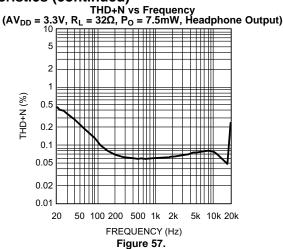

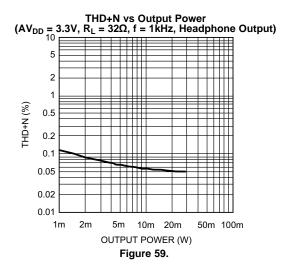

| THD+N                  | Total Harmonic Distortion + Noise (Headphone Amplifier)           | $f_{IN}$ = 1kHz, $P_{OUT}$ = 7.5mW, 0.04 32 $\Omega$ stereo load                                                    |                       |          | %         |  |

| P <sub>OHP</sub>       | Output Power (Headphone Amplifier)                                | THD = 0.5%, f <sub>OUT</sub> = 1KHz                                                                                 | 26                    | 19       | mW (min)  |  |

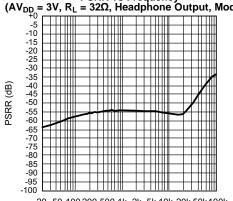

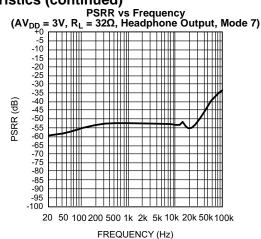

| PSRR                   | Power Supply Rejection Ratio (Headphone Amplifier)                | $C_B = 1.0 \mu F$<br>$V_{RIPPLE} = 200 m V_{PP}$<br>$f_{RIPPLE} = 217 H z$                                          | 62                    |          | dB        |  |

Disabling or bypassing the PLL will result in an improvement in noise measurements. Disabling or bypassing the PLL will result in an improvement in noise measurements.

Datasheet of LM4931ITL/NOPB - IC AUDIO SUBSYSTEM 1.1W D 42BGA

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

# LM4931

SNAS251E -APRIL 2004-REVISED MAY 2013

www.ti.com

# Electrical Characteristics DV<sub>DD</sub> = 3V, AV<sub>DD</sub> = 3V, R<sub>LHP</sub> = $32\Omega$ , R<sub>LHF</sub> = $8\Omega^{(1)(2)}$ (continued)

The following specifications apply for the circuit shown in Figure 62, unless otherwise specified. Limits apply for  $T_A = 25$ °C.

| Symbol                 | Parameter                                                       | Conditions                                                                                                                                                   | LM4931                |                       | Units    |

|------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|----------|

|                        |                                                                 |                                                                                                                                                              | Typical <sup>(3</sup> | Limits <sup>(4)</sup> | (Limits) |

| SNR (Voice)            | Signal-to-Noise Ratio of Voice<br>Channel (Headphone Amplifier) | Signal = V <sub>O</sub> at 0dBFS, f = 1kHz and 1%<br>THD+N,<br>Noise = digital zero, A-weighted,<br>0dB gain setting <sup>(7)</sup>                          |                       |                       |          |

|                        | Chaimer (Fleadphone 7 impliner)                                 | f <sub>MCLK</sub> = 12.288MHz, PLL disabled                                                                                                                  | 75                    |                       | dB       |

|                        |                                                                 | f <sub>MCLK</sub> = 12MHz, PLL active                                                                                                                        | 73                    |                       | dB       |

| SNR (Music)            | Signal-to-Noise Ratio of Music<br>Channel (Headphone Amplifier) | Signal = V <sub>O</sub> at 0dBFS, f = 1kHz and 1%<br>THD+N,<br>Noise = digital zero, A-weighted,<br>0dB gain setting <sup>(7)</sup>                          |                       |                       |          |

|                        | Chains (Hodephene / Impinion)                                   | f <sub>MCLK</sub> = 12.288MHz, PLL disabled                                                                                                                  | 86                    |                       | dB       |

|                        |                                                                 | f <sub>MCLK</sub> = 12MHz, PLL active                                                                                                                        | 82                    |                       | dB       |

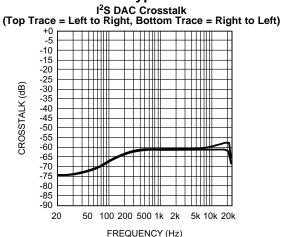

| X <sub>TALK</sub>      | Stereo Channel-to-Channel Crosstalk                             | $f_S = 48kHz$ ,<br>$f_{IN} = 1kHz$ sinewave at $-3dBFS$                                                                                                      | 62                    |                       | dB       |

| ΔA <sub>CH-CH</sub>    | Stereo Channel-to-Channel Gain<br>Mismatch                      |                                                                                                                                                              | 0.3                   |                       | dB       |

|                        |                                                                 | A-weighted filter,<br>Vin = digital zero <sup>(7)</sup>                                                                                                      |                       |                       |          |

| e <sub>N</sub> (Music) | Output Noise                                                    | f <sub>MCLK</sub> = 12.288MHz, PLL disabled                                                                                                                  | 45                    |                       | μV       |

|                        |                                                                 | f <sub>MCLK</sub> = 12MHz, PLL active                                                                                                                        | 65                    |                       | μV       |

| VCR                    | Volume Control Range (Headphone                                 | Minimum Gain                                                                                                                                                 | -46.5                 |                       | dB       |

| VOIC                   | Amplifier)                                                      | Maximum Gain                                                                                                                                                 | 0                     |                       | dB       |

| SS                     | Volume Control Stepsize (Headphone Amplifier)                   |                                                                                                                                                              | 1.5                   |                       | dB       |

| Microphone A           | Amplifier                                                       |                                                                                                                                                              |                       |                       |          |

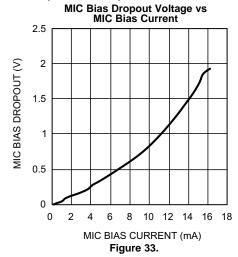

| $V_{BIAS}$             | Mic Bias Voltage                                                |                                                                                                                                                              | 2                     |                       | V        |

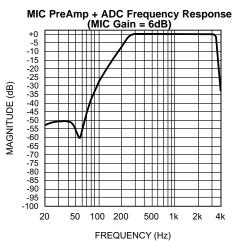

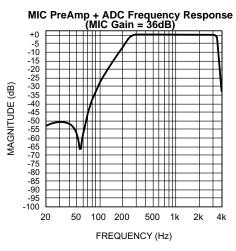

| GCR                    | Gain Control Range (Microphone                                  | Minimum Gain                                                                                                                                                 | 6                     |                       | dB       |

|                        | Amplifier)                                                      | Maximum Gain                                                                                                                                                 | 36                    |                       | dB       |

| SS                     | Gain Control Stepsize (Microphone Amplifier)                    |                                                                                                                                                              | 2                     |                       | dB       |

| Voice Codec            | (Typical numbers are with 1.024MHz                              | voice clock and 8kHz sampling frequency)                                                                                                                     |                       |                       |          |

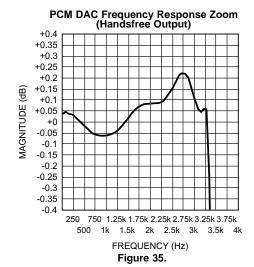

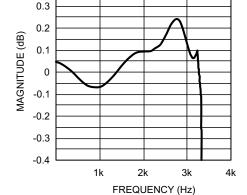

| R <sub>VDAC</sub>      | Voice DAC Ripple                                                | 300Hz-3.3kHz through headphone output.                                                                                                                       | +/- 0.15              |                       | dB       |

| R <sub>VADC</sub>      | Voice ADC Ripple                                                | 300Hz-3.3kHz through headphone output.                                                                                                                       | +/- 0.25              |                       | dB       |

| PB <sub>VDAC</sub>     | Voice DAC Passband                                              | -3dB Point                                                                                                                                                   | 3.46                  |                       | kHz      |

| SBA <sub>VDAC</sub>    | Voice DAC Stopband Attenuation                                  | Above 4kHz                                                                                                                                                   | 72                    |                       | dB       |

| UPB <sub>VDAC</sub>    | Upper Passband Cutoff Frequency                                 | Upper – 3dB Point                                                                                                                                            | 3.47                  |                       | kHz      |

| LPB <sub>VDAC</sub>    | Lower Passband Cutoff Frequency                                 | Lower – 3dB Point                                                                                                                                            | 0.230                 |                       | kHz      |

| SBA <sub>VADC</sub>    | Voice ADC Stopband Attenuation                                  | Above 4kHz                                                                                                                                                   | 65                    |                       | dB       |

| SBA <sub>NOTCH</sub>   | Voice ADC Notch Attenuation                                     | Centered on 55Hz, figure gives worst case attenuation for 50Hz & 60Hz                                                                                        | 58                    |                       | dB       |

| SNR (Voice)            | Signal-to-Noice Ratio of Voice<br>Channel (Voice ADC path)      | Signal = V <sub>O</sub> at 0dBFS, f = 1kHz and 1%<br>THD+N,<br>MIC_P, MIC_N Terminated to ground,<br>A-weighted, 36dB MIC Preamp gain setting <sup>(8)</sup> |                       |                       |          |

|                        | , , , ,                                                         | f <sub>MCLK</sub> = 12.288MHz, PLL disabled                                                                                                                  | 81                    |                       | dB       |

|                        |                                                                 | f <sub>MCLK</sub> = 12MHz, PLL active                                                                                                                        | 80                    |                       | dB       |

| STR                    | Side Tone Range                                                 | Minimum Gain                                                                                                                                                 | -30                   |                       | dB       |

|                        | olde folie Italige                                              | Maximum Gain                                                                                                                                                 | 0                     |                       | dB       |

(8) Disabling or bypassing the PLL will result in an improvement in noise measurements.

Submit Documentation Feedback

Copyright © 2004–2013, Texas Instruments Incorporated

6

Datasheet of LM4931ITL/NOPB - IC AUDIO SUBSYSTEM 1.1W D 42BGA Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

LM4931

www.ti.com

SNAS251E - APRIL 2004-REVISED MAY 2013

# Electrical Characteristics DV<sub>DD</sub> = 3V, AV<sub>DD</sub> = 3V, R<sub>LHP</sub> = $32\Omega$ , R<sub>LHF</sub> = $8\Omega^{(1)(2)}$ (continued)

The following specifications apply for the circuit shown in Figure 62, unless otherwise specified. Limits apply for  $T_A = 25$ °C.

| Symbol                  | Parameter                            | Conditions                                           | LM4931                |                       | Units                  |

|-------------------------|--------------------------------------|------------------------------------------------------|-----------------------|-----------------------|------------------------|

|                         |                                      |                                                      | Typical <sup>(3</sup> | Limits <sup>(4)</sup> | (Limits)               |

| SS                      | Side Tone Step Size                  |                                                      | 3                     |                       | dB                     |

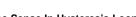

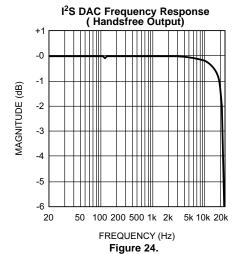

| Audio DAC (             | Typical numbers are with 6.144MHz at | udio clock and 48kHz sampling frequency)             |                       |                       |                        |

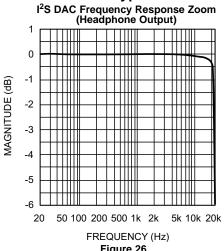

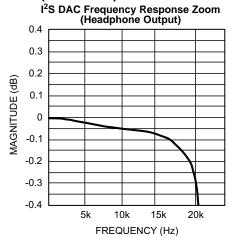

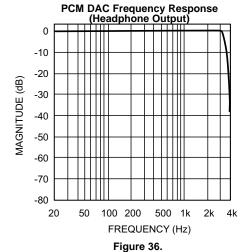

| R <sub>DAC</sub>        | Audio DAC Ripple                     | 20Hz-20kHz through headphone output                  | +/-0.1                |                       | dB                     |

| PB <sub>DAC</sub>       | Audio DAC Passband width             | -3dB point                                           | 22.7                  |                       | kHz                    |

| SBA <sub>DAC</sub>      | Audio DAC Stop band Attenuation      | Above 24kHz                                          | 76                    |                       | dB                     |

| DR <sub>DAC</sub>       | Audio DAC Dynamic Range              | DC – 20kHz                                           | 97                    |                       | dB                     |

| SNR <sub>DAC</sub>      | Audio DAC SNR Digital Filter Section | DC – 20kHz                                           | 97                    |                       | dB                     |

| PLL                     | -                                    |                                                      |                       |                       |                        |

| $f_{\text{IN}}$         | Input Frequency on MCLK pin          |                                                      | 12                    | 10<br>25              | MHz (min)<br>MHz (max) |

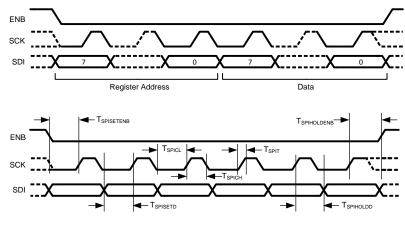

| SPI/I <sup>2</sup> C    |                                      |                                                      | II.                   | l l                   |                        |

| f <sub>SPI</sub>        | Maximum SPI Frequency                |                                                      | 400                   | 4000                  | kHz (max)              |

| t <sub>SPISETD</sub>    | SPI Data Setup Time                  |                                                      |                       | 100                   | ns (min)               |

| t <sub>SPISETENB</sub>  | SPI ENB Setup Time                   |                                                      |                       | 100                   | ns (min)               |

| t <sub>SPIHOLDD</sub>   | SPI Data Hold Time                   |                                                      |                       | 100                   | ns (min)               |

| t <sub>SPIHOLDENB</sub> | SPI ENB Hold Time                    |                                                      |                       | 100                   | ns (min)               |

| t <sub>SPICL</sub>      | SPI Clock Low Time                   |                                                      |                       | 500                   | ns (min)               |

| t <sub>SPICH</sub>      | SPI Clock HighTime                   |                                                      |                       | 500                   | ns (min)               |

| t <sub>SPIT</sub>       | SPI Clock Transition Time            |                                                      |                       | 5                     | ns (min)               |

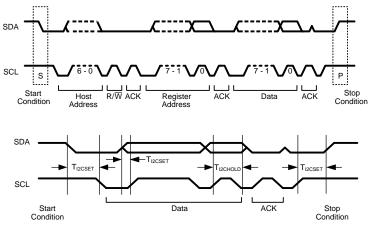

| f <sub>CLKI2C</sub>     | I <sup>2</sup> C_CLK Frequency       |                                                      | 400                   | 3400                  | kHz (max)              |

| t <sub>I2CHOLD</sub>    | I <sup>2</sup> C_DATA Hold Time      |                                                      |                       | 100                   | ns (min)               |

| t <sub>I2CSET</sub>     | I <sup>2</sup> C_DATA Setup Time     |                                                      |                       | 100                   | ns (min)               |

| PCM/I <sup>2</sup> S    |                                      |                                                      |                       |                       |                        |

| f <sub>CLKPCM</sub>     | PCM_CLK Frequency                    |                                                      | 128                   |                       | kHz                    |

|                         | PCM_CLK Duty Cycle                   |                                                      | 50                    | 40<br>60              | % (min)<br>% (max)     |

| f <sub>CLKI2S</sub>     | I <sup>2</sup> S_CLK Frequency       | I <sup>2</sup> S_RES = 0<br>I <sup>2</sup> S_RES = 1 | 1536<br>3072          |                       | kHz<br>kHz             |

|                         | I <sup>2</sup> S_WS Duty Cycle       |                                                      | 50                    | 40<br>60              | % (min)<br>% (max)     |

Datasheet of LM4931ITL/NOPB - IC AUDIO SUBSYSTEM 1.1W D 42BGA

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

# LM4931

SNAS251E - APRIL 2004 - REVISED MAY 2013

www.ti.com

# Electrical Characteristics DV<sub>DD</sub> = 3.3V, AV<sub>DD</sub> = 5V, $R_{LHP}$ = 32 $\Omega$ , $R_{LHF}$ = 8 $\Omega^{(1)(2)}$

The following specifications apply for the circuit shown in Figure 1, unless otherwise specified. Limits apply for T<sub>A</sub>= 25°C.

| Symbol             | Parameter                                            | Conditions                                                                                                        | LM4931 |                       | Units            |  |

|--------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------|-----------------------|------------------|--|

|                    |                                                      |                                                                                                                   |        | Limits <sup>(4)</sup> | (Limits)         |  |

| Power              |                                                      | 1                                                                                                                 |        |                       |                  |  |

|                    |                                                      | Mode 0                                                                                                            |        |                       |                  |  |

| $DI_SD$            | Digital Shutdown Current                             | f <sub>MCLK</sub> = 12MHz <sup>(5)</sup>                                                                          | 500    | 600                   | μA (max)         |  |

|                    |                                                      | No MCLK                                                                                                           | 1      |                       | μA (max)         |  |

| DI <sub>ST</sub>   | Digital Standby Current                              | Mode 1, f <sub>MCLK</sub> = 12MHz                                                                                 | 500    | 1600                  | μA (max)         |  |

|                    |                                                      | f <sub>MCLK</sub> = 12MHz                                                                                         |        |                       |                  |  |

| DI                 | Birital Brown Country                                | Mode 2, 3, 4                                                                                                      | 1.6    | 3.5                   | mA (max)         |  |

| DI <sub>DD</sub>   | Digital Power Supply Current                         | Mode 5, 6, 7                                                                                                      | 3.5    | 8                     | mA (max)         |  |

|                    |                                                      | Mode 8, 9, 10                                                                                                     | 4.0    | 8                     | mA (max)         |  |

| PLLI <sub>DD</sub> | PLL Quiescent Current                                | f <sub>MCLK</sub> = 12MHz                                                                                         | 3.3    | 4                     | mA (max)         |  |

| Al <sub>DD</sub>   | Analog Shutdown Current                              | Mode 0, No Load                                                                                                   | 0.6    | 3                     | μA (max)         |  |

| Al <sub>ST</sub>   | Analog Standby Current                               | Mode 1, No Load                                                                                                   | 220    | 450                   | μA (max)         |  |

|                    |                                                      | No Load                                                                                                           |        |                       |                  |  |

|                    |                                                      | Mode 2                                                                                                            | 18.5   | 32                    | mA (max)         |  |

|                    | Analog Power Supply Quiescent<br>Current             | Mode 3                                                                                                            | 7.3    | 12                    | mA (max)         |  |

|                    |                                                      | Mode 4                                                                                                            | 19.6   | 29                    | mA (max)         |  |

| $AI_{DD}$          |                                                      | Mode 5                                                                                                            | 19.4   | 30                    | mA (max)         |  |

|                    |                                                      | Mode 6                                                                                                            | 8.4    | 26                    | mA (max)         |  |

|                    |                                                      | Mode 7                                                                                                            | 20.5   | 30                    | mA (max)         |  |

|                    |                                                      | Mode 8, 9, 10                                                                                                     | 22     | 32                    | mA (max)         |  |

| Loudspeaker        | Amplifier                                            |                                                                                                                   |        |                       |                  |  |

| V <sub>FS</sub>    | Full-Scale Output Voltage (Mono speaker amplifie)r   | 8Ω load, 0dB gain setting                                                                                         | 2.6    |                       | V <sub>P-P</sub> |  |

| THD+N              | Total Harmonic Distortion + Noise                    | f <sub>OUT</sub> = 1kHz, P <sub>OUT</sub> = 400mW                                                                 | 0.16   |                       | %                |  |

| P <sub>OLS</sub>   | Loudspeaker Amplifier Output Power                   | THD = 1%, f <sub>OUT</sub> = 1kHz                                                                                 | 1.1    |                       | W                |  |

| PSRR               | Power Supply Rejection Ratio (Loudspeaker Amplifier) | $C_B = 1.0 \mu F$ $V_{RIPPLE} = 200 m V_{PP}$ $f_{RIPPLE} = 217 H z$                                              | 56     |                       | dB               |  |

| SNR (Voice)        | Signal-to-Noise Ratio of Voice                       | Signal = V <sub>O</sub> at 0dBFS, f = 1kHz<br>Noise = digital zero, A-weighted<br>0dB gain setting <sup>(6)</sup> |        |                       |                  |  |

| J ( V 0.00)        | Channel (Loudspeaker Amplifier)                      | f <sub>MCLK</sub> = 12.288MHz, PLL disabled                                                                       | 70     |                       | dB               |  |

|                    |                                                      | f <sub>MCLK</sub> = 12MHz, PLL active                                                                             | 69     |                       | dB               |  |

| SNR (Music)        | Signal-to-Noise Ratio of Music                       | Signal = V <sub>O</sub> at 0dBFS, f = 1kHz<br>Noise = digital zero, A-weighted<br>0dB gain setting <sup>(6)</sup> |        |                       |                  |  |

| J. 11 ( (WIGGIO)   | Channel (Loudspeaker Amplifier)                      | f <sub>MCLK</sub> = 12.288MHz, PLL disabled                                                                       | 74     |                       | dB               |  |

|                    |                                                      | f <sub>MCLK</sub> = 12MHz, PLL active                                                                             | 73     |                       | dB               |  |

<sup>(1)</sup> Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional but do not ensure specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which ensure specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not ensured for parameters where no limit is given, however, the typical value is a good indication of device performance.

Product Folder Links: 1 M4931

8

<sup>(2)</sup> All voltages are measured with respect to the relevant GND pin unless otherwise specified. All grounds should be coupled as close as possible to the device.

<sup>(3)</sup> Typicals are measured at 25°C and represent the parametric norm.

<sup>(4)</sup> Limits are ensured to TI's AOQL (Average Outgoing Quality Level).

<sup>(5)</sup> Digital shutdown current is measured with system clock set for PLL output while the PLL is disabled.

<sup>(6)</sup> Disabling or bypassing the PLL will result in an improvement in noise measurements.

Datasheet of LM4931ITL/NOPB - IC AUDIO SUBSYSTEM 1.1W D 42BGA

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

LM4931

www.ti.com

SNAS251E - APRIL 2004-REVISED MAY 2013

# Electrical Characteristics DV<sub>DD</sub> = 3.3V, AV<sub>DD</sub> = 5V, R<sub>LHP</sub> = 32 $\Omega$ , R<sub>LHF</sub> = 8 $\Omega^{(1)(2)}$ (continued)

| Symbol                 | Parameter                                               | Conditions                                                                                                               | LM4931                                      |    | Units            |

|------------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----|------------------|

| -                      |                                                         |                                                                                                                          | Typical <sup>(3</sup> Limits <sup>(4)</sup> |    | (Limits)         |

|                        |                                                         | A-Weighted filter, V <sub>IN</sub> = digital zero <sup>(6)</sup>                                                         |                                             |    |                  |

| e <sub>N</sub> (Music) | Output Noise                                            | f <sub>MCLK</sub> = 12.288MHz, PLL disabled                                                                              | 250                                         |    | μV               |

|                        |                                                         | f <sub>MCLK</sub> = 12MHz, PLL active                                                                                    | 320                                         |    | μV               |

| V <sub>os</sub>        | Offset Voltage                                          |                                                                                                                          | 10                                          |    | mV               |

|                        | Volume Control Range (Loudspeaker                       | Minimum Gain                                                                                                             | -34.5                                       |    | dB               |

| VCR                    | Amplifier)                                              | Maximum Gain                                                                                                             | 12                                          |    | dB               |

| SS                     | Volume Control Step Size                                |                                                                                                                          | 1.5                                         |    | dB               |

| Headphone A            | mplifier                                                |                                                                                                                          |                                             |    |                  |

| V <sub>FS</sub>        | Full-Scale Output Voltage<br>(Headphone Amplifier)      | 32Ω stereo load, 0dB gain setting                                                                                        | 2.6                                         |    | V <sub>P-P</sub> |

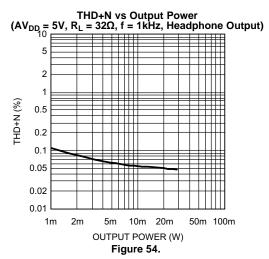

| THD+N                  | Total Harmonic Distortion + Noise (Headphone Amplifier) | $f_{IN}$ = 1kHz, $P_{OUT}$ = 7.5mW<br>32 $\Omega$ stereo load                                                            | 0.05                                        |    | %                |

| P <sub>OHP</sub>       | Output Power (Headphone Amplifier)                      | THD = 0.5%, f <sub>OUT</sub> = 1kHz                                                                                      | 26                                          | 20 | mW (min          |

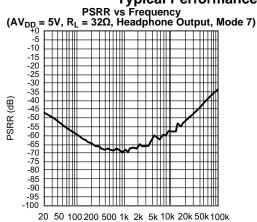

| PSRR                   | Power Supply Rejection Ratio (Headphone Amplifier)      | $C_B = 1.0 \mu F$<br>$V_{RIPPLE} = 200 m V_{PP}$<br>$f_{RIPPLE} = 217 H z$                                               | 70                                          |    | dB               |

| SNR (Voice)            | Signal-to-Noise Ratio of Voice                          | Signal = $V_O$ at f = 1kHz and 1% THD+N,<br>Noise = digital zero, A-weighted<br>0dB gain setting <sup>(6)</sup>          |                                             |    |                  |

| Sivit (Voice)          | Channel (Headphone Amplifier)                           | f <sub>MCLK</sub> = 12.288MHz, PLL disabled                                                                              | 75                                          |    | dB               |

|                        |                                                         | f <sub>MCLK</sub> = 12MHz, PLL active                                                                                    | 73                                          |    | dB               |

| SNR (Music)            | Signal-to-Noise Ratio of Music                          | Signal = V <sub>O</sub> at f = 1kHz and 1% THD+N,<br>Noise = digital zero, A-weighted<br>0dB gain setting <sup>(7)</sup> |                                             |    |                  |

| OIVIT (Music)          | Channel (Headphone Amplifier)                           | f <sub>MCLK</sub> = 12.288MHz, PLL disabled                                                                              | 86                                          |    | dB               |

|                        |                                                         | f <sub>MCLK</sub> = 12MHz, PLL active                                                                                    | 82                                          |    | dB               |

| X <sub>TALK</sub>      | Stereo Channel-to-Channel Crosstalk                     | $f_S = 48kHz$<br>$f_{IN} = 1kHz$ sinewave at -3dBFS                                                                      | 62                                          |    | dB               |

| ΔA <sub>CH-CH</sub>    | Stereo Channel-to-Channel Gain<br>Mismatch              | A Waighted filter                                                                                                        | 0.3                                         |    | dB               |

|                        |                                                         | A-Weighted filter V <sub>IN</sub> = digital zero <sup>(7)</sup>                                                          |                                             |    |                  |

| e <sub>N</sub> (Music) | Output Noise                                            | f <sub>MCLK</sub> = 12.288MHz, PLL disabled                                                                              | 45                                          |    | μV               |

|                        |                                                         | f <sub>MCLK</sub> = 12MHz, PLL active                                                                                    | 70                                          |    | μV               |

| VOD                    | Volume Control Range (Headphone                         | Minimum Gain                                                                                                             | -46.5                                       |    | dB               |

| VCR                    | Amplifier)                                              | Maximum Gain                                                                                                             | 0                                           |    | dB               |

| SS                     | Volume Control Step Size<br>(Headphone Amplifier)       |                                                                                                                          | 1.5                                         |    | dB               |

| Microphone A           | mplifier                                                |                                                                                                                          |                                             |    |                  |

| V <sub>BIAS</sub>      | Mic Bias Voltage                                        |                                                                                                                          | 2                                           |    | V                |

| GCR                    | Gain Control Range (Microphone Amplifier)               | Minimum Gain  Maximum Gain                                                                                               | 6<br>36                                     |    | dB<br>dB         |

| SS                     | Gain Control Step Size                                  |                                                                                                                          | 2                                           |    | dB               |

|                        | '                                                       | oice clock and 8kHz sampling frequency                                                                                   | 1                                           | 1  | -                |

| R <sub>VDAC</sub>      | Voice DAC Ripple                                        | 300Hz - 3.3kHz through headphone output                                                                                  | +/-0.15                                     |    | dB               |

|                        | ''                                                      | 0 1                                                                                                                      |                                             |    | dB               |

| R <sub>VADC</sub>      | Voice ADC Ripple                                        | 300Hz - 3.3kHz through headphone output                                                                                  | +/-0.25                                     |    | uв               |

Product Folder Links: LM4931

(7) Disabling or bypassing the PLL will result in an improvement in noise measurements.

Submit Documentation Feedback

Datasheet of LM4931ITL/NOPB - IC AUDIO SUBSYSTEM 1.1W D 42BGA Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

LM4931

SNAS251E -APRIL 2004-REVISED MAY 2013

www.ti.com

# Electrical Characteristics DV<sub>DD</sub> = 3.3V, AV<sub>DD</sub> = 5V, R<sub>LHP</sub> = 32 $\Omega$ , R<sub>LHF</sub> = 8 $\Omega$ <sup>(1)(2)</sup> (continued)

The following specifications apply for the circuit shown in Figure 1, unless otherwise specified. Limits apply for  $T_A=25^{\circ}C$ .

| Symbol                   | Parameter                            | Conditions                                                                                                                                         | LM4931                                      |          | Units                  |  |

|--------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------|------------------------|--|

|                          |                                      |                                                                                                                                                    | Typical <sup>(3</sup> Limits <sup>(4)</sup> |          | (Limits)               |  |

| SBA <sub>VDAC</sub>      | Voice DAC Stopband Attenuation       | Above 4kHz                                                                                                                                         | 72                                          |          | dB                     |  |

| UPB <sub>VADC</sub>      | Upper Passband Cutoff Frequency      | Upper – 3dB Point                                                                                                                                  | 3.47                                        |          | kHz                    |  |

| LPB <sub>VADC</sub>      | Lower Passband Cutoff Frequency      | Lower – 3dB Point                                                                                                                                  | 0.230                                       |          | kHz                    |  |

| SBA <sub>VADC</sub>      | Voice ADC Stopband Attenuation       | Above 4kHz                                                                                                                                         | 65                                          |          | dB                     |  |

| SBA <sub>NOTCH</sub>     | Voice ADC Notch Attenuation          | Centered on 55Hz, figure gives worst case attenuation for 50Hz & 60Hz                                                                              | 58                                          |          | dB                     |  |

| SNR (Voice)              | Signal-to-Noise Ratio of Voice       | Signal = V <sub>O</sub> at f = 1kHz and 1% THD+N,<br>MIC_P, MIC_N terminated to ground,<br>A-weighted, 36dB MIC Preamp gain setting <sup>(7)</sup> |                                             |          |                        |  |

| (,                       | Channel (Voice ADC path)             | f <sub>MCLK</sub> = 12.288MHz, PLL disabled                                                                                                        | 83                                          |          | dB                     |  |

|                          |                                      | f <sub>MCLK</sub> = 12MHz, PLL active                                                                                                              | 81                                          |          | dB                     |  |

| CTD                      | Oids Tarra Darras                    | Minimum                                                                                                                                            | -30                                         |          | dB                     |  |

| STR                      | Side Tone Range                      | Maximum                                                                                                                                            | 0                                           |          | dB                     |  |

| SS                       | Side Tone Step Size                  |                                                                                                                                                    | 3                                           |          | dB                     |  |

| Audio DAC (T             | ypical numbers are with 6.144MHz au  | dio clock and 48kHz sampling frequency)                                                                                                            |                                             | <u></u>  |                        |  |

| R <sub>DAC</sub>         | Audio DAC Ripple                     | 20Hz – 20kHz through headphone output                                                                                                              | +/- 0.1                                     |          | dB                     |  |

| PB <sub>DAC</sub>        | Audio DAC Passband width             | -3dB point                                                                                                                                         | 22.7                                        |          | kHz                    |  |

| SBA <sub>DAC</sub>       | Audio DAC Stop band Attenuation      | Above 24kHz                                                                                                                                        | 76                                          |          | dB                     |  |

| DR <sub>DAC</sub>        | Audio DAC Dynamic Range              | DC – 20kHz                                                                                                                                         | 97                                          |          | dB                     |  |

| SNR <sub>DAC</sub>       | Audio DAC SNR Digital Filter Section | DC – 20kHz                                                                                                                                         | 97                                          |          | dB                     |  |

| PLL                      | •                                    |                                                                                                                                                    |                                             |          |                        |  |

| f <sub>IN</sub>          | Input Frequency on MCLK pin          |                                                                                                                                                    | 12                                          | 10<br>20 | MHz (min)<br>MHz (max) |  |

| SPI/I <sup>2</sup> C     |                                      |                                                                                                                                                    |                                             |          |                        |  |

| f <sub>SPI</sub>         | Maximum SPI Frequency                |                                                                                                                                                    | 400                                         | 4000     | kHz (max)              |  |

| t <sub>SPISETD</sub>     | SPI Data Setup Time                  |                                                                                                                                                    |                                             | 100      | ns (min)               |  |

| t <sub>SPISETENB</sub>   | SPI ENB Setup Time                   |                                                                                                                                                    |                                             | 100      | ns (min)               |  |

| t <sub>SPISETHOLDD</sub> | SPI Data Hold Time                   |                                                                                                                                                    |                                             | 100      | ns (min)               |  |

| t <sub>SPIHOLDENB</sub>  | SPI ENB Hold Time                    |                                                                                                                                                    |                                             | 100      | ns (min)               |  |

| t <sub>SPICL</sub>       | SPI Clock Low Time                   |                                                                                                                                                    |                                             | 500      | ns (min)               |  |

| t <sub>SPICH</sub>       | SPI Clock High Time                  |                                                                                                                                                    |                                             | 500      | ns (min)               |  |

| t <sub>SPIT</sub>        | SPI Clock TransitionTime             |                                                                                                                                                    |                                             | 5        | ns (min)               |  |

| t <sub>CLKI2C</sub>      | I <sup>2</sup> C_CLK Frequency       |                                                                                                                                                    | 400                                         | 3400     | kHz (max)              |  |

| t <sub>I2CHOLD</sub>     | I <sup>2</sup> C_DATA Hold Time      |                                                                                                                                                    |                                             | 100      | ns (min)               |  |

| t <sub>I2CSET</sub>      | I <sup>2</sup> C_DATA Setup Time     |                                                                                                                                                    |                                             | 100      | ns (min)               |  |

| PCM/I <sup>2</sup> S     |                                      |                                                                                                                                                    | •                                           | •        |                        |  |

| f <sub>CLKPCM</sub>      | PCM_CLK Frequency                    |                                                                                                                                                    | 128                                         |          | kHz                    |  |

|                          | PCM_CLK Duty Cycle                   |                                                                                                                                                    | 50                                          | 40<br>60 | % (min)<br>% (max)     |  |

| f <sub>CLKI2S</sub>      | I <sup>2</sup> S_CLK Frequency       | I <sup>2</sup> S_RES = 0<br>I <sup>2</sup> S_RES = 1                                                                                               | 1536<br>3072                                |          | kHz                    |  |