# **Excellent Integrated System Limited**

Stocking Distributor

Click to view price, real time Inventory, Delivery & Lifecycle Information:

Micron Technology MT46H32M16LFCK-6 TR

For any questions, you can email us directly: <u>sales@integrated-circuit.com</u>

TN-46-16: 512Mb Mobile DDR: 95nm to 78nm Introduction

# Technical Note

# 512Mb Mobile DDR: 95nm to 78nm Product Transition Guide

### Introduction

This document describes critical product differences associated with the 512Mb Mobile (LP) DDR SDRAM product as it transitions from 95nm process technology to 78nm process technology. Micron makes every effort to ensure that new replacement products have full functional compatibility with previous products. This is accomplished through design, ATE characterization, and target system validation when possible. It is therefore unlikely that a system that has been designed with a Micron LP DDR SDRAM product will have any problems with a Micron replacement product. Micron does recommend, however, that the target system design be fully evaluated with the final version of the new product prior to conversion.

### **Part Number Transition**

Examples of replacement part numbers are shown in Table 1. These numbers are reflected in the data sheet for the replacement product.

| 95nm Part Number     | 78nm Part Number      |

|----------------------|-----------------------|

| MT46H16M32LFCM-6     | MT46H16M32LFCM-6:B    |

| MT46H16M32LFCM-6 IT  | MT46H16M32LFCM-6 IT:B |

| MT46H16M32LFCM-75    | MT46H16M32LFCM-6:B    |

| MT46H16M32LFCM-75 IT | MT46H16M32LFCM-6 IT:B |

| MT46H32M16LFCK-6     | MT46H32M16LFBF-6:B    |

| MT46H32M16LFCK-6 IT  | MT46H32M16LFBF-6 IT:B |

| MT46H32M16LFCK-75    | MT46H32M16LFBF-6:B    |

| MT46H32M16LFCK-75 IT | MT46H32M16LFBF-6 IT:B |

#### Table 1: Part Number Replacement Examples

# **Status Read Register for 78nm Product**

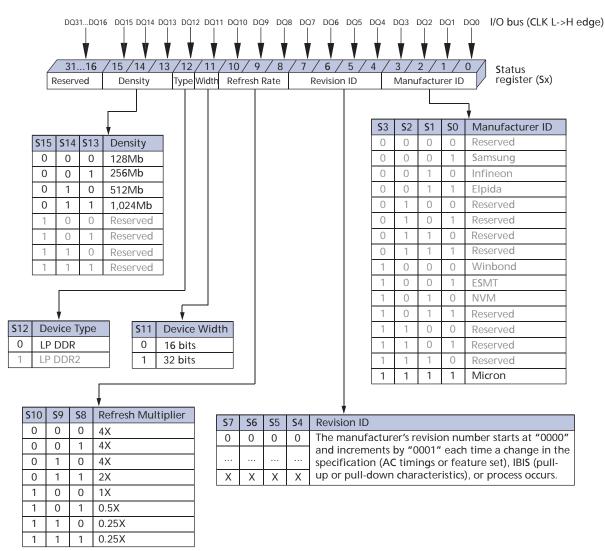

The status read register (SRR) has been added to the 78nm product. It is used to read the manufacturer ID, revision ID, refresh multiplier, width, type, and density of the Mobile SDRAM, as shown in Figure 1 on page 2. The information made available from this read-only register can assist the component package manufacturer. It can also be useful for product operation in the target application. The SRR is read via the LOAD MODE REGISTER command with BA0 = 1 and BA1 = 0. Consult the 78nm product data sheet for a full description of the SRR operation.

PDF: 09005aef82dfb176 / Source: 09005aef82dfb194 tn4616\_512\_mddr\_95\_to\_78nm\_t37\_47m.fm - Rev. B 9/07 EN

1

Micron Technology, Inc., reserves the right to change products or specifications without notice. ©2007 Micron Technology, Inc. All rights reserved.

Products and specifications discussed herein are for evaluation and reference purposes only and are subject to change by Micron without notice. Products are only warranted by Micron to meet Micron's production data sheet specifications. All information discussed herein is provided on an "as is" basis, without warranties of any kind.

# TN-46-16: 512Mb Mobile DDR: 95nm to 78nm AC Timing and DC Specification Differences

#### Figure 1: Status Read Register

# **AC Timing and DC Specification Differences**

The 78nm product supports the same speed grades as the 95nm product and will meet or exceed all timing parameters. The 78nm product also meets or exceeds all JEDECstandard LP DDR I/O level parameters as does the 95nm product.

Some DC specifications may vary between the 95nm and 78nm products. Consult the product data sheets for specific values.

#### TN-46-16: 512Mb Mobile DDR: 95nm to 78nm Package Differences

# Package Differences

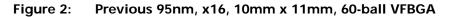

The 95nm, x16 and x32 products use SAC305 package solder ball composition, as shown in Figure 2.

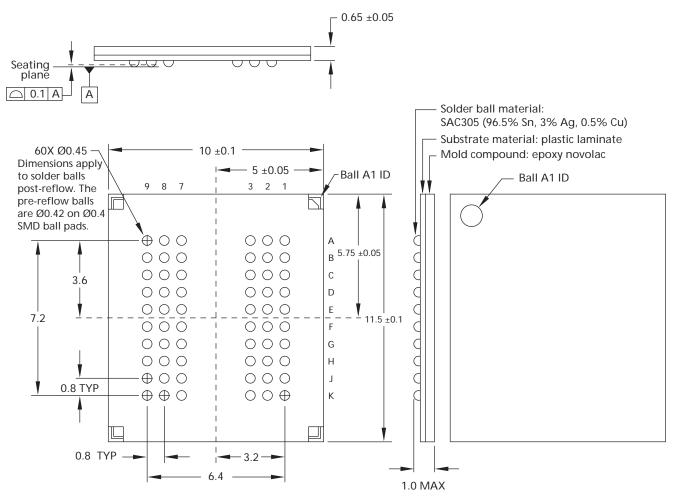

Both the x16 (60-ball) and the x32 (90-ball) packages for the 78nm product use SAC105 solder ball composition. This aligns with the industry trend toward SAC105 composition for enhanced drop test performance. The surface mount conditions for SAC105 are the same as for SAC305.

In addition, the 78nm, x16 product offers a smaller, 8mm x 9mm package outline to conserve application board space, as shown in Figure 3 on page 4. The ball assignments for both 78nm packages are JEDEC compliant.

Notes: 1. Dimensions are in millimeters.

PDF: 09005aef82dfb176 / Source: 09005aef82dfb194 tn4616\_512\_mddr\_95\_to\_78nm\_t37\_47m.fm - Rev. B 9/07 EN

#### TN-46-16: 512Mb Mobile DDR: 95nm to 78nm Die Bond Pad Order Changes

Figure 3: New 78nm, x16, 8 x 9mm, 60-ball VFBGA

Notes: 1. Dimensions are in millimeters.

# **Die Bond Pad Order Changes**

The 78nm, JEDEC-standard bond pad order is noticeably different from the 95nm bond pad order. An example of the differences for the x16 double-sided configuration is shown in Table 2 on page 5.

The JEDEC pad ordering guidelines do not specify exact placement requirements. Therefore, they do not guarantee bonding compatibility among vendors. Compatibility can be verified by direct comparison of die data sheet bond pad information.

### TN-46-16: 512Mb Mobile DDR: 95nm to 78nm **Die Bond Pad Order Changes**

#### Bond Pad Order Comparison<sup>1</sup> Table 2:

| Vdd        | Vdd             | V | SS         |          |

|------------|-----------------|---|------------|----------|

| Vss        | Vss             | V | DD         | ١        |

| VDD        | TQ              |   | ST         |          |

| Vss        | VDDQ            |   | jh-Z       | V        |

| VDD        | VssQ            |   | SS         | -<br>\   |

| BOND OPT   | VDDQ            |   | D_OPT      | V        |

| Vss        | VssQ            |   | DD         | v        |

| CS#        | VDD             |   | 4          | v        |

| A0         | Vss             |   | 15         | 1        |

| A1         | DQ15            |   | 16         | D        |

| A2         | DQ14            |   | 7          | D        |

| A3         | VDDQ            |   | \8         | D        |

| A4         | VssQ            |   | 19         | D        |

| A5         | DQ13            |   | 11         | 1        |

| A6         | DQ12            |   | 12         | v        |

| CKE        | DQ12<br>DQ11    |   | DD         | D        |

| CAS#       | DQ10            |   | ŚŚŚ        | D        |

| RAS#       | VDDQ            |   | KE         | [        |

| VDD        | VBDQ            |   | E#         | י<br>[   |

| VDD        | DQ9             |   | L#<br>\\$# |          |

| BA1        | DQ9<br>DQ8      |   | \S#        | <u>۷</u> |

|            | UDQS            |   |            | U        |

| BA0<br>WE# |                 |   | S#         |          |

|            | UDM             |   | A1         | ι        |

| A7         | VDD<br>BOND OPT |   | A0         |          |

| A8         | _               |   | )/AP       |          |

| A9         | Vss             |   | 0          | (        |

| A10        | Vss             |   | 1          |          |

| A11        | CK#             |   | 2          |          |

| A12        | СК              |   | \3         |          |

| Vss        | VDD             |   | DD         |          |

| VDD        | Vss             |   | SS         | L        |

| Vss        | CK#             |   | DD         | \        |

| VDD        | CK              | V | SS         | <u>۷</u> |

| High-Z     | VDD             |   |            | ]        |

| Vss        | Vss             |   |            | ]        |

| VDD        | VDD             |   |            | ]        |

|            | LDM             |   |            | 1        |

|            | LDQS            |   |            | V        |

|            | DQ7             |   |            | \        |

|            | DQ6             |   |            | [        |

|            | DQ5             |   |            | [        |

|            | DQ4             |   |            | [        |

|            | DQ3             |   |            | [        |

|            | DQ2             |   |            | \        |

|            | DQ1             |   |            | V        |

|            | DQ0             |   |            | V        |

|            | Vss             |   |            | \        |

|            | VDD             |   |            | 1        |

|            | VssQ            |   |            | V        |

|            | VddQ            |   |            | 1        |

|            | VssQ            |   |            |          |

|            | VddQ            |   |            |          |

|            | TEST            |   |            |          |

|            | High-Z          |   |            |          |

|            | Vice            |   |            |          |

# ded x16

Notes:

1. Blue cells indicate bond pad order differences.

Vss

For high-speed applications that use the single-sided configuration, special bonding recommendations are provided in the part-specific die data sheet.

#### TN-46-16: 512Mb Mobile DDR: 95nm to 78nm Summary

# Summary

Micron periodically offers product performance improvements through process node migration. This is the case with the product transition from 95nm to 78nm. Designers should consult product data sheets for detailed information on product differences before proceeding with product transitions.

8000 S. Federal Way, P.O. Box 6, Boise, ID 83707-0006, Tel: 208-368-3900 prodmktg@micron.com www.micron.com Customer Comment Line: 800-932-4992 Micron, the M logo, and the Micron logo are trademarks of Micron Technology, Inc. All other trademarks are the property of their respective owners.