# **Excellent Integrated System Limited**

Stocking Distributor

Click to view price, real time Inventory, Delivery & Lifecycle Information:

Intersil ISL9216IRZ

For any questions, you can email us directly: <a href="mailto:sales@integrated-circuit.com">sales@integrated-circuit.com</a>

Datasheet of ISL9216IRZ - IC MULTI-CELL LI-ION PROT 32-QFN

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

ISL9216, ISL9217

Data Sheet November 2, 2007 FN6488.1

### 8 to 12 Cell Li-Ion Battery Overcurrent Protection and Analog Front End Chip Set

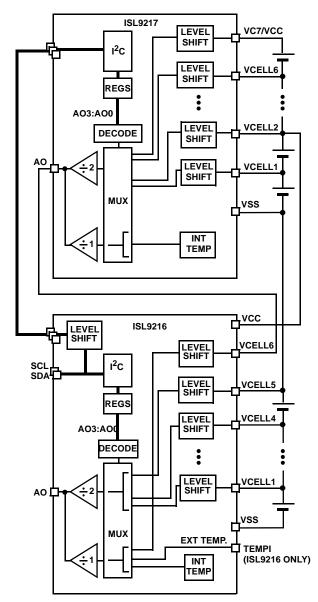

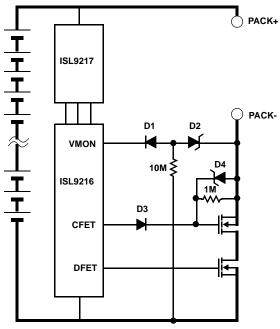

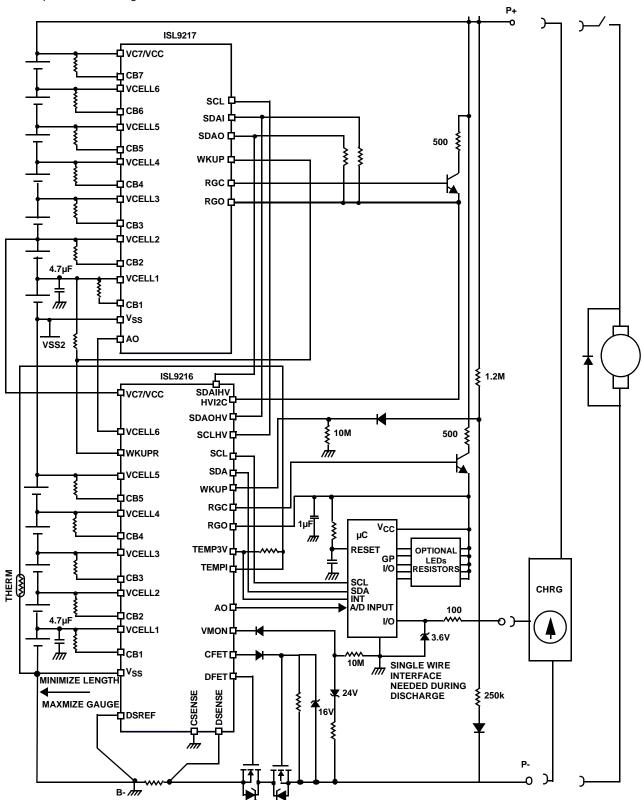

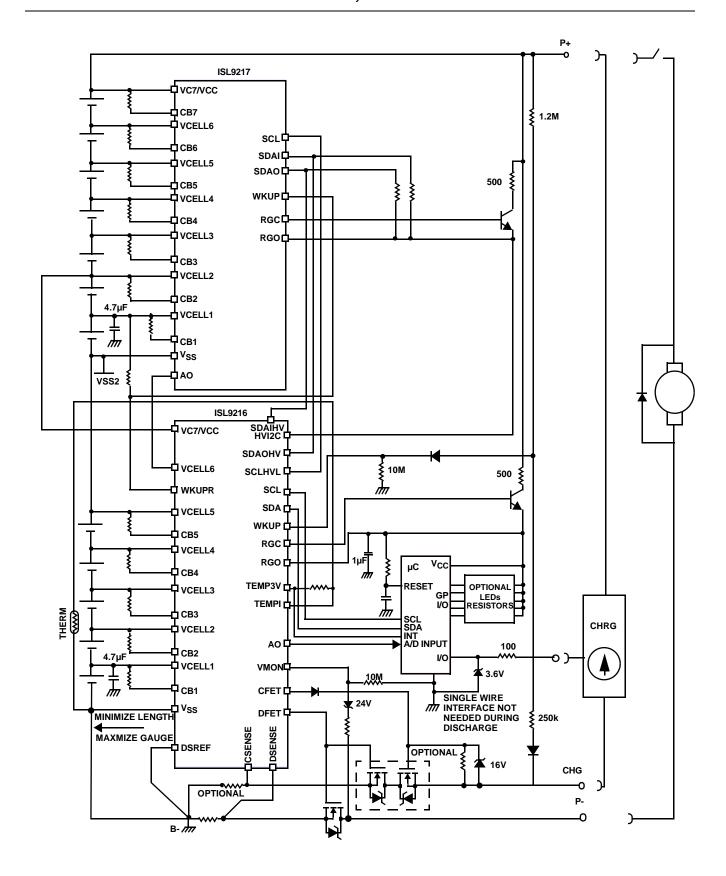

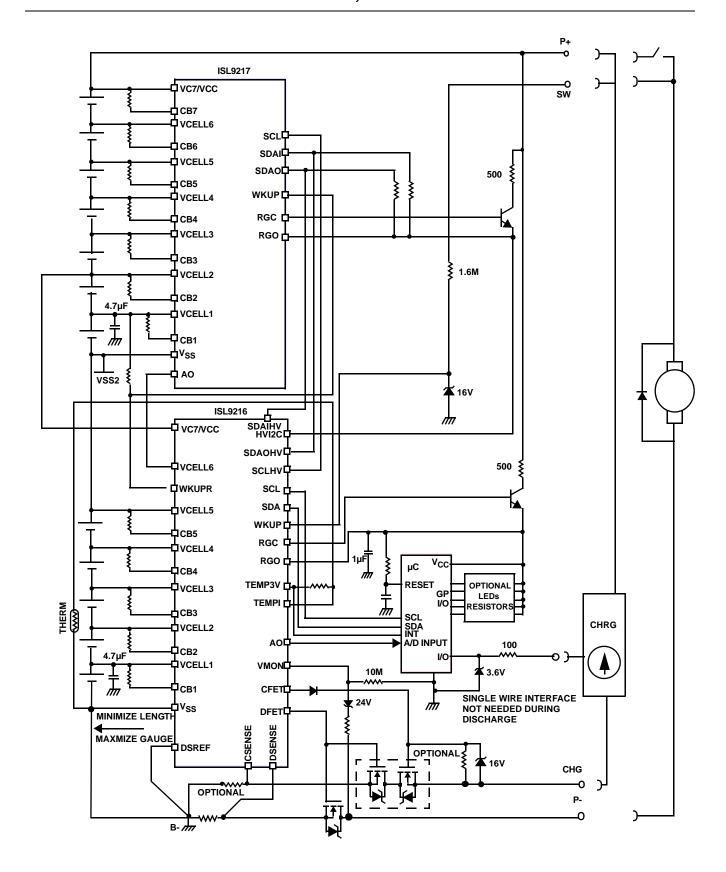

The ISL9216 and ISL9217 chipset provides overcurrent protection and voltage monitoring for multi-cell li-ion battery packs consisting of 8 to 12 cells. When used together, these devices provide integrated overcurrent protection circuitry, short circuit protection, an internal voltage regulator, internal cell balancing switches, cell voltage level shifters, and drive circuitry for external FET devices that control pack charge and discharge. Level shifting of the analog output voltage from the upper cells and communication between the chips is handled automatically.

Overcurrent and short circuit thresholds reside in internal RAM registers and are selected independently via software using an I<sup>2</sup>C serial interface. Detection and time-out delays can be individually varied using internal registers. Using an internal analog multiplexer, the device provides monitoring of cell voltage by a separate microcontroller with A/D converter. Software on this microcontroller implements all battery control functionality, except for overcurrent and short circuit shutdown.

### **Applications**

- Power Tools

- · Battery Backup Systems

- E-bikes

- · Portable Test Equipment

- Medical Systems

- Hybrid Vehicle

- Military Electronics

### **Ordering Information**

| PART NUMBER<br>(Note) | PART<br>MARKING | PACKAGE<br>(Pb-Free) | PKG.<br>DWG.# |

|-----------------------|-----------------|----------------------|---------------|

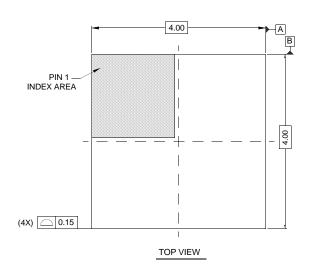

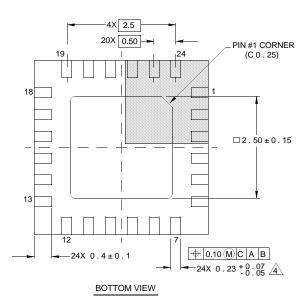

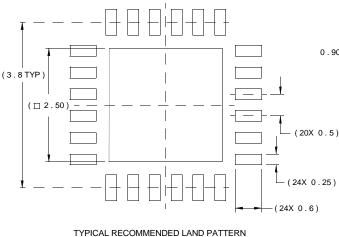

| ISL9216IRZ*           | ISL9216 IRZ     | 32 Ld 5x5 QFN        | L32.5x5B      |

| ISL9217IRZ*           | 921 7IRZ        | 24 Ld 4x4 QFN        | L24.4x4D      |

\*Add "-T" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate PLUS ANNEAL - e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

#### **Features**

- Software selectable overcurrent protection levels and variable protect detection/release times

- 4 Discharge overcurrent thresholds

- 4 Short circuit thresholds

- 4 Charge overcurrent thresholds

- 8 Overcurrent delay times (Charge)

- 8 Overcurrent delay times (Discharge)

- 2 Short circuit delay times (Discharge)

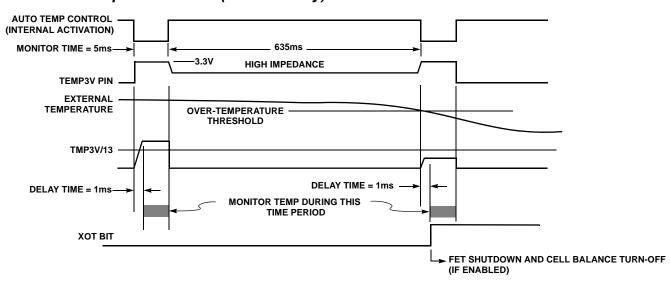

- Automatic FET turn-off and cell balance disable on reaching external (battery) or internal (IC) temperature limit

- Automatic over-ride of cell balance on reaching internal (IC) temperature limit

- · Fast short circuit pack shutdown

- Can use current sense resistor, FET r<sub>DS(ON)</sub>, or Sense FET for overcurrent detection

- · Four battery backed software controlled flags

- · Allows three different FET controls:

- Back-to-back N-Channel FETs for charge and discharge control

- Single N-Channel FET for discharge control

- N-Channel FET for discharge, with separate, optional (smaller) back-to-back FET for charge

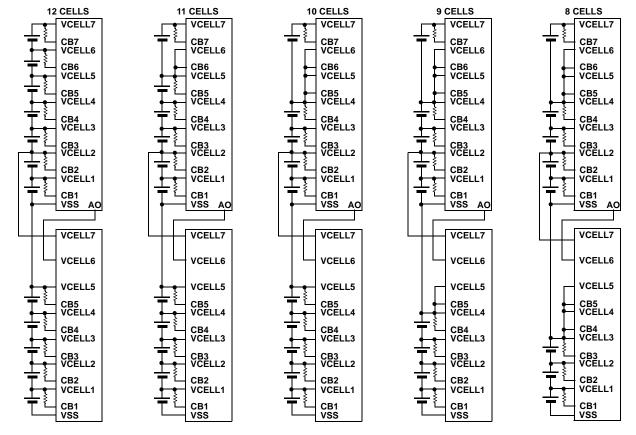

- · Chips cascade for packs of 8 to 12 cells

- Integrated charge/discharge FET drive circuitry with 200µA (typ) turn on current and 150mA (typ) discharge FET turn off current

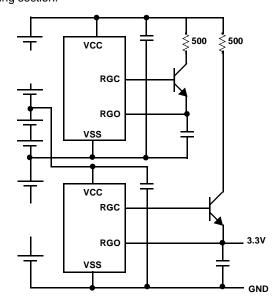

- 10% accurate 3.3V voltage regulator (35mA out with external NPN transistor having current gain of 70)

- · Cell voltage monitor accurate to within 25mV

- Monitored cell voltage output stable in 100µs

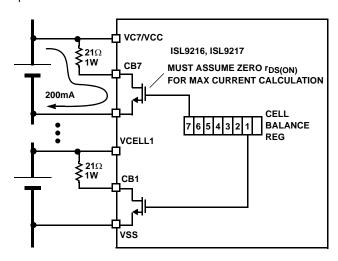

- Internal cell balancing FETs handle up to 200mA of balancing current for each cell (with the number of cells being balanced limited by the maximum power dissipation of 400mW)

- Simple I<sup>2</sup>C host interface

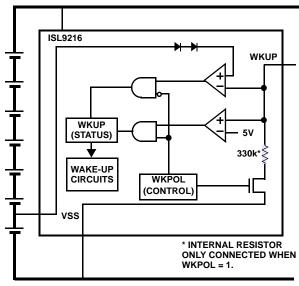

- Sleep operation with programmable negative edge or positive edge wake-up

- <10µA sleep mode</li>

- Pb-free (RoHS compliant)

Datasheet of ISL9216IRZ - IC MULTI-CELL LI-ION PROT 32-QFN

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

## ISL9216, ISL9217

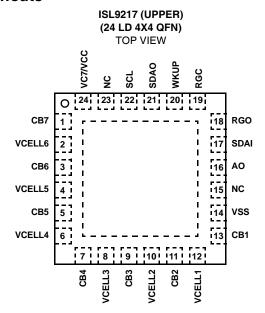

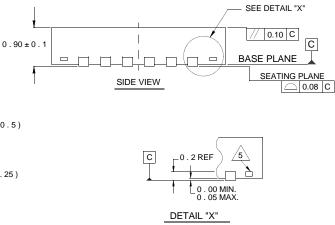

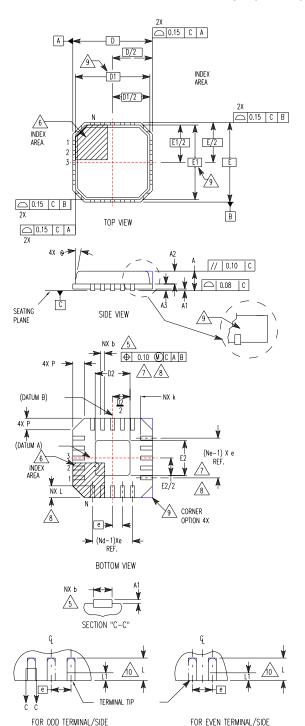

#### **Pinouts**

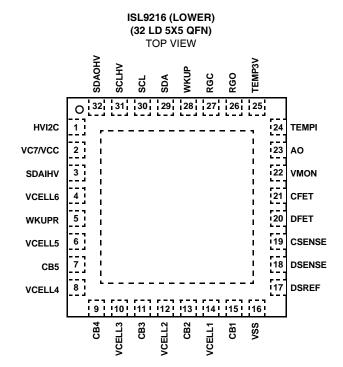

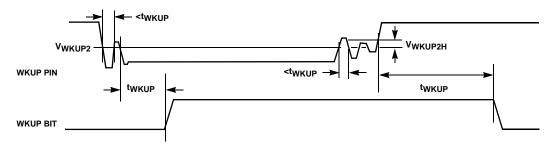

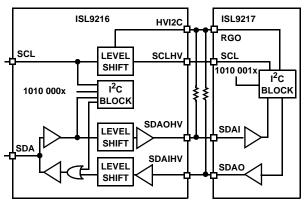

### **Functional Diagram**

# **Distributor of Intersil : Excellent Integrated System Limited**Datasheet of ISL9216IRZ - IC MULTI-CELL LI-ION PROT 32-QFN

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

## ISL9216, ISL9217

## Pin Descriptions

| SYMBOL  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VC7/VCC | <b>Battery Cell 7 Voltage Input/VCC Supply.</b> This pin is used to monitor the voltage of this battery cell externally at pin AO. This pin also provides the operating voltage for the IC circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VCELLN  | <b>Battery Cell N Voltage Input.</b> This pin is used to monitor the voltage of this battery cell externally at pin AO. VCELLN connects to the positive terminal of CELLN and the negative terminal of CELLN+1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CBN     | <b>Cell Balancing FET Control Output N.</b> This internal FET diverts a fraction of the current around a cell while the cell is being charged or adds to the current pulled from a cell during discharge in order to perform a cell voltage balancing operation. This function is generally used to reduce the voltage on an individual cell relative to other cells in the pack. The cell balancing FETs are turned on or off by an external controller.                                                                                                                                                                                                                                              |

| VSS     | <b>Ground</b> . This pin connects to the most negative terminal in the battery string.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DSREF   | <b>Discharge Current Sense Reference (ISL9216 only).</b> This input provides a separate reference point for the charge and discharge current monitoring circuits. with a separate reference connection, it is possible to minimize errors that result from voltage drops on the ground lead when the load is drawing large currents. If a separate reference is not necessary, connect this pin to VSS.                                                                                                                                                                                                                                                                                                |

| DSENSE  | <b>Discharge Current Sense Monitor (ISL9216 only).</b> This input monitors the discharge current by monitoring a voltage. It can monitor the voltage across a sense resistor, or the voltage across the DFET, or by using a FET with a current sense pin. The voltage on this pin is measured with reference to DSREF.                                                                                                                                                                                                                                                                                                                                                                                 |

| CSENSE  | Charge Current Sense Monitor (ISL9216 only). This input monitors the charge current by monitoring a voltage. It can monitor the voltage across a sense resistor, or the voltage across the CFET, or by using a FET with a current sense pin. The voltage on this pin is measured with reference to VSS.                                                                                                                                                                                                                                                                                                                                                                                                |

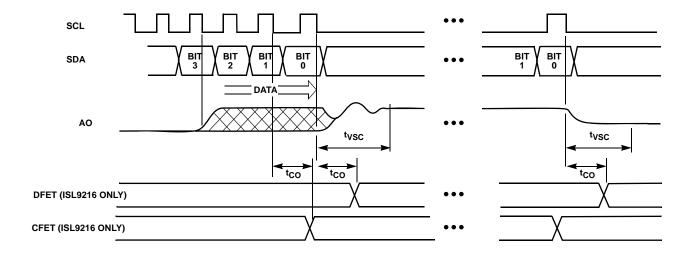

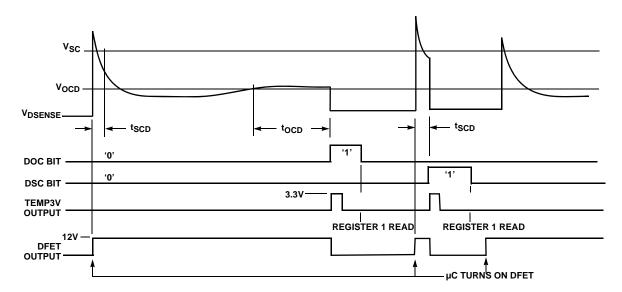

| DFET    | <b>Discharge FET Control (ISL9216 only).</b> The ISL9216 controls the gate of a discharge FET through this pin. The power FET is a N-Channel device. The FET is turned on only by the microcontroller. The FET can be turned off by the microcontroller, but the ISL9216 can also turn off the FET in the event of an overcurrent or short circuit condition. If the microcontroller detects an undervoltage condition on any of the battery cells, it will turn off the FET off by controlling this output with a control bit.                                                                                                                                                                        |

| CFET    | Charge FET Control (ISL9216 only). The ISL9216 controls the gate of a charge FET through this pin. The power FET is a N-Channel device. The FET is turned on only by the microcontroller. The FET can be turned off by the microcontroller, but the ISL9216 can also turn off the FET in the event of an overcurrent condition. If the microcontroller detects an overvoltage condition on any of the battery cells, it will turn off the FET off by controlling this output with a control bit.                                                                                                                                                                                                       |

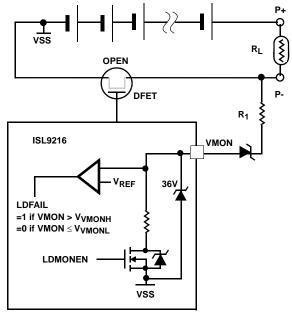

| VMON    | <b>Discharge Load Monitoring (ISL9216 only).</b> In the event of an overcurrent or short circuit condition, the microcontroller can enable a series diode and resistor that connects between the VMON pin and VSS. When FETs open because of an overcurrent or short circuit condition, and the load remains, the voltage at VMON will be near the VCC voltage. When the load is released, the voltage at VMON drops below a threshold indicating that the overcurrent or short circuit condition is resolved. At this point, the LDFAIL flag is cleared and operation can resume.                                                                                                                     |

| AO      | Analog Multiplexer Output. The analog output pin is used by an external microcontroller to monitor the cell voltages and temperature sensor voltages. The microcontroller selects the specific voltage being applied to the output by writing to a control register.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

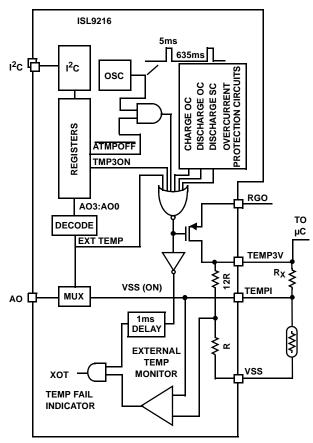

| TEMP3V  | Temperature Monitor Output Control (ISL9216 only). This pin outputs a voltage to be used in a divider that consists of a fixed resistor and a thermistor. The thermistor is located in close proximity to the cells. The TEMP3V output is connected internally to the RGO voltage through a PMOS switch only during a measurement of the temperature, otherwise the output is off. The TEMP3V output can be turned on continuously with a special control bit.  Microcontroller Wake-up Control. This pin is also turned on when any of the DSC, DOC, or COC bits are set. This can be used to wake-up a sleeping microcontroller to respond to overcurrent conditions with its own control mechanism. |

| TEMPI   | <b>Temperature Monitor Input (ISL9216 only).</b> This pin inputs the voltage across a thermistor to determine the temperature of the cells. When this input voltage drops below TEMP3V/13, an external over-temperature condition exists. The TEMPI voltage is also fed to the AO output pin through an analog multiplexer so the temperature of the cells can be monitored by the microcontroller.                                                                                                                                                                                                                                                                                                    |

| RGO     | Regulated Output Voltage. This pin connects to the emitter of an external NPN transistor and works in conjunction with the RGC pin to provide a regulated 3.3V. The voltage at this pin provides feedback for the regulator and power for many of the ISL9216 and ISL9217 internal circuits. For the ISL9216, this output also provides the 3.3V output voltage for the microcontroller and other external circuits.                                                                                                                                                                                                                                                                                   |

| RGC     | Regulated Output Control. This pin connects to the base of an external NPN transistor and works in conjunction with the RGO pin to provide a regulated 3.3V. The RGC output provides the control signal to provide the 3.3V regulated voltage on the RGO pin.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

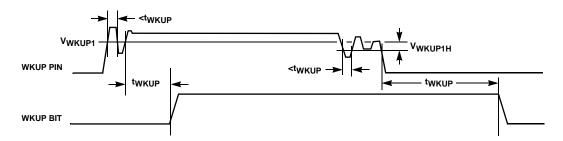

| WKUP    | <ul> <li>Wake-up Voltage. This input wakes up the part when the voltage crosses a turn-on threshold (wake-up is edge triggered) and the condition of the pin is reflected in the WKUP bit (The WKUP bit is level sensitive).</li> <li>WKPOL bit = "1": the device wakes up on the rising edge of the WKUP pin. Also, the WKUP bit is HIGH only when the WKUP pin voltage &gt; threshold.</li> <li>WKPOL bit = "0", the device wakes up on the falling edge of the WKUP pin. Also, the WKUP bit is HIGH only when the WKUP pin voltage &lt; threshold.</li> </ul>                                                                                                                                       |

Datasheet of ISL9216IRZ - IC MULTI-CELL LI-ION PROT 32-QFN

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

## ISL9216, ISL9217

## Pin Descriptions (Continued)

| SYMBOL             | DESCRIPTION                                                                                                                                                                                                                 |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WKUPR              | Wake-up Upper Device Signal (ISL9216 only). This output wakes up the ISL9217 (upper device) when the output is turned on by the microcontroller. Once the upper device is awake, this output can be turned off.             |

| SDA                | Serial Data (ISL9216 only). This is the bi-directional data line for an I <sup>2</sup> C interface.                                                                                                                         |

| SCL                | <b>Serial Clock.</b> This is the clock line for an I <sup>2</sup> C communication link.                                                                                                                                     |

| SDAI               | <b>Serial Data Input (ISL9217 only).</b> This pin is a uni-directional I <sup>2</sup> C serial data input from the ISL9216 to the cascaded ISL9217 device. This pin connects to the ISL9216 SDAOHV pin.                     |

| SDAO               | <b>Serial Data Output (ISL9217 only).</b> This pin is a uni-directional I <sup>2</sup> C serial data output to the ISL9216 from the cascaded ISL9217 device. This pin connects to the ISL9216 SDAIHV pin.                   |

| SDAIHV             | <b>Serial Data Input (ISL9216 only).</b> This pin is a uni-directional I <sup>2</sup> C serial data input from the cascaded ISL9217 device to the ISL9216. This pin connects to the ISL9217 SDAO pin.                       |

| SDAOHV             | Serial Data Output (ISL9216 only). This pin is a uni-directional serial data output from the ISL9216 to the cascaded ISL9217 device. This pin connects to the ISL9217 SDAI pin.                                             |

| SCLHV              | Serial Clock Output (ISL9216 only). This pin sends clock pulses from the lower device (ISL9216) to the upper device (ISL9217) for communication between cascaded devices                                                    |

| HVI <sup>2</sup> C | HV I <sup>2</sup> C Reference Voltage (ISL9216 only). This is a reference voltage for the ISL9216 to facilitate the communication link between cascaded devices. Tie this pin on the ISL9216 to the RGO pin of the ISL9217. |

Datasheet of ISL9216IRZ - IC MULTI-CELL LI-ION PROT 32-QFN

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

### ISL9216, ISL9217

#### **Thermal Information**

| Thermal Resistance (Typical, Notes 1, 2) | θ <sub>JA</sub> (°C/W) | $\theta_{JC}$ (°C/W) |

|------------------------------------------|------------------------|----------------------|

| 32 Ld QFN                                | 31                     | 2                    |

| 24 Ld QFN                                | 32                     | 2                    |

| Continuous Package Power Dissipation     |                        | 400mW                |

| Storage Temperature                      | <del>.</del> -         | 55 to +125°C         |

| Pb-free reflow profile                   |                        | ee link below        |

| http://www.intersil.com/pbfree/Pb-FreeR  | teflow.asp             |                      |

#### **Operating Conditions**

| Operating Temperature40°C to | +85°C   |

|------------------------------|---------|

| Operating Voltage            |         |

| VCC pin                      | 30.1V   |

| VCELL1-VSS                   | to 4.3V |

| VCELLN-(VCELLN-1)            | to 4.3V |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 2.  $\theta_{JC}$ , "case temperature" location is at the center of the exposed metal pad on the package underside. See Tech Brief TB379.

**Operating Specifications** All Specifications Apply to Both the ISL9216 and ISL9217 Separately Over the Recommended Operating Conditions, Unless Otherwise Specified.

| DESCRIPTION                                                 | SYMBOL              | TEST CONDITIONS                                                                                                                                 | MIN  | TYP  | MAX  | UNIT |

|-------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Operating Voltage                                           | V <sub>CC</sub>     |                                                                                                                                                 | 9.2  |      | 31   | V    |

| Power-up Condition 1                                        | V <sub>PORVCC</sub> | V <sub>CC</sub> voltage (Note 3)                                                                                                                |      | 4    | 9.2  | V    |

| Power-up Condition 2 Threshold                              | V <sub>POR123</sub> | V <sub>CELL1</sub> - V <sub>SS</sub> and V <sub>CELL2</sub> - V <sub>CELL1</sub> and V <sub>CELL3</sub> - V <sub>CELL2</sub> (rising) (Note 3)  | 1.1  | 1.7  | 2.3  | V    |

| Power-up Condition 2 Hysteresis                             | V <sub>PORhys</sub> | V <sub>CELL1</sub> - V <sub>SS</sub> and V <sub>CELL2</sub> - V <sub>CELL1</sub> and V <sub>CELL3</sub> - V <sub>CELL2</sub> (falling) (Note 3) |      | 70   |      | mV   |

| 3.3V Regulated Voltage                                      | V <sub>RGO</sub>    | 0μA < I <sub>RGC</sub> < 350μA                                                                                                                  | 3.0  | 3.3  | 3.6  | V    |

| 3.3VDC Voltage Regulator Control<br>Current Limit           | I <sub>RGC</sub>    | (Control current at output of RGC.<br>Recommend NPN with gain of 70+)                                                                           | 0.35 | 0.50 |      | mA   |

| V <sub>CC</sub> Supply Current                              | I <sub>VCC1</sub>   | Power-up defaults, WKUP pin = 0V.                                                                                                               |      | 400  | 510  | μA   |

| RGO Supply Current                                          | I <sub>RGO1</sub>   |                                                                                                                                                 |      | 300  | 410  | μA   |

| V <sub>CC</sub> Supply Current                              | I <sub>VCC2</sub>   | LDMONEN bit = 1, VMON floating, CFET = 1,                                                                                                       |      | 400  | 700  | μA   |

| RGO Supply Current                                          | I <sub>RGO2</sub>   | DFET = 1, WKPOL bit = 1, VWKUP = 10V, [AO3:AO0] bits = 06H.                                                                                     |      | 450  | 650  | μA   |

| V <sub>CC</sub> Supply Current                              | I <sub>VCC3</sub>   | Default register settings, except SLEEP                                                                                                         |      |      | 10   | μA   |

| RGO Supply Current                                          | I <sub>RGO3</sub>   | bit = 1. WKUP pin = VCELL1                                                                                                                      |      |      | 1    | μA   |

| VCELL Input Current - V <sub>CELL1</sub>                    | I <sub>VCELL1</sub> | AO3:AO0 = 0000H                                                                                                                                 |      |      | 14   | μA   |

| VCELL Input Current - V <sub>CELL5</sub>                    | I <sub>VCELL1</sub> | AO3:AO0 = 0000H (ISL9216 Only)                                                                                                                  |      |      | 20   | μA   |

| VCELL Input Current - V <sub>CELLN</sub>                    | I <sub>VCELLN</sub> | AO3:AO0 = 0000H                                                                                                                                 |      |      | 10   | μA   |

| OVERCURRENT/SHORT CIRCUIT PRO                               | TECTION S           | SPECIFICATIONS (ISL9216 only)                                                                                                                   |      |      |      |      |

| Overcurrent Detection Threshold                             | V <sub>OCD</sub>    | V <sub>OCD</sub> = 0.10V (OCDV1, OCDV0 = 0, 0)                                                                                                  | 80.0 | 0.10 | 0.12 | V    |

| (Discharge) Voltage Relative to DSREF (Default in Boldface) |                     | V <sub>OCD</sub> = 0.12V (OCDV1, OCDV0 = 0, 1)                                                                                                  | 0.10 | 0.12 | 0.14 | V    |

| (Detault III Boldiace)                                      |                     | V <sub>OCD</sub> = 0.14V (OCDV1, OCDV0 = 1, 0)                                                                                                  | 0.12 | 0.14 | 0.16 | V    |

|                                                             |                     | V <sub>OCD</sub> = 0.16V (OCDV1, OCDV0 = 1, 1)                                                                                                  | 0.14 | 0.16 | 0.18 | V    |

Datasheet of ISL9216IRZ - IC MULTI-CELL LI-ION PROT 32-QFN

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

## ISL9216, ISL9217

# Operating Specifications Apply to Both the ISL9216 and ISL9217 Separately Over the Recommended Operating Conditions, Unless Otherwise Specified. (Continued)

| DESCRIPTION                                                 | SYMBOL             | TEST CONDITIONS                                               | MIN   | TYP   | MAX   | UNIT |

|-------------------------------------------------------------|--------------------|---------------------------------------------------------------|-------|-------|-------|------|

| Overcurrent Detection Threshold                             | Vocc               | V <sub>OCC</sub> = 0.10V (OCCV1, OCCV0 = 0, 0)                | -0.12 | -0.10 | -0.07 | ٧    |

| (Charge) Voltage Relative to DSREF (Default in Boldface)    |                    | V <sub>OCC</sub> = 0.12V (OCCV1, OCCV0 = 0, 1)                | -0.14 | -0.12 | -0.09 | V    |

| (20.00.000                                                  |                    | V <sub>OCC</sub> = 0.14V (OCCV1, OCCV0 = 1, 0)                | -0.16 | -0.14 | -0.11 | V    |

|                                                             |                    | V <sub>OCC</sub> = 0.16V (OCCV1, OCCV0 = 1, 1)                | -0.18 | -0.16 | -0.13 | V    |

| Short Current Detection Threshold                           | V <sub>SC</sub>    | V <sub>OC</sub> = 0.20V (SCDV1, SCDV0 = 0, 0)                 | 0.15  | 0.20  | 0.25  | V    |

| (Discharge) Voltage Relative to DSREF (Default in Boldface) |                    | V <sub>OC</sub> = 0.35V (SCDV1, SCDV0 = 0, 1)                 | 0.30  | 0.35  | 0.40  | V    |

| (                                                           |                    | V <sub>OC</sub> = 0.65V (SCDV1, SCDV0 = 1, 0)                 | 0.60  | 0.65  | 0.70  | V    |

|                                                             |                    | V <sub>OC</sub> = 1.20V (SCDV1, SCDV0 = 1, 1)                 | 1.10  | 1.20  | 1.30  | V    |

| Load Monitor Input Threshold (falling edge)                 | V <sub>VMON</sub>  | LDMONEN bit = "1"                                             | 1.1   | 1.45  | 1.8   | V    |

| Load Monitor Input Threshold (hysteresis)                   | V <sub>VMONH</sub> | LDMONEN bit = "1"                                             |       | 0.25  |       | mV   |

| Load Monitor Current                                        | I <sub>VMON</sub>  |                                                               | 20    | 40    | 60    | μΑ   |

| Short Circuit Time-out                                      | t <sub>SCD</sub>   | Internal short circuit detection delay (SCLONG bit = '0')     | 90    | 190   | 290   | μs   |

|                                                             |                    | Internal short circuit detection delay (SCLONG bit = '1')     | 5     | 10    | 15    | ms   |

| Over Discharge Current Time-out (Default in Boldface)       | tocd               | t <sub>OCD</sub> = 160ms (OCDT1, OCDT0 = 0, 0 and DTDIV = 0)  | 80    | 160   | 240   | ms   |

|                                                             |                    | t <sub>OCD</sub> = 320ms (OCDT1, OCDT0 = 0, 1 and DTDIV = 0)  | 160   | 320   | 480   | ms   |

|                                                             |                    | t <sub>OCD</sub> = 640ms (OCDT1, OCDT0 = 1, 0 and DTDIV = 0)  | 320   | 640   | 960   | ms   |

|                                                             |                    | t <sub>OCD</sub> = 1280ms (OCDT1, OCDT0 = 1, 1 and DTDIV = 0) | 640   | 1280  | 1920  | ms   |

|                                                             |                    | $t_{OCD}$ = 2.5ms (OCDT1, OCDT0 = 0, 0 and DTDIV = 1)         | 1.25  | 2.50  | 3.75  | ms   |

|                                                             |                    | t <sub>OCD</sub> = 5ms (OCDT1, OCDT0 = 0, 1 and DTDIV = 1)    | 2.5   | 5     | 7.5   | ms   |

|                                                             |                    | t <sub>OCD</sub> = 10ms (OCDT1, OCDT0 = 1, 0 and DTDIV = 1)   | 5     | 10    | 15    | ms   |

|                                                             |                    | t <sub>OCD</sub> = 20ms (OCDT1, OCDT0 = 1, 1 and DTDIV = 1)   | 10    | 20    | 30    | ms   |

| Over Charge Current Time-out (Default in Boldface)          | tocc               | t <sub>OCC</sub> = 80ms (OCCT1, OCCT0 = 0, 0 and CTDIV = 0)   | 40    | 80    | 120   | ms   |

|                                                             |                    | $t_{OCC}$ = 160ms (OCCT1, OCCT0 = 0, 1 and CTDIV = 0)         | 80    | 160   | 240   | ms   |

|                                                             |                    | $t_{OCC}$ = 320ms (OCCT1, OCCT0 = 1, 0 and CTDIV = 0)         | 160   | 320   | 480   | ms   |

|                                                             |                    | t <sub>OCC</sub> = 640ms (OCCT1, OCCT0 = 1, 1 and CTDIV = 0)  | 320   | 640   | 960   | ms   |

|                                                             |                    | t <sub>OCC</sub> = 2.5ms (OCCT1, OCCT0 = 0, 0 and CTDIV = 1)  | 1.25  | 2.50  | 3.75  | ms   |

|                                                             |                    | t <sub>OCC</sub> = 5ms (OCCT1, OCCT0 = 0, 1 and CTDIV = 1)    | 2.5   | 5     | 7.5   | ms   |

|                                                             |                    | t <sub>OCC</sub> = 10ms (OCCT1, OCCT0 = 1, 0 and CTDIV = 1)   | 5     | 10    | 15    | ms   |

|                                                             |                    | t <sub>OCC</sub> = 20ms (OCCT1, OCCT0 = 1, 1 and CTDIV = 1)   | 10    | 20    | 30    | ms   |

intersil

Datasheet of ISL9216IRZ - IC MULTI-CELL LI-ION PROT 32-QFN

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

## ISL9216, ISL9217

Operating Specifications Apply to Both the ISL9216 and ISL9217 Separately Over the Recommended Operating Conditions, Unless Otherwise Specified. (Continued)

| DESCRIPTION                                                 | SYMBOL             | TEST CONDITIONS                                                                                                                         | MIN | TYP  | MAX | UNIT  |

|-------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| OVER-TEMPERATURE PROTECTION S                               | PECIFICAT          | TIONS                                                                                                                                   |     |      |     |       |

| Internal Temperature Shutdown<br>Threshold                  | T <sub>INTSD</sub> |                                                                                                                                         |     | 115  |     | °C    |

| Internal Temperature Hysteresis                             | T <sub>HYS</sub>   | Temperature drop needed to restore operation after an over-temperature shutdown.                                                        |     | 105  |     | °C    |

| Internal Over-Temperature Turn-on Delay Time                | T <sub>ITD</sub>   |                                                                                                                                         |     | 128  |     | ms    |

| External Temperature Output Current                         | I <sub>XT</sub>    | Current output capability at TEMP3V pin (ISL9216 only)                                                                                  | 1.2 |      |     | mA    |

| External Temperature Limit Threshold                        | T <sub>XTF</sub>   | Voltage at $V_{TEMPI}$ (ISL9216 only);<br>Relative to: $\frac{V_{TEMP3V}}{13}$ . (Falling edge)                                         | -20 | 0    | +20 | mV    |

| External Temperature Limit Hysteresis                       | T <sub>XTH</sub>   | Voltage at V <sub>TEMPI</sub> (ISL9216 only).                                                                                           | 60  | 110  | 160 | mV    |

| External Temperature Monitor Delay                          | <sup>t</sup> XTD   | Delay between activating the external sensor and the internal over-temp detection. (ISL9216 only)                                       |     | 1    |     | ms    |

| External Temperature Autoscan On Time                       | txtaon             | TEMP3V is ON (3.3V) (ISL9216 only)                                                                                                      |     | 5    |     | ms    |

| External Temperature Autoscan Off Time                      | tXTAOFF            | TEMP3V output is off. (ISL9216 only)                                                                                                    |     | 635  |     | ms    |

| ANALOG OUTPUT SPECIFICATIONS                                |                    |                                                                                                                                         |     |      |     |       |

| Cell Monitor Analog Output Voltage<br>Accuracy              | V <sub>AO6A</sub>  | $[V_{CELL1} - (V_{SS})]/2 - AO$<br>$[V_{CELLN} - (V_{CELLN-1})]/2 - AO$ for N = 1 to 5.<br>(ISL9216 only)                               | -25 |      | 30  | mV    |

|                                                             | V <sub>AO6B</sub>  | V <sub>CELL6</sub> - AO.<br>(ISL9216 only)                                                                                              | -42 |      | 58  | mV    |

|                                                             | V <sub>AO7A</sub>  | $[V_{CELL1} - (V_{SS})]/2 - AO$<br>$[V_{CELLN} - (V_{CELLN-1})]/2 - AO$ for N = 1 to 5.<br>(ISL9217 only)                               | -20 |      | 25  | mV    |

|                                                             | V <sub>AO7B</sub>  | $[V_{CELLN} - (V_{CELLN-1})]/2$ - AO for N = 6 to 7. (ISL9217 only)                                                                     | -32 |      | 43  | mV    |

| Cell Monitor Analog Output External<br>Temperature Accuracy | V <sub>AOXT</sub>  | External temperature monitoring accuracy.<br>Voltage error at AO when monitoring TEMPI<br>voltage (measured with TEMPI = 1V)            | -10 |      | 10  | mV    |

| Internal Temperature Monitor Output<br>Voltage Slope        | VINTMON            | Internal temperature monitor voltage change                                                                                             |     | -3.5 |     | mV/°C |

| Internal Temperature Monitor Output                         | T <sub>INT25</sub> | Output at +25°C                                                                                                                         |     | 1.31 |     | V     |

| AO Output Stabilization Time                                | tvsc               | From SCL falling edge at data bit 0 of command to AO output stable within 0.5% of final value. AO voltage steps from 0V to 2V. (Note 6) |     |      | 0.1 | ms    |

| CELL BALANCE SPECIFICATIONS                                 |                    |                                                                                                                                         |     | •    |     | ,     |

| Cell Balance Transistor r <sub>DS(ON)</sub>                 | R <sub>CB</sub>    | (Note 5)                                                                                                                                |     | 5    |     | Ω     |

| Cell Balance Transistor Current                             | I <sub>CB</sub>    |                                                                                                                                         |     |      | 200 | mA    |

Datasheet of ISL9216IRZ - IC MULTI-CELL LI-ION PROT 32-QFN

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

## ISL9216, ISL9217

Operating Specifications Apply to Both the ISL9216 and ISL9217 Separately Over the Recommended Operating Conditions, Unless Otherwise Specified. (Continued)

| DESCRIPTION                                                            | SYMBOL               | TEST CONDITIONS                                                                                                                        | MIN                      | TYP                      | MAX                      | UNIT |

|------------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|------|

| WAKE-UP/SLEEP SPECIFICATIONS                                           | l.                   |                                                                                                                                        | 1                        | 1                        |                          |      |

| Device WKUP Pin Voltage Threshold (WKUP pin active HIGH rising edge)   | V <sub>WKUP1</sub>   | WKUP pin rising edge (WKPOL = 1) Device wakes up and sets WKUP flag HIGH. (ISL9216 only)                                               | 3.5                      | 5.0                      | 6.5                      | V    |

| Device WKUP Pin Hysteresis<br>(WKUP pin active HIGH)                   | V <sub>WKUP1H</sub>  | WKUP pin falling edge hysteresis<br>(WKPOL = 1) sets WKUP flag LOW (does<br>not automatically enter sleep mode)<br>(ISL9216 only)      |                          | 100                      |                          | mV   |

| Internal Resistor on WKUP                                              | R <sub>WKUP</sub>    | Resistance from WKUP pin to VSS (WKPOL = 1) (ISL9216 only)                                                                             | 130                      | 230                      | 330                      | kΩ   |

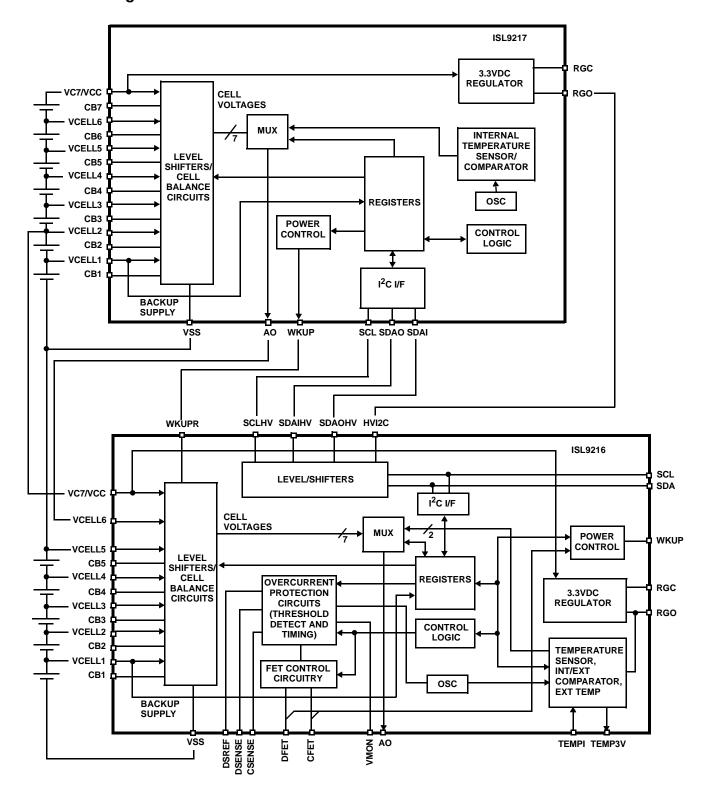

| Device WKUP Pin Voltage Threshold (WKUP pin active LOW - Falling Edge) | V <sub>WKUP2</sub>   | WKUP pin falling edge (WKPOL = 0) Device wakes up and sets WKUP flag HIGH.                                                             | V <sub>CELL1</sub> - 2.6 | V <sub>CELL1</sub> - 2.0 | V <sub>CELL1</sub> - 1.2 | V    |

| Device WKUP Pin Hysteresis<br>(WKUP pin active LOW)                    | V <sub>WKUP2H</sub>  | WKUP pin rising edge hysteresis<br>(WKPOL = 0) sets WKUP flag LOW (does<br>not automatically enter sleep mode)                         |                          | 200                      |                          | mV   |

| Device Wake-up Delay                                                   | tWKUP                | Delay after voltage on WKUP pin crosses the threshold (rising or falling) before activating the WKUP bit.                              | 20                       | 40                       | 60                       | ms   |

| FET CONTROL SPECIFICATIONS (For                                        | VCELL1, VC           | CELL2, VCELL3 voltages from 2.8V to 4.3V -                                                                                             | ISL9216 only             | )                        |                          |      |

| Control Outputs Response Time (CFET, DFET)                             | tco                  | Bit 0 to start of control signal (DFET)<br>Bit 1 to start of control signal (CFET)                                                     |                          | 1.0                      |                          | μs   |

| CFET Gate Voltage                                                      | VCFET                | No load on CFET                                                                                                                        | V <sub>CELL3</sub> - 0.5 |                          | V <sub>CELL3</sub>       | V    |

| DFET Gate Voltage                                                      | VDFET                | No load on DFET                                                                                                                        | V <sub>CELL3</sub> - 0.5 |                          | V <sub>CELL3</sub>       | V    |

| FET Turn-on Current (DFET)                                             | I <sub>DF(ON)</sub>  | DFET voltage = 0 to VCELL3 - 1.5V                                                                                                      | 80                       | 130                      | 400                      | μA   |

| FET Turn-on Current (CFET)                                             | I <sub>CF(ON)</sub>  | CFET voltage = 0 to VCELL3 - 1.5V                                                                                                      | 80                       | 200                      | 400                      | μA   |

| FET Turn-off Current (DFET)                                            | I <sub>DF(OFF)</sub> | DFET voltage = VDFET to 1V                                                                                                             | 100                      | 180                      |                          | mA   |

| DFET Resistance to VSS                                                 | R <sub>DF(OFF)</sub> | VDFET <1V (When turning off the FET)                                                                                                   |                          |                          | 11                       | Ω    |

| SERIAL INTERFACE CHARACTERISTIC                                        | CS (Over re          | commended operating conditions, unless oth                                                                                             | nerwise specifi          | ed)                      |                          |      |

| SCL Clock Frequency                                                    | f <sub>SCL</sub>     |                                                                                                                                        |                          |                          | 100                      | kHz  |

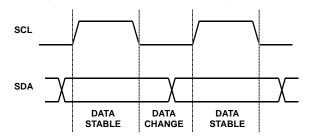

| SCL Falling Edge to SDA Output Data<br>Valid                           | t <sub>AA</sub>      | From SCL falling crossing $V_{IH}$ (min), until SDA exits the $V_{IL}$ (max) to $V_{IH}$ (min) window.                                 |                          |                          | 3.5                      | μs   |

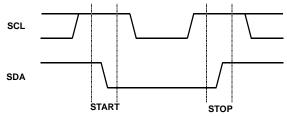

| Time the Bus Must be Free Before Start of New Transmission             | t <sub>BUF</sub>     | SDA crossing V <sub>IH</sub> (min) during a STOP condition to SDA crossing V <sub>IH</sub> (min) during the following START condition. | 4.7                      |                          |                          | μs   |

| Clock LOW Time                                                         | t <sub>LOW</sub>     | Measured at the V <sub>IL</sub> (max) crossing.                                                                                        | 4.7                      |                          |                          | μs   |

| Clock HIGH Time                                                        | tHIGH                | Measured at the V <sub>IH</sub> (min) crossing.                                                                                        | 4.0                      |                          |                          | μs   |

| Start Condition Setup Time                                             | <sup>t</sup> SU:STA  | SCL rising edge to SDA falling edge. Both crossing the V <sub>IH</sub> (min) level.                                                    | 4.7                      |                          |                          | μs   |

| Start Condition Hold Time                                              | t <sub>HD:STA</sub>  | From SDA falling edge crossing $V_{IL}(max)$ to SCL falling edge crossing $V_{IH}(min)$ .                                              | 4.0                      |                          |                          | μs   |

| Input Data Setup Time                                                  | t <sub>SU:DAT</sub>  | From SDA exiting the V <sub>IL</sub> (max) to V <sub>IH</sub> (min) window to SCL rising edge crossing V <sub>IL</sub> (min).          | 250                      |                          |                          | ns   |

| Input Data Hold Time                                                   | t <sub>HD:DAT</sub>  | From SCL rising edge crossing $V_{IH}(min)$ to SDA entering the $V_{IL}(max)$ to $V_{IH}(min)$ window.                                 | 300                      |                          |                          | ns   |

| Stop Condition Setup Time                                              | tsu:sto              | From SCL rising edge crossing $V_{IH}(min)$ to SDA rising edge crossing $V_{IL}(max)$ .                                                | 4.0                      |                          |                          | μs   |

Datasheet of ISL9216IRZ - IC MULTI-CELL LI-ION PROT 32-QFN

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

### ISL9216, ISL9217

# Operating Specifications Apply to Both the ISL9216 and ISL9217 Separately Over the Recommended Operating Conditions, Unless Otherwise Specified. (Continued)

| DESCRIPTION                                                         | SYMBOL              | TEST CONDITIONS                                                                                                                                                 | MIN                                         | TYP | MAX                                                                           | UNIT |

|---------------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----|-------------------------------------------------------------------------------|------|

| Stop Condition Hold Time                                            | thd:STO             | From SDA rising edge to SCL falling edge. Both crossing $V_{IH}(\min)$ .                                                                                        | 4.0                                         |     |                                                                               | μs   |

| Data Output Hold Time                                               | <sup>t</sup> DH     | From SCL falling edge crossing V <sub>IL</sub> (max) until SDA enters the V <sub>IL</sub> (max) to V <sub>IH</sub> (min) window. (Note 4)                       | 0                                           |     |                                                                               | ns   |

| SDA and SCL Rise Time                                               | t <sub>R</sub>      | From V <sub>IL</sub> (max) to V <sub>IH</sub> (min).                                                                                                            |                                             |     | 1000                                                                          | ns   |

| SDA and SCL Fall Time                                               | t <sub>F</sub>      | From V <sub>IH</sub> (min) to V <sub>IL</sub> (max).                                                                                                            |                                             |     | 300                                                                           | ns   |

| Capacitive Loading of SDA or SCL                                    | Cb                  | Total on-chip and off-chip                                                                                                                                      |                                             |     | 400                                                                           | pF   |

| SDA and SCL Bus Pull-up Resistor - Off<br>Chip                      | R <sub>OUT</sub>    | Maximum is determined by $t_R$ and $t_F$ .<br>For Cb = 400pF, max is about $2k\Omega \sim 2.5k\Omega$<br>For Cb = 40pF, max is about $15k\Omega$ to $20k\Omega$ |                                             |     |                                                                               | kΩ   |

| Input Leakage Current (SCL, SDA, SDAI, SDAO, SCLHV, SDAIHV, SDAOHV) | ILI                 |                                                                                                                                                                 | -10                                         |     | 10                                                                            | μA   |

| Input Buffer LOW Voltage (SCL, SDA, SDAI)                           | V <sub>IL1</sub>    | Voltage relative to V <sub>SS</sub> of the device.                                                                                                              | -0.3                                        |     | V <sub>RGO</sub> x 0.3                                                        | V    |

| Input Buffer HIGH Voltage (SCL, SDA, SDAI)                          | V <sub>IH1</sub>    | Voltage relative to V <sub>SS</sub> of the device.                                                                                                              | V <sub>RGO</sub> x 0.7                      |     | V <sub>RGO</sub> + 0.1V                                                       | V    |

| Input LOW Voltage (SDAIHV)                                          | V <sub>IL2</sub>    | SDAIHV pulled up to HCI2C. (ISL9216 only)                                                                                                                       | V <sub>CELL5</sub> - 0.3                    |     | V <sub>VCELL5</sub> +<br>[V <sub>HVI2C</sub> -<br>V <sub>VCELL5</sub> ] x 0.3 | V    |

| Input HIGH Voltage (SDAIHV)                                         | V <sub>IH2</sub>    | SDAIHV pulled up to HCI2C. (ISL9216 only)                                                                                                                       | VVCELL5 +<br>[VHVI2C -<br>VVCELL5] x<br>0.7 |     | V <sub>HVI2C</sub> + 0.1V                                                     | V    |

| Output Buffer LOW Voltage (SDA, SDAO)                               | VOL1                | I <sub>OL</sub> = 1mA<br>(voltage relative to V <sub>SS</sub> of the device)                                                                                    |                                             |     | 0.4                                                                           | V    |

| Output Buffer LOW Voltage (SDAOHV)                                  | VOL2                | I <sub>OL</sub> = 1mA                                                                                                                                           |                                             |     | V <sub>VCELL5</sub> + 0.5                                                     | V    |

| SDA, SCL, SDAI Input Buffer Hysteresis                              | I2CHYST<br>(Note 4) | Sleep bit = 0                                                                                                                                                   | 0.05*V <sub>RGO</sub>                       |     |                                                                               | V    |

#### NOTES:

- 3. Power-up of the device requires all VCELL1, VCELL2, VCELL3, and VCC to be above the limits specified.

- 4. The device provides an internal hold time of at least 300ns for the SDA signal to bridge the unidentified region of the falling edge of SCL.

- 5. Limits established by characterization and are not production tested.

- 6. Maximum output capacitance = 15pF

## Wake-up Timing (WKPOL = 0)

## Wake-up Timing (WKPOL = 1)

## Change in Voltage Source, FET Control

### Automatic Temperature Scan (ISL9216 only)

### Discharge Overcurrent/Short Circuit Monitor (ISL9216 only) (Assumes DENOCD and DENSCD bits are '0')

Datasheet of ISL9216IRZ - IC MULTI-CELL LI-ION PROT 32-QFN

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

## ISL9216, ISL9217

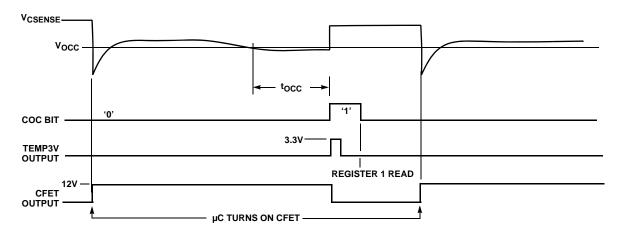

### Charge Overcurrent Monitor (ISL9216 only) (Assumes DENOCC bit is '0')

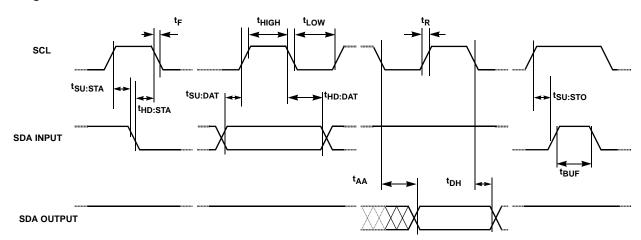

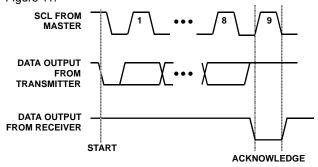

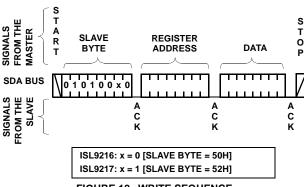

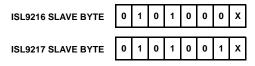

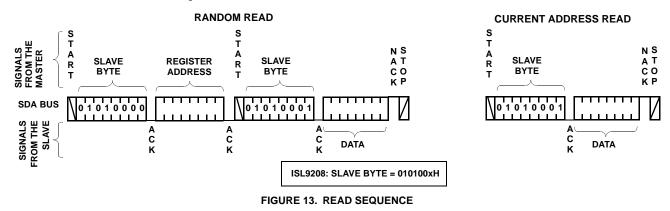

## Serial Interface Timing Diagrams

### **Bus Timing**

This timing shows the communication with the ISL9216. Communication with the ISL9217 (through the ISL9216) adds some lag time, however, overall the communication with the ISL9217 meets the same timing requirements as communication with the ISL9216.

### Symbol Table

| WAVEFORM | INPUTS                            | OUTPUTS                            |

|----------|-----------------------------------|------------------------------------|

|          | Must be steady                    | Will be steady                     |

|          | May change<br>from LOW<br>to HIGH | Will change<br>from LOW<br>to HIGH |

|          | May change<br>from HIGH<br>to LOW | Will change<br>from HIGH<br>to LOW |

|          | Don't Care:<br>Changes<br>Allowed | Changing:<br>State Not<br>Known    |

|          | N/A                               | Center Line is High Impedance      |

Datasheet of ISL9216IRZ - IC MULTI-CELL LI-ION PROT 32-QFN

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

### ISL9216, ISL9217

## Registers

#### **TABLE 1. REGISTERS**

| ADDR        | REGISTER                     | READ/WRITE                                           | 7                                             | 6                                                      | 5                                    | 4                                         | 3                                         | 2                                          | 1                                 | 0                                   |

|-------------|------------------------------|------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------|--------------------------------------|-------------------------------------------|-------------------------------------------|--------------------------------------------|-----------------------------------|-------------------------------------|

| 00H         | Configuration<br>Status      | Read only                                            | <b>CU</b><br>Cascade U                        | CL<br>Cascade L                                        | Reserved                             | WKUP<br>WKUP pin<br>Status                | Reserved                                  | Reserved                                   | Reserved                          | Reserved                            |

| 01H         | Operating Status<br>(Note 9) | Read only                                            | Reserved                                      | Reserved                                               | XOT<br>Ext over<br>temp              | IOT<br>Int over<br>Temp                   | LDFAIL<br>Load Fail<br>(VMON)             | DSC<br>Short<br>Circuit                    | DOC<br>Discharge<br>OC            | COC<br>Charge OC                    |

| 02H         | Cell Balance                 | Read/Write                                           | CB7ON                                         | CB6ON/<br>WKUPR                                        | CB5ON                                | CB4ON                                     | CB3ON                                     | CB2ON                                      | CB10N                             | Reserved                            |

|             |                              |                                                      |                                               | Cell balance F                                         | ET control b                         | its (plus WKU                             | P of ISL9217                              | in cascade)                                |                                   |                                     |

| 03H         | Analog Out                   | Read/Write                                           | UFLG1                                         | UFLG0                                                  | Reserved                             | Reserved                                  | AO3                                       | AO2                                        | AO1                               | AO0                                 |

|             |                              |                                                      | User Flag 1                                   | User Flag 0                                            |                                      |                                           |                                           | Analog outp                                | ut select bits                    |                                     |

| 04H         | FET Control                  | Read/Write                                           | SLEEP<br>Force<br>Sleep<br>(Note 10)          | LDMONEN Turn on VMON connection                        | Reserved                             | Reserved                                  | Reserved                                  | Reserved                                   | CFET Turn on Charge FET (Note 11) | DFET Turn on Disharge FET (Note 11) |

| 05H         | Discharge Set                | Read/Write<br>(Write only if<br>DISSETEN bit<br>set) | Turn off<br>automatic<br>OCD<br>control       | OCDV1 Configure C Discharge                            |                                      | Turn off<br>automatic<br>SCD control      | SCDV1 Configure S Discharge               | SCDV0<br>Short Circuit<br>Threshold        | J                                 | OCDT0  Overcurrent Time-out         |

| 06H         | Charge Set                   | Read/Write<br>(Write only if<br>CHSETEN bit<br>set)  | Turn off<br>automatic<br>OCC<br>control       | OCCV1  Configure C  Charge T                           |                                      | SCLONG<br>Long Short-<br>circuit delay    | CTDIV Divide charge time by 32            | DTDIV<br>Divide<br>discharge<br>time by 64 | _                                 | OCCT0  Overcurrent  Time-out        |

| 07H         | Feature Set                  | Read/Write<br>(Write only if<br>FSETEN bit<br>set)   | ATMPOFF Turn off automatic external temp scan | DIS3 Disable 3.3V reg. (device requires external 3.3V) | TMP3ON<br>Temp 3.3V<br>keep on       | DISXTSD Disable external thermal shutdown | DISITSD Disable internal thermal shutdown | POR<br>Force POR                           | DISWKUP<br>Disable<br>WKUP pin    | WKPOL<br>Wake-up<br>Polarity        |

| 08H         | Write Enable                 | Read/Write                                           | FSETEN Enable Feature Set writes              | CHSETEN Enable Charge Set writes                       | DISSETEN Enable Discharge Set writes | UFLG3<br>User Flag 3                      | <b>UFLG2</b><br>User Flag 2               | Reserved                                   | Reserved                          | Reserved                            |

| 09H:<br>FFH | Reserved                     | NA                                                   |                                               |                                                        |                                      | RESER                                     | EVED                                      |                                            |                                   |                                     |

#### NOTES:

- 7. A "1" written to a control or configuration bit causes the action to be taken. A "1" read from a status bit indicates that the condition exists.

- 8. "Reserved" indicates that the bit or register is reserved for future expansion. When writing to addresses 2, 3, 4, 6, 7, and 8: write a reserved bit with the value "0". Do not write to reserved registers at addresses 09H through FFH. Ignore reserved bits that are returned in a read operation.

- 9. These status bits are automatically cleared when the register is read. All other status bits are cleared when the condition is cleared.

- 10. This SLEEP bit is cleared on initial power-up, by the WKUP pin going high (when WKPOL = "1") or by the WKUP pin going low (when WKPOL = "0"), and by writing a "0" to the location with an I<sup>2</sup>C command.

- 11. When the automatic responses are enabled, these bits are automatically reset by hardware when an overcurrent or short circuit condition turns off the FETs. At all other times, an I<sup>2</sup>C write operation controls the output to the respective FET and a read returns the current state of the FET drive output circuit (though not the actual voltage at the output pin).

- 12. The shaded registers are not used in the ISL9217 device. Shaded status registers return '0' when read. Shaded "read/write" registers can be read and written, but they provide no functionality. When writing to the shaded areas in the ISL9217, the locations must be written as "0".

Datasheet of ISL9216IRZ - IC MULTI-CELL LI-ION PROT 32-QFN

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

## ISL9216, ISL9217

## Status Registers

#### TABLE 2. CONFIGURATION STATUS REGISTER (ADDR: 00H)

| BIT | FUNCTION                          | DESCRIPTION                                                                                                                                                                                                                                                      |

|-----|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CU<br>Cascade U                   | Indicates the device is an ISL9217. This bit is set in hardware and cannot be changed.                                                                                                                                                                           |

| 6   | CL<br>Cascade L                   | Indicates the device is an ISL9216. This bit is set in hardware and cannot be changed.                                                                                                                                                                           |

| 5   | SA                                | Reserved for ISL9208 devices.                                                                                                                                                                                                                                    |

| 4   | <b>WKUP</b><br>Wake-up Pin Status | This bit is set and reset by hardware.  When 'WKPOL' is HIGH,  'WKUP' HIGH = WKUP pin > Threshold voltage  'WKUP' LOW = WKUP pin < Threshold voltage  When 'WKPOL' is LOW  'WKUP' HIGH = WKUP pin < Threshold voltage  'WKUP' LOW = WKUP pin > Threshold voltage |

| 3   | RESERVED                          | Reserved for future expansion.                                                                                                                                                                                                                                   |

| 2   | RESERVED                          | Reserved for future expansion.                                                                                                                                                                                                                                   |

| 1   | RESERVED                          | Reserved for future expansion.                                                                                                                                                                                                                                   |

| 0   | RESERVED                          | Reserved for future expansion.                                                                                                                                                                                                                                   |

### TABLE 3. OPERATING STATUS REGISTER (ADDR: 01H)

| BIT | FUNCTION                                     | DESCRIPTION                                                                                                                                                                                                                                                            |

|-----|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RESERVED                                     | Reserved for future expansion.                                                                                                                                                                                                                                         |

| 6   | RESERVED                                     | Reserved for future expansion.                                                                                                                                                                                                                                         |

| 5   | XOT<br>Ext Over-temp<br>(ISL9216 only)       | This bit is set to "1" when the external thermistor indicates an over-temperature condition. If the temperature condition has cleared, this bit is reset when the register is read.                                                                                    |

| 4   | IOT<br>Int Over-temp                         | This bit is set to "1" when the internal thermistor indicates an over-temperature condition. If the temperature condition has cleared, this bit is reset when the register is read.                                                                                    |

| 3   | LDFAIL<br>Load Fail (VMON)<br>(ISL9216 only) | When the function is enabled, this bit is set to "1" by hardware when a discharge overcurrent or short circuit condition occurs and the load remains heavy. When the load fail condition is cleared or under a light load, the bit is reset when the register is read. |

| 2   | DSC<br>Short Circuit<br>(ISL9216 only)       | This bit is set by hardware when a short circuit condition occurs during discharge. When the discharge short circuit condition is removed, the bit is reset when the register is read.                                                                                 |

| 1   | DOC<br>Discharge OC<br>(ISL9216 only)        | This bit is set by hardware when an overcurrent condition occurs during discharge. When the discharge overcurrent condition is removed, the bit is reset when the register is read.                                                                                    |

| 0   | COC<br>Charge OC<br>(ISL9216 only)           | This bit is set by hardware when an overcurrent condition occurs during charge. When the charge overcurrent condition is removed, the bit is reset when the register is read.                                                                                          |

Datasheet of ISL9216IRZ - IC MULTI-CELL LI-ION PROT 32-QFN

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

## ISL9216, ISL9217

## **Control Registers**

TABLE 4. CELL BALANCE CONTROL REGISTER (ADDR: 02H)

|                |                         | CONT           | ROL REGISTER   | DL REGISTER BITS |                |                |                               |

|----------------|-------------------------|----------------|----------------|------------------|----------------|----------------|-------------------------------|

| BIT 7<br>CB7ON | BIT 6<br>CB6ON<br>WKUPR | BIT 5<br>CB5ON | BIT 4<br>CB4ON | BIT 3<br>CB3ON   | BIT 2<br>CB2ON | BIT 1<br>CB1ON | BALANCE                       |

| Х              | х                       | х              | х              | х                | х              | 1              | Cell1 ON                      |

| х              | х                       | х              | х              | х                | х              | 0              | Cell1 OFF                     |

| х              | х                       | х              | х              | х                | 1              | х              | Cell2 ON                      |

| х              | х                       | х              | х              | х                | 0              | х              | Cell2 OFF                     |

| х              | х                       | х              | х              | 1                | х              | х              | Cell3 ON                      |

| х              | х                       | х              | х              | 0                | х              | х              | Cell3 OFF                     |

| х              | х                       | х              | 1              | х                | х              | х              | Cell4 ON                      |

| х              | х                       | х              | 0              | х                | х              | х              | Cell4 OFF                     |

| х              | х                       | 1              | х              | х                | х              | х              | Cell5 ON                      |

| х              | х                       | 0              | х              | х                | х              | х              | Cell5 OFF                     |

| х              | 1                       | х              | х              | х                | х              | х              | Cell6 ON/WKUPR On (Note 13)   |

| х              | 0                       | х              | х              | х                | х              | х              | Cell6 OFF/WKUPR OFF (Note 13) |

| 1              | х                       | х              | х              | х                | х              | х              | Cell7 ON (ISL9217 only)       |

| 0              | х                       | х              | х              | х                | х              | х              | Cell7 OFF (ISL9217 only)      |

| Bit 0          | Bit 0 RESERVED          |                |                | uture expansio   | n              | 1              |                               |

NOTE:

13. WKUPR Pin refers to the ISL9216

16

Datasheet of ISL9216IRZ - IC MULTI-CELL LI-ION PROT 32-QFN

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

## ISL9216, ISL9217

### TABLE 5. ANALOG OUT CONTROL REGISTER (ADDR: 03H)

| BITS         | FUNC                 | CTION        |                | DESCRIPTION                                                                                         |

|--------------|----------------------|--------------|----------------|-----------------------------------------------------------------------------------------------------|

| 7            | UFLG1<br>User Flag   | 1            | General purpo  | se flag usable by microcontroller software. This bit is battery backed up, even when RGO turns off. |

| 6            | UFLG0<br>User Flag 0 |              | General purpo  | se flag usable by microcontroller software. This bit is battery backed up, even when RGO turns off. |

| 5:4          | RESERVE              | D            | Reserved for f | uture expansion                                                                                     |

| BIT 3<br>AO3 | BIT 2<br>AO2         | BIT 1<br>AO1 | BIT 0<br>AO0   | OUTPUT VOLTAGE                                                                                      |

| 0            | 0                    | 0            | 0              | No Output (low power state)                                                                         |

| 0            | 0                    | 0            | 1              | VCELL1                                                                                              |

| 0            | 0                    | 1            | 0              | VCELL2                                                                                              |

| 0            | 0                    | 1            | 1              | VCELL3                                                                                              |

| 0            | 1                    | 0            | 0              | VCELL4                                                                                              |