## **Excellent Integrated System Limited**

Stocking Distributor

Click to view price, real time Inventory, Delivery & Lifecycle Information:

Integrated Device Technology (IDT) ICS674R-01

For any questions, you can email us directly: <u>sales@integrated-circuit.com</u>

## USER CONFIGURABLE DIVIDER

# DATASHEET

#### ICS674-01

## Description

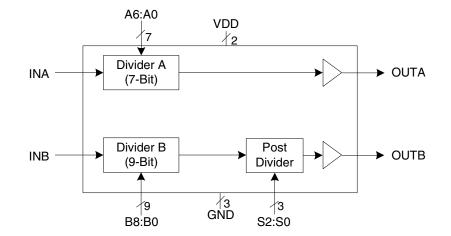

The ICS674-01 consists of two separate configurable dividers. The A Divider is a 7-bit divider and can divide by 3 to 129. The B Divider consists of a 9-bit divider followed by a post divider. The 9-bit divider can divide by 12 to 519. The post divider has eight settings of 1, 2, 4, 5, 6, 7, 8, and 10; giving a maximum total divide of 5190. The A and B Dividers can be cascaded to give a maximum divide of 669510. The ICS674-01 supports the ICS673 PLL Building Block and enables the user to build a full custom PLL synthesizer.

#### Features

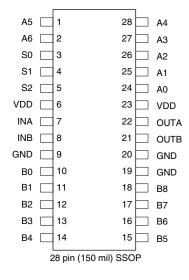

- Packaged in 28-pin SSOP (150 mil body)

- Available in Pb (lead) free package

- General purpose programmable divider

- Supports ICS673 PLL Building Block

- User determines the divide by setting input pins

- Pull-ups on all select inputs

- Includes one 7-bit Divider for OUTA

- Includes one 9-bit Divider and one selectable Post Divider for OUTB

- Industrial temperature range available

- 25 mA drive capability at TTL levels

- Advanced, low power CMOS process

- Operating voltage of 3.3 V or 5 V

NOTE: EOL for non-green parts to occur on 5/13/10 per PDN U-09-01

### **Block Diagram**

ICS674-01 USER CONFIGURABLE DIVIDER

**CLOCK DIVIDER**

### **Pin Assignment**

### **Post Divider Table**

| S2<br>Pin 5 | S1<br>Pin 4 | S0<br>Pin 3 | Post Divide |

|-------------|-------------|-------------|-------------|

| 0           | 0           | 0           | 10          |

| 0           | 0           | 1           | 2           |

| 0           | 1           | 0           | 8           |

| 0           | 1           | 1           | 4           |

| 1           | 0           | 0           | 5           |

| 1           | 0           | 1           | 7           |

| 1           | 1           | 0           | 1           |

| 1           | 1           | 1           | 6           |

## **Pin Descriptions**

| Pin<br>Number | Pin<br>Name   | Pin Type | Pin Description                                                                                              |

|---------------|---------------|----------|--------------------------------------------------------------------------------------------------------------|

| 1, 2, 24 - 28 | A5, A6, A0-A4 | Input    | Divider A word input pins. Forms a number from 1 to 127. Internal pull-up resistors. See page 3 for details. |

| 3 - 5         | S0, S1, S2    | Input    | Select pins for Post Divider. See table above. Internal pull-up resistors.                                   |

| 6, 23         | VDD           | Power    | Connect to VDD.                                                                                              |

| 7             | INA           | Input    | Divider A input.                                                                                             |

| 8             | INB           | Input    | Divider B input.                                                                                             |

| 9, 19 - 20    | GND           | Power    | Connect to ground.                                                                                           |

| 10 - 18       | B0 - B8       | Input    | Divider B word input pins. Forms a number from 4 to 511. Internal pull-up resistors. See page 3 for details. |

| 21            | OUTB          | Output   | Divider B output.                                                                                            |

| 22            | OUTA          | Output   | Divider A output.                                                                                            |

#### ICS674-01 USER CONFIGURABLE DIVIDER

**CLOCK DIVIDER**

#### **External Components**

The ICS674-01 requires a minimum number of external components for proper operation. A  $0.01\mu$ F decoupling capacitor should be connected between each VDD and GND as close to the device as possible. A series termination resistor of  $33\Omega$  should be used in series with OUTA and OUTB pins.

## Determining (setting) the Divider

The user has full control in setting the desired divide. The user should connect the appropriate divider select input pins directly to ground (or VDD, although this is not required because of internal pull-ups) during Printed Circuit Board layout, ensuring that the ICS674-01 will automatically produce the correct divide when all components are soldered. It is also possible to connect the inputs to parallel I/O ports in order to change divides. The divides of the ICS674-01 can be determined by the following equations:

Divide A = DAW + 2

Where Divider A Word (DAW) = 1 to 127 (0 is not permitted)

Divide  $B = (DBW+8) \times PD$

Where Divider B Word (DBW) = 4 to 511 (0, 1, 2, 3 are not permitted) Post Divider (PD) = values on page 2

For example, suppose Divide A is desired to be 61 and Divide B is desired to be 284, then DAW = 59, DBW = 276, and PD = 1. This means A6:A0 is 0111011, B8:B0 is 100010100 and S2:S0 is 110. Since all inputs have pull-ups, it is only necessary to ground the zero pins, namely A6, A2, B7, B6, B5, B1, B0, and S0. These configuration pins can be changed at any time during operation.

#### ICS674-01 USER CONFIGURABLE DIVIDER

**CLOCK DIVIDER**

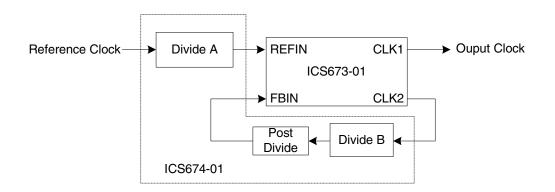

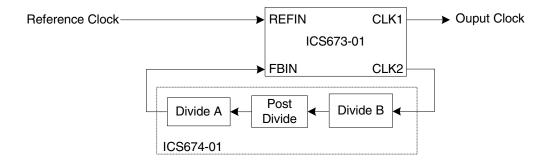

## Using the ICS674-01 with the ICS673-01:

The ICS674-01 may be used with the ICS673-01 to build a frequency synthesizer. The following example shows a typical application when the reference clock is in the MHz range:

If the reference is in the kHz range, for example 8 kHz, the following configuration may be more typical:

Note that in both examples, Divide B is connected to the output of the ICS673. This is because Divide B has a higher operating frequency than Divide A.

4

ICS674-01 USER CONFIGURABLE DIVIDER

**CLOCK DIVIDER**

### **Absolute Maximum Ratings**

Stresses above the ratings listed below can cause permanent damage to the ICS674-01. These ratings, which are standard values for IDT commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| Item                                      | Rating              |

|-------------------------------------------|---------------------|

| Supply Voltage, VDD                       | 7 V                 |

| All Inputs and Outputs                    | -0.5 V to VDD+0.5 V |

| CLKIN and FBIN inputs                     | -0.5 V to 5.5 V     |

| Electrostatic Discharge                   | 2000 V              |

| Ambient Operating Temperature             | 0 to +70° C         |

| Ambient Operating Temperature (I version) | -40 to +85° C       |

| Storage Temperature                       | -65 to +150° C      |

| Junction Temperature                      | 150°C               |

| Soldering Temperature                     | 260° C              |

#### **Recommended Operation Conditions**

| Parameter                                         | Min. | Тур. | Max. | Units |

|---------------------------------------------------|------|------|------|-------|

| Ambient Operating Temperature                     | 0    |      | +70  | °C    |

| Power Supply Voltage (measured in respect to GND) | +3.0 |      | +5.5 | V     |

#### **DC Electrical Characteristics**

VDD=5 V ±10%, Ambient temperature -40 to +85° C, unless stated otherwise

| Parameter                | Symbol          | Conditions                                 | Min.      | Тур.  | Max.      | Units |

|--------------------------|-----------------|--------------------------------------------|-----------|-------|-----------|-------|

| Operating Voltage        | VDD             |                                            | 3.0       |       | 5.5       | V     |

| Input High Voltage       | V <sub>IH</sub> | All A, B, and S pins                       | 2         |       |           | V     |

| Input Low Voltage        | V <sub>IL</sub> | All A, B, and S pins                       |           |       | 0.8       | V     |

| Input High Voltage       | V <sub>IH</sub> | INA and INB only                           | (VDD/2)+1 | VDD/2 |           | V     |

| Input Low Voltage        | V <sub>IL</sub> | INA and INB only                           |           | VDD/2 | (VDD/2)-1 | V     |

| Output High Voltage      | V <sub>OH</sub> | I <sub>OH</sub> = -25 mA                   | 2.4       |       |           | V     |

| Output Low Voltage       | V <sub>OL</sub> | I <sub>OL</sub> = 25 mA                    |           |       | 0.4       | V     |

| Operating Supply Current | IDD             | No load, f <sub>in</sub> =100 MHz<br>3.3 V |           | 3     |           | mA    |

| DivA=DivB=20             |                 | No load, f <sub>in</sub> =100 MHz<br>5 V   |           | 5     |           | mA    |

#### ICS674-01 USER CONFIGURABLE DIVIDER

**CLOCK DIVIDER**

| Parameter                | Symbol          | Conditions          | Min. | Тур. | Max. | Units |

|--------------------------|-----------------|---------------------|------|------|------|-------|

| Short Circuit Current    | I <sub>OS</sub> | Each output         |      | ±70  |      | mA    |

| On-Chip Pull-up Resistor | R <sub>PU</sub> | A, B, S select pins |      | 270  |      | kΩ    |

| Input Capacitance        | C <sub>IN</sub> | A, B, S select pins |      | 5    |      | pF    |

#### **AC Electrical Characteristics**

VDD = 5 V, Ambient Temperature -40 to +85° C,  $C_{LOAD}$  at CLK = 15 pF, unless stated otherwise

| Parameter                                              | Symbol          | Conditions            | Min. | Тур.     | Max. | Units |

|--------------------------------------------------------|-----------------|-----------------------|------|----------|------|-------|

| Input Frequency, Divider A                             | f <sub>IN</sub> | 3.3 V                 | 0    |          | 135  | MHz   |

| Input Frequency, Divider B                             |                 | 3.3 V                 | 0    |          | 180  | MHz   |

| Input Frequency, Divider A                             | -               | 5 V                   | 0    |          | 200  | MHz   |

| Input Frequency, Divider B                             |                 | 5 V                   | 0    |          | 235  | MHz   |

| Input Frequency, Divider A<br>(Industrial temperature) | f <sub>IN</sub> | at 3.3 V, +85° C      | 0    |          | 125  | MHz   |

| Input Frequency, Divider B<br>(Industrial temperature) |                 | at 3.3 V, +85° C      | 0    |          | 170  | MHz   |

| Input Frequency, Divider A<br>(Industrial temperature) |                 | at 5 V, +85° C        | 0    |          | 190  | MHz   |

| Input Frequency, Divider B<br>(Industrial temperature) | -               | at 5 V, +85° C        | 0    |          | 220  | MHz   |

| Output Rise Time                                       | t <sub>OR</sub> | 20% to 80%            |      | 1.5      |      | ns    |

| Output Fall Time                                       | t <sub>OF</sub> | 80% to 20%            |      | 1.5      |      | ns    |

| OUTB Clock Duty Cycle <sup>1</sup>                     | t <sub>DC</sub> | at VDD/2              | 45   | 49 to 51 | 55   | %     |

| OUTB Clock Duty Cycle<br>odd post dividers             |                 | at VDD/2, except PD=1 | 40   |          | 60   | %     |

| OUTA Clock Duty Cycle <sup>1</sup>                     |                 | at VDD/2              | 20   |          | 98.5 | %     |

| Peak-to-Peak Jitter                                    |                 | 15 pF                 |      |          | 400  | ps    |

| Cycle-to-Cycle Jitter                                  |                 | 30 pF loads           |      |          | 300  | ps    |

| Propagation Delay,                                     | T <sub>PA</sub> | VDD = 3.3 V, +25° C   |      | 6.5      |      | ns    |

| Divider A                                              |                 | VDD = 5.0 V, +25° C   |      | 4.5      |      | ns    |

| Propagation Delay,                                     | T <sub>PB</sub> | VDD = 3.3 V, +25° C   |      | 20       |      | ns    |

| Divider B + Post Divider                               |                 | VDD = 5.0 V, +25° C   |      | 13       |      | ns    |

<sup>1</sup> The duty cycle of OUTA is dependent on the selected divide. This because OUTA goes low for 1 input clock cycles on INA. For example, if a divide of 20 is selected, the duty cycle will be 90%. Simlarly, if PD=1 is selected for OUTB, the duty cycle will be dependent on the selected divide. In this case, OUTB goes high for approximately 8 input clock cycles on INB.

#### ICS674-01 USER CONFIGURABLE DIVIDER

**CLOCK DIVIDER**

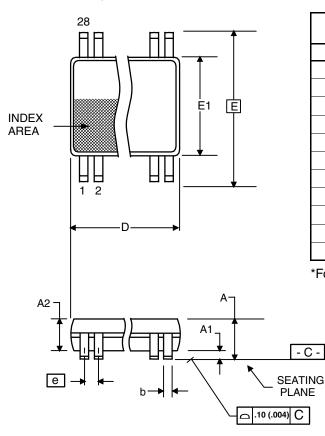

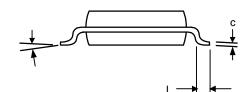

#### Package Outline and Package Dimensions (28-pin SSOP, 150 Mil. Body)

Package dimensions are kept current with JEDEC Publication No. 95

|        | Millimeters |            | Incl       | nes*       |

|--------|-------------|------------|------------|------------|

| Symbol | Min         | Max        | Min        | Max        |

| A      | 1.35        | 1.75       | .053       | .069       |

| A1     | 0.10        | 0.25       | .0040      | .010       |

| A2     |             | 1.50       |            | .059       |

| b      | 0.20        | 0.30       | 0.008      | 0.012      |

| С      | 0.18        | 0.25       | .007       | .010       |

| D      | 9.80        | 10.00      | .386       | .394       |

| E      | 5.80        | 6.20       | .228       | .244       |

| E1     | 3.80        | 4.00       | .150       | .157       |

| е      | 0.635       | Basic      | 0.025      | Basic      |

| L      | 0.40        | 1.27       | .016       | .050       |

| α      | <b>0</b> °  | <b>8</b> ° | <b>0</b> ° | <b>8</b> ° |

\*For reference only. Controlling dimensions in mm.

#### **Ordering Information**

| Part / Order Number | Marking    | Shipping Packaging | Package     | Temperature  |

|---------------------|------------|--------------------|-------------|--------------|

| 674R-01*            | 674R-01    | Tubes              | 28-pin SSOP | 0 to +70° C  |

| 674R-01T*           | 674R-01    | Tape and Reel      | 28-pin SSOP | 0 to +70° C  |

| 674R-01LF           | 674R-01LF  | Tubes              | 28-pin SSOP | 0 to +70° C  |

| 674R-01LFT          | 674R-01LF  | Tape and Reel      | 28-pin SSOP | 0 to +70° C  |

| 674R-01I*           | 674R-01I   | Tubes              | 28-pin SSOP | -40 to 85° C |

| 674R-01IT*          | 674R-01I   | Tape and Reel      | 28-pin SSOP | -40 to 85° C |

| 674R-01ILF          | 674R-01ILF | Tubes              | 28-pin SSOP | -40 to 85° C |

| 674R-01ILFT         | 674R-01ILF | Tape and Reel      | 28-pin SSOP | -40 to 85° C |

#### \*NOTE: EOL for non-green parts to occur on 5/13/10 per PDN U-09-01

Parts that are ordered with a "LF" suffix to the part number are the Pb-Free configuration and are RoHS compliant.

While the information presented herein has been checked for both accuracy and reliability, Integrated Device Technology (IDT) assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial applications. Any other applications such as those requiring extended temperature range, high-reliability, or other extraordinary environmental requirements are not recommended without additional processing by IDT. IDT reserves the right to change any circuitry or specifications without notice. IDT does not authorize or warrant any IDT product for use in life support devices or critical medical instruments.

ICS674-01 USER CONFIGURABLE DIVIDER

**CLOCK DIVIDER**

## Innovate with IDT and accelerate your future networks. Contact:

# www.IDT.com

#### For Sales

800-345-7015 408-284-8200 Fax: 408-284-2775 For Tech Support www.idt.com/go/clockhelp

#### Corporate Headquarters Integrated Device Technology, Inc. www.idt.com

© 2006 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice. IDT and the IDT logo are trademarks of Integrated Device Technology, Inc. Accelerated Thinking is a service mark of Integrated Device Technology, Inc. All other brands, product names and marks are or may be trademarks or registered trademarks used to identify products or services of their respective owners. Printed in USA