## Excellent Integrated System Limited

Stocking Distributor

Click to view price, real time Inventory, Delivery & Lifecycle Information:

[Texas Instruments](#)

[TPS65281RGVR](#)

For any questions, you can email us directly:

[sales@integrated-circuit.com](mailto:sales@integrated-circuit.com)

**PRECISION ADJUSTABLE CURRENT LIMITED POWER DISTRIBUTION SWITCH WITH 4.5V TO 18V INPUT VOLTAGE, 3A OUTPUT CURRENT SYNCHRONOUS BUCK REGULATOR**Check for Samples: [TPS65281](#), [TPS65281-1](#)**FEATURES****INTEGRATED POWER DISTRIBUTION SWITCH**

- Operating Input Voltage Range: 2.5 V to 6.5 V

- Adjustable Current Limit: 75 mA - 2.7 A (typical)

- $\pm 6\%$  Current-Limit Accuracy at 1.7 A (typical)

- Over Current Latch-Off Protection (TPS65281) and Over Current Auto-Recovery (TPS65281-1)

- Reverse Input-Output Voltage Protection

- Built-In Soft-Start

- Integrated Back-to-Back Power MOSFETs With 100-m $\Omega$  On-Resistance

- Over Temperature Protection

**INTEGRATED BUCK CONVERTER**

- Wide Input Voltage Range: 4.5 V to 18 V

- Maximum Continuous 3-A Output Current

- Feedback Reference Voltage: 0.8 V  $\pm 1\%$

- Adjustable 300-kHz to 1.4-MHz Switching Frequency

- Adjustable Soft Start and Tracking With Built-In 1-ms Internal Soft-Start Time

- Cycle-by-Cycle Current Limit

- Output Over-voltage Protection

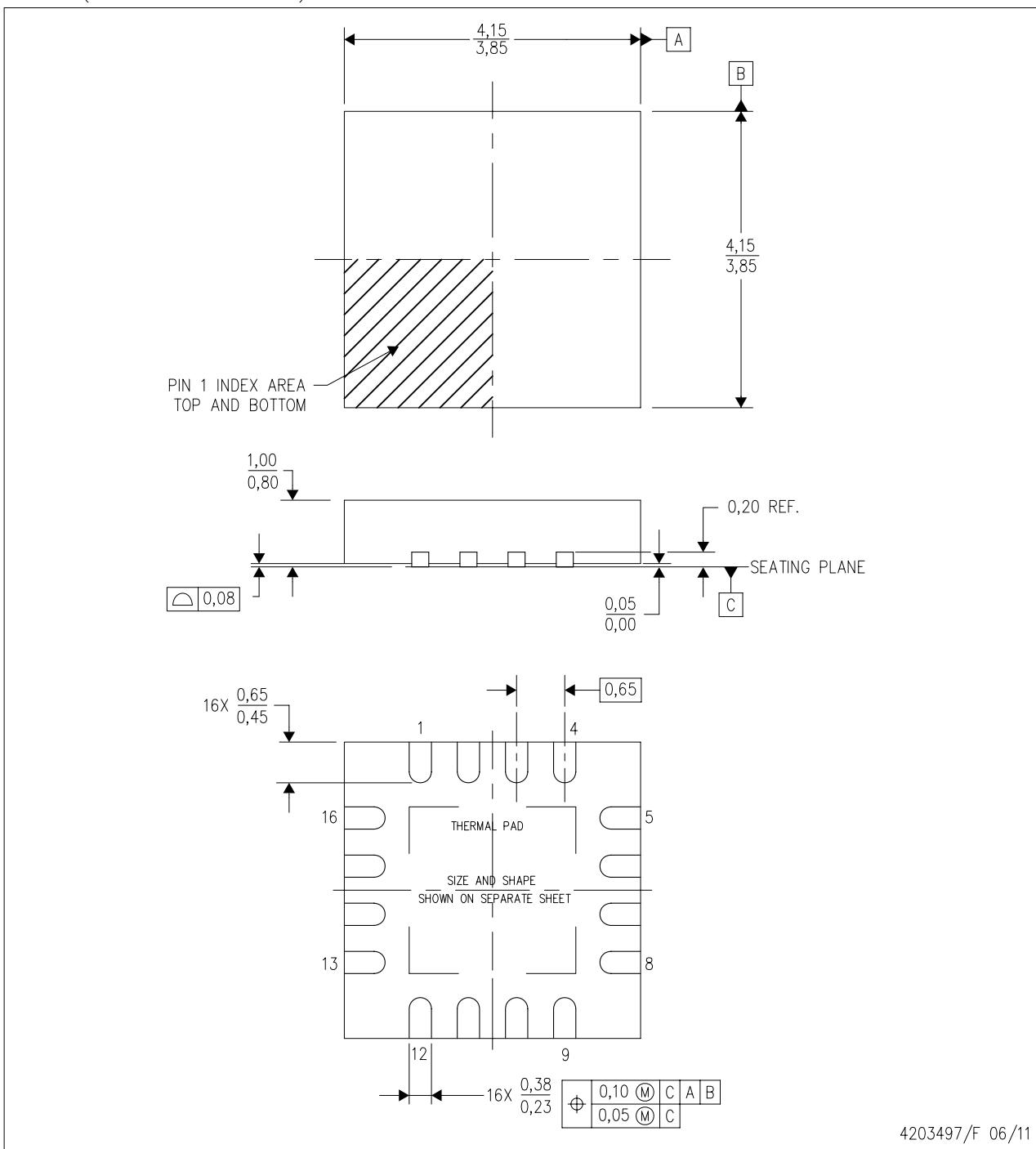

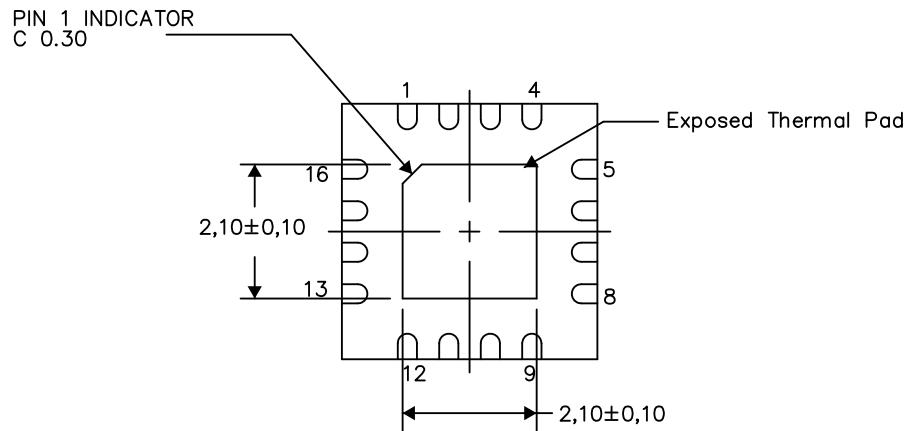

- 16-Lead QFN (RGV) 4-mm x 4-mm Package

**APPLICATIONS**

- USB Ports and Hubs

- Digital TV

- Set-Top Boxes

- VOIP Phones

- Tablet PC

**DESCRIPTION/ORDERING INFORMATION**

The TPS65281/TPS65281-1 incorporates an N-channel back-to-back power MOSFET switch and a monolithic buck converter. The device is intended to provide a total power distribution solution for digital TV, set-top boxes, tablet PC and VOIP phones etc applications, where precision current limiting is required or heavy capacitive load or short circuit are encountered.

A 100-m $\Omega$  independent power distribution switch limits the output current to a programmable current limit threshold between typical 75 mA and 2.7 A by using an external resistor. The current limit accuracy as tight as  $\pm 6\%$  can be achieved at higher current limit setting. TPS65281 provides circuit breaker functionality by latching off the power switch during over-current or reverse-voltage situations. TPS65281-1 limits output current to a safe level by using a constant current mode when the output load exceeds the current limit threshold. An internal reverse-voltage comparator disables the power switch when the output voltage is driven higher than the input to protect the device on the input side of the switch in normal operation. The nFAULT output asserts low under over-current and reverse-voltage conditions. Back-to-back power MOSFETs structure prevents the reverse current injection from an active load at output port during shutdown of power switch.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

The buck DC/DC converter integrates power MOSFETs for optimized power efficiency and reduced external component count. A wide 4.5-V to 18-V input supply range to buck encompasses most intermediate bus voltages operating off 5-V, 9-V, 12-V or 15-V power bus. Constant frequency peak current mode control simplifies the compensation and provides fast transient response. The buck can be precisely sequenced and ramp up in order to align with other rails in the system with the soft-start pin. With SS pin floating, the built-in 1ms soft-start time prevents in-rush current. Cycle-by-cycle over current protection and hiccup operation limit MOSFET power dissipation in short circuit or over loading fault conditions. The switching frequency of the converter can be programmed from 300 kHz to 1.4 MHz with an external resistor at ROSC pin. With ROSC pin connecting to V7V pin, floating, or grounding, a default fixed switching frequency can be selected to reduce an external resistor.

The TPS65281/TPS65281-1 is available in a 16-lead thermally enhanced QFN (RGV) 4-mm x 4-mm thin package.

**ORDERING INFORMATION<sup>(1)</sup>**

| T <sub>A</sub> | PACKAGE <sup>(2)</sup> | ORDERABLE PART NUMBER | TOP-SIDE MARKING |

|----------------|------------------------|-----------------------|------------------|

| –40°C to 85°C  | 16-Pin QFN (RGV)       | TPS65281RGVR          | TPS65281         |

|                |                        | TPS65281RGVT          |                  |

|                |                        | TPS65281-1RGVR        | TPS65281-1       |

|                |                        | TPS65281-1RGVT        |                  |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at [www.ti.com](http://www.ti.com).

(2) Package drawings, thermal data, and symbolization are available at [www.ti.com/packaging](http://www.ti.com/packaging).

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

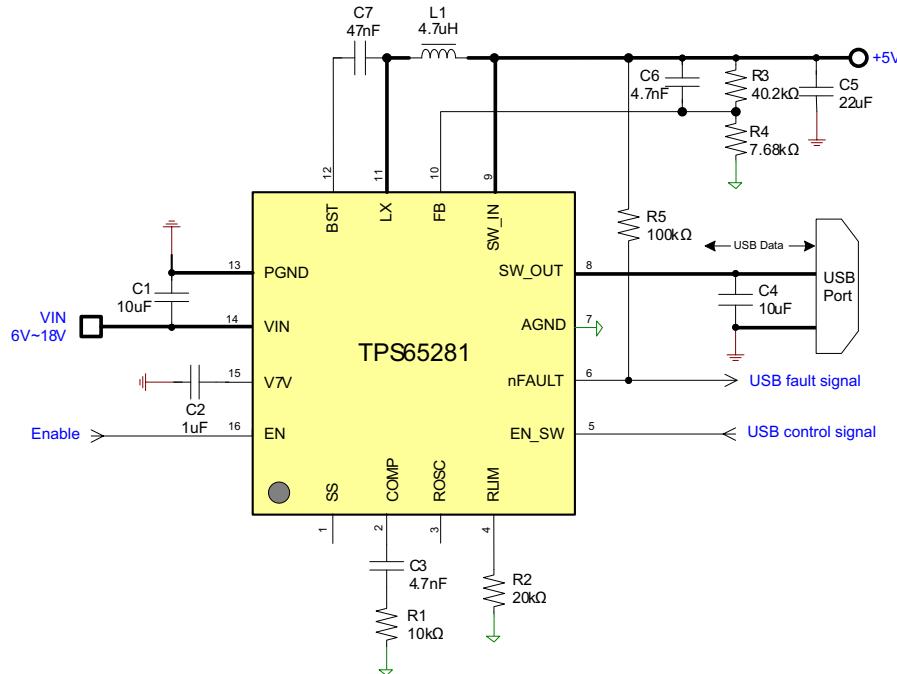

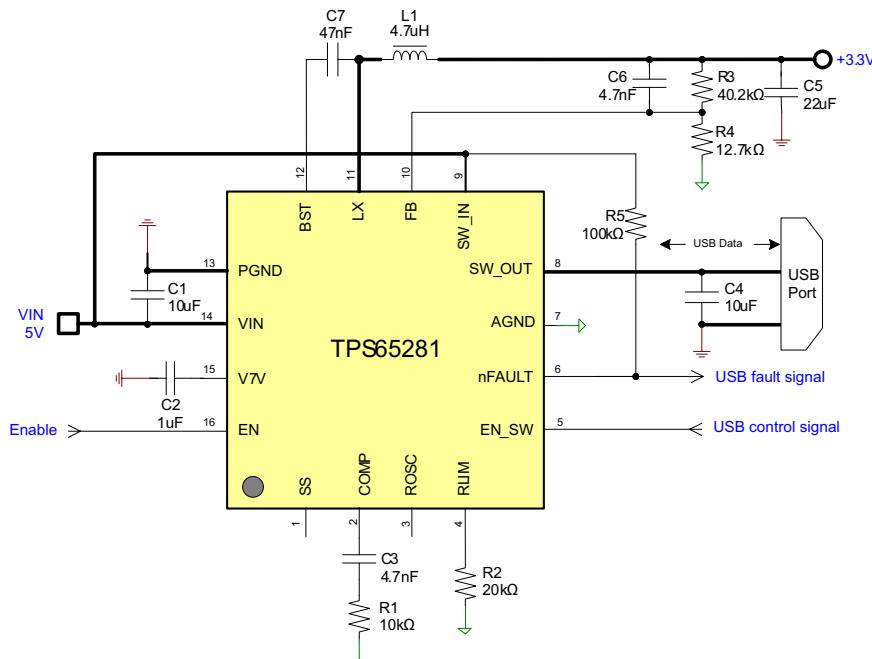

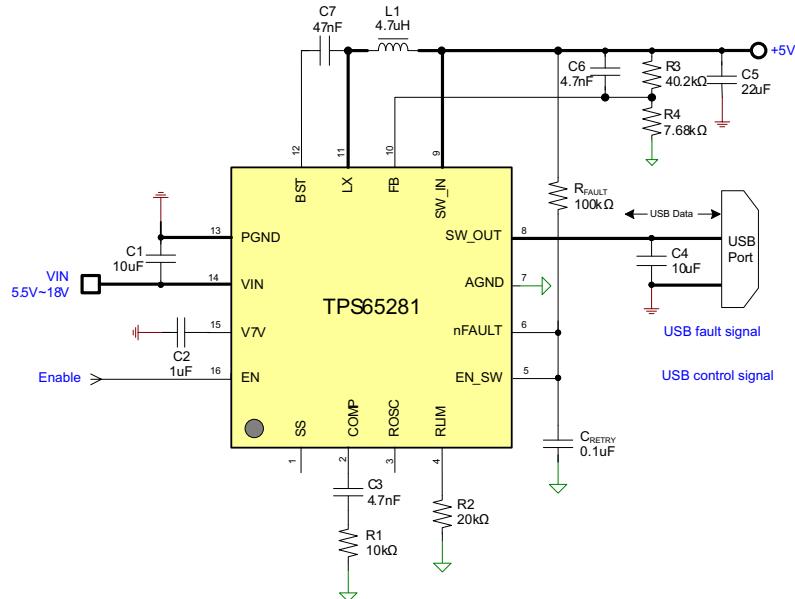

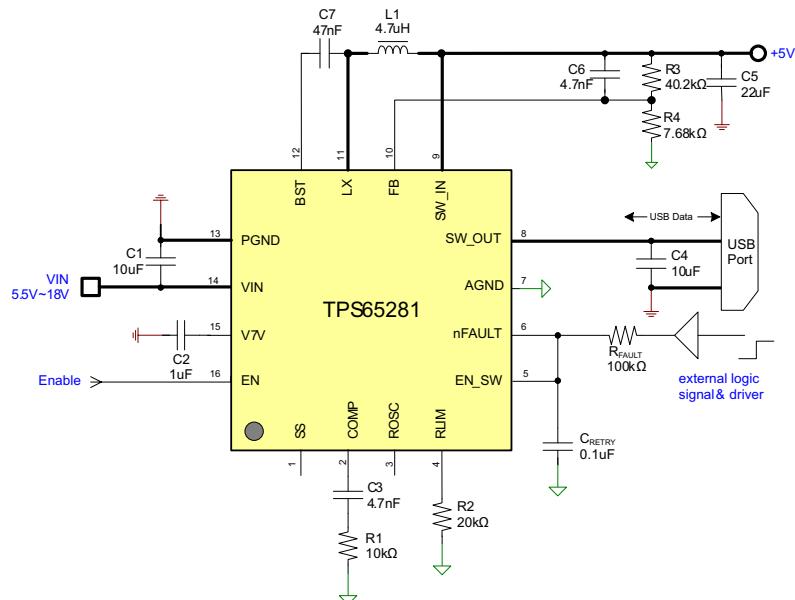

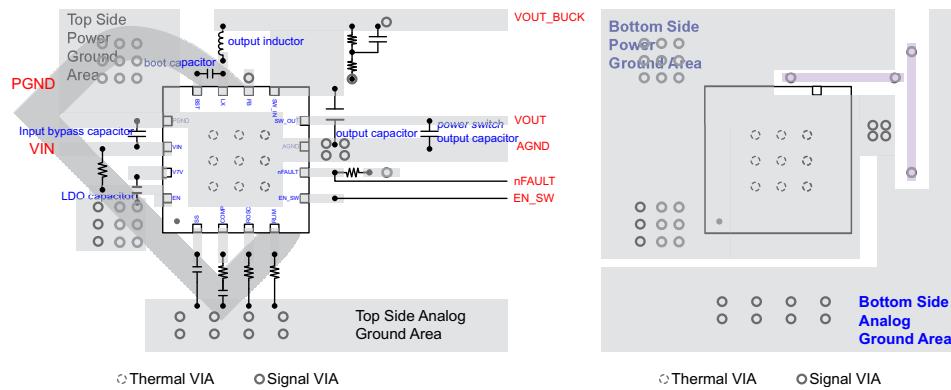

### TYPICAL APPLICATION

**Figure 1. 12-V Power Bus**

**Figure 2. 5-V Power Bus**

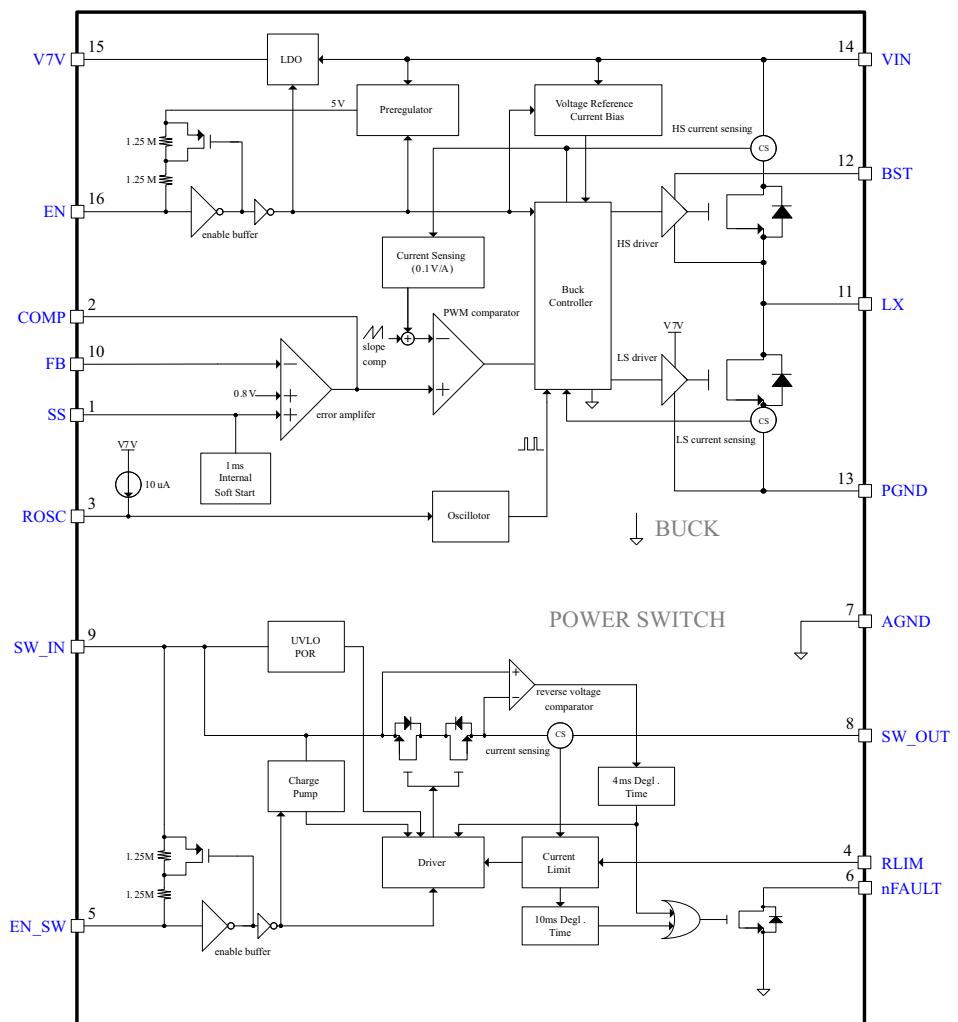

### FUNCTION BLOCK DIAGRAM

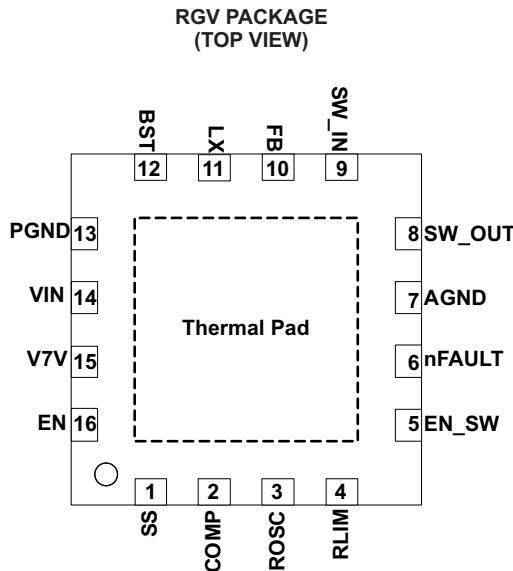

**PIN OUT**

Exposed thermal pad must be soldered to PCB for optimal thermal performance.

**TERMINAL FUNCTIONS**

| NAME      | NO. | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SS        | 1   | Soft-start and tracking input for buck converter. An internal 5- $\mu$ A current source is connected to this pin. An external soft-start can be programmed by connecting a capacitor between this pin and ground. Leave the pin floating to have a default 1-ms of soft-start time. This pin allows the start-up of buck output to track an external voltage using an external resistor divider at this pin.                                                                                                     |

| COMP      | 2   | Error amplifier output and Loop compensation pin for buck. Connect a series RC to compensate the control loop of buck converter.                                                                                                                                                                                                                                                                                                                                                                                 |

| ROSC      | 3   | Oscillator clock frequency control pin. Connect the pin to ground for a fixed 300-kHz switching frequency. Connect the pin to V <sub>7V</sub> or float the pin for a fixed 600-kHz switching frequency. Other switch frequencies between 300 kHz to 1.4 MHz can be programmed using a resistor connected from this pin to ground. A internal 10- $\mu$ A pull-up current develops a voltage to be used in oscillator. Directly applying the voltage to the ROSC pin can linearly adjust the switching frequency. |

| RLIM      | 4   | Power switch current limit control pin. An external resistor used to set current limit threshold of power switch. Recommended 15 k $\Omega$ $\leq$ RLIM $\leq$ 232 k $\Omega$ .                                                                                                                                                                                                                                                                                                                                  |

| EN_SW     | 5   | Enable pin of power switch. Logic high turns on power switch. Forcing the pin below 0.4 V shuts down power switch. Not recommend floating this pin, though there is a 2.5-M $\Omega$ pull-up resistor connecting this pin.                                                                                                                                                                                                                                                                                       |

| nFAULT    | 6   | Active low open drain output, asserted in conditions when over-current happens for more than 10 ms or reverse-voltage of power switch for more than 4 ms.                                                                                                                                                                                                                                                                                                                                                        |

| AGND      | 7   | Analog ground common to buck controller and power switch controller. It must be routed separately from high current power grounds to the (-) terminal of bypass capacitor of internal V <sub>7V</sub> LDO output.                                                                                                                                                                                                                                                                                                |

| SW_OUT    | 8   | Power switch output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SW_IN     | 9   | Power switch input pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| FB        | 10  | Feedback sensing pin for buck output voltage. Connect this pin to the resistor divider of buck output. The feedback reference voltage is 0.8 V $\pm$ 1%.                                                                                                                                                                                                                                                                                                                                                         |

| LX        | 11  | Switching node connection to the internal power FETs, inductor and bootstrap capacitor for buck converter. The voltage swing at this pin is from a diode voltage below the ground up to V <sub>IN</sub> voltage.                                                                                                                                                                                                                                                                                                 |

| BST       | 12  | Bootstrapped supply to the high side floating gate driver in buck converter. Connect a capacitor (recommend 47 nF) from BST pin to LX pin.                                                                                                                                                                                                                                                                                                                                                                       |

| PGND      | 13  | Power ground connection. Connect PGND pin as close as practical to the (-) terminal of input ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                                                                  |

| VIN       | 14  | Input power supply for buck. Connect VIN pin as close as practical to the (+) terminal of a input ceramic capacitor (suggest 10 $\mu$ F).                                                                                                                                                                                                                                                                                                                                                                        |

| V7V       | 15  | Internal LDO output. The internal gate driver for low side power MOSFET and control circuits are powered from this voltage. Decouple this pin to power ground with a minimum 1- $\mu$ F ceramic capacitor. The output voltage level of LDO is regulated to typical 6.3 V for optimal conduction on-resistances of internal power MOSFETs.                                                                                                                                                                        |

| EN        | 16  | Enable for buck converter and the device. Logic high enables buck converter and bias supply to power switches. Forcing the pin below 0.4 V shuts down the entire device, reducing the quiescent current to approximate typical 7 $\mu$ A. Not recommend floating this pin. The device can be automatically started up with connecting EN pin to VIN though a 10 k $\Omega$ resistor.                                                                                                                             |

| Power PAD |     | Exposed pad beneath the IC. Connect to the ground. Always solder power pad to the board, and have as many thermal vias as possible on the PCB to enhance power dissipation. There is no ground or any other electric signal downbonded to the pad inside the IC package.                                                                                                                                                                                                                                         |

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                                                 |                                              |             |    |

|-------------------------------------------------|----------------------------------------------|-------------|----|

| VIN                                             |                                              | –0.3 to 18  | V  |

| LX (Maximum withstand voltage transient < 20ns) |                                              | –1.0 to 18  | V  |

| BST referenced to LX pin                        |                                              | –0.3 to 7   | V  |

| SW_IN, SW_OUT                                   |                                              | –0.3 to 7   | V  |

| EN, EN_SW, nFAULT, V7V, ROSC, RLIM              |                                              | –0.3 to 7   | V  |

| SS, COMP, FB                                    |                                              | –0.3 to 3.6 | V  |

| AGND, PGND                                      |                                              | –0.3 to 0.3 | V  |

| T <sub>J</sub>                                  | Operating virtual junction temperature range | –40 to 125  | °C |

| T <sub>STG</sub>                                | Storage temperature range                    | –55 to 150  | °C |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                |                         | MIN | NOM | MAX | UNIT |

|----------------|-------------------------|-----|-----|-----|------|

| VIN            | Input operating voltage | 4.5 | 18  |     | V    |

| T <sub>A</sub> | Ambient temperature     | –40 | 85  |     | °C   |

## ELECTROSTATIC DISCHARGE (ESD) PROTECTION<sup>(1)</sup>

|                           |  | MIN  | MAX | UNIT |

|---------------------------|--|------|-----|------|

| Human body model (HBM)    |  | 4000 |     | V    |

| Charge device model (CDM) |  | 500  |     | V    |

| Machine model (MM)        |  | 200  |     | V    |

(1) SW\_OUT pin human body model (HBM) ESD protection rating 4 kV, and machine model (MM) rating 200V.

## THERMAL INFORMATION

| THERMAL METRIC <sup>(1)</sup> | TPS65281/TPS65281-1                                         | UNITS |

|-------------------------------|-------------------------------------------------------------|-------|

|                               | RGV                                                         |       |

|                               | 16 PINS                                                     |       |

| θ <sub>JA</sub>               | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 36.5  |

| θ <sub>JCTop</sub>            | Junction-to-case (top) thermal resistance <sup>(3)</sup>    | 42.7  |

| θ <sub>JB</sub>               | Junction-to-board thermal resistance <sup>(4)</sup>         | 14.7  |

| ψ <sub>JT</sub>               | Junction-to-top characterization parameter <sup>(5)</sup>   | 0.5   |

| ψ <sub>JB</sub>               | Junction-to-board characterization parameter <sup>(6)</sup> | 14.8  |

| θ <sub>JCbot</sub>            | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | 3.3   |

(1) For more information about traditional and new thermal metrics, see the *IC Package Thermal Metrics* application report, [SPRA953](#).

(2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

(3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

(4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

(5) The junction-to-top characterization parameter, ψ<sub>JT</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

(6) The junction-to-board characterization parameter, ψ<sub>JB</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

(7) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

## ELECTRICAL CHARACTERISTICS

$T_J = 25^\circ\text{C}$ ,  $V_{IN} = 12\text{ V}$ ,  $f_{SW} = 600\text{ kHz}$ ,  $R_{nFAULT} = 100\text{ k}\Omega$  (unless otherwise noted)

| PARAMETER                        | TEST CONDITIONS                                                                                                    | MIN                                                                                                     | TYP   | MAX  | UNIT             |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------|------|------------------|

| <b>INPUT SUPPLY</b>              |                                                                                                                    |                                                                                                         |       |      |                  |

| $V_{IN}$                         | Input voltage range                                                                                                |                                                                                                         | 4.5   | 18   | V                |

| $IDD_{SDN}$                      | Shutdown supply current                                                                                            | EN = EN_SW = low                                                                                        |       | 7    | $\mu\text{A}$    |

| $IDD_{Q\_NSW}$                   | Switching quiescent current with no load at DCDC output                                                            | EN = high, EN_SW = low, FB = 6 V<br>With Buck not switching                                             |       | 0.8  | mA               |

| $IDD_{Q\_SW}$                    | Switching quiescent current with no load at DCDC output, Buck switching                                            | EN = high, EN_SW = low, FB = 5 V<br>With Buck switching                                                 |       | 13   | mA               |

| UVLO                             | $V_{IN}$ under voltage lockout                                                                                     | Rising $V_{IN}$                                                                                         | 4.10  | 4.30 | 4.50             |

|                                  |                                                                                                                    | Falling $V_{IN}$                                                                                        | 3.85  | 4.10 | 4.35             |

|                                  |                                                                                                                    | Hysteresis                                                                                              |       | 0.2  |                  |

| $V_{7V}$                         | Internal biasing supply                                                                                            | $V_{7V}$ load current = 0 A,<br>$V_{IN} = 12\text{ V}$                                                  | 6.17  | 6.32 | 6.47             |

| <b>OSCILLATOR</b>                |                                                                                                                    |                                                                                                         |       |      |                  |

| $f_{SW\_BK}$                     | Switching frequency range                                                                                          | Set by external resistor ROSC                                                                           | 300   | 1400 | kHz              |

| $f_{SW}$                         | Programmable frequency                                                                                             | ROSC = 51 $\text{k}\Omega$                                                                              |       | 510  | kHz              |

|                                  |                                                                                                                    | ROSC = 140 $\text{k}\Omega$                                                                             |       | 1400 |                  |

|                                  |                                                                                                                    | ROSC floating or connected to $V_{7V}$                                                                  |       | 600  |                  |

|                                  |                                                                                                                    | ROSC connected to ground                                                                                |       | 270  |                  |

| <b>BUCK CONVERTER</b>            |                                                                                                                    |                                                                                                         |       |      |                  |

| $V_{FB}$                         | Feedback voltage                                                                                                   | $V_{COMP} = 1.2\text{ V}$ , $T_J = 25^\circ\text{C}$                                                    | 0.792 | 0.8  | 0.808            |

|                                  |                                                                                                                    | $V_{COMP} = 1.2\text{ V}$ , $T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$                            | 0.784 | 0.8  | 0.816            |

| $V_{LINEREG}$                    | Line regulation - DC                                                                                               | $I_{OUT} = 2\text{ A}$                                                                                  |       | 0.5  | %/V              |

| $V_{LOADREG}$                    | Load regulation - DC                                                                                               | $I_{OUT} = 0.3\text{ A}$ - $2.7\text{ A}$                                                               |       | 0.5  | %/A              |

| $G_{m\_EA}$                      | Error amplifier trans-conductance <sup>(1)</sup>                                                                   | $-2\text{ }\mu\text{A} < I_{COMP} < 2\text{ }\mu\text{A}$                                               |       | 500  | $\mu\text{s}$    |

| $G_{m\_SRC}$                     | COMP voltage to inductor current $G_m$ <sup>(1)</sup>                                                              | $I_{LX} = 0.5\text{ A}$                                                                                 |       | 20   | A/V              |

| $V_{ENH}$                        | EN high level input voltage                                                                                        |                                                                                                         |       | 2    | V                |

| $V_{ENL}$                        | EN low level input voltage                                                                                         |                                                                                                         |       | 0.4  | V                |

| $I_{SS}$                         | Soft-start charging current                                                                                        |                                                                                                         |       | 4.7  | $\mu\text{A}$    |

| $t_{SS\_INT}$                    | Internal soft-start time                                                                                           | SS pin open                                                                                             | 0.5   | 1    | 1.5              |

| $I_{LIMIT}$                      | Buck peak inductor current limit                                                                                   |                                                                                                         |       | 4    | A                |

| $R_{ds(on\_HS)}$                 | On resistance of high side FET in buck                                                                             | $V_{7V} = 6.3\text{ V}$ , with bond wire resistance                                                     |       | 90   | $\text{m}\Omega$ |

| $R_{ds(on\_LS)}$                 | On resistance of low side FET in buck                                                                              | $V_{IN} = 12\text{ V}$ , with bond wire resistance                                                      |       | 70   | $\text{m}\Omega$ |

| <b>POWER DISTRIBUTION SWITCH</b> |                                                                                                                    |                                                                                                         |       |      |                  |

| $V_{SW\_IN}$                     | Power switch input voltage range                                                                                   |                                                                                                         | 2.5   | 6    | V                |

| $V_{UVLO\_SW}$                   | Input under-voltage lock out                                                                                       | $V_{SW\_IN}$ rising                                                                                     | 2.15  | 2.25 | 2.35             |

|                                  |                                                                                                                    | $V_{SW\_IN}$ falling                                                                                    | 2.08  | 2.13 | 2.28             |

|                                  |                                                                                                                    | Hysteresis                                                                                              |       | 120  | mV               |

| $R_{DS(on\_SW)}$                 | Power switch NDMOS on-resistance                                                                                   | $V_{SW\_IN} = 5\text{ V}$ , $I_{SW\_OUT} = 0.5\text{ A}$ , including bond wire resistance               |       | 100  | $\text{m}\Omega$ |

|                                  |                                                                                                                    | $V_{SW\_IN} = 2.5\text{ V}$ , $I_{SW\_OUT} = 0.5\text{ A}$ , includes bond wire resistance              |       | 100  |                  |

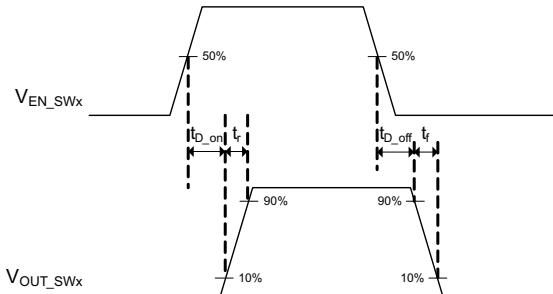

| $t_{D\_on}$                      | Turn-on delay time from EN_SW turns high                                                                           |                                                                                                         |       | 1.4  | ms               |

| $t_{D\_off}$                     | Turn-off delay time from EN_SW turns low                                                                           | $V_{SW\_IN} = 5\text{ V}$ , $C_L = 22\text{ }\mu\text{F}$ , $R_L = 100\text{ }\Omega$<br>(see Figure 3) |       | 1.2  | ms               |

| $t_r$                            | Output rise time                                                                                                   |                                                                                                         |       | 1.3  | 1.5              |

| $t_f$                            | Output fall time                                                                                                   |                                                                                                         |       | 5    | 10               |

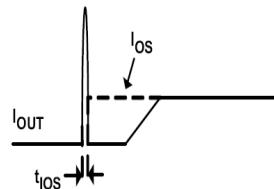

| $I_{OS}$                         | Current limit threshold (maximum DC current delivered to load) and short circuit current, SW_OUT connect to ground | $R_{LIM} = 14.3\text{ k}\Omega$                                                                         | 1.65  | 1.76 | 1.87             |

|                                  |                                                                                                                    | $R_{LIM} = 20\text{ k}\Omega$                                                                           | 1.18  | 1.26 | 1.34             |

|                                  |                                                                                                                    | $R_{LIM} = 50\text{ k}\Omega$                                                                           | 0.47  | 0.5  | 0.53             |

|                                  |                                                                                                                    | RLIM shorted to SW_IN or open                                                                           | 1.12  | 1.2  | 1.28             |

| $t_{ios}$                        | Response time to short circuit                                                                                     | $V_{SW\_IN} = 5\text{ V}$                                                                               |       | 2    | us               |

(1) Specified by design.

## ELECTRICAL CHARACTERISTICS (continued)

$T_J = 25^\circ\text{C}$ ,  $V_{IN} = 12\text{ V}$ ,  $f_{SW} = 600\text{ kHz}$ ,  $R_{nFAULT} = 100\text{ k}\Omega$  (unless otherwise noted)

| PARAMETER               | TEST CONDITIONS                                                               | MIN | TYP | MAX | UNIT             |

|-------------------------|-------------------------------------------------------------------------------|-----|-----|-----|------------------|

| $t_{DEGLITCH(OCP)}$     | Switch over current fault deglitch                                            | 7   | 10  | 13  | ms               |

| $V_{L\_nFAULT}$         | $nFAULT$ pin output low voltage                                               |     | 80  |     | mV               |

| $V_{EN\_SWH}$           | EN_SW high level input voltage                                                | 2   |     |     | V                |

| $V_{EN\_SWL}$           | EN_SW low level input voltage                                                 |     | 0.4 |     | V                |

| $R_{DIS}$               | Discharge resistance                                                          |     | 100 |     | $\Omega$         |

| <b>THERMAL SHUTDOWN</b> |                                                                               |     |     |     |                  |

| $T_{TRIP\_BUCK}$        | Thermal protection trip point                                                 | 160 |     |     | $^\circ\text{C}$ |

| $T_{HYST\_BUCK}$        | Thermal protection hysteresis                                                 | 20  |     |     | $^\circ\text{C}$ |

| $T_{TRIP\_SW}$          | Power switch thermal protection trip point in current limit (TPS65281-1 only) | 145 |     |     | $^\circ\text{C}$ |

| $T_{HYST\_SW}$          | Hysteresis                                                                    | 10  |     |     | $^\circ\text{C}$ |

Figure 3. Power Switches Test Circuit and Voltage Waveforms

Figure 4. Response Time to Short Circuit Waveform

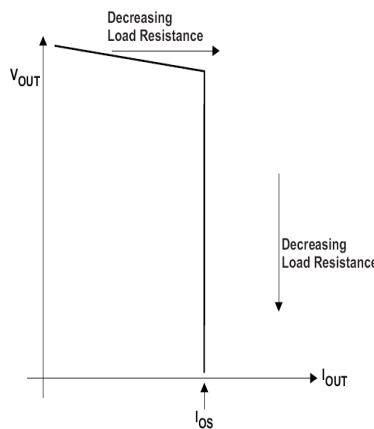

Figure 5. Output Voltage vs Current Limit Threshold

### TYPICAL CHARACTERISTICS

$T_J = 25^\circ\text{C}$ ,  $V_{IN} = 12\text{ V}$ ,  $f_{SW} = 600\text{ kHz}$ ,  $R_{nFAULT} = 100\text{ k}\Omega$  (unless otherwise noted)

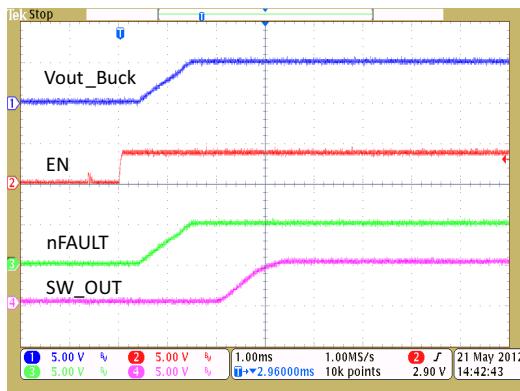

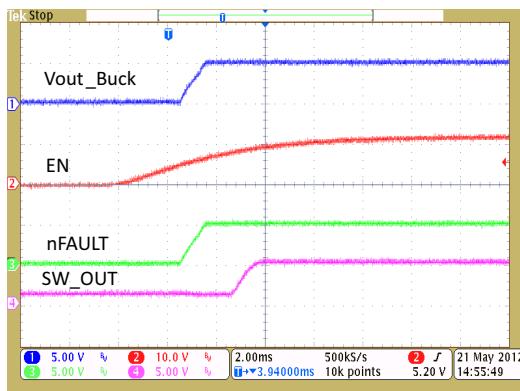

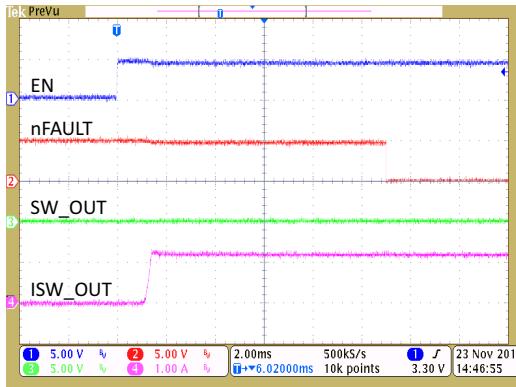

Figure 6. Power Up by EN Pin

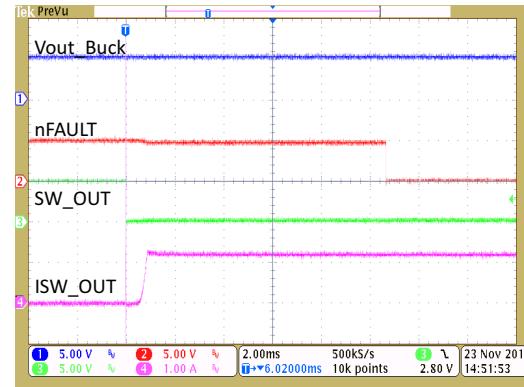

Figure 7. Power Down by EN Pin

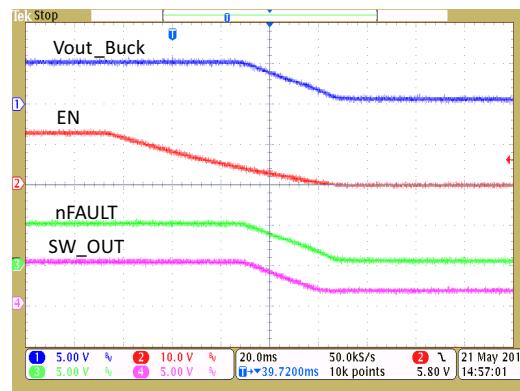

Figure 8. Power Up by  $V_{IN}$

(EN pin connects to  $V_{IN}$  with a  $10\text{-k}\Omega$  resistor)

Figure 9. Power Down by  $V_{IN}$

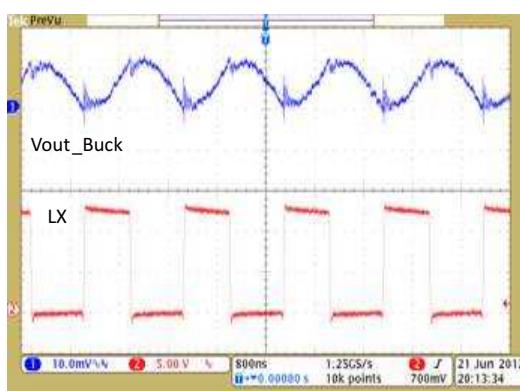

Figure 10.  $V_{OUT}$  Ripple and  $L_X$

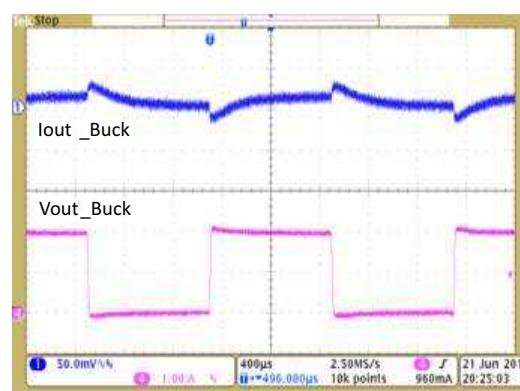

Figure 11. Load Transient

### TYPICAL CHARACTERISTICS (continued)

$T_J = 25^\circ\text{C}$ ,  $V_{IN} = 12\text{ V}$ ,  $f_{SW} = 600\text{ kHz}$ ,  $R_{nFAULT} = 100\text{ k}\Omega$  (unless otherwise noted)

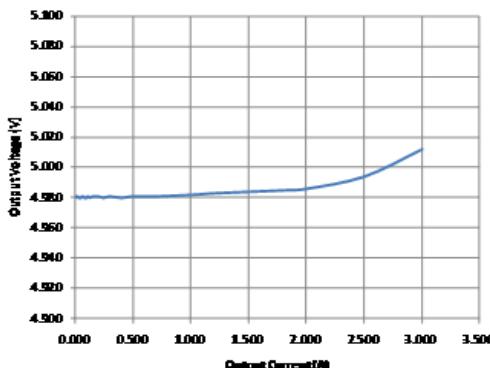

Figure 12. Buck Load Regulation

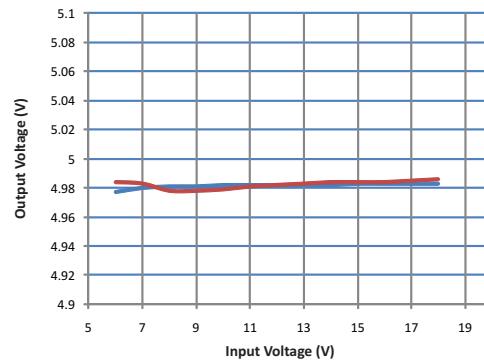

Figure 13. Buck Line Regulation

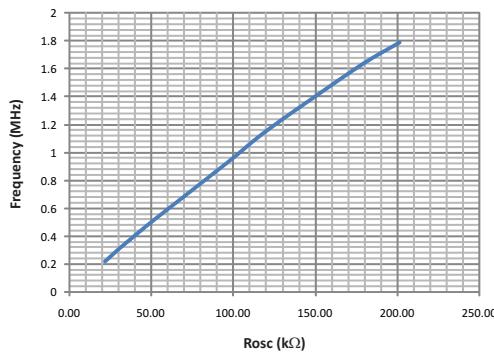

Figure 14. Oscillator Frequency vs Rosc Voltage

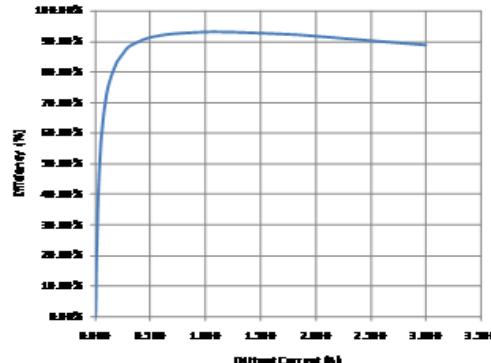

Figure 15. Buck Efficiency

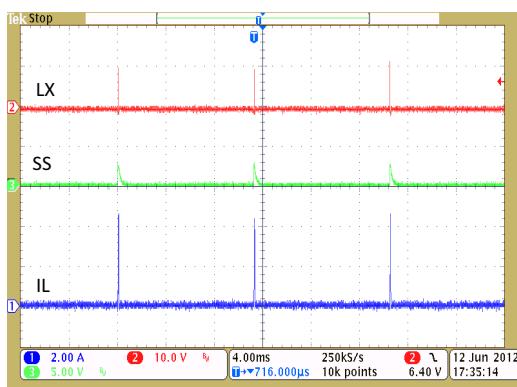

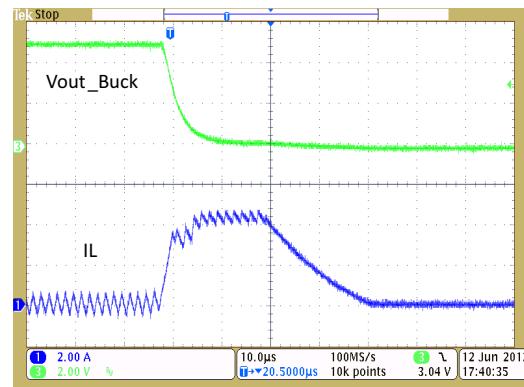

Figure 16. Buck Hiccup Response to Hard-Short Circuit

Figure 17. Zoom In Buck Output Hard Short Response

## TPS65281, TPS65281-1

SLVSBH7B – JULY 2012 – REVISED DECEMBER 2012

[www.ti.com](http://www.ti.com)

### TYPICAL CHARACTERISTICS (continued)

$T_J = 25^\circ\text{C}$ ,  $V_{IN} = 12\text{ V}$ ,  $f_{SW} = 600\text{ kHz}$ ,  $R_{nFAULT} = 100\text{ k}\Omega$  (unless otherwise noted)

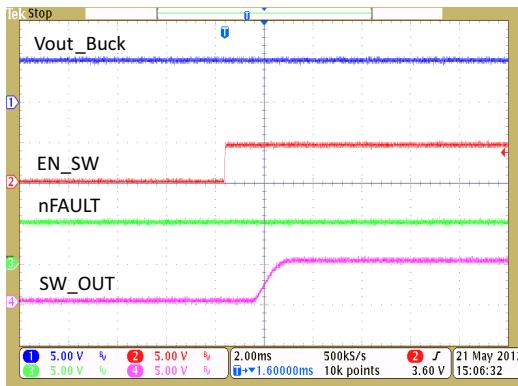

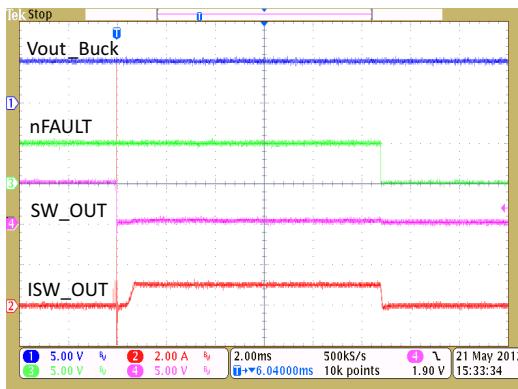

Figure 18. Power Switch Turn On Delay and Rise Time

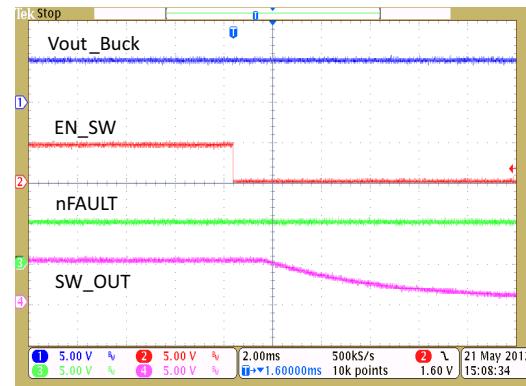

Figure 19. Power Switch Turn Off Delay and Fall Time

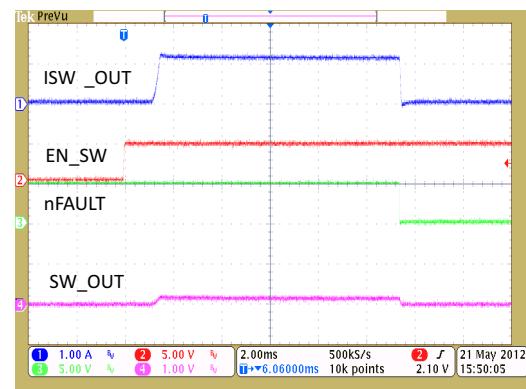

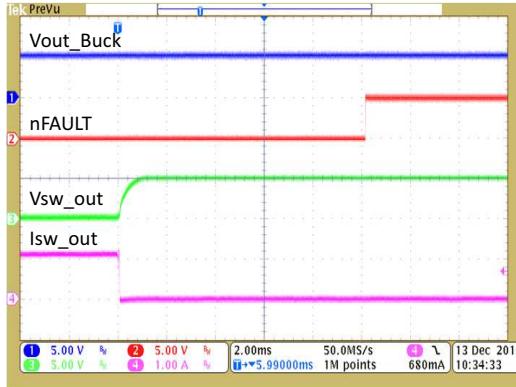

Figure 20. Power Switch Hard Short (Latch Off Version)

Figure 21. Power Switch Starts up to Short Circuit (Latch Off Version)

Figure 22. Power Switch No Load to 2-Ω Resistor (Latch Off Version)

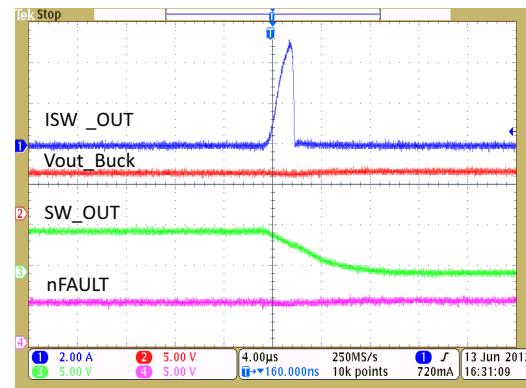

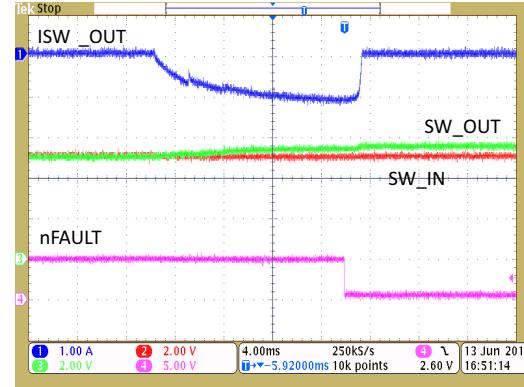

Figure 23. Power Switch Response Time ( $T_{ios}$ ) to Output Hard Short

### TYPICAL CHARACTERISTICS (continued)

$T_J = 25^\circ\text{C}$ ,  $V_{IN} = 12\text{ V}$ ,  $f_{SW} = 600\text{ kHz}$ ,  $R_{nFAULT} = 100\text{ k}\Omega$  (unless otherwise noted)

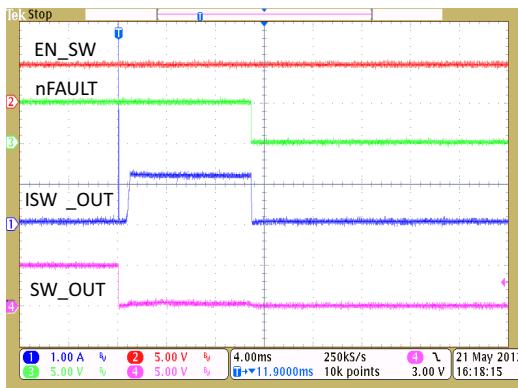

Figure 24. Power Switch Hard Short

(Auto-Recovery Version)

Figure 25. Power Switch Starts Up to Short Circuit

(Auto-Recovery Version)

Figure 26. Power Switch Recover from Over Current

(Auto-Recovery Version)

Figure 27. Power Switch Reverse Voltage Protection

Response

## OVERVIEW

TPS65281/TPS65281-1 PMIC integrates a current-limited, power distribution switch using N-channel MOSFETs for applications where short circuits or heavy capacitive loads will be encountered and provide a precision current limit protection. Additional device features include over temperature protection and reverse-voltage protection. The device incorporates an internal charge pump and gate drive circuitry necessary to drive the N-channel MOSFET. The charge pump supplies power to the driver circuit and provide the necessary voltage to pull the gate of the MOSFET above the source. The charge pump operates from input voltage of power switch as low as 2.5 V and requires little supply current. The driver incorporates circuitry that controls the rise and fall times of output voltage to limit large current and voltage surges and provides built-in soft-start functionality. TPS65281-1 device limits output current to a safe level by using a constant current mode when the output load exceeds the current limit threshold. TPS65281 device latches off when the load exceeds the current limit threshold. The device asserts the nFAULT signal during over current or reverse voltage faulty condition.

TPS65281/TPS65281-1 PMIC also integrates a synchronous step-down converter with a fixed 5-V output voltage to provide the power for power switches in the USB ports. The synchronous buck converter incorporates a 90-mΩ high side power MOSFET and 70-mΩ low side power MOSFET to achieve high efficiency power conversion. The converter supports an input voltage range from 4.5 V to 18 V. The converter operates in continuous conduction mode with peak current mode control for simplified loop compensation. The switching clock frequency can be programmed from 300 kHz to 1.4 MHz from the ROSC pin connection. The peak inductor current limit threshold is internally set at 4 A typical. The device builds in an internal 1-ms soft-start time to reduce inrush current during power-up.

## POWER SWITCH DETAILED DESCRIPTION

### Over Current Condition

The TPS65281/TPS65281-1 responds to over-current conditions on power switches by limiting the output currents to the  $I_{OCP\_SW}$  level, which is fixed internally. The load current is less than the current-limit threshold and the device does not limit current. During normal operation the N-channel MOSFET is fully enhanced, and  $V_{SW\_OUT} = V_{SW\_IN} - (I_{SW\_OUT} \times R_{ds(on\_SW)})$ . The voltage drop across the MOSFET is relatively small compared to  $V_{SW\_IN}$ , and  $V_{SW\_OUT} \approx V_{SW\_IN}$ . When an over current condition is detected, the device maintains a constant output current and reduces the output voltage accordingly. During current-limit operation, the N-channel MOSFET is no longer fully enhanced and the resistance of the device increases. This allows the device to effectively regulate the current to the current-limit threshold. The effect of increasing the resistance of the MOSFET is that the voltage drop across the device is no longer negligible ( $V_{SW\_IN} \neq V_{SW\_OUT}$ ), and  $V_{SW\_OUT}$  decreases. The amount that  $V_{SW\_OUT}$  decreases is proportional to the magnitude of the overload condition. The expected  $V_{SW\_OUT}$  can be calculated by  $I_{OS} \times R_{LOAD}$ , where  $I_{OS}$  is the current-limit threshold and  $R_{LOAD}$  is the magnitude of the overload condition.

Three possible overload conditions can occur as summarized in [Table 1](#).

**Table 1. Possible Overload Conditions**

| CONDITIONS                                                                                                        | BEHAVIORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Short circuit or partial short circuit present when the device is powered up or enabled                           | The output voltage is held near zero potential with respect to ground and the TPS65281 ramps output current to $I_{OCP\_SW}$ . The TPS65281-1 will limit the current to $I_{OS}$ until the overload condition is removed or the device begins to thermal cycle. The TPS65281 limits the current to $I_{OS}$ until the overload condition is removed or the internal deglitch time (10 ms typical) is reached and the device is turned off. The device will remain off until power is cycled or the device enable is toggled.                                                                                                                                                                                  |

| Gradually increasing load (<100 A/s) from normal operating current to $I_{OS}$                                    | The current rises until current limit. Once the threshold has been reached, the device switches into its current limiting at $I_{OS}$ . The TPS65281-1 will limit the current to $I_{OS}$ until the overload condition is removed or the device begins to thermal cycle. The TPS65281 limits the current to $I_{OS}$ until the overload condition is removed or the internal deglitch time (10 ms typical) is reached and the device is turned off. The device will remain off until power is cycled or the device enable is toggled.                                                                                                                                                                         |

| Short circuit, partial short circuit or fast transient overload occurs while the device is enabled and powered on | The device responds to the over-current condition within time $t_{IOS}$ (see <a href="#">Figure 5</a> ). The current sensing amplifier is overdriven during this time, and needs time for loop response. Once $t_{IOS}$ has passed, the current sensing amplifier recovers and limits the current to $I_{OS}$ . The TPS65281-1 will limit the current to $I_{OS}$ until the overload condition is removed or the device begins to thermal cycle. The TPS65281 limits the current to $I_{OS}$ until the overload condition is removed or the internal deglitch time (10 ms typical) is reached and the device is turned off. The device will remain off until power is cycled or the device enable is toggled. |

The TPS65281-1 thermal cycles if an overload condition is present long enough to activate thermal limiting in any of the above cases. The power switch turns off when the junction temperature exceeds 145°C (typical) while in current limit. The device remains off until the junction temperature cools 10°C (typical) and then restarts. The TPS65281-1 cycles on and off until the overload is removed.

### Reverse Current and Voltage Protection

A power switch in the TPS65281/TPS65281-1 incorporates two back-to-back N-channel power MOSFETs as to prevent the reverse current flowing back the input through body diode of MOSFET when power switches are off.

The reverse-voltage protection feature turns off the N-channel MOSFET whenever the output voltage exceeds the input voltage by 135 mV (typical) for 4 ms (typical). This prevents damage to devices on the input side of the TPS65281/TPS65281-1 by preventing significant current from sinking into the input capacitance of power switch or buck output capacitance. The TPS65281-1 device allows the N-channel MOSFET to turn on once the output voltage goes below the input voltage for the same 4-ms deglitch time. The TPS65281 device keeps the power switch turned off even if the reverse-voltage condition is removed and do not allow the N-channel MOSFET to turn on until power is cycled or the device enable is toggled. The reverse-voltage comparator also asserts the nFAULT output (active-low) after 4 ms.

### nFAULT Response

The nFAULT open-drain output is asserted (active low) during an over current, over temperature or reverse-voltage condition. The TPS65281-1 asserts the nFAULT signal until the fault condition is removed and the device resumes normal operation. The TPS65281 asserts the nFAULT signal during a fault condition and remains asserted while the part is latched-off. The nFAULT signal is de-asserted once device power is cycled or the enable is toggled and the device resumes normal operation. The TPS65281/TPS65281-1 is designed to eliminate false nFAULT reporting by using an internal delay deglitch circuit for over current (10 ms typical) and reverse-voltage (4 ms typical) conditions without the need for external circuitry. This ensures that nFAULT is not accidentally asserted due to normal operation such as starting into a heavy capacitive load. Deglitching circuitry delays entering and leaving fault conditions. Over temperature conditions are not deglitched and assert the FAULT signal immediately.

### Under-Voltage Lockup (UVLO)

The under-voltage lockout (UVLO) circuit disables the power switch until the input voltage reaches the UVLO turn-on threshold. Built-in hysteresis prevents unwanted on/off cycling due to input voltage drop from large current surges.

### Enable and Output Discharge

The logic enable EN\_SW controls the power switch, bias for the charge pump, driver, and other circuits. The supply current from power switch driver is reduced to less than 1  $\mu$ A when a logic low is present on EN\_SW. A logic high input on EN\_SW enables the driver, control circuits, and power switch. There is 2.5-M $\Omega$  pull-up resistor connecting to EN\_SW pin. After power switch is turned on, the resistor is switched to 1.25 M $\Omega$ . The enable input is compatible with both TTL and CMOS logic levels. Floating the pin is not recommended.

When enable is de-asserted, the discharge function is active. The output capacitor of power switch is discharged through an internal NMOS that has a discharge resistance of 100  $\Omega$ . Hence, the output voltage drops down to zero. The time taken for discharge is dependent on the RC time constant of the resistance and the output capacitor.

### Power Switch Input and Output Capacitance

Input and output capacitance improves the performance of the device. The actual capacitance should be optimized for the particular application. The output capacitor of buck should be placed as close to the SW\_IN and AGND if the integrated buck supply the power to power switch. For the application which input to power switch is from another supply, a 0.1- $\mu$ F or greater ceramic bypass capacitor between SW\_IN and AGND is recommended as close to the device as possible for local noise de-coupling. This precaution reduces ringing on the input due to power-supply transients. Additional capacitance may be needed on the input to reduce voltage overshoot from exceeding the absolute maximum voltage of the device during heavy transient conditions. This is especially important during bench testing when long, inductive cables are used to connect the input of power switches in the evaluation board to the bench power-supply.

Placing a high-value electrolytic capacitor on the output pin is recommended when large transient currents are expected on the output.

### Programming the Current-Limit Threshold

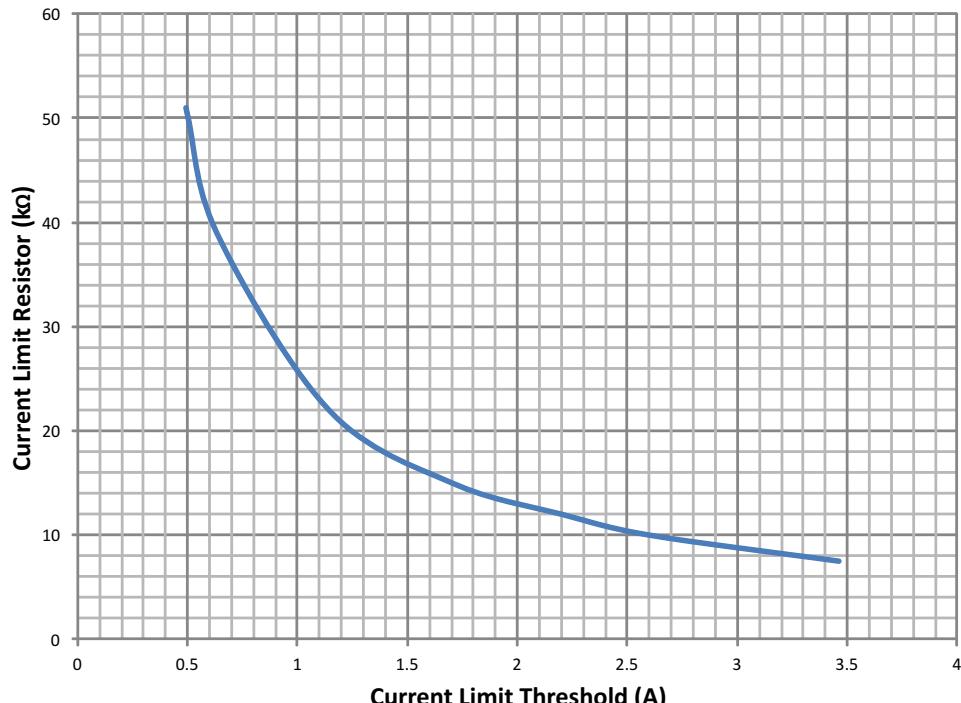

The over-current threshold is user programmable via an external resistor. The TPS65281/TPS65281-1 uses an internal regulation loop to provide a regulated voltage on the RLIM pin. The current-limit threshold is proportional to the current sourced out of RLIM. The recommended 1% resistor range for RLIM is  $5\text{ k}\Omega \leq \text{RLIM} \leq 232\text{ k}\Omega$  to ensure stability of the internal regulation loop. Many applications require that the minimum current limit is above a certain current level or that the maximum current limit is below a certain current level, so it is important to consider the tolerance of the over-current threshold when selecting a value for RLIM. The following equations and [Figure 28](#) can be used to calculate the resulting over-current threshold for a given external resistor value (RLIM). The traces routing the RLIM resistor to the TPS65281/TPS65281-1 should be as short as possible to reduce parasitic effects on the current-limit accuracy.

RLIM can be selected to provide a current-limit threshold that occurs 1) above a minimum load current or 2) below a maximum load current.

Current-Limit Threshold Equations (I<sub>OS</sub>):

$$I_{OS\max} = \left( \frac{22980 \cdot V}{RLIM^{0.94} \cdot K\Omega} \right) (\text{mA}) \quad (1)$$

$$I_{OS\text{nom}} = \left( \frac{23950 \cdot V}{RLIM^{0.977} \cdot K\Omega} \right) (\text{mA}) \quad (2)$$

$$I_{OS\min} = \left( \frac{25230 \cdot V}{RLIM^{1.016} \cdot K\Omega} \right) (\text{mA}) \quad (3)$$

Where  $15\text{ k}\Omega \leq \text{RLIM} \leq 232\text{ k}\Omega$ .

While the maximum recommended value of RLIM is 232 kΩ, there is one additional configuration that allows for a lower current-limit threshold. The RLIM pin may be connected directly to SW\_IN to provide a 1.2 A (typ) current-limit threshold. Additional low-ESR ceramic capacitance may be necessary from SW\_IN to AGND in this configuration to prevent unwanted noise from coupling into the sensitive RLIM circuitry.

**Figure 28. Current Limit Threshold (I<sub>OS</sub>) vs Current Limit Resistor (RLIM)**

## Constant-Current vs. Latch-Off Operation and Impact on Output Voltage

Both the constant-current device (TPS65281-1) and latch-off device (TPS65281) operate identically during normal operation, i.e. the load current is less than the current-limit threshold and the devices are not limiting current. During normal operation the N-channel MOSFET is fully enhanced, and  $V_{SW\_OUT} = V_{SW\_IN} - (I_{SW\_OUT} \times r_{DS(on)})$ . The voltage drop across the MOSFET is relatively small compared to  $V_{SW\_IN}$ , and  $V_{SW\_OUT} \approx V_{SW\_IN}$ .

Both the constant-current device (TPS65281-1) and latch-off device (TPS65281) operate identically during the initial onset of an over-current event. Both devices limit current to the programmed current-limit threshold set by RLIM by operating the N-channel MOSFET in the linear mode. During current-limit operation, the N-channel MOSFET is no longer fully-enhanced and the resistance of the device increases. This allows the device to effectively regulate the current to the current-limit threshold. The effect of increasing the resistance of the MOSFET is that the voltage drop across the device is no longer negligible ( $V_{SW\_IN} \neq V_{SW\_OUT}$ ), and  $V_{SW\_OUT}$  decreases. The amount that  $V_{SW\_OUT}$  decreases is proportional to the magnitude of the overload condition. The expected  $V_{SW\_OUT}$  can be calculated by  $I_{OCP\_SW} \times R_{LOAD}$ , where  $I_{OCP\_SW}$  is the current-limit threshold and  $R_{LOAD}$  is the magnitude of the overload condition.

For example, if  $I_{OCP\_SW}$  is programmed to 1 A and a 1- $\Omega$  overload condition is applied, the resulting  $V_{OUT}$  is 1 V.

While both the constant-current device (TPS65281-1) and latch-off device (TPS65281) operate identically during the initial onset of an overcurrent event, they behave differently if the overcurrent event lasts longer than the internal delay deglitch circuit (10 ms typical). The constant-current device (TPS65281-1) asserts the FAULT flag after the deglitch period and continues to regulate the current to the current-limit threshold indefinitely. In practical circuits, the power dissipation in the package will increase the die temperature above the overtemperature shutdown threshold (145°C typical), and the device will turn off until the die temperature decreases by the hysteresis of the thermal shutdown circuit (10°C typical). The device will turn on and continue to thermal cycle until the overload condition is removed. The constant-current devices resume normal operation once the overload condition is removed. The latch-off device (TPS65281) asserts the FAULT flag after the deglitch period and immediately turns off the device. The device remains off regardless of whether the overload condition is removed from the output. The latch-off device remains off and do not resume normal operation until the surrounding system either toggles the enable or cycles power to the device.

## UNIVERSAL SERIAL BUS (USB) POWER-DISTRIBUTION REQUIREMENTS

One application for this device is for current limiting in universal serial bus (USB) applications. The original USB interface was a 12-Mb/s or 1.5-Mb/s, multiplexed serial bus designed for low-to-medium bandwidth PC peripherals (e.g., keyboards, printers, scanners, and mice). As the demand for more bandwidth increased, the USB 2.0 standard was introduced increasing the maximum data rate to 480-Mb/s. The four-wire USB interface is conceived for dynamic attach-detach (hot plug-unplug) of peripherals. Two lines are provided for differential data, and two lines are provided for 5-V power distribution.

USB data is a 3.3-V level signal, but power is distributed at 5 V to allow for voltage drops in cases where power is distributed through more than one hub across long cables. Each function must provide its own regulated 3.3 V from the 5-V input or its own internal power supply. The USB specification classifies two different classes of devices depending on its maximum current draw. A device classified as low-power can draw up to 100 mA as defined by the standard. A device classified as high-power can draw up to 500 mA. It is important that the minimum current-limit threshold of the current-limiting power-switch exceed the maximum current-limit draw of the intended application. The latest USB standard should always be referenced when considering the current-limit threshold.

The USB specification defines two types of devices as hubs and functions. A USB hub is a device that contains multiple ports for different USB devices to connect and can be self-powered (SPH) or bus-powered (BPH). A function is a USB device that is able to transmit or receive data or control information over the bus. A USB function can be embedded in a USB hub. A USB function can be one of three types included in the list below.

- Low-power, bus-powered function

- High-power, bus-powered function

- Self-powered function

SPHs and BPHs distribute data and power to downstream functions. The TPS65281 has higher current capability than required for a single USB port allowing it to power multiple downstream ports.

### Self-Powered and Bus-Powered HUBs

A SPH has a local power supply that powers embedded functions and downstream ports. This power supply must provide between 4.75 V and 5.25 V to downstream facing devices under full-load and no-load conditions. SPHs are required to have current-limit protection and must report over-current conditions to the USB controller. Typical SPHs are desktop PCs, monitors, printers, and stand-alone hubs.

A BPH obtains all power from an upstream port and often contains an embedded function. It must power up with less than 100 mA. The BPH usually has one embedded function, and power is always available to the controller of the hub. If the embedded function and hub require more than 100 mA on power up, the power to the embedded function may need to be kept off until enumeration is completed. This is accomplished by removing power or by shutting off the clock to the embedded function. Power switching the embedded function is not necessary if the aggregate power draw for the function and controller is less than 100 mA. The total current drawn by the bus-powered device is the sum of the current to the controller, the embedded function, and the downstream ports, and it is limited to 500 mA from an upstream port.

### Low-Power Bus-Powered and High-Power Bus-Powered Functions

Both low-power and high-power bus-powered functions obtain all power from upstream ports. Low-power functions always draw less than 100 mA; high-power functions must draw less than 100 mA at power up and can draw up to 500 mA after enumeration. If the load of the function is more than the parallel combination of  $44\ \Omega$  and  $10\ \mu\text{F}$  at power up, the device must implement inrush current limiting.

## USB Power Distribution Requirements

USB can be implemented in several ways regardless of the type of USB device being developed. Several power-distribution features must be implemented.

SPHs must:

- Current limit downstream ports

- Report over-current conditions

BPHs must:

- Enable/disable power to downstream ports

- Power up at < 100 mA

- Limit inrush current (< 44 Ω and 10 µF)

Functions must:

- Limit inrush currents

- Power up at < 100 mA

The feature set of the TPS65281 meets each of these requirements. The integrated current limiting and over-current reporting is required by self-powered hubs. The logic-level enable and controlled rise times meet the need of both input and output ports on bus-powered hubs and the input ports for bus-powered functions.

## BUCK DC/DC CONVERTER DETAILED DESCRIPTION

### Output Voltage

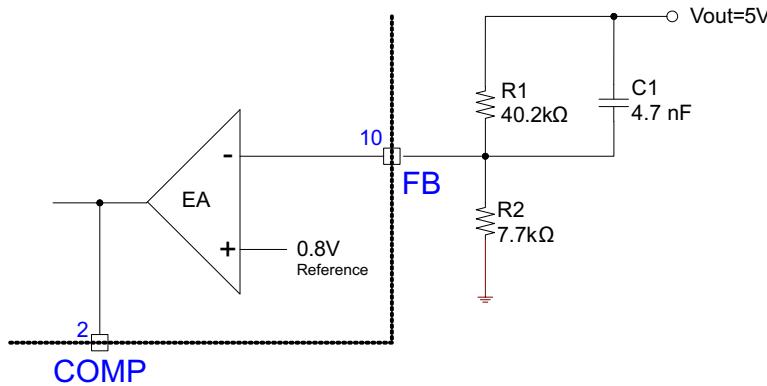

The TPS65281/TPS65281-1 regulates output voltage set by a feedback resistor divider to 0.8-V reference voltage. This pin should be directly connected to middle of resistor divider. It is recommended to use 1% tolerance or better divider resistors. Great care should be taken to route the FB line away from noise sources, such as the inductor or the LX switching node line. Start with 40.2 k $\Omega$  for the R1 resistor and use [Equation 4](#) to calculate R2.

$$R_2 = R_1 \cdot \left( \frac{0.8V}{V_{OUT} - 0.8V} \right) \quad (4)$$

**Figure 29. Buck Feedback Resistor Divider**

### Switching Frequency Selection

The selection of switching frequency is a tradeoff between efficiency and component size. Low frequency operation increases efficiency by reducing MOSFET switching losses, but requires larger inductance and capacitance to maintain low output ripple voltage. The switching frequency of the TPS65281/TPS65281-1 buck controller can be selected with the connection at ROSC pin. The ROSC pin can be connected to AGND, tied to V7V, open or programmed through an external resistor. Tying ROSC pin to AGND selects 300 kHz, while tying ROSC pin to V7V or floating ROSC pin selects 600 kHz. Placing a resistor between ROSC and AGND allows the buck switching frequency to be programmed between 300 kHz to 1.4 MHz, as shown in [Figure 14](#). The programmed clock frequency by an external resistor can be calculated with the following equation:

$$f_{SW} = 10 \times R_{osc} \quad (5)$$

### Soft-Start Time

The start-up of buck output is controlled by the voltage on the SS pin. When the voltage on the SS pin is less than the internal 0.8-V reference, the TPS65281/TPS65281-1 regulates the internal feedback voltage to the voltage on the SS pin instead of 0.8 V. The SS pin can be used to program an external soft-start function or to allow output of the buck to track another supply during start-up. The device has an internal pull-up current source of 4.7  $\mu$ A that charges an external soft-start capacitor to provide a linear ramping voltage at SS pin. The TPS65281 will regulate the internal feedback voltage according to the voltage on the SS pin, allowing  $V_{out}$  to rise smoothly from 0 V to its final regulated value. The total soft-start time will be approximately:

$$T_{SS} = C_{SS} \cdot \left( \frac{0.8 \cdot V}{4.7 \cdot \mu A} \right) \quad (6)$$

## Internal V7V Regulator

The TPS65281/TPS65281-1 features an internal P-channel low dropout linear regulator (LDO) that supplies power at the V7V pin from the VIN supply. V7V powers the gate drivers and much of the TPS65281/TPS65281-1's internal circuitry. The LDO regulates V7V to 6.3 V of over drive voltage on the power MOSFET for the best efficiency performance. The LDO can supply a peak current of 50 mA and must be bypassed to ground with a minimum 1- $\mu$ F ceramic capacitor. The capacitor placed directly adjacent to the V7V and PGND pins is highly recommended to supply the high transient currents required by the MOSFET gate drivers.

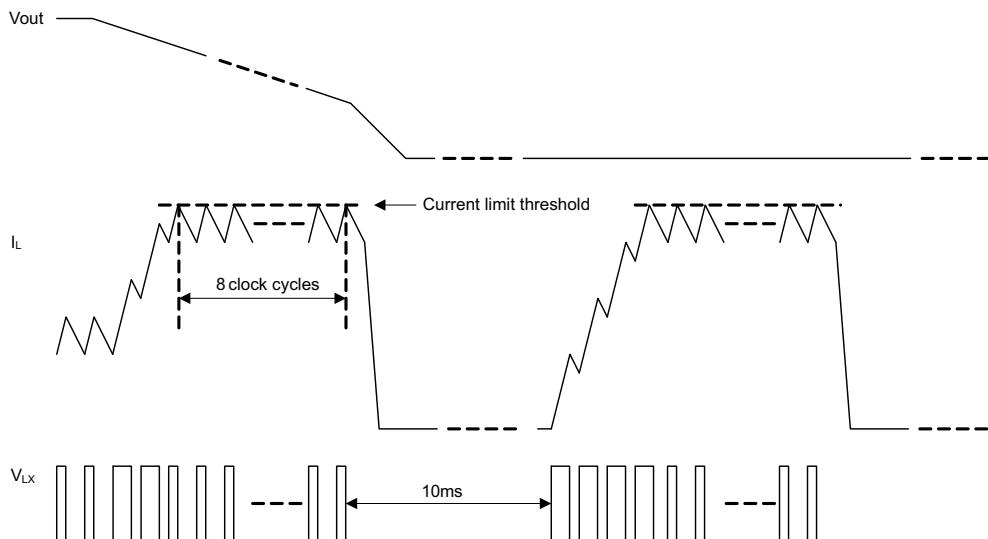

## Short Circuit Protection

During the PWM on-time, the current through the internal high side switching MOSFET is sampled. The sampled current is compared to a nominal 5-A over-current limit. If the sampled current exceeds the over-current limit reference level, an internal over-current fault counter is set to 1 and an internal flag is set. Both internal high side and low side power MOSFETs are immediately turned off and will not be turned on again until the next switching cycle. If the over-current condition persists for eight sequential clock cycles, the over-current fault counter overflows indicating an over-current fault condition exists. The buck regulator is shut down and stays turned off for 10 ms. If the over-current condition clears prior to the counter reaching eight consecutive cycles, the internal flag and counter are reset. The protection circuitry attempts to recover from the over-current condition after 10-ms power down time. The internal over-current flag and counter are reset. A normal soft-start cycle is attempted and normal operation continues if the over-current fault condition has cleared. If the over-current fault counter overflows during soft-start, the converter shuts down and this hiccup mode operation repeats.

**Figure 30. DC/DC Over-Current Protection**

## Inductor Selection

The higher operating frequency allows the use of smaller inductor and capacitor values. A higher frequency generally results in lower efficiency because of MOSFET gate charge losses. In addition to this basic trade-off, the effect of the inductor value on ripple current and low current operation must also be considered. The ripple current depends on the inductor value. The inductor ripple current,  $i_L$ , decreases with higher inductance or higher frequency and increases with higher input voltage,  $V_{IN}$ . Accepting larger values of  $i_L$  allows the use of low inductances, but results in higher output voltage ripple and greater core losses.

Use [Equation 7](#) to calculate the value of the output inductor. LIR is a coefficient that represents inductor peak-to-peak ripple to DC load current. It is suggested to use 0.1 ~ 0.3 for most LIR applications.

Actual core loss of the inductor is independent of core size for a fixed inductor value, but it is dependent on the inductance value selected. As inductance increases, core losses decrease. Unfortunately, increased inductance requires more turns of wire and therefore copper losses will increase. Ferrite designs have very low core loss and are preferred for high switching frequencies, so design goals can concentrate on copper loss and preventing saturation. Ferrite core material saturates hard, which means that inductance collapses abruptly when the peak design current is exceeded. It results in an abrupt increase in inductor ripple current and consequent output voltage ripple. Do not allow the core to saturate. It is important that the RMS current and saturation current ratings are not exceeding the inductor specification. The RMS and peak inductor current can be calculated from [Equation 9](#) and [Equation 10](#).

$$L = \frac{V_{in} - V_{out}}{I_O \cdot LIR} \cdot \frac{V_{out}}{V_{in} \cdot f_{sw}} \quad (7)$$

$$\Delta i_L = \frac{V_{in} - V_{out}}{L} \cdot \frac{V_{out}}{V_{in} \cdot f_{sw}} \quad (8)$$

$$i_{Lrms} = \sqrt{I_O^2 + \frac{(\frac{V_{out} \cdot (V_{inmax} - V_{out})}{V_{inmax} \cdot L \cdot f_{sw}})^2}{12}} \quad (9)$$

$$I_{Lpeak} = I_O + \frac{\Delta i_L}{2} \quad (10)$$

For this design example, use  $LIR = 0.3$ , and the inductor is calculated to be  $5.40 \mu\text{H}$  with  $V_{IN} = 12 \text{ V}$ ,  $V_{OUT} = 5 \text{ V}$  and  $f_{sw} = 600 \text{ kHz}$ . Choose a  $4.7 \mu\text{H}$  standard inductor, the peak to peak inductor ripple is about 34% of 3-A DC load current.

## Output Capacitor Selection

There are two primary considerations for selecting the value of the output capacitor. The output capacitors are selected to meet load transient and output ripple's requirements.

[Equation 11](#) gives the minimum output capacitance to meet the transient specification. For this example,  $L_O = 4.7 \mu\text{H}$ ,  $\Delta I_{OUT} = 3 \text{ A} - 0.0 \text{ A} = 3 \text{ A}$  and  $\Delta V_{OUT} = 500 \text{ mV}$  (10% of regulated 5 V). Using these numbers gives a minimum capacitance of  $17 \mu\text{F}$ . A standard  $22 \mu\text{F}$  ceramic capacitor is used in the design.

$$C_O > \frac{\Delta I_{OUT}^2 \cdot L}{V_{out} \cdot \Delta V_{out}} \quad (11)$$

The selection of  $C_{OUT}$  is driven by the effective series resistance (ESR). [Equation 12](#) calculates the minimum output capacitance needed to meet the output voltage ripple specification. Where  $f_{sw}$  is the switching frequency,  $\Delta V_{OUT}$  is the maximum allowable output voltage ripple, and  $\Delta i_L$  is the inductor ripple current. In this case, the maximum output voltage ripple is  $50 \text{ mV}$  (1% of regulated 5 V). From [Equation 8](#), the output current ripple is 1 A. From [Equation 12](#), the minimum output capacitance meeting the output voltage ripple requirement is  $4.6 \mu\text{F}$  with  $3\text{-m}\Omega$  esr resistance.

$$C_O > \frac{1}{8 \cdot f_{sw}} \cdot \frac{1}{\frac{\Delta V_{out}}{\Delta i_L} - \text{esr}} \quad (12)$$

After considering both requirements, for this example, one  $22 \mu\text{F}$  6.3 V X7R ceramic capacitor with  $3 \text{ m}\Omega$  of ESR will be used.

## Input Capacitor Selection

A minimum  $10 \mu\text{F}$  X7R/X5R ceramic input capacitor is recommended to be added between  $V_{IN}$  and  $GND$ . These capacitors should be connected as close as physically possible to the input pins of the converters, as they handle the RMS ripple current shown in [Equation 13](#). For this example,  $I_{OUT} = 2 \text{ A}$ ,  $V_{OUT} = 5 \text{ V}$ , minimum  $V_{in\_min} = 9.6 \text{ V}$ . The input capacitors must support a ripple current of 1 A RMS.

$$I_{inrms} = I_{out} \cdot \sqrt{\frac{V_{out}}{V_{inmin}} \cdot \frac{(V_{inmin} - V_{out})}{V_{inmin}}} \quad (13)$$

The input capacitance value determines the input ripple voltage of the regulator. The input voltage ripple can be calculated using [Equation 14](#). Using the design example values,  $I_{out\_max} = 2 \text{ A}$ ,  $C_{IN} = 10 \mu\text{F}$ ,  $f_{sw} = 600 \text{ kHz}$ , yields an input voltage ripple of 83 mV.

$$\Delta V_{in} = \frac{I_{out_{max}} \cdot 0.25}{C_{in} \cdot f_{sw}} \quad (14)$$

To prevent large voltage transients, a low ESR capacitor sized for the maximum RMS current must be used.

### Bootstrap Capacitor Selection

The external bootstrap capacitor connected to the BST pins supply the gate drive voltages for the topside MOSFETs. The capacitor between BST pin and LX pin is charged through an internal diode from V<sub>7V</sub> when the LX pin is low. When high side MOSFETs are to be turned on, the driver places the bootstrap voltage across the gate-source of the desired MOSFET. This enhances the top MOSFET switch and turns it on. The switch node voltage, LX, rises to V<sub>IN</sub> and the BST pin follows. With the internal high side MOSFET on, the bootstrap voltage is above the input supply:  $V_{BST} = V_{IN} + V_{7V}$ . The selection on bootstrap capacitance is related with internal high side power MOSFET gate capacitance. A 0.047- $\mu\text{F}$  ceramic capacitor is recommended to be connected between the BST to LX pin for proper operation. It is recommended to use a ceramic capacitor with X5R or better grade dielectric. The capacitor should have 10-V or higher voltage rating.

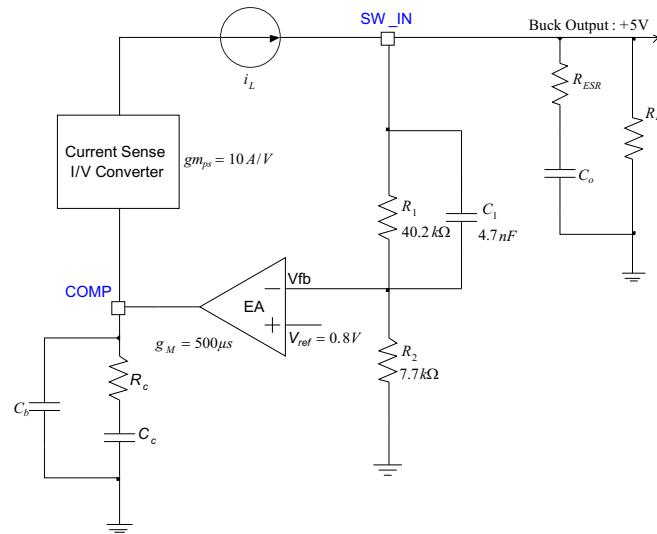

### Loop Compensation

The integrated buck DC/DC converter in TPS65281 incorporates a peak current mode. The error amplifier is a trans-conductance amplifier with a gain of 500  $\mu\text{A}/\text{V}$ . A typical type II compensation circuit adequately delivers a phase margin between 60° and 90°.  $C_b$  adds a high frequency pole to attenuate high frequency noise when needed. To calculate the external compensation components, follow these steps:

1. Select switching frequency,  $f_{sw}$ , that is appropriate for application depending on L and C sizes, output ripple and EMI. Switching frequency between 500 kHz and 1 MHz gives the best trade off between performance and cost. To optimize efficiency, a lower switching frequency is desired.

2. Set up cross over frequency,  $f_c$ , which is typically between 1/5 and 1/20 of  $f_{sw}$ .

3. RC can be determined by:

$$R_C = \frac{2\pi \cdot f_c \cdot V_o \cdot C_o}{g_M \cdot V_{ref} \cdot g_{m_{ps}}} \quad (15)$$

where  $g_m$  is the error amplifier gain (500  $\mu\text{A}/\text{V}$ ) and  $g_{m_{ps}}$  is the power stage voltage to current conversion gain (20  $\text{A}/\text{V}$ ).

4. Calculate  $C_C$  by placing a compensation zero at or before the dominant pole,  $f_p = \frac{1}{C_o \cdot R_L \cdot 2\pi}$ .

$$C_C = \frac{R_L \cdot C_o}{R_C} \quad (16)$$

5. Optional  $C_b$  can be used to cancel the zero from the ESR associated with  $C_o$ .

$$C_b = \frac{R_{esr} \cdot C_o}{R_C} \quad (17)$$

**Figure 31. DC/DC Loop Compensation**

## APPLICATION INFORMATION

### Thermal Shutdown

The device implements an internal thermal shutdown to protect itself if the junction temperature exceeds 160°C. The thermal shutdown forces the buck converter to stop switching when the junction temperature exceeds thermal trip threshold. Once the die temperature decreases below 140°C, the device reinitiates the power up sequence. The thermal shutdown hysteresis is 20°C.

### Power Dissipation and Junction Temperature

The total power dissipation inside TPS65281/TPS65281-1 should not exceed the maximum allowable junction temperature of 125°C. The maximum allowable power dissipation is a function of the thermal resistance of the package,  $\theta_{JA}$ , and ambient temperature. The analysis below gives an approximation in calculating junction temperature based on the power dissipation in the package. However, it is important to note that thermal analysis is strongly dependent on additional system level factors. Such factors include air flow, board layout, copper thickness and surface area, and proximity to other devices dissipating power. Good thermal design practice must include all system level factors in addition to individual component analysis.

To calculate the temperature inside the device under continuous load, use the following procedure.

1. Define the total continuous current through the buck converter (including the load current through power switches). Make sure the continuous current does not exceed the maximum load current requirement.

2. From the graphs below, determine the expected losses (Y axis) in Watts for the buck converter inside the device. The loss  $P_{D\_BUCK}$  depends on the input supply and the selected switching frequency. Please note, the data is measured in the provided evaluation board (EVM).

3. Determine the load current  $I_{OUT}$  through the power switch. Read  $R_{DS(on)}$  of the power switch from the Electrical Characteristics table.

4. The power loss through power switches can be calculated by:

$$P_{D\_PW} = R_{DS(on)} \times I_{OUT} \quad (18)$$

5. The Dissipating Rating Table provides the thermal resistance,  $\theta_{JA}$ , for specific packages and board layouts.

6. The maximum temperature inside the IC can be calculated by:

$$T_J = P_{D\_BUCK} + P_{D\_PW} \times \theta_{JA} + T_A \quad (19)$$

Where:

$T_A$  = Ambient temperature (°C)

$\theta_{JA}$  = Thermal resistance (°C/W)

$P_{D\_BUCK}$  = Total power dissipation in buck converter (W)

$P_{D\_PW}$  = Total power dissipation in power switches (W)

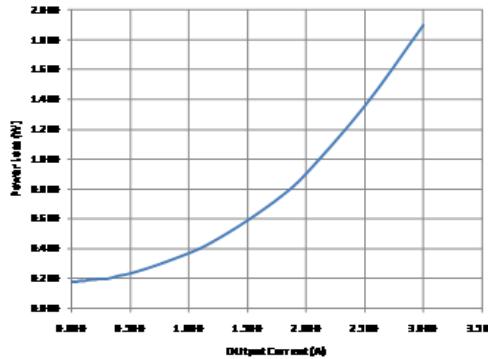

**Figure 32. Buck Power Loss vs Output Current**

$V_{IN} = 12$  V,  $f_{SW} = 600$  kHz

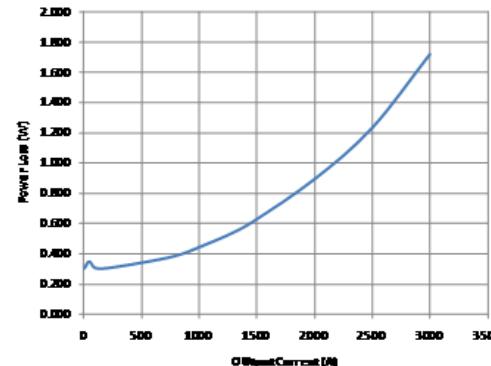

**Figure 33. Buck Power Loss vs Output Current**

$V_{IN} = 12$  V,  $f_{SW} = 300$  kHz

## Auto-Retry Functionality

Some applications require that an over-current condition disables the part momentarily during a fault condition and re-enables after a pre-set time. This auto-retry functionality can be implemented with an external resistor and capacitor shown in Figure 34. During a fault condition, nFAULT pulls low disabling the part. The part is disabled when EN is pulled low, and nFAULT goes high impedance allowing CRETRY to begin charging. The part re-enables when the voltage on EN\_SW reaches the turn-on threshold, and the auto-retry time is determined by the resistor/capacitor time constant. The part will continue to cycle in this manner until the fault condition is removed.

**Figure 34. Auto Retry Functionality**

Some applications require auto-retry functionality and the ability to enable/disable with an external logic signal. Figure 35 shows how an external logic signal can drive EN\_SW through RFAULT and maintain auto-retry functionality. The resistor/capacitor time constant determines the auto-retry time-out period.

**Figure 35. Auto Retry Functionality With External Enable Signal**

## PCB Layout Recommendation

When laying out the printed circuit board, the following guidelines should be used to ensure proper operation of the IC. These items are also illustrated graphically in the layout diagram of **Figure 36**.

- There are several signal paths that conduct fast changing currents or voltages that can interact with stray inductance or parasitic capacitance to generate noise or degrade the power supplies performance. To help eliminate these problems, the VIN pin should be bypassed to ground with a low ESR ceramic bypass capacitor with X5R or X7R dielectric. This capacitor provides the AC current into the internal power MOSFETs. Connect the (+) terminal of the input capacitor as close as possible to the VIN pin, and connect the (-) terminal of the input capacitor as close as possible to the PGND pin. Care should be taken to minimize the loop area formed by the bypass capacitor connections, the VIN pins, and the power ground PGND connections.