## **Excellent Integrated System Limited**

Stocking Distributor

Click to view price, real time Inventory, Delivery & Lifecycle Information:

Analog Devices Inc. AD9914BCPZ

For any questions, you can email us directly: sales@integrated-circuit.com

# 3.5 GSPS Direct Digital Synthesizer with 12-Bit DAC

Data Sheet AD9914

#### **FEATURES**

3.5 GSPS internal clock speed Integrated 12-bit DAC Frequency tuning resolution to 190 pHz 16-bit phase tuning resolution

12-bit amplitude scaling

Programmable modulus

Automatic linear and nonlinear frequency sweeping capability

32-bit parallel datapath interface

8 frequency/phase offset profiles

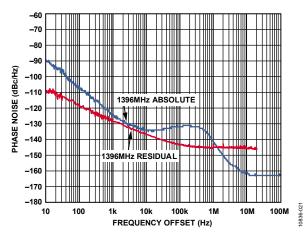

Phase noise: -128 dBc/Hz (1 kHz offset at 1396 MHz)

Wideband SFDR < -50 dBc

Serial or parallel input/output control

1.8 V/3.3 V power supplies

Software and hardware controlled power-down

88-lead LFCSP package

**PLL REF CLK multiplier**

Phase modulation capability

**Amplitude modulation capability**

#### **APPLICATIONS**

Agile LO frequency synthesis

Programmable clock generator

FM chirp source for radar and scanning systems

Test and measurement equipment

Acousto-optic device drivers

Polar modulator

Fast frequency hopping

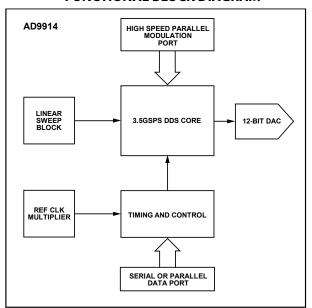

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

Datasheet of AD9914BCPZ - IC DDS 3.5GSPS DAC 12BIT 88LFCSP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

## **AD9914\* Product Page Quick Links**

Last Content Update: 08/04/2016

## Comparable Parts 🖳

View a parametric search of comparable partsView a parametric search of comparable parts

### Evaluation Kits <a> □</a>

• AD9914 Evaluation Board

## Documentation <a>□</a>

#### **Application Notes**

AN-953: Direct Digital Synthesis (DDS) with a Programmable Modulus

#### **Data Sheet**

AD9914: 3.5 GSPS Direct Digital Synthesizer with 12-Bit DAC Data Sheet

#### **User Guides**

• AD9914 Evaluation Board User Guide

### Tools and Simulations

AD9914 IBIS Model

### Reference Materials

#### **Press**

- Analog Devices Advances RF and Microwave Designs from Bits to Antenna and Back at IMS2012

- Analog Devices Unveils Industry's Fastest 12-bit, Direct Digital Synthesizers for Frequency-Agile Wireless Applications

#### **Product Selection Guide**

· RF Source Booklet

## Design Resources <a> □</a>

- · AD9914 Material Declaration

- · PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

## Discussions

View all AD9914 EngineerZone Discussions

## Sample and Buy 🖳

Visit the product page to see pricing options

## Technical Support -

Submit a technical question or find your regional support number

<sup>\*</sup> This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page (labeled "Important Links") does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.

Datasheet of AD9914BCPZ - IC DDS 3.5GSPS DAC 12BIT 88LFCSP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

## AD9914 Data Sheet

| TABLE OF CONTENTS                                             |                                                              |

|---------------------------------------------------------------|--------------------------------------------------------------|

| Features1                                                     | 12-Bit DAC Output                                            |

| Applications1                                                 | DAC Calibration Output20                                     |

| Functional Block Diagram1                                     | Reconstruction Filter                                        |

| Revision History2                                             | Clock Input (REF_CLK/REF_CLK)2                               |

| General Description3                                          | PLL Lock Indication22                                        |

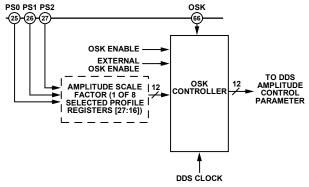

| Specifications4                                               | Output Shift Keying (OSK)22                                  |

| DC Specifications4                                            | Digital Ramp Generator (DRG)2                                |

| AC Specifications                                             |                                                              |

| Absolute Maximum Ratings 8                                    |                                                              |

| Thermal Performance                                           |                                                              |

| ESD Caution                                                   |                                                              |

| Pin Configuration and Function Descriptions                   |                                                              |

| Typical Performance Characteristics                           | 1 1                                                          |

| · -                                                           | ,                                                            |

| Equivalent Circuits                                           |                                                              |

| Theory of Operation                                           | Serial Input/Output Timing Diagrams                          |

| Single Tone Mode                                              | MSB/LSB Transfers                                            |

| Profile Modulation Mode17                                     | Parallel Programming (8-/16-Bit)                             |

| Digital Ramp Modulation Mode17                                | Register Map and Bit Descriptions                            |

| Parallel Data Port Modulation Mode17                          | Register Bit Descriptions3                                   |

| Programmable Modulus Mode17                                   | -                                                            |

| Mode Priority18                                               |                                                              |

| Functional Block Detail19                                     | 8                                                            |

| DDS Core                                                      |                                                              |

| REVISION HISTORY                                              |                                                              |

| 6/2016—Rev. E to Rev. F                                       | 7/2013—Rev. A to Rev. B                                      |

| 6/2016—Rev. E to Rev. F<br>Changes to Figure 1914             |                                                              |

| Changes to Figure 17                                          | Changes to Table 2                                           |

| 1/2016—Rev. D to Rev. E                                       | Changes to DDS Core Section                                  |

| Changes to DDS Core Section                                   | C                                                            |

| Change to Figure 3019                                         |                                                              |

| Updated Outline Dimensions45                                  |                                                              |

|                                                               | Loop Filter Components Section, and Figure 34                |

| 1/2014—Rev. C to Rev. D                                       | Change to Table 143                                          |

| Changes to Digital Timing Specifications Parameter, Table 2 5 | Changes to Bits [15:8], Table 17                             |

| Changes to Figure 2315                                        | 5                                                            |

| Change to DAC Calibration Output Section20                    | 8/2012—Rev. 0 to Rev. A                                      |

| Change to Address 0x02, Table 1434                            | Changes to Features Section                                  |

| Changes to Table 1741                                         | Changed Differential Input Voltage Unit from mV p-p to V p-p |

|                                                               | Changes to Table 14                                          |

| 11/2013—Rev. B to Rev. C                                      | Changes to Table 1640                                        |

| Changes to Table 2                                            |                                                              |

| Change to Programming and Function Pins Section30             | Updated Outline Dimensions4                                  |

Datasheet of AD9914BCPZ - IC DDS 3.5GSPS DAC 12BIT 88LFCSP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

Data Sheet AD9914

### **GENERAL DESCRIPTION**

The AD9914 is a direct digital synthesizer (DDS) featuring a 12-bit DAC. The AD9914 uses advanced DDS technology, coupled with an internal high speed, high performance DAC to form a digitally programmable, complete high frequency synthesizer capable of generating a frequency-agile analog output sinusoidal waveform at up to 1.4 GHz. The AD9914 enables fast frequency hopping and fine tuning resolution (64-bit capable using programmable modulus mode). The AD9914 also offers fast phase and amplitude hopping capability. The frequency tuning and control words are loaded into the AD9914 via a serial or

parallel input/output port. The AD9914 also supports a user defined linear sweep mode of operation for generating linear swept waveforms of frequency, phase, or amplitude. A high speed, 32-bit parallel data input port is included, enabling high data rates for polar modulation schemes and fast reprogramming of the phase, frequency, and amplitude tuning words.

The AD9914 is specified to operate over the extended industrial temperature range (see the Absolute Maximum Ratings section).

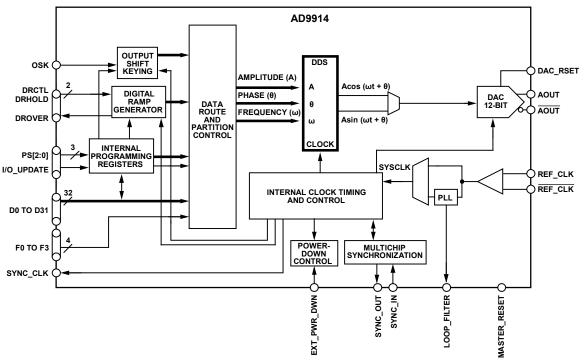

Figure 2. Detailed Block Diagram

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

Datasheet of AD9914BCPZ - IC DDS 3.5GSPS DAC 12BIT 88LFCSP

AD9914 Data Sheet

## **SPECIFICATIONS**

#### **DC SPECIFICATIONS**

AVDD (1.8 V) and DVDD (1.8 V) = 1.8 V  $\pm$  5%, AVDD (3.3 V) and DVDD\_I/O (3.3 V) = 3.3 V  $\pm$  5%,  $T_A$  = 25°C,  $R_{SET}$  = 3.3 k $\Omega$ ,  $I_{OUT}$  = 20 mA, external reference clock frequency = 3.5 GHz with reference clock (REF CLK) multiplier bypassed, unless otherwise noted.

Table 1.

| Parameter                                                | Min   | Тур  | Max      | Unit  | Test Conditions/Comments                                                                      |

|----------------------------------------------------------|-------|------|----------|-------|-----------------------------------------------------------------------------------------------|

| SUPPLY VOLTAGE                                           |       |      |          |       |                                                                                               |

| DVDD_I/O                                                 | 3.135 | 3.30 | 3.465    | V     | Pin 16, Pin 83                                                                                |

| DVDD                                                     | 1.71  | 1.80 | 1.89     | V     | Pin 6, Pin 23, Pin 73                                                                         |

| AVDD (3.3 V)                                             | 3.135 | 3.30 | 3.465    | V     | Pin 34, Pin 36, Pin 39, Pin 40, Pin 43, Pin 47, Pin 50, Pin 52, Pin 53, Pin 60                |

| AVDD (1.8 V)                                             | 1.71  | 1.80 | 1.89     | V     | Pin 32, Pin 56, Pin 57                                                                        |

| SUPPLY CURRENT                                           |       |      |          |       | See also the total power dissipation specifications                                           |

| I <sub>DVDD_I/O</sub>                                    |       |      | 20       | mA    | Pin 16, Pin 83                                                                                |

| $I_{DVDD}$                                               |       |      | 433      | mA    | Pin 6, Pin 23, Pin 73                                                                         |

| I <sub>AVDD(3.3V)</sub>                                  |       |      | 640      | mA    | Pin 34, Pin 36, Pin 39, Pin 40, Pin 43, Pin 47, Pin 50, Pin 52, Pin 53, Pin 60                |

| I <sub>AVDD(1.8V)</sub>                                  |       |      | 178      | mA    | Pin 32, Pin 56, Pin 57                                                                        |

| TOTAL POWER DISSIPATION                                  |       |      |          |       |                                                                                               |

| Base DDS Power, PLL Disabled                             |       | 2392 | 3091     | mW    | 3.5 GHz, single-tone mode, modules disabled, linear sweep disabled, amplitude scaler disabled |

| Base DDS Power, PLL Enabled                              |       | 2237 | 2627     | mW    | 2.5 GHz, single-tone mode, modules disabled, linear sweep disabled, amplitude scaler disabled |

| Linear Sweep Additional Power                            |       | 28   |          | mW    |                                                                                               |

| Modulus Additional Power                                 |       | 20   |          | mW    |                                                                                               |

| Amplitude Scaler Additional Power                        |       | 138  |          | mW    | Manual or automatic                                                                           |

| Full Power-Down Mode                                     |       | 400  | 616      | mW    | Using either the power-down and enable register or the EXT_PWR_DWN pin                        |

| CMOS LOGIC INPUTS                                        |       |      |          |       |                                                                                               |

| Input High Voltage (V <sub>IH</sub> )                    | 2.0   |      | DVDD_I/O | V     |                                                                                               |

| Input Low Voltage (V <sub>I</sub> L)                     |       |      | 0.8      | V     |                                                                                               |

| Input Current (I <sub>INH</sub> , I <sub>INL</sub> )     |       | ±60  | ±200     | μΑ    | At $V_{IN} = 0 V$ and $V_{IN} = DVDD_I/O$                                                     |

| Maximum Input Capacitance (C <sub>IN</sub> )             |       | 3    |          | pF    |                                                                                               |

| CMOS LOGIC OUTPUTS                                       |       |      |          |       |                                                                                               |

| Output High Voltage (V <sub>OH</sub> )                   | 2.7   |      | DVDD_I/O | V     | $I_{OH} = 1 \text{ mA}$                                                                       |

| Output Low Voltage (Vol)                                 |       |      | 0.4      | V     | $I_{OL} = 1 \text{ mA}$                                                                       |

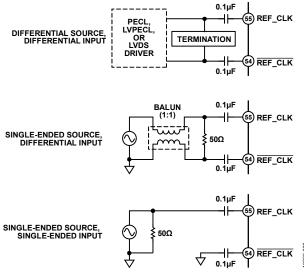

| REF CLK INPUT CHARACTERISTICS                            |       |      |          |       | REF CLK inputs must always be ac-coupled (both single-ended and differential)                 |

| REF CLK Multiplier Bypassed                              |       |      |          |       |                                                                                               |

| Input Capacitance                                        |       | 1    |          | pF    | Single-ended, each pin                                                                        |

| Input Resistance                                         |       | 1.4  |          | kΩ    | Differential                                                                                  |

| Internally Generated DC Bias<br>Voltage                  |       | 2    |          | V     |                                                                                               |

| Differential Input Voltage<br>REF CLK Multiplier Enabled |       | 0.8  | 1.5      | V p-p |                                                                                               |

| Input Capacitance                                        |       | 1    |          | pF    | Single-ended, each pin                                                                        |

| Input Resistance                                         |       | 1.4  |          | kΩ    | Differential                                                                                  |

| Internally Generated DC Bias<br>Voltage                  |       | 2    |          | V     |                                                                                               |

| Differential Input Voltage                               |       | 0.8  | 1.5      | V p-p |                                                                                               |

Datasheet of AD9914BCPZ - IC DDS 3.5GSPS DAC 12BIT 88LFCSP

Data Sheet AD9914

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

#### **AC SPECIFICATIONS**

AVDD (1.8V) and DVDD (1.8V) = 1.8 V  $\pm$  5%, AVDD3 (3.3V) and DVDD\_I/O (3.3V) = 3.3 V  $\pm$  5%,  $T_A$  = 25°C,  $R_{SET}$  = 3.3 k $\Omega$ ,  $I_{OUT}$  = 20 mA, external reference clock frequency = 3.5 GHz with reference clock (REF CLK) multiplier bypassed, unless otherwise noted.

Table 2.

| Parameter                                    | Min            | Тур  | Max            | Unit   | Test Conditions/Comments                                      |

|----------------------------------------------|----------------|------|----------------|--------|---------------------------------------------------------------|

| REF CLK INPUT                                |                |      |                |        | Input frequency range                                         |

| REF CLK Multiplier Bypassed                  |                |      |                |        |                                                               |

| Input Frequency Range                        | 500            |      | 3500           | MHz    | Maximum $f_{OUT}$ is $0.4 \times f_{SYSCLK}$                  |

| Duty Cycle                                   | 45             |      | 55             | %      |                                                               |

| Minimum Differential Input Level             | 632            |      |                | mV p-p | Equivalent to 316 mV swing on each leg                        |

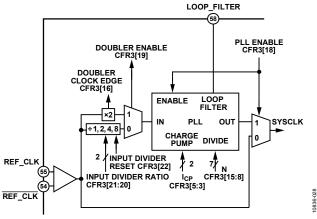

| System Clock (SYSCLK) PLL Enabled            |                |      |                |        |                                                               |

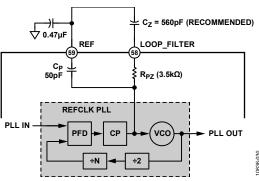

| VCO Frequency Range                          | 2400           |      | 2500           | MHz    |                                                               |

| VCO Gain (K <sub>V</sub> )                   |                | 60   |                | MHz/V  |                                                               |

| Maximum PFD Rate                             |                |      | 125            | MHz    |                                                               |

| CLOCK DRIVERS                                |                |      |                |        |                                                               |

| SYNC_CLK Output Driver                       |                |      |                |        |                                                               |

| Frequency Range                              |                |      | 146            | MHz    |                                                               |

| Duty Cycle                                   | 45             | 50   | 55             | %      |                                                               |

| Rise Time/Fall Time (20% to 80%)             |                | 650  |                | ps     |                                                               |

| SYNC_OUT Output Driver                       |                |      |                |        | 10 pF load                                                    |

| Frequency Range                              |                |      | 9.1            | MHz    |                                                               |

| Duty Cycle                                   | 33             |      | 66             | %      | CFR2 register, Bit 9 = 1                                      |

| Rise Time (20% to 80%)                       |                | 1350 |                | ps     | 10 pF load                                                    |

| Fall Time (20% to 80%)                       |                | 1670 |                | ps     | 10 pF load                                                    |

| DAC OUTPUT CHARACTERISTICS                   |                |      |                |        |                                                               |

| Output Frequency Range (1st<br>Nyquist Zone) | 0              |      | 1750           | MHz    |                                                               |

| Output Resistance                            |                | 50   |                | Ω      | Single-ended (each pin internally terminated to AVDD (3.3 V)) |

| Output Capacitance                           |                | 1    |                | pF     |                                                               |

| Full-Scale Output Current                    |                |      | 20.48          | mA     | Range depends on DAC R <sub>SET</sub> resistor                |

| Gain Error                                   | -10            |      | +10            | % FS   |                                                               |

| Output Offset                                |                |      | 0.6            | μΑ     |                                                               |

| Voltage Compliance Range                     | AVDD –<br>0.50 |      | AVDD +<br>0.50 | V      |                                                               |

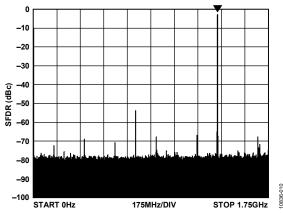

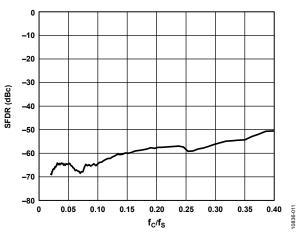

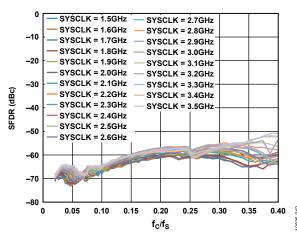

| Wideband SFDR                                |                |      |                |        | See the Typical Performance Characteristics section           |

| 101.1 MHz Output                             |                | -66  |                | dBc    | 0 MHz to 1750 MHz                                             |

| 427.5 MHz Output                             |                | -65  |                | dBc    | 0 MHz to 1750 MHz                                             |

| 696.5 MHz Output                             |                | -57  |                | dBc    | 0 MHz to 1750 MHz                                             |

| 1396.5 MHz Output                            |                | -52  |                | dBc    | 0 MHz to 1750 MHz                                             |

| Narrow-Band SFDR                             |                |      |                |        | See the Typical Performance Characteristics section           |

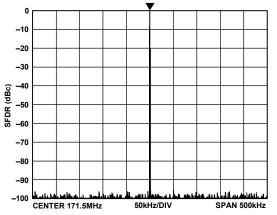

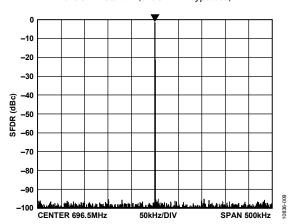

| 100.5 MHz Output                             |                | -95  |                | dBc    | ±500 kHz                                                      |

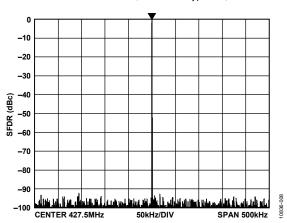

| 427.5 MHz Output                             |                | -95  |                | dBc    | ±500 kHz                                                      |

| 696.5 MHz Output                             |                | -95  |                | dBc    | ±500 kHz                                                      |

| 1396.5 MHz Output                            |                | -92  |                | dBc    | ±500 kHz                                                      |

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

#### AD9914 **Data Sheet**

| Parameter                                                    | Min | Тур | Max  | Unit            | Test Conditions/Comments                           |

|--------------------------------------------------------------|-----|-----|------|-----------------|----------------------------------------------------|

| DIGITAL TIMING SPECIFICATIONS                                |     |     |      |                 |                                                    |

| Time Required to Enter Power-Down                            |     | 45  |      | ns              | Power-down mode loses DAC/PLL calibration settings |

| Time Required to Leave Power-Down                            |     | 250 |      | ns              | Must recalibrate DAC/PLL                           |

| Minimum Master Reset time                                    | 24  |     |      | SYSCLK cycles   |                                                    |

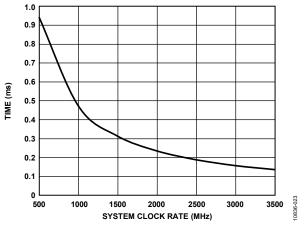

| Maximum DAC Calibration Time (t <sub>CAL</sub> )             |     |     | 135  | μs              | See the DAC Calibration Output section for formula |

| $Maximum\ PLL\ Calibration\ Time\ (t_{REF\_CLK})$            |     |     | 16   | ms              | PFD rate = 25 MHz                                  |

|                                                              |     |     | 8    | ms              | PFD rate = 50 MHz                                  |

| Maximum Profile Toggle Rate                                  |     |     | 2    | SYNC_CLK period |                                                    |

| PARALLEL PORT TIMING                                         |     |     |      |                 |                                                    |

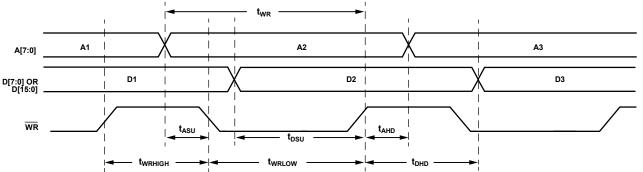

| Write Timing                                                 |     |     |      |                 |                                                    |

| Address Setup Time to $\overline{WR}$ Active                 | 1   |     |      | ns              |                                                    |

| Address Hold Time to WR Inactive                             |     |     | 0    | ns              |                                                    |

| Data Setup Time to $\overline{WR}$ Inactive                  | 3.8 |     |      | ns              |                                                    |

| Data Hold Time to $\overline{WR}$ Inactive                   |     |     | 0    | ns              |                                                    |

| WR Minimum Low Time                                          |     |     | 2.1  | ns              |                                                    |

| WR Minimum High Time                                         |     |     | 3.8  | ns              |                                                    |

| Minimum WR Time                                              |     |     | 10.5 | ns              |                                                    |

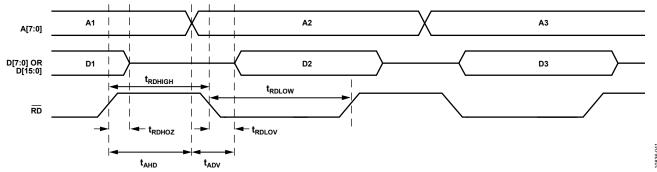

| Read Timing                                                  |     |     |      |                 |                                                    |

| Address to Data Valid                                        |     |     | 92   | ns              |                                                    |

| Address Hold to RD Inactive                                  |     |     | 0    | ns              |                                                    |

| RD Active to Data Valid                                      |     |     | 69   | ns              |                                                    |

| RD Inactive to Data Tristate                                 |     |     | 50   | ns              |                                                    |

| RD Minimum Low Time                                          |     |     | 69   | ns              |                                                    |

| RD Minimum High Time                                         |     |     | 50   | ns              |                                                    |

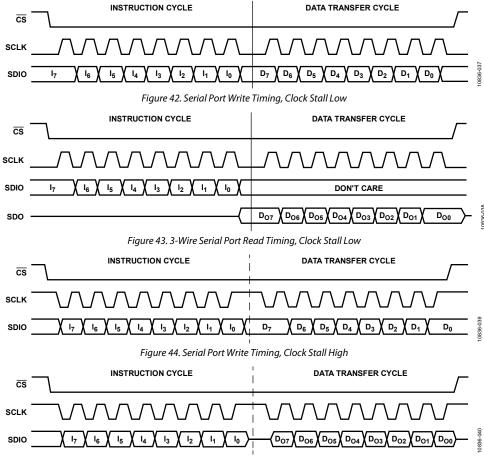

| SERIAL PORT TIMING                                           |     |     |      |                 |                                                    |

| SCLK Clock Rate (1/t <sub>CLK</sub> )                        |     |     | 80   | MHz             | SCLK duty cycle = 50%                              |

| SCLK Pulse Width High, thigh                                 | 1.5 |     | 00   | ns              | Selicately eyele 50%                               |

| SCLK Pulse Width Low, tLow                                   | 5.1 |     |      | ns              |                                                    |

| SDIO to SCLK Setup Time, t <sub>DS</sub>                     | 4.9 |     |      | ns              |                                                    |

| SDIO to SCLK Hold Time, t <sub>DH</sub>                      |     |     | 0    | ns              |                                                    |

| SCLK Falling Edge to Valid Data on SDIO/SDO, t <sub>DV</sub> |     |     | 78   | ns              |                                                    |

| CS to SCLK Setup Time, t₅                                    | 4   |     |      | ns              |                                                    |

| CS to SCLK Hold Time, t <sub>H</sub>                         |     |     | 0    | ns              |                                                    |

| CS Minimum Pulse Width High, tpwh                            | 4   |     |      | ns              |                                                    |

| DATA PORT TIMING                                             |     |     |      |                 |                                                    |

| D[31:0] Setup Time to SYNC_CLK                               | 2   |     |      | ns              |                                                    |

| D[31:0] Hold Time to SYNC_CLK                                |     |     | 0    | ns              |                                                    |

| F[3:0] Setup Time to SYNC_CLK                                | 2   |     |      | ns              |                                                    |

| F[3:0] Hold Time to SYNC_CLK                                 |     |     | 0    | ns              |                                                    |

| IO_UPDATE Pin Setup Time to<br>SYNC_CLK                      | 2   |     |      | ns              |                                                    |

| IO_UPDATE Pin Hold Time to<br>SYNC_CLK                       |     |     | 0    | ns              |                                                    |

| Profile Pin Setup Time to SYNC_CLK                           | 2   |     |      | ns              |                                                    |

| Profile Pin Hold Time to SYNC_CLK                            |     |     | 0    | ns              |                                                    |

| DR_CTL/DR_HOLD Setup Time to<br>SYNC_CLK                     | 2   |     |      | ns              |                                                    |

| DR_CTL/DR_HOLD Hold Time to SYNC_CLK                         |     |     | 0    | ns              |                                                    |

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

#### AD9914 **Data Sheet**

| Parameter                                                                  | Min Typ | Max | Unit          | Test Conditions/Comments                                       |

|----------------------------------------------------------------------------|---------|-----|---------------|----------------------------------------------------------------|

| DATA LATENCY (PIPELINE DELAY)                                              |         |     |               | SYSCLK cycles = f <sub>S</sub> = system clock frequency in GHz |

| Single Tone Mode or Profile Mode<br>(Matched Latency Disabled)             |         |     |               |                                                                |

| Frequency                                                                  | 318     |     | SYSCLK cycles | OSK disabled                                                   |

|                                                                            | 342     |     | SYSCLK cycles | OSK enabled                                                    |

| Phase                                                                      | 294     |     | SYSCLK cycles | OSK disabled                                                   |

|                                                                            | 318     |     | SYSCLK cycles | OSK enabled                                                    |

| Amplitude                                                                  | 102     |     | SYSCLK cycles | OSK enabled                                                    |

| Single Tone Mode or Profile Mode<br>(Matched Latency Enabled)              |         |     |               |                                                                |

| Frequency                                                                  | 318     |     | SYSCLK cycles | OSK disabled                                                   |

|                                                                            | 342     |     | SYSCLK cycles | OSK enabled                                                    |

| Phase                                                                      | 318     |     | SYSCLK cycles | OSK disabled                                                   |

|                                                                            | 342     |     | SYSCLK cycles | OSK enabled                                                    |

| Amplitude                                                                  | 342     |     | SYSCLK cycles | OSK enabled                                                    |

| Modulation Mode with 32-Bit<br>Parallel Port (Matched Latency<br>Disabled) |         |     |               |                                                                |

| Frequency                                                                  | 318     |     | SYSCLK cycles | OSK disabled                                                   |

|                                                                            | 342     |     | SYSCLK cycles | OSK enabled                                                    |

| Phase                                                                      | 294     |     | SYSCLK cycles | OSK disabled                                                   |

|                                                                            | 318     |     | SYSCLK cycles | OSK enabled                                                    |

| Amplitude                                                                  | 102     |     | SYSCLK cycles | OSK enabled                                                    |

| Modulation Mode with 32-Bit Parallel<br>Port (Matched Latency Enabled)     |         |     |               |                                                                |

| Frequency                                                                  | 318     |     | SYSCLK cycles | OSK disabled                                                   |

|                                                                            | 342     |     | SYSCLK cycles | OSK enabled                                                    |

| Phase                                                                      | 318     |     | SYSCLK cycles | OSK disabled                                                   |

|                                                                            | 342     |     | SYSCLK cycles | OSK enabled                                                    |

| Amplitude                                                                  | 342     |     | SYSCLK cycles | OSK enabled                                                    |

| Sweep Mode (Match Latency<br>Disabled)                                     |         |     |               |                                                                |

| Frequency                                                                  | 342     |     | SYSCLK cycles | OSK disabled                                                   |

|                                                                            | 366     |     | SYSCLK cycles | OSK enabled                                                    |

| Phase                                                                      | 318     |     | SYSCLK cycles | OSK disabled                                                   |

|                                                                            | 342     |     | SYSCLK cycles | OSK enabled                                                    |

| Amplitude                                                                  | 126     |     | SYSCLK cycles | OSK enabled                                                    |

| Sweep Mode (Match Latency<br>Enabled)                                      |         |     |               |                                                                |

| Frequency                                                                  | 342     |     | SYSCLK cycles | OSK disabled                                                   |

|                                                                            | 366     |     | SYSCLK cycles | OSK enabled                                                    |

| Phase                                                                      | 342     |     | SYSCLK cycles | OSK disabled                                                   |

|                                                                            | 366     |     | SYSCLK cycles | OSK enabled                                                    |

| Amplitude                                                                  | 366     |     | SYSCLK cycles | OSK enabled                                                    |

Datasheet of AD9914BCPZ - IC DDS 3.5GSPS DAC 12BIT 88LFCSP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

AD9914 Data Sheet

## **ABSOLUTE MAXIMUM RATINGS**

#### Table 3.

| Parameter                               | Rating          |

|-----------------------------------------|-----------------|

| AVDD (1.8 V), DVDD (1.8 V) Supplies     | 2 V             |

| AVDD (3.3 V), DVDD_I/O (3.3 V) Supplies | 4 V             |

| Digital Input Voltage                   | −0.7 V to +4 V  |

| Digital Output Current                  | 5 mA            |

| Storage Temperature Range               | −65°C to +150°C |

| Operating Temperature Range             | -40°C to +85°C  |

| Maximum Junction Temperature            | 150°C           |

| Lead Temperature (10 sec Soldering)     | 300°C           |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL PERFORMANCE

Table 4.

| Table 4.              |                                                                                            |                    |      |

|-----------------------|--------------------------------------------------------------------------------------------|--------------------|------|

| Symbol                | Description                                                                                | Value <sup>1</sup> | Unit |

| θја                   | Junction-to-ambient thermal<br>resistance (still air) per JEDEC<br>JESD51-2                | 24.1               | °C/W |

| Өлма                  | Junction-to-ambient thermal<br>resistance (1.0 m/sec airflow)<br>per JEDEC JESD51-6        | 21.3               | °C/W |

| $\theta_{\text{JMA}}$ | Junction-to-ambient thermal<br>resistance (2.0 m/sec air flow)<br>per JEDEC JESD51-6       | 20.0               | °C/W |

| $\theta_{JB}$         | Junction-to-board thermal<br>resistance (still air) per JEDEC<br>JESD51-8                  | 13.3               | °C/W |

| $\Psi_{\text{JB}}$    | Junction-to-board characterization<br>parameter (still air) per JEDEC<br>JESD51-6          | 12.8               | °C/W |

| $\theta_{\text{JC}}$  | Junction-to-case thermal resistance                                                        | 2.21               | °C/W |

| Ψл                    | Junction-to-top-of-package<br>characterization parameter (still air)<br>per JEDEC JESD51-2 | 0.23               | °C/W |

<sup>&</sup>lt;sup>1</sup> Results are from simulations. PCB is JEDEC multilayer. Thermal performance for actual applications requires careful inspection of the conditions in the application to determine if they are similar to those assumed in these calculations.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

Datasheet of AD9914BCPZ - IC DDS 3.5GSPS DAC 12BIT 88LFCSP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

Data Sheet AD9914

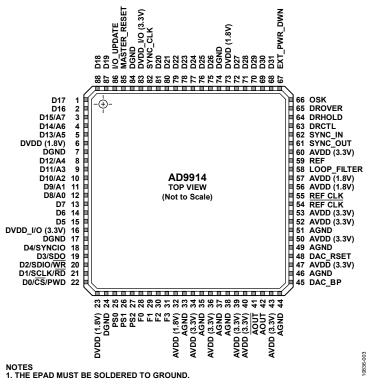

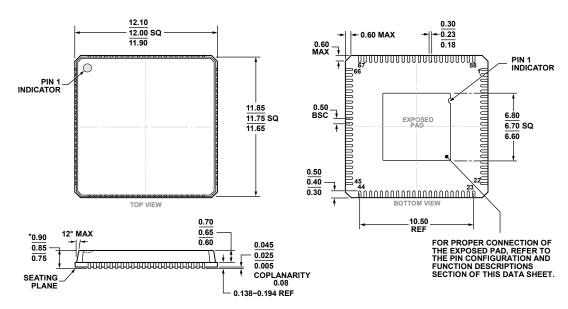

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 5. Pin Function Descriptions**

| Pin No.                                          | Mnemonic                            | I/O <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------|-------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 13 to 15, 68<br>to 72, 75 to 81,<br>87, 88 | D5 to D7, D16 to<br>D31, D27 to D31 | I/O              | Parallel Port Pins. The 32-bit parallel port offers the option for serial or parallel programming of the internal registers. In addition, the parallel port can be configured to provide direct FSK, PSK, or ASK (or combinations thereof) modulation data. The 32-bit parallel port configuration is set by the state of the four function pins (F0 to F3). |

| 3                                                | D15/A7                              | I/O              | Parallel Port Pin/Address Line. The state of the F0 to F3 function pins determines if this pin acts as a line for direct FSK, PSK, or ASK data or as an address line for programming the internal registers.                                                                                                                                                 |

| 4                                                | D14/A6                              | I/O              | Parallel Port Pin/Address Line. The state of the F0 to F3 function pins determines if this pin acts as a line for direct FSK, PSK, or ASK data or as an address line for programming the internal registers.                                                                                                                                                 |

| 5                                                | D13/A5                              | I/O              | Parallel Port Pin/Address Line. The state of the F0 to F3 function pins determines if this pin acts as a line for direct FSK, PSK, or ASK data or as an address line for programming the internal registers.                                                                                                                                                 |

| 8                                                | D12/A4                              | I/O              | Parallel Port Pin/Address Line. The state of the F0 to F3 function pins determines if this pin acts as a line for direct FSK, PSK, or ASK data or as an address line for programming the internal registers.                                                                                                                                                 |

| 9                                                | D11/A3                              | I/O              | Parallel Port Pin/Address Line. The state of the F0 to F3 function pins determines if this pin acts as a line for direct FSK, PSK, or ASK data or as an address line for programming the internal registers.                                                                                                                                                 |

| 10                                               | D10/A2                              | I/O              | Parallel Port Pin/Address Line. Multipurpose pin depending on the state of the function pins (F0 to F3). The state of the F0 to F3 function pins determines if this pin acts as a line for direct FSK, PSK, or ASK data or as an address line for programming the internal registers.                                                                        |

| 11                                               | D9/A1                               | I/O              | Parallel Port Pin/Address Line. Multipurpose pin depending on the state of the function pins (F0 to F3). The state of the F0 to F3 function pins determines if this pin acts as a line for direct FSK, PSK, or ASK data or as an address line for programming the internal registers.                                                                        |

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

Datasheet of AD9914BCPZ - IC DDS 3.5GSPS DAC 12BIT 88LFCSP

AD9914 Data Sheet

| Pin No.                                      | Mnemonic        | I/O¹ | Description                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------|-----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12                                           | D8/A0           | I/O  | Parallel Port Pin/Address Line. The state of the F0 to F3 function pins determines if this pin acts as a line for direct FSK, PSK, or ASK data or as an address line for programming the internal registers.                                                                                                                                                                                        |

| 18                                           | D4/SYNCIO       | 1    | Parallel Port Pin/Serial Port Synchronization Pin. This pin is D4 for direct FSK, PSK, or ASK data.  If serial mode is invoked via F0 to F3, this pin resets the serial port.                                                                                                                                                                                                                       |

| 19                                           | D3/SDO          | I/O  | Parallel Port Pin/Serial Data Output. This pin is D3 for direct FSK, PSK, or ASK data. If serial mode is invoked via F0 to F3, this pin is used for readback mode for serial operation.                                                                                                                                                                                                             |

| 20                                           | D2/SDIO/WR      | I/O  | Parallel Port Pin/Serial Data Input and Output/Write Input. This pin is D2 for direct FSK, PSK, or ASK data. If serial mode is invoked via F0 to F3, this pin is used for the SDIO for serial operation. If parallel mode is enabled, this pin is writes to change the values of the internal registers.                                                                                            |

| 21                                           | D1/SCLK/RD      | ı    | Parallel Port Pin/Serial Clock/Read Input. This pin is D1 for direct FSK, PSK, or ASK data. If serial mode is invoked via F0 to F3, this pin is used for SCLK for serial operation. If parallel mode is enabled, this pin reads back the value of the internal registers.                                                                                                                           |

| 22                                           | D0/CS/PWD       | I    | Parallel Port Pin/Chip Select/Parallel Width. This pin is D0 for direct FSK, PSK, or ASK data. If serial mode is invoked via F0 to F3, this pin is used for the chip select for serial operation. If parallel mode is enabled, this pin sets either 8-bit data or 16-bit data.                                                                                                                      |

| 6, 23, 73                                    | DVDD (1.8V)     | ı    | Digital Core Supplies (1.8 V).                                                                                                                                                                                                                                                                                                                                                                      |

| 7, 17, 24, 74, 84                            | DGND            | i    | Digital Ground.                                                                                                                                                                                                                                                                                                                                                                                     |

| 16, 83                                       | DVDD_I/O (3.3V) | i    | Digital Input/Output Supplies (3.3 V).                                                                                                                                                                                                                                                                                                                                                              |

| 32, 56, 57                                   | AVDD (1.8V)     | 1    | Analog Core Supplies (1.8 V).                                                                                                                                                                                                                                                                                                                                                                       |

| 33, 35, 37, 38,<br>44, 46, 49, 51            | AGND            | İ    | Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                      |

| 34, 36, 39, 40,<br>43, 47, 50, 52,<br>53, 60 | AVDD (3.3V)     | ı    | Analog DAC Supplies (3.3 V).                                                                                                                                                                                                                                                                                                                                                                        |

| 25, 26, 27                                   | PS0 to PS2      | I    | Profile Select Pins. Digital inputs (active high). Use these pins to select one of eight phase/frequency profiles for the DDS. Changing the state of one of these pins transfers the current contents of all input/output buffers to the corresponding registers. State changes must be set up on the SYNC_CLK pin (Pin 82).                                                                        |

| 28, 29, 30, 31                               | F0 to F3        | I    | Function Pins. Digital inputs. The state of these pins determines if a serial or parallel interface is used. In addition, the function pins determine how the 32-bit parallel data-word is partitioned for FSK, PSK, or ASK modulation mode.                                                                                                                                                        |

| 41                                           | AOUT            | 0    | DAC Complementary Output Source. Analog output (voltage mode). Internally connected through a 50 $\Omega$ resistor to AVDD (3.3 V).                                                                                                                                                                                                                                                                 |

| 42                                           | AOUT            | 0    | DAC Output Source. Analog output (voltage mode). Internally connected through a 50 $\Omega$ resistor to AVDD (3.3 V).                                                                                                                                                                                                                                                                               |

| 45                                           | DAC_BP          | I    | DAC Bypass Pin. Provides access to the common control node of the DAC current sources.<br>Connecting a capacitor between this pin and ground can improve noise performance at the DAC output.                                                                                                                                                                                                       |

| 48                                           | DAC_RSET        | 0    | Analog Reference. This pin programs the DAC output full-scale reference current. Connect a 3.3 k $\Omega$ resistor to AGND.                                                                                                                                                                                                                                                                         |

| 54                                           | REF_CLK         | 1    | Complementary Reference Clock Input. Analog input.                                                                                                                                                                                                                                                                                                                                                  |

| 55                                           | REF_CLK         | 1    | Reference Clock Input. Analog input.                                                                                                                                                                                                                                                                                                                                                                |

| 58                                           | LOOP_FILTER     | 0    | External PLL Loop Filter Node.                                                                                                                                                                                                                                                                                                                                                                      |

| 59                                           | REF             | 0    | Local PLL Reference Supply. Typically at 2.05 V.                                                                                                                                                                                                                                                                                                                                                    |

| 61                                           | SYNC_OUT        | 0    | Digital Synchronization Output. This pin synchronizes multiple chips.                                                                                                                                                                                                                                                                                                                               |

| 62                                           | SYNC_IN         | 1    | Digital Synchronization Input. This pin synchronizes multiple chips.                                                                                                                                                                                                                                                                                                                                |

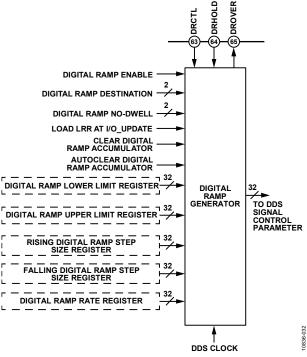

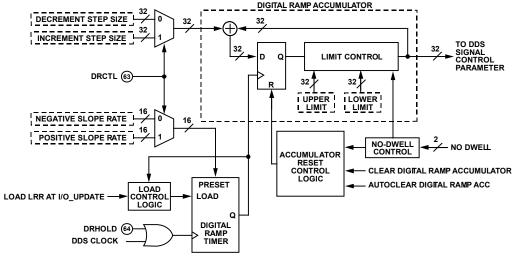

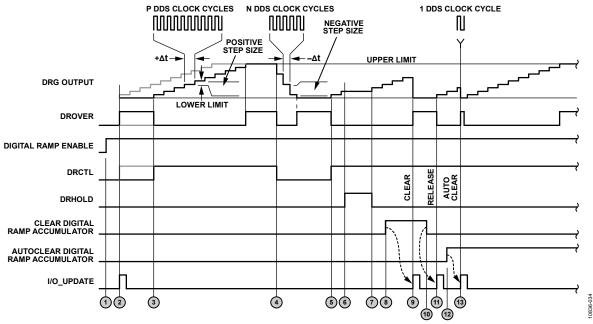

| 63                                           | DRCTL           | 1    | Ramp Control. Digital input (active high). This pin controls the sweep direction (up/down).                                                                                                                                                                                                                                                                                                         |

| 64                                           | DRHOLD          | 1    | Ramp Hold. Digital input (active high). Pauses the sweep when active.                                                                                                                                                                                                                                                                                                                               |

| 65                                           | DROVER          | 0    | Ramp Over. Digital output (active high). This pin switches to Logic 1 when the digital ramp generator reaches the programmed upper or lower limit.                                                                                                                                                                                                                                                  |

| 66                                           | OSK             | I    | Output Shift Keying. Digital input (active high). When the OSK features are placed in either manual or automatic mode, this pin controls the OSK function. In manual mode, it toggles the multiplier between 0 (low) and the programmed amplitude scale factor (high). In automatic mode, a low sweeps the amplitude down to zero and a high sweeps the amplitude up to the amplitude scale factor. |

Datasheet of AD9914BCPZ - IC DDS 3.5GSPS DAC 12BIT 88LFCSP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

## Data Sheet AD9914

| Pin No. | Mnemonic     | I/O¹ | Description                                                                                                                                                                                  |

|---------|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 67      | EXT_PWR_DWN  | 1    | External Power-Down. Digital input (active high). A high level on this pin initiates the currently programmed power-down mode.                                                               |

| 82      | SYNC_CLK     | 0    | Clock Output. Digital output. Many of the digital inputs on the chip, such as I/O_UPDATE, PS[2:0], and the parallel data port (D0 to D31), must be set up on the rising edge of this signal. |

| 85      | MASTER_RESET | I    | Master Reset. Digital input (active high). Clears all memory elements and sets registers to default values.                                                                                  |

| 86      | I/O_UPDATE   | 1    | Input/Output Update. Digital input (active high). A high on this pin transfers the contents of the input/output buffers to the corresponding internal registers.                             |

|         | EPAD         |      | Exposed Pad. The EPAD must be soldered to ground.                                                                                                                                            |

$<sup>^{1}</sup>$  I = input, O = output.

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

AD9914 Data Sheet

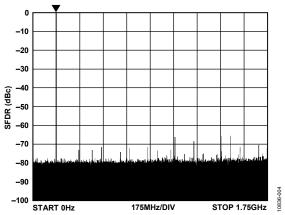

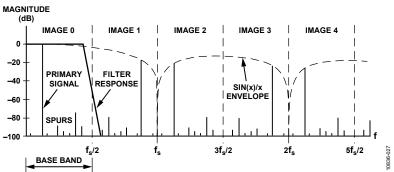

## TYPICAL PERFORMANCE CHARACTERISTICS

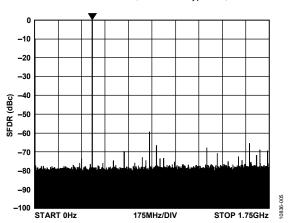

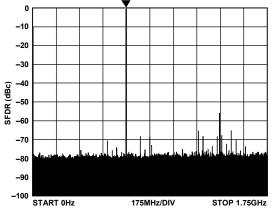

Nominal supply voltage; DAC  $R_{SET} = 3.3 \text{ k}\Omega$ ,  $T_A = 25$ °C, unless otherwise noted.

Figure 4. Wideband SFDR at 171.5 MHz SYSCLK = 3.5 GHz (SYSCLK PLL Bypassed)

Figure 5. Wideband SFDR at 427.5 MHz SYSCLK = 3.5 GHz (SYSCLK PLL Bypassed)

Figure 6. Wideband SFDR at 696.5 MHz, SYSCLK = 3.5 GHz (SYSCLK PLL Bypassed)

Figure 7. Narrow-Band SFDR at 171.5 MHz, SYSCLK = 3.5 GHz (SYSCLK PLL Bypassed)

Figure 8. Narrow-Band SFDR at 427.5 MHz, SYSCLK = 3.5 GHz (SYSCLK PLL Bypassed)

Figure 9. Narrow-Band SFDR at 696.5 MHz, SYSCLK = 3.5 GHz (SYSCLK PLL Bypassed)

Datasheet of AD9914BCPZ - IC DDS 3.5GSPS DAC 12BIT 88LFCSP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

## Data Sheet AD9914

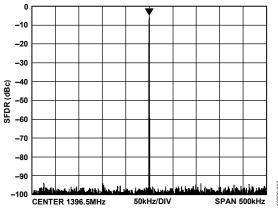

Figure 10. Wideband SFDR at 1396.5 MHz, SYSCLK = 3.5 GHz (SYSCLK PLL Bypassed)

Figure 11. Wideband SFDR vs. Normalized  $f_{OUT}$ SYSCLK = 3.5 GHz

Figure 12. Wideband SFDR vs. Normalized foυτ, SYSCLK = 2.5 GHz to 3.5 GHz

Figure 13. Narrow-Band SFDR at 1396.5 MHz, SYSCLK = 3.5 GHz (SYSCLK PLL Bypassed)

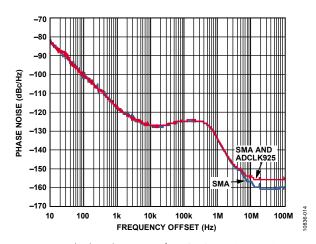

Figure 14. Absolute Phase Noise of REF CLK Source Driving AD9914 Rohde & Schwarz SMA100 Signal Generator at 3.5 GHz Buffered by Series ADCLK925

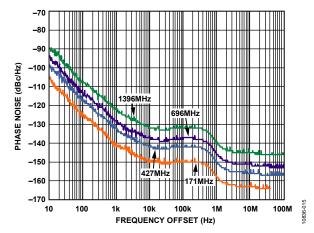

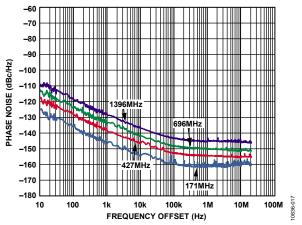

Figure 15. Absolute Phase Noise Curves of DDS Output at 3.5 GHz Operation

Datasheet of AD9914BCPZ - IC DDS 3.5GSPS DAC 12BIT 88LFCSP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

AD9914 Data Sheet

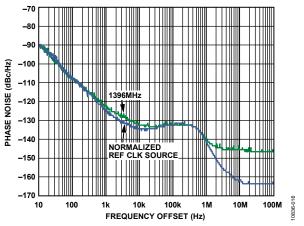

Figure 16. Absolute Phase Noise Curves of Normalized REF CLK Source to DDS Output at 1396 MHz (SYSCLK = 3.5 GHz)

Figure 17. Residual Phase Noise Curves

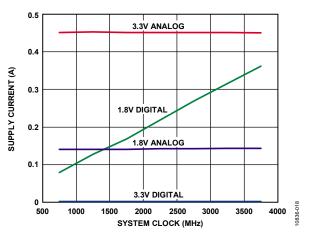

Figure 18. Power Supply Current vs. SYSCLK

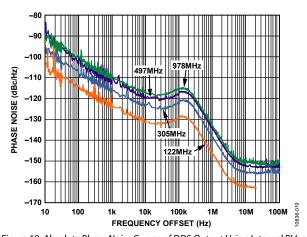

Figure 19. Absolute Phase Noise Curves of DDS Output Using Internal PLL at 2.5 GHz Operation

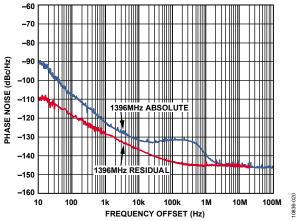

Figure 20. Residual PN vs. Absolute PN Measurement Curves at 1396 MHz

Figure 21. Residual Phase Noise vs. Normalized Absolute REF CLK Source Phase Noise at 1396 MHz

Datasheet of AD9914BCPZ - IC DDS 3.5GSPS DAC 12BIT 88LFCSP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

Data Sheet AD9914

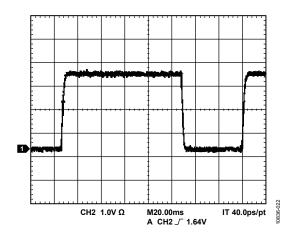

Figure 22. SYNC\_OUT (fsysclk/384)

Figure 23. DAC Calibration Time vs. SYSCLK Rate. See the DAC Calibration Output Section for Formula.

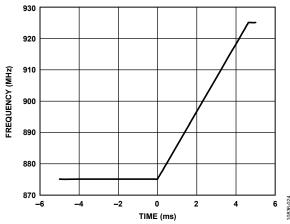

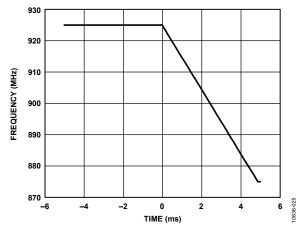

Figure 24. Measured Rising Linear Frequency Sweep

Figure 25. Measured Falling Linear Frequency Sweep

Datasheet of AD9914BCPZ - IC DDS 3.5GSPS DAC 12BIT 88LFCSP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

AD9914 Data Sheet

## **EQUIVALENT CIRCUITS**

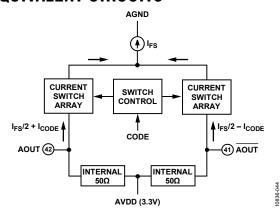

Figure 26. DAC Output

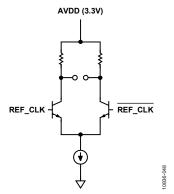

Figure 27. REF CLK input

Figure 28. CMOS Input

Figure 29. CMOS Output

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

Data Sheet AD9914

### THEORY OF OPERATION

The AD9914 has five modes of operation.

- Single tone

- Profile modulation

- Digital ramp modulation (linear sweep)

- Parallel data port modulation

- Programmable modulus mode

The modes define the data source supplies the DDS with the signal control parameters: frequency, phase, or amplitude. The partitioning of the data into different combinations of frequency, phase, and amplitude is established based on the mode and/or specific control bits and function pins.

Although the various modes are described independently, they can be enabled simultaneously. This provides an unprecedented level of flexibility for generating complex modulation schemes. However, to avoid multiple data sources from driving the same DDS signal control parameter, the device has a built-in priority protocol.

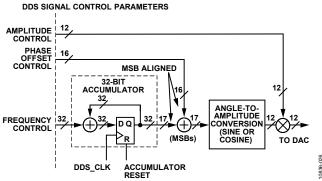

In single tone mode, the DDS signal control parameters come directly from the profile programming registers. In digital ramp modulation mode, the DDS signal control parameters are delivered by a digital ramp generator. In parallel data port modulation mode, the DDS signal control parameters are driven directly into the parallel port.

The various modulation modes generally operate on only one of the DDS signal control parameters (two in the case of the polar modulation format via the parallel data port). The unmodulated DDS signal control parameters are stored in programming registers and automatically routed to the DDS based on the selected mode.

A separate output shift keying (OSK) function is also available. This function employs a separate digital linear ramp generator that affects only the amplitude parameter of the DDS. The OSK function has priority over the other data sources that can drive the DDS amplitude parameter. As such, no other data source can drive the DDS amplitude when the OSK function is enabled.

#### **SINGLE TONE MODE**

In single tone mode, the DDS signal control parameters are supplied directly from the profile programming registers. A profile is an independent register that contains the DDS signal control parameters. Eight profile registers are available. Note that the profile pins must select the desired register.

#### **PROFILE MODULATION MODE**

Each profile is independently accessible. For FSK, PSK, or ASK modulation, use the three external profile pins (PS[2:0]) to select the desired profile. A change in the state of the profile pins with the next rising edge on SYNC\_CLK updates the DDS with the parameters specified by the selected profile. Therefore, the profile change must meet the setup and hold times to the SYNC\_CLK rising edge. Note that amplitude control must also be enabled using the OSK enable bit in the CFR1 register (0x00[8]).

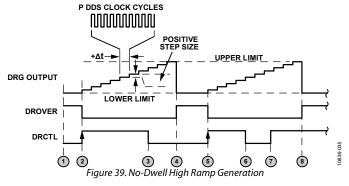

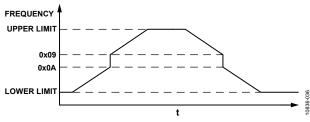

#### **DIGITAL RAMP MODULATION MODE**

In digital ramp modulation mode, the modulated DDS signal control parameter is supplied directly from the digital ramp generator (DRG). The ramp generation parameters are controlled through the serial or parallel input/output port.

The ramp generation parameters allow the user to control both the rising and falling slopes of the ramp. The upper and lower boundaries of the ramp, the step size and step rate of the rising portion of the ramp, and the step size and step rate of the falling portion of the ramp are all programmable.

The ramp is digitally generated with 32-bit output resolution. The 32-bit output of the DRG can be programmed to affect frequency, phase, or amplitude. When programmed for frequency, all 32 bits are used. However, when programmed for phase or amplitude, only the 16 MSBs or 12 MSBs, respectively, are used.

The ramp direction (rising or falling) is externally controlled by the DRCTL pin. An additional pin (DRHOLD) allows the user to suspend the ramp generator in the present state. Note that amplitude control must also be enabled using the OSK enable bit in Register CFR1.

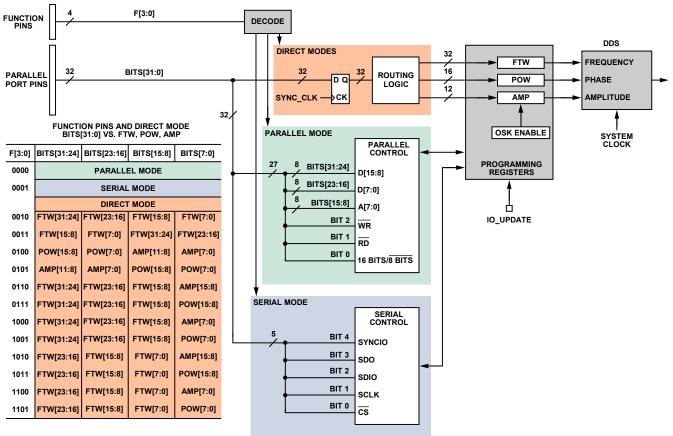

#### PARALLEL DATA PORT MODULATION MODE

In parallel data port modulation mode, the modulated DDS signal control parameter(s) are supplied directly from the 32-bit parallel data port. The function pins define how the 32-bit data-word is applied to the DDS signal control parameters. Formatting of the 32-bit data-word is unsigned binary, regardless of the destination.

#### Parallel Data Clock (SYNC\_CLK)

The AD9914 generates a clock signal on the SYNC\_CLK pin that runs at 1/24 of the DAC sample rate (the sample rate of the parallel data port). SYNC\_CLK serves as a data clock for the parallel port.

#### PROGRAMMABLE MODULUS MODE

In programmable modulus mode, the DRG is used as an auxiliary accumulator to alter the frequency equation of the DDS core, making it possible to implement fractions that are not restricted to a power of 2 in the denominator. A standard DDS is restricted to powers of 2 as a denominator because the phase accumulator is a set of bits as wide as the frequency tuning word (FTW).

When in programmable modulus mode, however, the frequency equation is:

$$f_0 = (f_S)(FTW + A/B)/2^{32}$$

where  $f_0/f_S < \frac{1}{2}$ ,  $0 \le FTW < 2^{31}$ ,  $2 \le B \le 2^{32} - 1$ , and A < B.

This equation implies a modulus of  $B \times 2^{32}$  (rather than  $2^{32}$ , in the case of a standard DDS). Furthermore, because B is programmable, the result is a DDS with a programmable modulus.

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

AD9914 Data Sheet

When in programmable modulus mode, the 32-bit auxiliary accumulator operates in a way that allows it to roll over at a value other than the full capacity of  $2^{32}$ . That is, it operates with a modified modulus based on the programmable value of B. With each roll over of the auxiliary accumulator, a value of 1 LSB adds to the current accumulated value of the 32-bit phase accumulator. This behavior changes the modulus of the phase accumulator to  $B \times 2^{32}$  (instead of  $2^{32}$ ), allowing it to synthesize the desired  $f_0$ .

To determine the programmable modulus mode register values for FTW, A, and B, the user must first define  $f_0/f_s$  as a ratio of relatively prime integers, M/N. That is, having converted  $f_0$  and  $f_s$  to integers, M and N, reduce the fraction, M/N, to the lowest terms. Then, divide M × 232 by N. The integer part of this division operation is the value of FTW (Register 0x04[31:0]). The remainder, Y, of this division operation is

$$Y = (2^{32} \times M) - (FTW \times N)$$

The value of Y facilitates the determination of A and B by taking the fraction, Y/N, and reducing it to the lowest terms. Then, the numerator of the reduced fraction is A (Register 0x06[31:0]) and the denominator is the B (Register 0x05[31:0]).

For example, synthesizing precisely 300 MHz with a 1 GHz system clock is not possible with a standard DDS. It is possible, however, using programmable modulus as follows.

First, express  $f_0/f_S$  as a ratio of integers:

300,000,000/1,000,000,000

Reducing this fraction to lowest terms yields 3/10; therefore, M = 3 and N = 10. FTW is the integer part of  $(M \times 2^{32})/N$ , or  $(3 \times 2^{32})/10$ , which is 1,288,490,188 (0x4CCCCCC in 32-bit hexadecimal notation). The remainder, Y, of  $(3 \times 2^{32})/10$ , is  $(2^{32} \times 3) - (1,288,490,188 \times 10)$ , which is 8. Therefore, Y/N is 8/10, which reduces to 4/5. Therefore, A = 4 and B = 5 (0x00000004 and 0x00000005 in 32-bit hexadecimal notation, respectively). Programming the AD9914 with these values of FTW, A, and B results in an output frequency that is exactly 3/10 of the system clock frequency.

#### **MODE PRIORITY**

The ability to activate each mode independently makes it possible to have multiple data sources attempting to drive the same DDS signal control parameter (frequency, phase, and amplitude). To avoid contention, the AD9914 has a built-in priority system. Table 6 summarizes the priority for each of the DDS modes. The data source column in Table 6 lists data sources for a particular DDS signal control parameter in descending order of precedence. For example, if the profile mode enable bit and the parallel data port enable bit (0x01[23:22]) are set to Logic 1 and both are programmed to source the frequency tuning word to DDS output, the profile modulation mode has priority over the parallel data port modulation mode.

**Table 6. Data Source Priority**

|                  |                      | DDS Signal Control Parameters                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Priority         | Data Source          | Conditions                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| Highest Priority | Programmable modulus | If programmable modulus mode is used to output frequency only, no other data source can control the output frequency in this mode. Note that the DRG is used in conjunction with programmable modulus mode; therefore, the DRG cannot be used to sweep phase or amplitude in programmable modulus mode. |  |  |  |  |  |

|                  |                      | If output phase offset control is desired, enable profile mode and use the profile registers and profile pins accordingly to control output phase adjustment.                                                                                                                                           |  |  |  |  |  |

|                  |                      | If output amplitude control is desired, enable profile mode and use the profile registers and profile pins accordingly to control output amplitude adjustment. Note that the OSK enable bit must be set to control the output amplitude.                                                                |  |  |  |  |  |

|                  | DRG                  | The digital ramp modulation mode is the next highest priority mode. If the DRG is enabled to sweep output frequency, phase, or amplitude, the two parameters not being swept can be controlled independently via the profile mode.                                                                      |  |  |  |  |  |

|                  | Profiles             | The profile modulation mode is the next highest priority mode. Profile mode can control all three parameters independently, if desired.                                                                                                                                                                 |  |  |  |  |  |