## **Excellent Integrated System Limited**

Stocking Distributor

Click to view price, real time Inventory, Delivery & Lifecycle Information:

[Texas Instruments](#)

[THS5641AIDW](#)

For any questions, you can email us directly:

[sales@integrated-circuit.com](mailto:sales@integrated-circuit.com)

- Member of the Pin-Compatible CommsDAC™ Product Family

- 100 MSPS Update Rate

- 8-Bit Resolution

- Signal-to-Noise and Distortion Ratio (SINAD) at 5 MHz: 50 dB

- Integral Nonlinearity INL: 0.25 LSB

- Differential Nonlinearity DNL: 0.25 LSB

- 1 ns Setup/Hold Time

- Glitch Energy: 5 pV-s

- Settling Time to 0.1%: 35 ns

- Differential Scalable Current Outputs: 2 mA to 20 mA

- On-Chip 1.2-V Reference

- 3-V and 5-V Single Supply Operation

- Straight Binary or Twos Complement Input

- Power Dissipation: 100 mW at 3.3 V, Sleep Mode: 17 mW at 3.3 V

- Package: 28-Pin SOIC and TSSOP

**SOIC (DW) OR TSSOP (PW) PACKAGE

(TOP VIEW)**

|    |    |    |                  |

|----|----|----|------------------|

| D7 | 1  | 28 | CLK              |

| D6 | 2  | 27 | DV <sub>DD</sub> |

| D5 | 3  | 26 | DGND             |

| D4 | 4  | 25 | MODE             |

| D3 | 5  | 24 | AV <sub>DD</sub> |

| D2 | 6  | 23 | COMP2            |

| D1 | 7  | 22 | IOUT1            |

| D0 | 8  | 21 | IOUT2            |

| NC | 9  | 20 | AGND             |

| NC | 10 | 19 | COMP1            |

| NC | 11 | 18 | BIASJ            |

| NC | 12 | 17 | EXTIO            |

| NC | 13 | 16 | EXTLO            |

| NC | 14 | 15 | SLEEP            |

NC – No internal connection

**description**

The THS5641A is an 8-bit resolution digital-to-analog converter (DAC) optimized for video applications and digital data transmission in wired and wireless communication systems. The 8-bit DAC is a member of the CommsDAC™ series of high-speed, low-power CMOS digital-to-analog converters. The CommsDAC™ family consists of pin compatible 14-, 12-, 10-, and 8-bit DACs. All devices offer identical interface options, small outline package and pinout. The THS5641A offers superior ac and dc performance while supporting update rates up to 100 MSPS.

The THS5641A operates from an analog and digital supply of 3 V to 5.5 V. Its inherent low power dissipation of 100 mW ensures that the device is well suited for portable and low power applications. Lowering the full-scale current output reduces the power dissipation without significantly degrading performance. The device features a SLEEP mode, which reduces the standby power to approximately 17 mW, thereby optimizing the power consumption for system needs.

The THS5641A is manufactured in Texas Instruments advanced high-speed mixed-signal CMOS process. A current-source-array architecture combined with simultaneous switching shows excellent dynamic performance. On-chip edge-triggered input latches and a 1.2 V temperature compensated bandgap reference provide a complete monolithic DAC solution. The digital supply range of 3 V to 5.5 V supports 3 V and 5 V CMOS logic families. Minimum data input setup and hold times allow for easy interfacing with external logic. The THS5641A supports both a straight binary and twos complement input word format, enabling flexible interfacing with digital signal processors.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

CommsDAC is a trademark of Texas Instruments.

**PRODUCTION DATA** information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 2002, Texas Instruments Incorporated

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

**THS5641A**

**8-BIT, 100 MSPS, CommsDAC™**

**DIGITAL-TO-ANALOG CONVERTER**

SLAS277A –MARCH 2000 – REVISED SEPTEMBER 2002

**description (continued)**

The THS5641A provides a nominal full-scale differential output current of 20 mA and  $>300$  k $\Omega$  output impedance, supporting both single-ended and differential applications. The output current can be directly fed to the load (e.g., external resistor load or transformer), with no additional external output buffer required. An accurate on-chip reference and control amplifier allows the user to adjust this output current from 20 mA down to 2 mA, with no significant degradation of performance. This reduces power consumption and provides 20 dB gain range control capabilities. Alternatively, an external reference voltage and control amplifier may be applied in applications using a multiplying DAC.

The THS5641A is available in both a 28-pin SOIC and TSSOP package. The device is characterized for operation over the industrial temperature range of  $-40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$ .

**AVAILABLE OPTIONS**

| TA                                            | PACKAGE          |                 |

|-----------------------------------------------|------------------|-----------------|

|                                               | 28-TSSOP<br>(PW) | 28-SOIC<br>(DW) |

| $-40^{\circ}\text{C}$ to $85^{\circ}\text{C}$ | THS5641AIPW      | THS5641AIDW     |

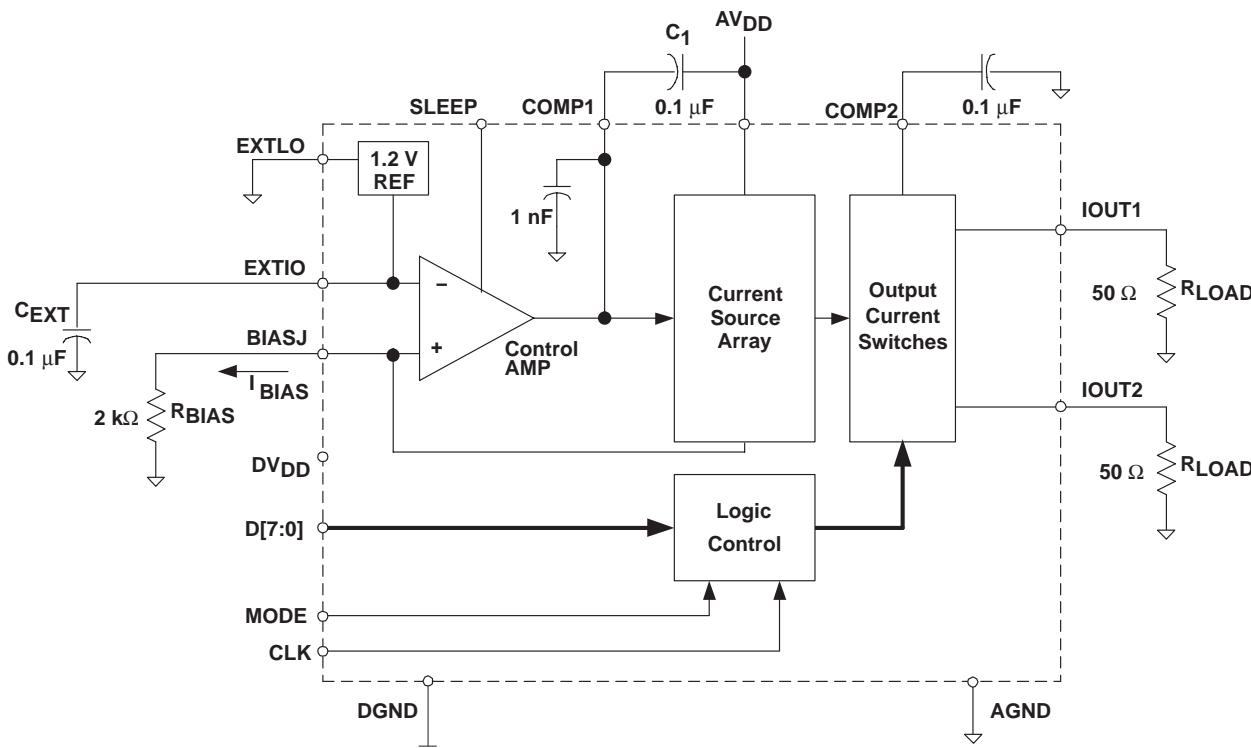

**functional block diagram**

**Terminal Functions**

| TERMINAL<br>NAME | NO.    | I/O | DESCRIPTION                                                                                                                                                                                                                                    |

|------------------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGND             | 20     | I   | Analog ground return for the internal analog circuitry                                                                                                                                                                                         |

| AV <sub>DD</sub> | 24     | I   | Positive analog supply voltage (3 V to 5.5 V)                                                                                                                                                                                                  |

| BIASJ            | 18     | O   | Full-scale output current bias                                                                                                                                                                                                                 |

| CLK              | 28     | I   | External clock input. Input data latched on rising edge of the clock.                                                                                                                                                                          |

| COMP1            | 19     | I   | Compensation and decoupling node, requires a 0.1 $\mu$ F capacitor to AV <sub>DD</sub> .                                                                                                                                                       |

| COMP2            | 23     | I   | Internal bias node, requires a 0.1 $\mu$ F decoupling capacitor to AGND.                                                                                                                                                                       |

| D[7:0]           | [1:8]  | I   | Data bits 0 through 7.<br>D7 is most significant data bit (MSB), D0 is least significant data bit (LSB).                                                                                                                                       |

| DGND             | 26     | I   | Digital ground return for the internal digital logic circuitry                                                                                                                                                                                 |

| DV <sub>DD</sub> | 27     | I   | Positive digital supply voltage (3 V to 5.5 V)                                                                                                                                                                                                 |

| EXTIO            | 17     | I/O | Used as external reference input when internal reference is disabled (i.e., EXTLO = AV <sub>DD</sub> ). Used as internal reference output when EXTLO = AGND, requires a 0.1 $\mu$ F decoupling capacitor to AGND when used as reference output |

| EXTLO            | 16     | O   | Internal reference ground. Connect to AV <sub>DD</sub> to disable the internal reference source                                                                                                                                                |

| IOUT1            | 22     | O   | DAC current output. Full scale when all input bits are set 1                                                                                                                                                                                   |

| IOUT2            | 21     | O   | Complementary DAC current output. Full scale when all input bits are 0                                                                                                                                                                         |

| MODE             | 25     | I   | Mode select. Internal pulldown. Mode 0 is selected if this pin is left floating or connected to DGND. See timing diagram.                                                                                                                      |

| NC               | [9:14] | N   | No connection                                                                                                                                                                                                                                  |

| SLEEP            | 15     | I   | Asynchronous hardware power down input. Active High. Internal pulldown. Requires 5 $\mu$ s to power down but 3 ms to power up.                                                                                                                 |

**absolute maximum ratings over operating free-air temperature (unless otherwise noted)†**

|                                                                        |                                    |

|------------------------------------------------------------------------|------------------------------------|

| Supply voltage range, AV <sub>DD</sub> (see Note 1) .....              | -0.3 V to 6.5 V                    |

| DV <sub>DD</sub> (see Note 2) .....                                    | -0.3 V to 6.5 V                    |

| Voltage between AGND and DGND .....                                    | -0.3 V to 0.5 V                    |

| Supply voltage range, AV <sub>DD</sub> to DV <sub>DD</sub> .....       | -6.5 V to 6.5 V                    |

| CLK, SLEEP, MODE (see Note 2) .....                                    | -0.3 V to DV <sub>DD</sub> + 0.3 V |

| Digital input D7-D0 (see Note 2) .....                                 | -0.3 V to DV <sub>DD</sub> + 0.3 V |

| IOUT1, IOUT2 (see Note 1) .....                                        | -1 V to AV <sub>DD</sub> + 0.3 V   |

| COMP1, COMP2 (see Note 1) .....                                        | -0.3 V to AV <sub>DD</sub> + 0.3 V |

| EXTIO, BIASJ (see Note 1) .....                                        | -0.3 V to AV <sub>DD</sub> + 0.3 V |

| EXTLO (see Note 1) .....                                               | -0.3 V to 0.3 V                    |

| Peak input current (any input) .....                                   | 20 mA                              |

| Peak total input current (all inputs) .....                            | -30 mA                             |

| Operating free-air temperature range, T <sub>A</sub> : THS5641AI ..... | -40°C to 85°C                      |

| Storage temperature range .....                                        | -65°C to 150°C                     |

| Lead temperature 1,6 mm (1/16 inch) from the case for 10 seconds ..... | 260°C                              |

† Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. Measured with respect to AGND.

2. Measured with respect to DGND.

**THS5641A**

**8-BIT, 100 MSPS, CommsDAC™**

**DIGITAL-TO-ANALOG CONVERTER**

SLAS277A –MARCH 2000 – REVISED SEPTEMBER 2002

**electrical characteristics over recommended operating free-air temperature range, AV<sub>DD</sub> = 5 V, DV<sub>DD</sub> = 5 V, I<sub>OUTFS</sub> = 20 mA (unless otherwise noted)**

**dc specifications**

| PARAMETER                                     | TEST CONDITIONS                                                                | MIN    | TYP       | MAX  | UNIT          |

|-----------------------------------------------|--------------------------------------------------------------------------------|--------|-----------|------|---------------|

| <b>Resolution</b>                             |                                                                                | 8      |           |      | Bits          |

| <b>DC accuracy†</b>                           |                                                                                |        |           |      |               |

| INL Integral nonlinearity                     | TA = -40°C to 85°C                                                             | -0.25  | ±0.1      | 0.25 | LSB           |

| DNL Differential nonlinearity                 |                                                                                | -0.25  | ±0.05     | 0.25 | LSB           |

| <b>Monotonicity</b>                           |                                                                                |        | Monotonic |      |               |

| <b>Analog output</b>                          |                                                                                |        |           |      |               |

| Offset error                                  |                                                                                | 0.02   |           |      | %FSR          |

| Gain error                                    | Without internal reference                                                     | 2.3    |           |      | %FSR          |

|                                               | With internal reference                                                        | 1.3    |           |      |               |

| Full scale output current‡                    |                                                                                | 2      | 20        |      | mA            |

| Output compliance range                       | AV <sub>DD</sub> = 5 V, I <sub>OUTFS</sub> = 20 mA                             | -1     | 1.25      |      | V             |

|                                               | AV <sub>DD</sub> = 3.3 V I <sub>OUTFS</sub> = 20 mA                            | -1     | 0.6       |      | V             |

| Output resistance                             |                                                                                | 300    |           |      | kΩ            |

| Output capacitance                            |                                                                                | 5      |           |      | pF            |

| <b>Reference output</b>                       |                                                                                |        |           |      |               |

| Reference voltage                             |                                                                                | 1.18   | 1.22      | 1.32 | V             |

| Reference output current§                     |                                                                                | 100    |           |      | nA            |

| <b>Reference input</b>                        |                                                                                |        |           |      |               |

| V <sub>EXTIO</sub> Input voltage range        |                                                                                | 0.1    | 1.25      |      | V             |

| Input resistance                              |                                                                                | 1      |           |      | MΩ            |

| Small signal bandwidth¶                       | Without C <sub>COMP1</sub>                                                     | 1.3    |           |      | MHz           |

| Input capacitance                             |                                                                                | 100    |           |      | pF            |

| <b>Temperature coefficients</b>               |                                                                                |        |           |      |               |

| Offset drift                                  |                                                                                | 0      |           |      | ppm of FSR/°C |

| Gain drift                                    | Without internal reference                                                     | ±40    |           |      |               |

|                                               | With internal reference                                                        | ±120   |           |      |               |

| Reference voltage drift                       |                                                                                | ±35    |           |      |               |

| <b>Power supply</b>                           |                                                                                |        |           |      |               |

| AV <sub>DD</sub> Analog supply voltage        |                                                                                | 3      | 5.5       |      | V             |

| DV <sub>DD</sub> Digital supply voltage       |                                                                                | 3      | 5.5       |      | V             |

| I <sub>AVDD</sub> Analog supply current       |                                                                                | 25     | 30        |      | mA            |

|                                               | Sleep mode supply current                                                      | 3      | 5         |      | mA            |

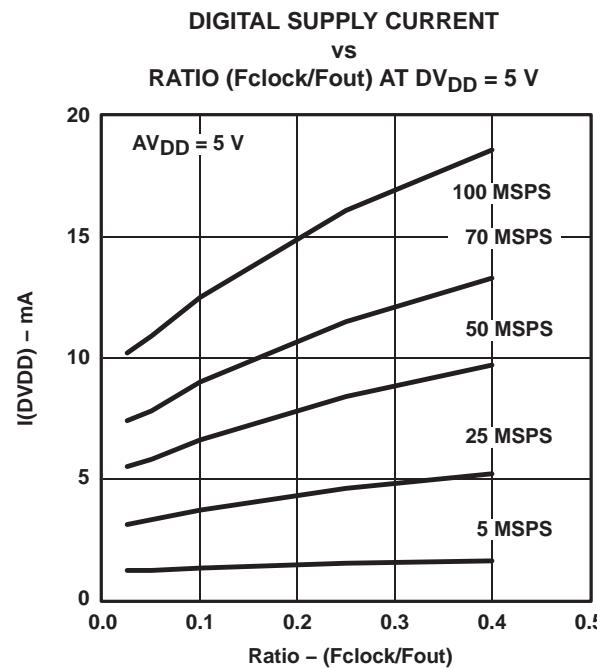

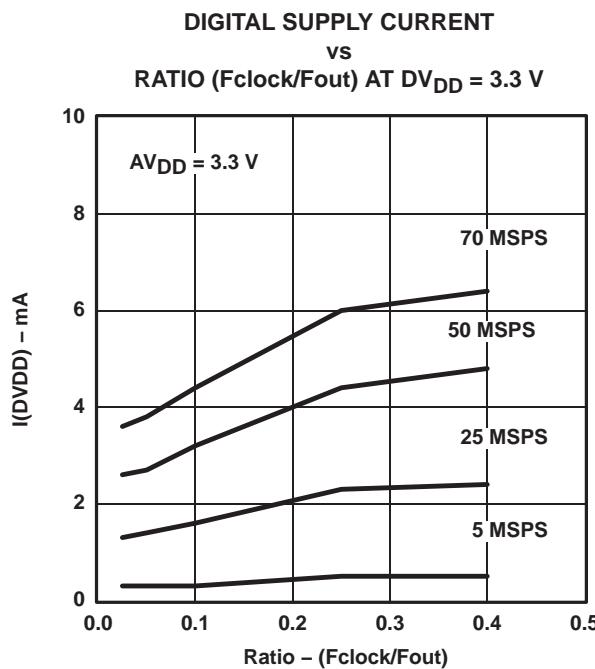

| I <sub>DVDD</sub> Digital supply current#     |                                                                                | 5      | 6         |      | mA            |

| Power dissipation                             | AV <sub>DD</sub> = 5 V, DV <sub>DD</sub> = 5 V I <sub>OUTFS</sub> = 20 mA      | 175    |           |      | mW            |

|                                               | AV <sub>DD</sub> = 3.3 V, DV <sub>DD</sub> = 3.3 V, I <sub>OUTFS</sub> = 20 mA | 100    |           |      |               |

| AV <sub>DD</sub> Power supply rejection ratio |                                                                                | ±0.4   |           |      | %FSR/V        |

|                                               |                                                                                | ±0.025 |           |      |               |

| Operating range                               |                                                                                | -40    | 85        |      | °C            |

† Measured at I<sub>OUT1</sub> in virtual ground configuration.

‡ Nominal full-scale current I<sub>OUTFS</sub> equals 32X the IBIAS current.

§ Use an external buffer amplifier with high impedance input to drive any external load.

¶ Reference bandwidth is a function of external cap at COMP1 pin and signal level.

# Measured at f<sub>CLK</sub> = 50 MSPS and f<sub>OUT</sub> = 1 MHz.

|| Measured for 50 Ω R<sub>LOAD</sub> at I<sub>OUT1</sub> and I<sub>OUT2</sub>, f<sub>CLK</sub> = 50 MSPS and f<sub>OUT</sub> = 20 MHz.

Specifications subject to change

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

**electrical characteristics over recommended operating free-air temperature range,  $AV_{DD} = 5$  V,  $DV_{DD} = 5$  V,  $I_{OUTFS} = 20$  mA, single-ended output  $I_{OUT1}$ ,  $50\ \Omega$  doubly terminated load (unless otherwise noted)**

**ac specifications**

| PARAMETER                          |                                           | TEST CONDITIONS                                                                      | MIN | TYP | MAX | UNIT                   |

|------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------|-----|-----|-----|------------------------|

| <b>Analog output</b>               |                                           |                                                                                      |     |     |     |                        |

| f <sub>CLK</sub>                   | Maximum output update rate                | DV <sub>DD</sub> = 4.5 V to 5.5 V                                                    | 100 |     |     | MSPS                   |

|                                    |                                           | DV <sub>DD</sub> = 3 V to 3.6 V                                                      | 67  |     |     |                        |

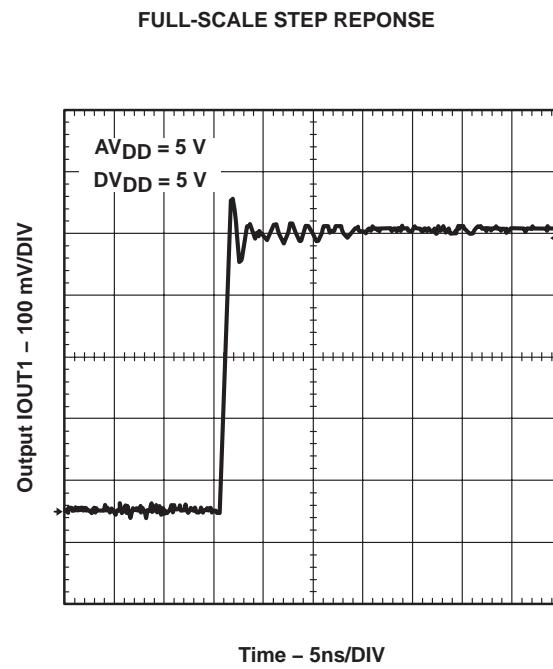

| t <sub>s</sub> (DAC)               | Output settling time to 0.1% <sup>†</sup> |                                                                                      |     | 35  |     | ns                     |

| t <sub>pd</sub>                    | Output propagation delay                  |                                                                                      |     | 1   |     | ns                     |

| GE                                 | Glitch energy <sup>‡</sup>                | Worst case LSB transition (code 127 – code 128)                                      |     | 5   |     | pV-s                   |

| t <sub>r</sub> (I <sub>OUT</sub> ) | Output rise time 10% to 90% <sup>†</sup>  |                                                                                      |     | 1   |     | ns                     |

| t <sub>f</sub> (I <sub>OUT</sub> ) | Output fall time 90% to 10% <sup>†</sup>  |                                                                                      |     | 1   |     | ns                     |

| Output noise                       | I <sub>OUTFS</sub> = 20 mA                |                                                                                      | 15  |     |     | pA/ $\sqrt{\text{Hz}}$ |

|                                    | I <sub>OUTFS</sub> = 2 mA                 |                                                                                      | 10  |     |     |                        |

| <b>AC linearity (to Nyquist)</b>   |                                           |                                                                                      |     |     |     |                        |

| SINAD                              | Signal-to-noise and distortion ratio      | f <sub>CLK</sub> = 5 MSPS, f <sub>OUT</sub> = 1 MHz, T <sub>A</sub> = 25°C           | 50  |     |     | dB                     |

|                                    |                                           | f <sub>CLK</sub> = 25 MSPS, f <sub>OUT</sub> = 1 MHz, T <sub>A</sub> = 25°C          | 50  |     |     |                        |

|                                    |                                           | f <sub>CLK</sub> = 25 MSPS, f <sub>OUT</sub> = 5 MHz, T <sub>A</sub> = 25°C          | 50  |     |     |                        |

|                                    |                                           | f <sub>CLK</sub> = 25 MSPS, f <sub>OUT</sub> = 10 MHz, T <sub>A</sub> = 25°C         | 48  |     |     |                        |

|                                    |                                           | f <sub>CLK</sub> = 50 MSPS, f <sub>OUT</sub> = 1 MHz, T <sub>A</sub> = 25°C          | 50  |     |     |                        |

|                                    |                                           | f <sub>CLK</sub> = 50 MSPS, f <sub>OUT</sub> = 5 MHz, T <sub>A</sub> = 25°C          | 50  |     |     |                        |

|                                    |                                           | f <sub>CLK</sub> = 50 MSPS, f <sub>OUT</sub> = 20 MHz, T <sub>A</sub> = 25°C         | 47  |     |     |                        |

|                                    |                                           | f <sub>CLK</sub> = 70 MSPS, f <sub>OUT</sub> = 5 MHz, T <sub>A</sub> = 25°C          | 50  |     |     |                        |

|                                    |                                           | f <sub>CLK</sub> = 70 MSPS, f <sub>OUT</sub> = 10 MHz, T <sub>A</sub> = 25°C         | 50  |     |     |                        |

|                                    |                                           | f <sub>CLK</sub> = 70 MSPS, f <sub>OUT</sub> = 20 MHz, T <sub>A</sub> = 25°C         | 46  |     |     |                        |

|                                    |                                           | f <sub>CLK</sub> = 100 MSPS, f <sub>OUT</sub> = 10 MHz, T <sub>A</sub> = 25°C        | 47  |     |     |                        |

|                                    |                                           | f <sub>CLK</sub> = 100 MSPS, f <sub>OUT</sub> = 22 MHz, T <sub>A</sub> = 25°C        | 47  |     |     |                        |

|                                    |                                           | f <sub>CLK</sub> = 100 MSPS, f <sub>OUT</sub> = 40 MHz, T <sub>A</sub> = 25°C        | 45  |     |     |                        |

|                                    |                                           | f <sub>CLK</sub> = 5 MSPS, f <sub>OUT</sub> = 1 MHz, T <sub>A</sub> = 25°C           | -69 |     |     | dBc                    |

|                                    |                                           | f <sub>CLK</sub> = 25 MSPS, f <sub>OUT</sub> = 1 MHz, T <sub>A</sub> = 25°C          | -67 |     |     |                        |

|                                    |                                           | f <sub>CLK</sub> = 25 MSPS, f <sub>OUT</sub> = 5 MHz, T <sub>A</sub> = 25°C          | -69 |     |     |                        |

|                                    |                                           | f <sub>CLK</sub> = 25 MSPS, f <sub>OUT</sub> = 10 MHz, T <sub>A</sub> = 25°C         | -57 |     |     |                        |

|                                    |                                           | f <sub>CLK</sub> = 50 MSPS, f <sub>OUT</sub> = 1 MHz, T <sub>A</sub> = 25°C          | -67 |     |     |                        |

|                                    |                                           | f <sub>CLK</sub> = 50 MSPS, f <sub>OUT</sub> = 1 MHz, T <sub>A</sub> = -40°C to 85°C | -64 |     |     |                        |

|                                    |                                           | f <sub>CLK</sub> = 50 MSPS, f <sub>OUT</sub> = 5 MHz, T <sub>A</sub> = 25°C          | -66 |     |     |                        |

|                                    |                                           | f <sub>CLK</sub> = 50 MSPS, f <sub>OUT</sub> = 20 MHz, T <sub>A</sub> = 25°C         | -52 |     |     |                        |

|                                    |                                           | f <sub>CLK</sub> = 70 MSPS, f <sub>OUT</sub> = 5 MHz, T <sub>A</sub> = 25°C          | -64 |     |     |                        |

|                                    |                                           | f <sub>CLK</sub> = 70 MSPS, f <sub>OUT</sub> = 10 MHz, T <sub>A</sub> = 25°C         | -60 |     |     |                        |

|                                    |                                           | f <sub>CLK</sub> = 70 MSPS, f <sub>OUT</sub> = 20 MHz, T <sub>A</sub> = 25°C         | -48 |     |     |                        |

|                                    |                                           | f <sub>CLK</sub> = 100 MSPS, f <sub>OUT</sub> = 10 MHz, T <sub>A</sub> = 25°C        | -53 |     |     |                        |

|                                    |                                           | f <sub>CLK</sub> = 100 MSPS, f <sub>OUT</sub> = 22 MHz, T <sub>A</sub> = 25°C        | -53 |     |     |                        |

|                                    |                                           | f <sub>CLK</sub> = 100 MSPS, f <sub>OUT</sub> = 40 MHz, T <sub>A</sub> = 25°C        | -47 |     |     |                        |

<sup>†</sup> Measured single ended into  $50\ \Omega$  load at I<sub>OUT1</sub>.

<sup>‡</sup> Single-ended output I<sub>OUT1</sub>,  $50\ \Omega$  doubly terminated load.

**THS5641A**

**8-BIT, 100 MSPS, CommsDAC™**

**DIGITAL-TO-ANALOG CONVERTER**

SLAS277A –MARCH 2000 – REVISED SEPTEMBER 2002

electrical characteristics over recommended operating free-air temperature range,  $AV_{DD} = 5$  V,  $DV_{DD} = 5$  V,  $I_{OUT,FS} = 20$  mA, single-ended output  $I_{OUT1}$ ,  $50\ \Omega$  doubly terminated load (unless otherwise noted) (continued)

**ac specifications**

| PARAMETER                        |                             | TEST CONDITIONS                                              | MIN | TYP | MAX | UNIT |

|----------------------------------|-----------------------------|--------------------------------------------------------------|-----|-----|-----|------|

| <b>AC linearity (to Nyquist)</b> |                             |                                                              |     |     |     |      |

| SFDR                             | Spurious free dynamic range | $f_{CLK} = 5$ MSPS, $f_{OUT} = 1$ MHz, $T_A = 25^\circ C$    | 68  |     |     | dBc  |

|                                  |                             | $f_{CLK} = 25$ MSPS, $f_{OUT} = 1$ MHz, $T_A = 25^\circ C$   | 69  |     |     |      |

|                                  |                             | $f_{CLK} = 25$ MSPS, $f_{OUT} = 5$ MHz, $T_A = 25^\circ C$   | 68  |     |     |      |

|                                  |                             | $f_{CLK} = 25$ MSPS, $f_{OUT} = 10$ MHz, $T_A = 25^\circ C$  | 56  |     |     |      |

|                                  |                             | $f_{CLK} = 50$ MSPS, $f_{OUT} = 1$ MHz, $T_A = 25^\circ C$   | 67  |     |     |      |

|                                  |                             | $f_{CLK} = 50$ MSPS, $f_{OUT} = 5$ MHz, $T_A = 25^\circ C$   | 67  |     |     |      |

|                                  |                             | $f_{CLK} = 50$ MSPS, $f_{OUT} = 20$ MHz, $T_A = 25^\circ C$  | 53  |     |     |      |

|                                  |                             | $f_{CLK} = 70$ MSPS, $f_{OUT} = 5$ MHz, $T_A = 25^\circ C$   | 65  |     |     |      |

|                                  |                             | $f_{CLK} = 70$ MSPS, $f_{OUT} = 10$ MHz, $T_A = 25^\circ C$  | 63  |     |     |      |

|                                  |                             | $f_{CLK} = 70$ MSPS, $f_{OUT} = 20$ MHz, $T_A = 25^\circ C$  | 48  |     |     |      |

|                                  |                             | $f_{CLK} = 100$ MSPS, $f_{OUT} = 10$ MHz, $T_A = 25^\circ C$ | 55  |     |     |      |

|                                  |                             | $f_{CLK} = 100$ MSPS, $f_{OUT} = 22$ MHz, $T_A = 25^\circ C$ | 55  |     |     |      |

|                                  |                             | $f_{CLK} = 100$ MSPS, $f_{OUT} = 40$ MHz, $T_A = 25^\circ C$ | 48  |     |     |      |

**digital specifications**

| PARAMETER           |                             | TEST CONDITIONS        | MIN                      | TYP | MAX | UNIT    |

|---------------------|-----------------------------|------------------------|--------------------------|-----|-----|---------|

| <b>Interface</b>    |                             |                        |                          |     |     |         |

| V <sub>IH</sub>     | High-level input voltage    | $DV_{DD} = 5$ V        | 3.5                      | 5   |     | V       |

|                     |                             | $DV_{DD} = 3.3$ V      | 2.1                      | 3.3 |     |         |

| V <sub>IL</sub>     | Low-level input voltage     | $DV_{DD} = 5$ V        | 0                        | 1.3 |     | V       |

|                     |                             | $DV_{DD} = 3.3$ V      | 0                        | 0.9 |     |         |

| I <sub>IH</sub>     | High-level input current    | MODE and SLEEP         | $DV_{DD} = 3$ V to 5.5 V | -15 | 15  | $\mu A$ |

|                     |                             | All other digital pins | $DV_{DD} = 3$ V to 5.5 V | -10 | 10  |         |

| I <sub>IL</sub>     | Low-level input current     | MODE and SLEEP         | $DV_{DD} = 3$ V to 5.5 V | -15 | 15  | $\mu A$ |

|                     |                             | All other digital pins | $DV_{DD} = 3$ V to 5.5 V | -10 | 10  |         |

| C <sub>I</sub>      | Input capacitance           |                        | 1                        | 5   |     | pF      |

| <b>Timing</b>       |                             |                        |                          |     |     |         |

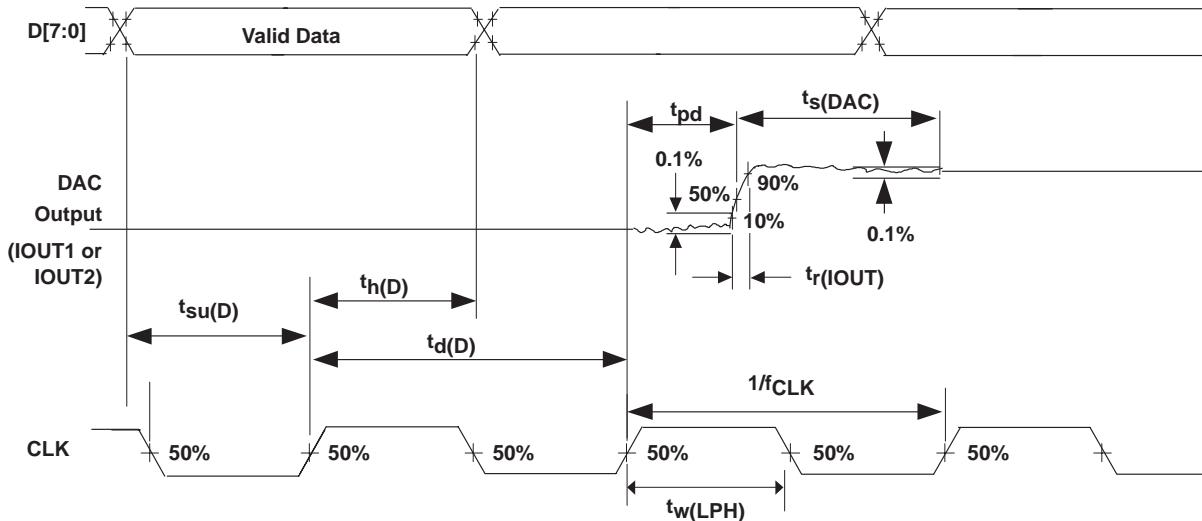

| t <sub>su(D)</sub>  | Input setup time            |                        | 1                        |     |     | ns      |

| t <sub>h(D)</sub>   | Input hold time             |                        | 1                        |     |     | ns      |

| t <sub>w(LPH)</sub> | Input latch pulse high time |                        | 4                        |     |     | ns      |

| t <sub>d(D)</sub>   | Digital delay time          |                        |                          |     | 1   | clk     |

Specifications subject to change

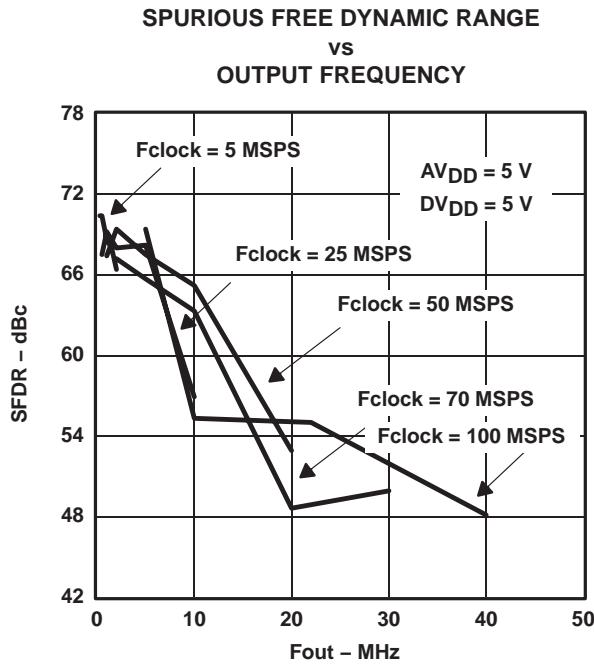

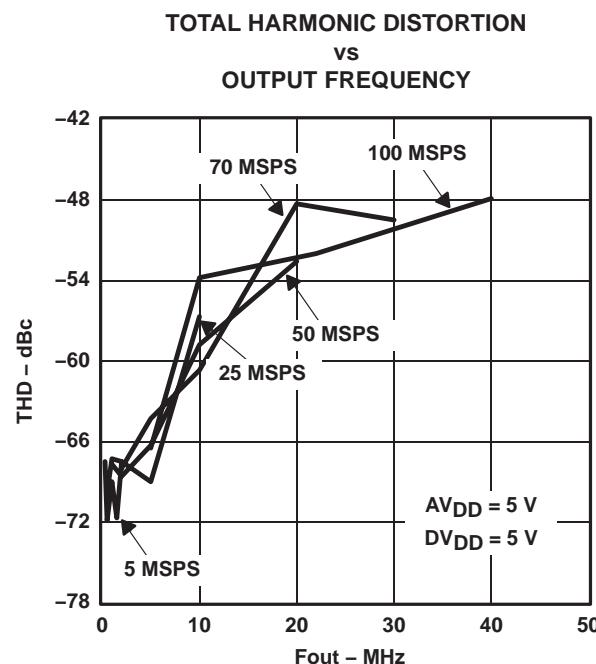

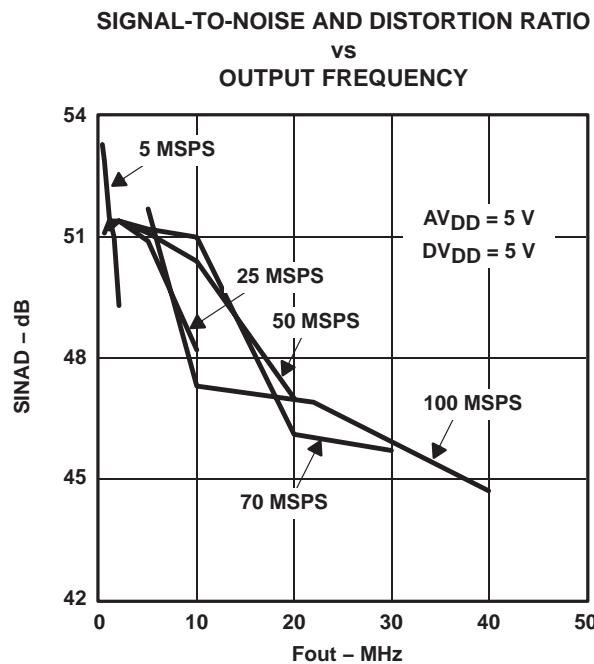

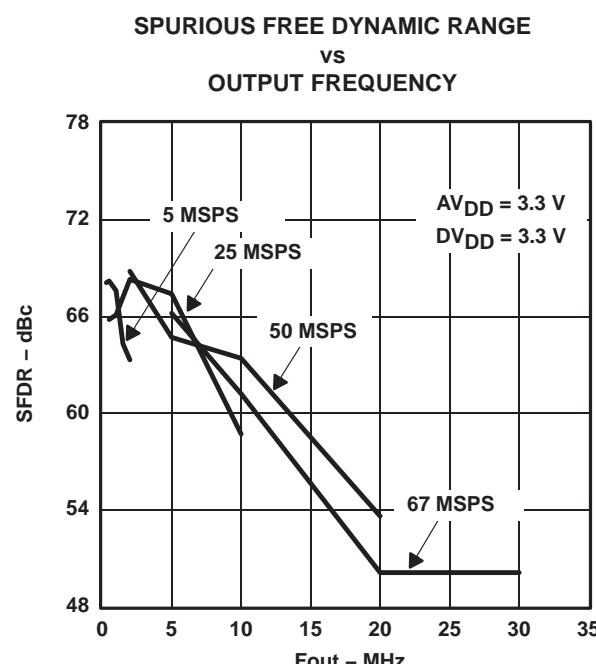

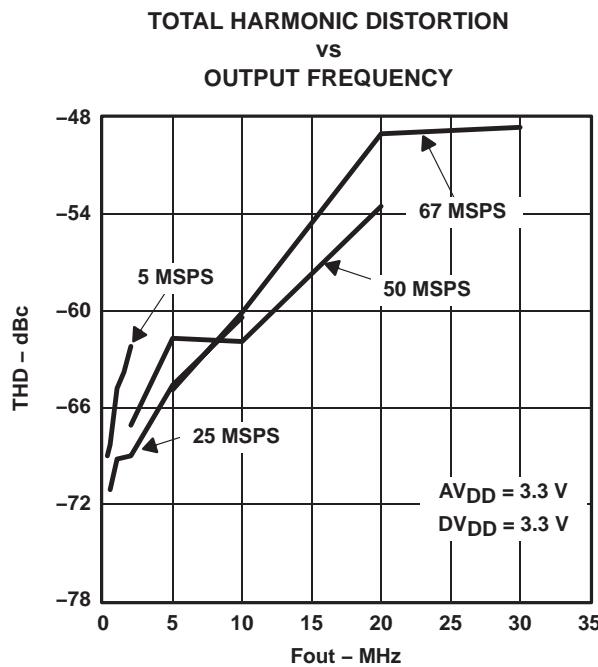

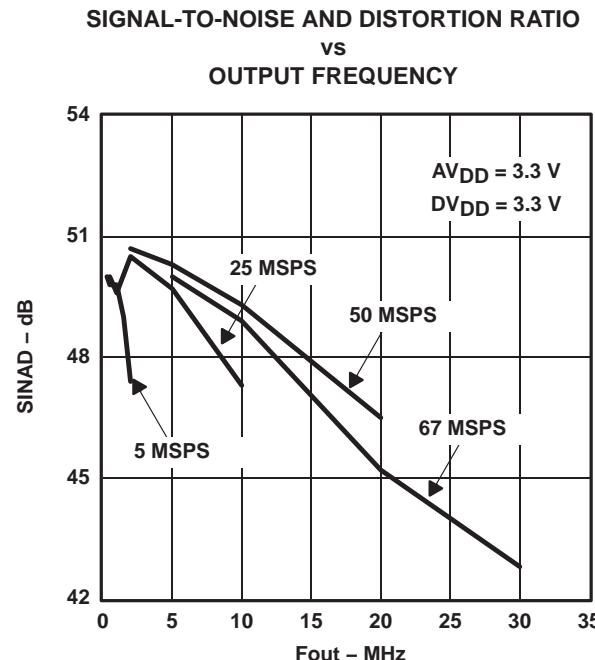

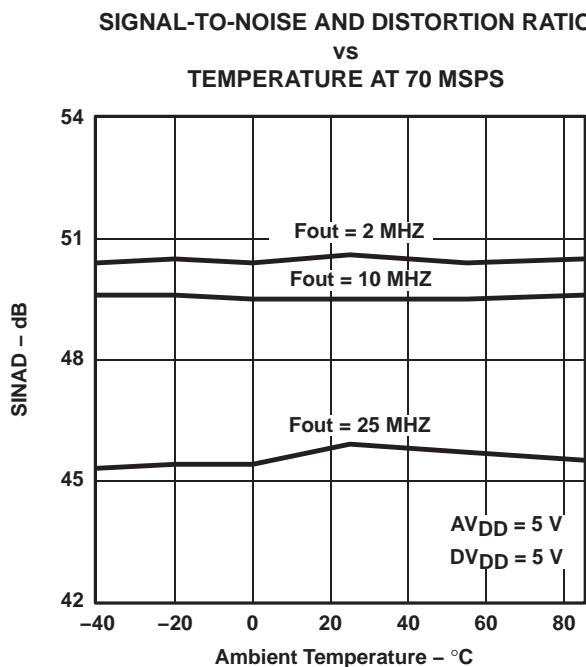

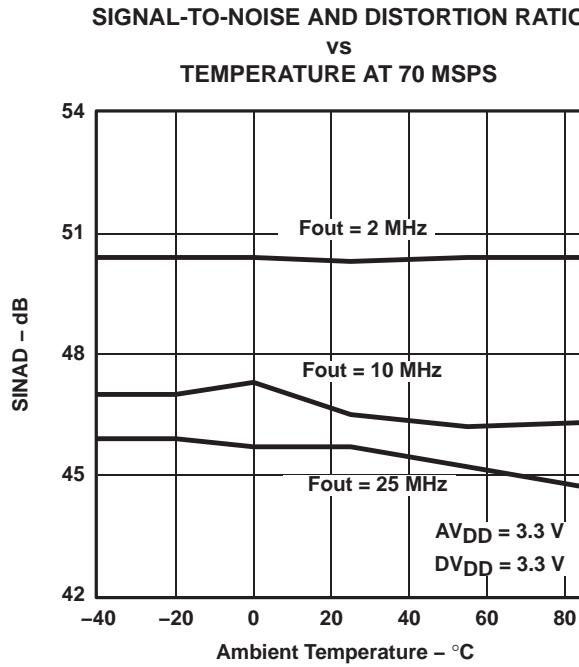

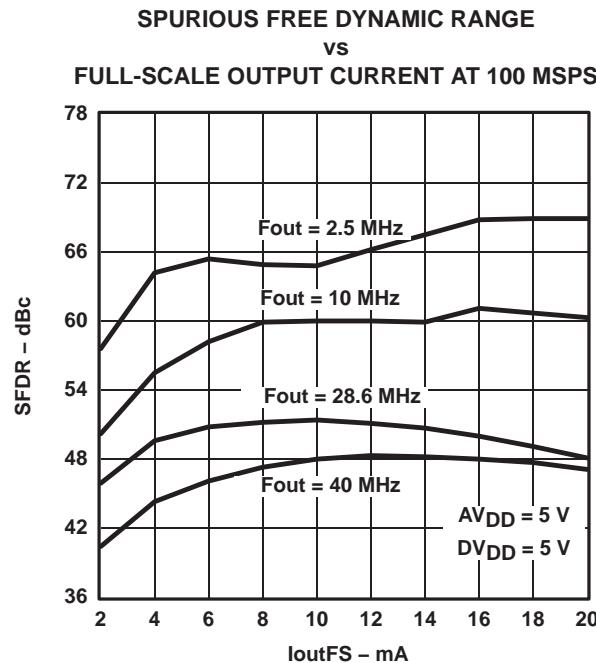

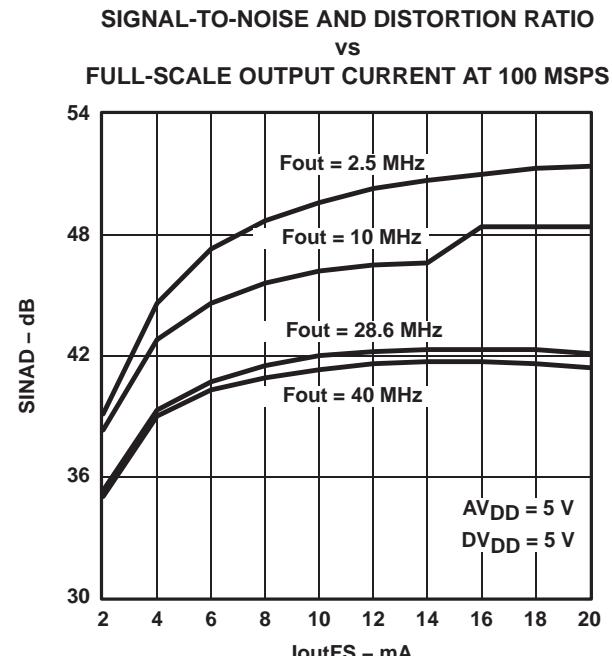

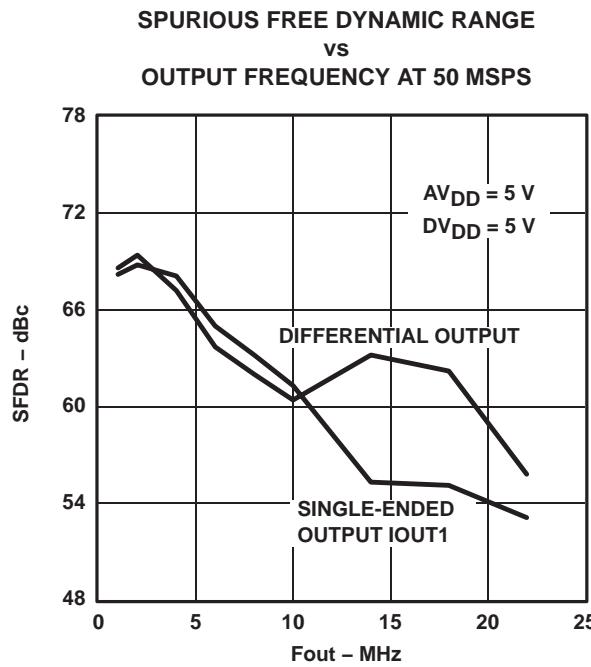

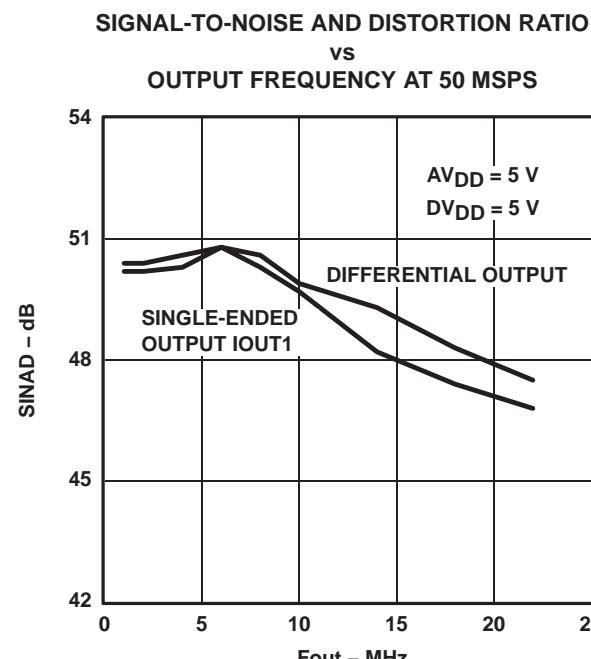

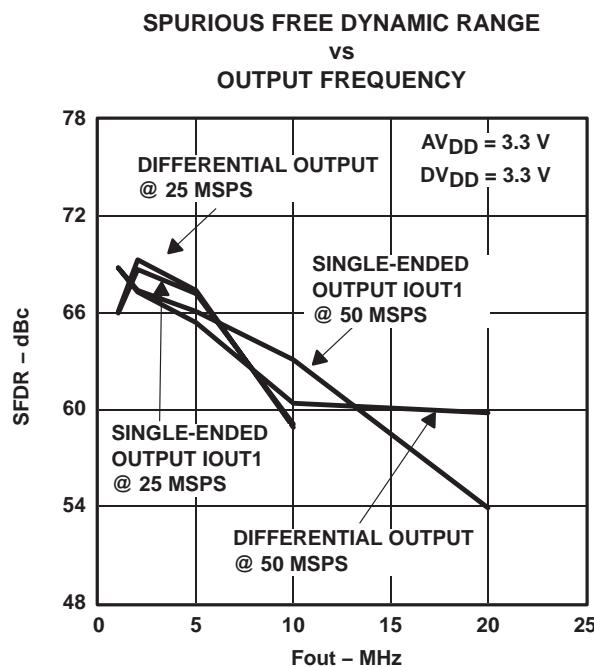

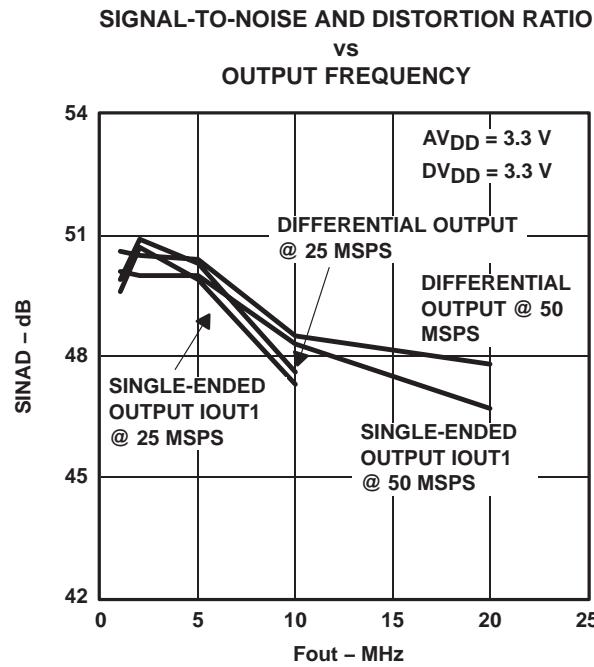

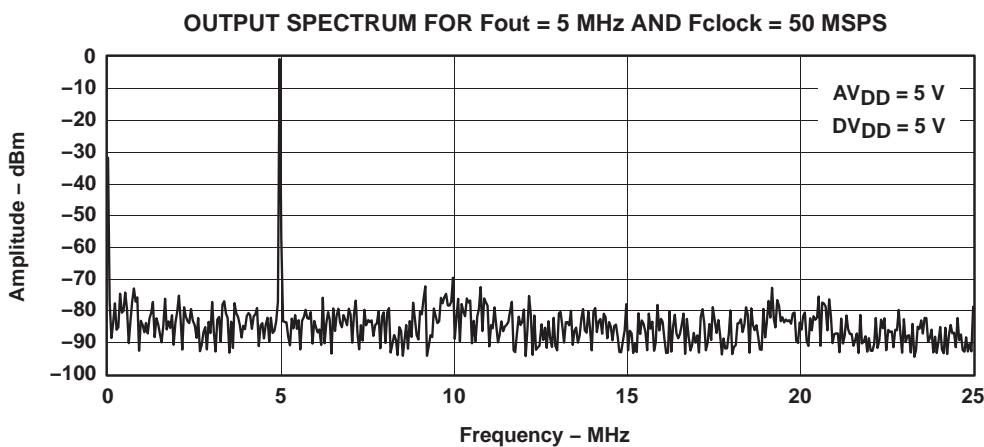

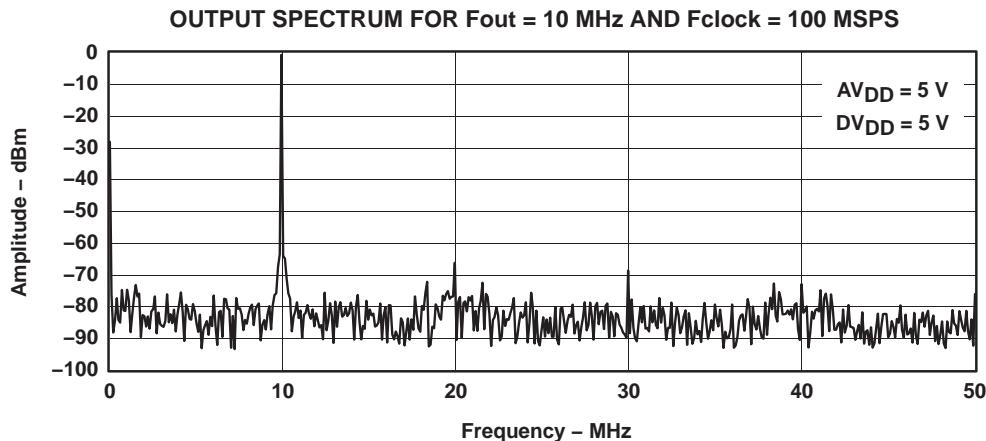

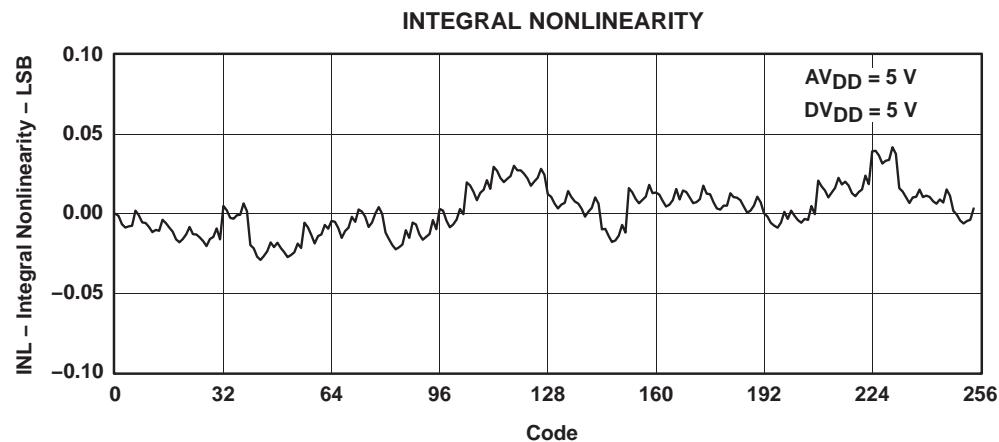

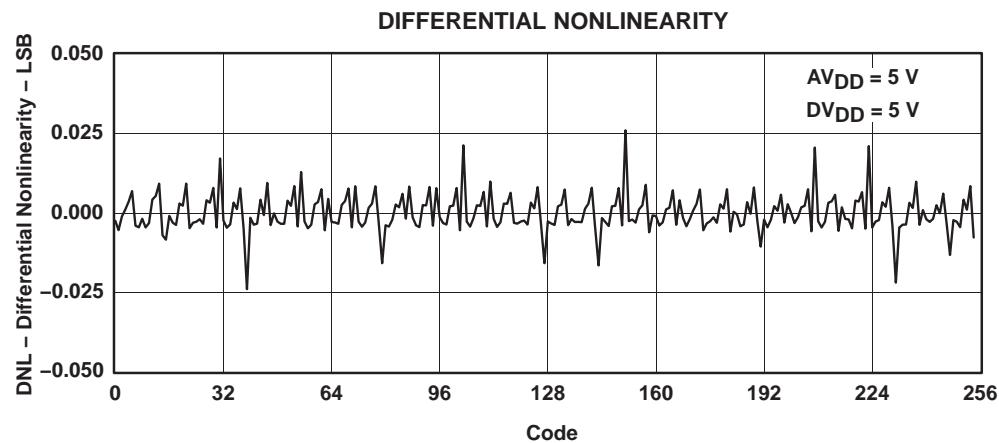

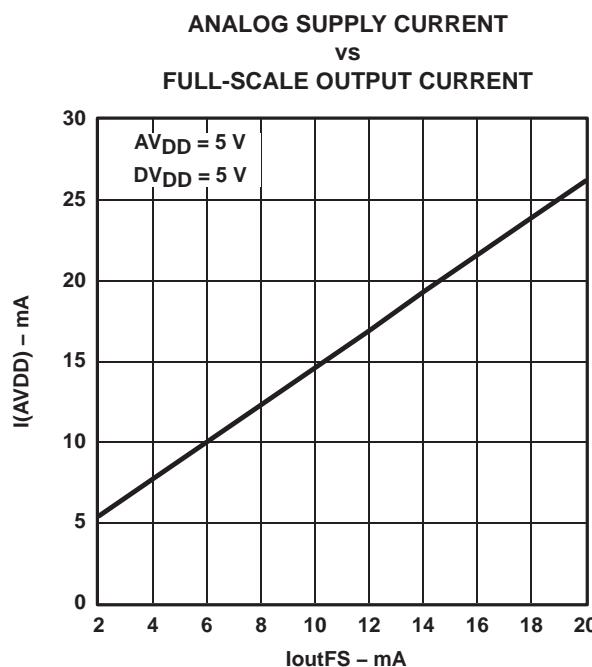

**TYPICAL CHARACTERISTICS<sup>†</sup>**

Figure 1

Figure 2

Figure 3

Figure 4

<sup>†</sup> AV<sub>DD</sub> and DV<sub>DD</sub> specified for each chart separately, I<sub>O</sub>UT<sub>FS</sub> = 20 mA, single-ended output I<sub>O</sub>UT1, 50 Ω doubly terminated load, T<sub>A</sub> = 25°C (unless otherwise noted.)

**THS5641A**

**8-BIT, 100 MSPS, CommsDAC™**

**DIGITAL-TO-ANALOG CONVERTER**

SLAS277A –MARCH 2000 – REVISED SEPTEMBER 2002

**TYPICAL CHARACTERISTICS<sup>†</sup>**

Figure 5

Figure 6

Figure 7

Figure 8

<sup>†</sup> AV<sub>DD</sub> and DV<sub>DD</sub> specified for each chart separately, IOUT<sub>FS</sub> = 20 mA, single-ended output IOUT1, 50 Ω doubly terminated load, T<sub>A</sub> = 25°C (unless otherwise noted.)

**TYPICAL CHARACTERISTICS<sup>†</sup>**

Figure 9

Figure 10

Figure 11

Figure 12

<sup>†</sup> AV<sub>DD</sub> and DV<sub>DD</sub> specified for each chart separately, I<sub>OUTFS</sub> = 20 mA, single-ended output I<sub>OUT1</sub>, 50 Ω doubly terminated load, T<sub>A</sub> = 25°C (unless otherwise noted.)

**THS5641A**

**8-BIT, 100 MSPS, CommsDAC™**

**DIGITAL-TO-ANALOG CONVERTER**

SLAS277A –MARCH 2000 – REVISED SEPTEMBER 2002

**TYPICAL CHARACTERISTICS<sup>†</sup>**

Figure 13

Figure 14

Figure 15

<sup>†</sup> AV<sub>DD</sub> and DV<sub>DD</sub> specified for each chart separately, I<sub>OUT</sub><sub>FS</sub> = 20 mA, single-ended output IOUT1, 50 Ω doubly terminated load, TA = 25°C (unless otherwise noted.)

**TYPICAL CHARACTERISTICS†**

**Figure 16**

**Figure 17**

**Figure 18**

†  $AV_{DD}$  and  $DV_{DD}$  specified for each chart separately,  $I_{OUT,FS} = 20$  mA, single-ended output IOUT1,  $50\ \Omega$  doubly terminated load,  $T_A = 25^\circ\text{C}$  (unless otherwise noted.)

**THS5641A**

**8-BIT, 100 MSPS, CommsDAC™**

**DIGITAL-TO-ANALOG CONVERTER**

SLAS277A –MARCH 2000 – REVISED SEPTEMBER 2002

**TYPICAL CHARACTERISTICS<sup>†</sup>**

Figure 19

Figure 20

Figure 21

Figure 22

<sup>†</sup> AV<sub>DD</sub> and DV<sub>DD</sub> specified for each chart separately, I<sub>OUTFS</sub> = 20 mA, single-ended output I<sub>OUT1</sub>, 50 Ω doubly terminated load, TA = 25°C (unless otherwise noted.)

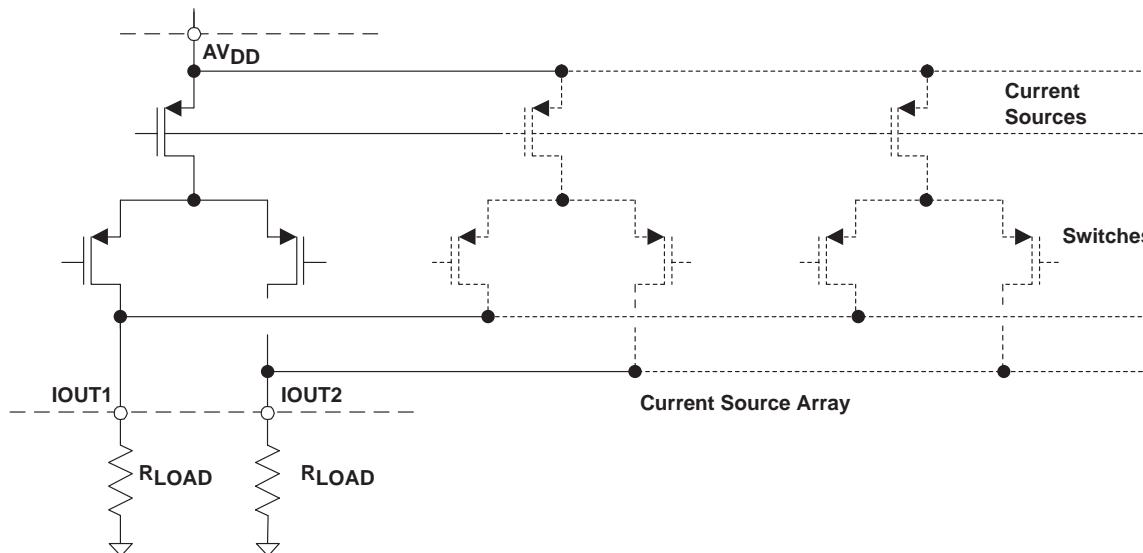

## APPLICATION INFORMATION

The THS5641A architecture is based on current steering, combining high update rates with low power consumption. The CMOS device consists of a segmented array of PMOS transistor current sources, which are capable of delivering a full-scale current up to 20 mA. High-speed differential current switches direct the current of each current source to either one of the output nodes, IOUT1 or IOUT2. The complementary output currents thus enable differential operation, canceling out common mode noise sources (on-chip and PCB noise), dc offsets, even order distortion components, and increase signal output power by a factor of two. Major advantages of the segmented architecture are minimum glitch energy, excellent DNL, and very good dynamic performance. The DAC's high output impedance of  $>300$  k $\Omega$  and fast switching result in excellent dynamic linearity (spurious free dynamic range SFDR).

The full-scale output current is set using an external resistor  $R_{BIAS}$  in combination with an on-chip bandgap voltage reference source (1.2 V) and control amplifier. The current  $I_{BIAS}$  through resistor  $R_{BIAS}$  is mirrored internally to provide a full-scale output current equal to 32 times  $I_{BIAS}$ . The full-scale current can be adjusted from 20 mA down to 2 mA.

### data interface and timing

The THS5641A comprises separate analog and digital supplies, i.e.  $AV_{DD}$  and  $DV_{DD}$ . The analog and digital supply voltage can be set independently from 5.5 V down to 3 V. The THS5641A provides two operating modes, as shown in Table 1. Mode 0 (mode pin connected to DGND) supports a straight binary input data word format, whereas mode 1 (mode pin connected to  $DV_{DD}$ ) sets a two's complement input configuration.

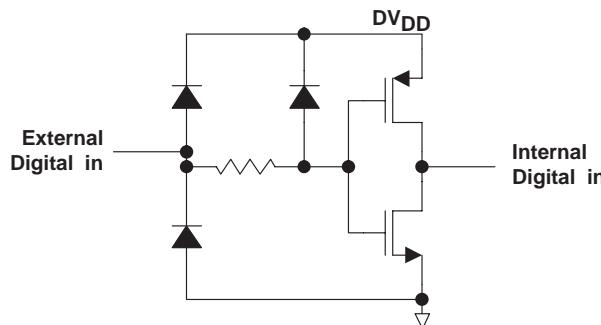

Figure 23 shows the timing diagram. Internal edge-triggered flip-flops latch the input word on the rising edge of the input clock. The THS5641A provides for minimum setup and hold times ( $> 1$  ns), allowing for noncritical external interface timing. Conversion latency is one clock cycle for both modes. The clock duty cycle can be chosen arbitrarily under the timing constraints listed in the digital specifications table. However, a 50% duty cycle will give optimum dynamic performance. Figure 24 shows a schematic of the equivalent digital inputs of the THS5641A, valid for pins D7-D0, SLEEP, and CLK. The digital inputs are CMOS-compatible with logic thresholds of  $DV_{DD}/2 \pm 20\%$ . Since the THS5641A is capable of being updated up to 100 MSPS, the quality of the clock and data input signals are important in achieving the optimum performance. The drivers of the digital data interface circuitry should be specified to meet the minimum setup and hold times of the THS5641A, as well as its required min/max input logic level thresholds. Typically, the selection of the slowest logic family that satisfies the above conditions will result in the lowest data feed-through and noise. Additionally, operating the THS5641A with reduced logic swings and a corresponding digital supply ( $DV_{DD}$ ) will reduce data feed-through. Note that the update rate is limited to 67 MSPS for a digital supply voltage  $DV_{DD}$  of 3 V to 3.6 V.

**THS5641A**

**8-BIT, 100 MSPS, CommsDAC™**

**DIGITAL-TO-ANALOG CONVERTER**

SLAS277A –MARCH 2000 – REVISED SEPTEMBER 2002

**APPLICATION INFORMATION**

Figure 23. Timing Diagram

Table 1. Input Interface Modes

| FUNCTION/MODE     | MODE 0                     | MODE 1                                 |

|-------------------|----------------------------|----------------------------------------|

|                   | MODE PIN CONNECTED TO DGND | MODE PIN CONNECTED TO DV <sub>DD</sub> |

| Input code format | Binary                     | Twos complement                        |

Figure 24. Digital Equivalent Input

## APPLICATION INFORMATION

### DAC transfer function

The THS5641A delivers complementary output currents  $I_{OUT1}$  and  $I_{OUT2}$ . Output current  $I_{OUT1}$  equals the approximate full-scale output current when all input bits are set high in mode 0 (straight binary input), i.e. the binary input word has the decimal representation 255. For mode 1, the MSB is inverted (twos complement input format). Full-scale output current will flow through terminal  $I_{OUT2}$  when all input bits are set low (mode 0, straight binary input). The relation between  $I_{OUT1}$  and  $I_{OUT2}$  can thus be expressed as:

$$I_{OUT1} = I_{OUT_{FS}} - I_{OUT2}$$

where  $I_{OUT_{FS}}$  is the full-scale output current. The output currents can be expressed as:

$$I_{OUT1} = I_{OUT_{FS}} \times \frac{CODE}{256}$$

$$I_{OUT2} = I_{OUT_{FS}} \times \frac{(255 - CODE)}{256}$$

where CODE is the decimal representation of the DAC data input word. Output currents  $I_{OUT1}$  and  $I_{OUT2}$  drive resistor loads  $R_{LOAD}$  or a transformer with equivalent input load resistance  $R_{LOAD}$ . This would translate into single-ended voltages  $V_{OUT1}$  and  $V_{OUT2}$  at terminal  $I_{OUT1}$  and  $I_{OUT2}$ , respectively, of:

$$V_{OUT1} = I_{OUT1} \times R_{LOAD} = \frac{CODE}{256} \times I_{OUT_{FS}} \times R_{LOAD}$$

$$V_{OUT2} = I_{OUT2} \times R_{LOAD} = \frac{(255 - CODE)}{256} \times I_{OUT_{FS}} \times R_{LOAD}$$

The differential output voltage  $V_{OUT_{DIFF}}$  can thus be expressed as:

$$V_{OUT_{DIFF}} = V_{OUT1} - V_{OUT2} = \frac{(2CODE - 255)}{256} \times I_{OUT_{FS}} \times R_{LOAD}$$

The latter equation shows that applying the differential output will result in doubling of the signal power delivered to the load. Since the output currents of  $I_{OUT1}$  and  $I_{OUT2}$  are complementary, they become additive when processed differentially. Care should be taken not to exceed the compliance voltages at node  $I_{OUT1}$  and  $I_{OUT2}$ , which would lead to increased signal distortion.

**THS5641A**

**8-BIT, 100 MSPS, CommsDAC™**

**DIGITAL-TO-ANALOG CONVERTER**

SLAS277A –MARCH 2000 – REVISED SEPTEMBER 2002

**APPLICATION INFORMATION**

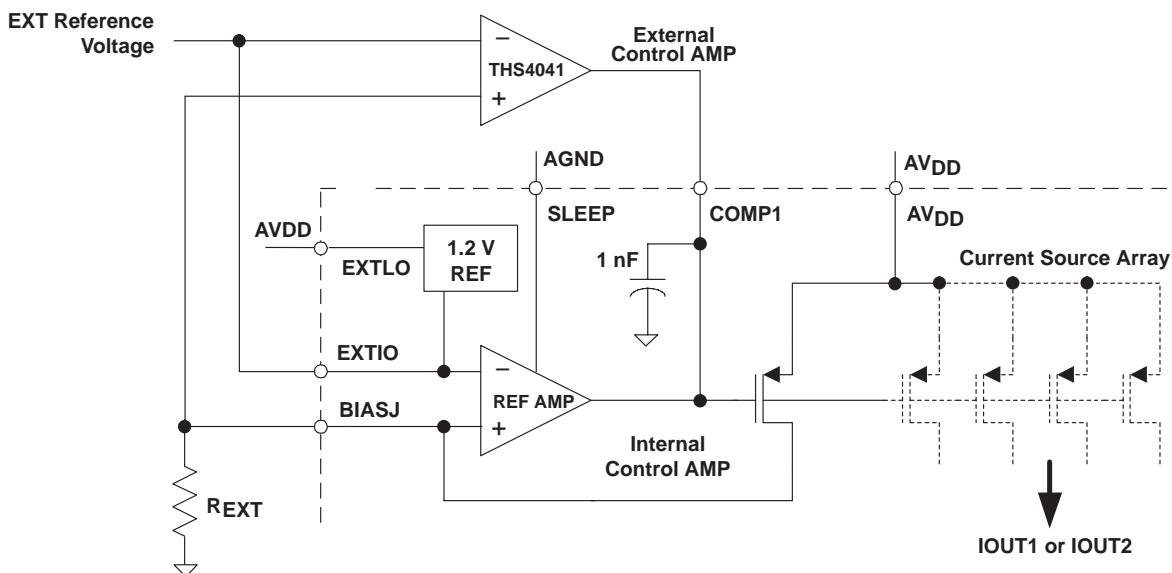

**reference operation**

The THS5641A comprises a bandgap reference and control amplifier for biasing the full-scale output current. The full-scale output current is set by applying an external resistor  $R_{BIAS}$ . The bias current  $I_{BIAS}$  through resistor  $R_{BIAS}$  is defined by the on-chip bandgap reference voltage and control amplifier. The full-scale output current equals 32 times this bias current. The full-scale output current  $I_{OUT_{FS}}$  can thus be expressed as:

$$I_{OUT_{FS}} = 32 \times I_{BIAS} = \frac{32 \times V_{EXTIO}}{R_{BIAS}}$$

where  $V_{EXTIO}$  is the voltage at terminal EXTIO. The bandgap reference voltage delivers an accurate voltage of 1.2 V. This reference is active when terminal EXTLO is connected to AGND. An external decoupling capacitor  $C_{EXT}$  of 0.1  $\mu$ F should be connected externally to terminal EXTIO for compensation. The bandgap reference can additionally be used for external reference operation. In that case, an external buffer with high impedance input should be applied in order to limit the bandgap load current to a maximum of 100 nA. The internal reference can be disabled and overridden by an external reference by connecting EXTLO to AV<sub>DD</sub>. Capacitor  $C_{EXT}$  may hence be omitted. Terminal EXTIO thus serves as either input or output node.

The full-scale output current can be adjusted from 20 mA down to 2 mA by varying resistor  $R_{BIAS}$  or changing the externally applied reference voltage. The internal control amplifier has a wide input range, supporting the full-scale output current range of 20 dB. The bandwidth of the internal control amplifier is defined by the internal 1 nF compensation capacitor at pin COMP1 and the external compensation capacitor C1. The relatively weak internal control amplifier may be overridden by an externally applied amplifier with sufficient drive for the internal 1 nF load, as shown in Figure 25. This provides the user with more flexibility and higher bandwidths, which are specifically attractive for gain control and multiplying DAC applications. Pin SLEEP should be connected to AGND or left disconnected when an external control amplifier is used.

**Figure 25. Bypassing the Internal Reference and Control Amplifier**

## APPLICATION INFORMATION

### analog current outputs

Figure 26 shows a simplified schematic of the current source array output with corresponding switches. Differential PMOS switches direct the current of each individual PMOS current source to either the positive output node IOUT1 or its complementary negative output node IOUT2. The output impedance is determined by the stack of the current sources and differential switches, and is typically  $>300\text{ k}\Omega$  in parallel with an output capacitance of 5 pF.

Output nodes IOUT1 and IOUT2 have a negative compliance voltage of  $-1\text{ V}$ , determined by the CMOS process. Beyond this value, transistor breakdown may occur, resulting in reduced reliability of the THS5641A device. The positive output compliance depends on the full-scale output current IOUT<sub>FS</sub> and positive supply voltage AV<sub>DD</sub>. The positive output compliance equals  $1.25\text{ V}$  for AV<sub>DD</sub> =  $5\text{ V}$  and IOUT<sub>FS</sub> =  $20\text{ mA}$ . For AV<sub>DD</sub> =  $3.3\text{ V}$  the output compliance is limited to  $0.6\text{ V}$ . Exceeding the positive compliance voltage adversely affects distortion performance and integral nonlinearity. The optimum distortion performance for a single-ended or differential output is achieved when the maximum full-scale signal at IOUT1 and IOUT2 does not exceed  $0.5\text{ V}$  (e.g. when applying a  $50\text{ }\Omega$  doubly terminated load for  $20\text{ mA}$  full-scale output current). Applications requiring the THS5641A output (i.e., OUT1 and/or OUT2) to extend its output compliance should size R<sub>LOAD</sub> accordingly.

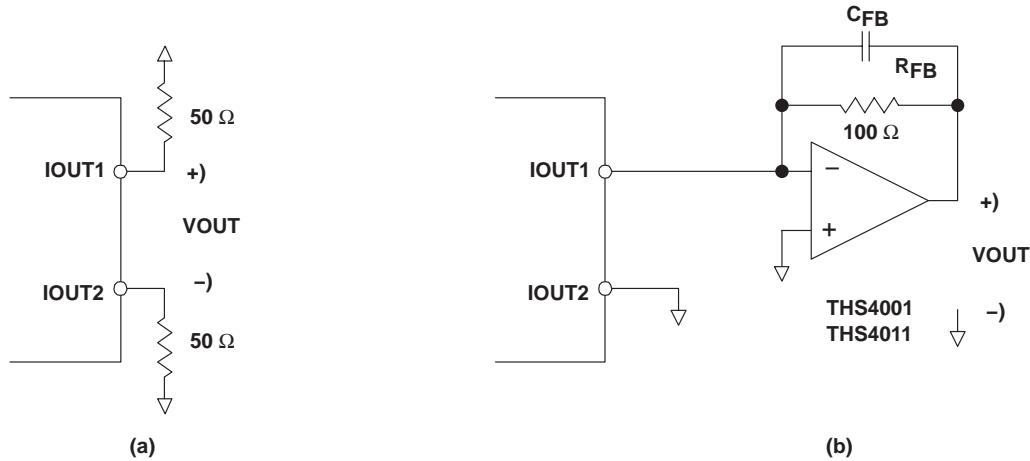

Figure 26. Equivalent Analog Current Output

Figure 27(a) shows the typical differential output configuration with two matched externally resistor loads. The nominal resistor load of  $50\text{ }\Omega$  will give a differential output swing of  $2\text{ V}_{\text{PP}}$  when applying a  $20\text{ mA}$  full-scale output current. The output impedance of the THS5641A depends slightly on the output voltage at nodes IOUT1 and IOUT2. Consequently, for optimum dc integral nonlinearity, the configuration of Figure 27(b) should be chosen. In this I-V configuration, terminal IOUT1 is kept at virtual ground by the inverting operational amplifier. The complementary output should be connected to ground to provide a dc current path for the current sources switched to IOUT2. Note that the INL/DNL specifications for the THS5641A are measured with IOUT1 maintained at virtual ground. The amplifier's maximum output swing and the DAC's full-scale output current determine the value of the feedback resistor R<sub>FB</sub>. Capacitor C<sub>FB</sub> filters the steep edges of the THS5641A current output, thereby reducing the operational amplifier slew-rate requirements. In this configuration, the op amp should operate on a dual supply voltage due to its positive and negative output swing. Node IOUT1 should be selected if a single-ended unipolar output is desirable.

**THS5641A**

**8-BIT, 100 MSPS, CommsDAC™**

**DIGITAL-TO-ANALOG CONVERTER**

SLAS277A –MARCH 2000 – REVISED SEPTEMBER 2002

**APPLICATION INFORMATION**

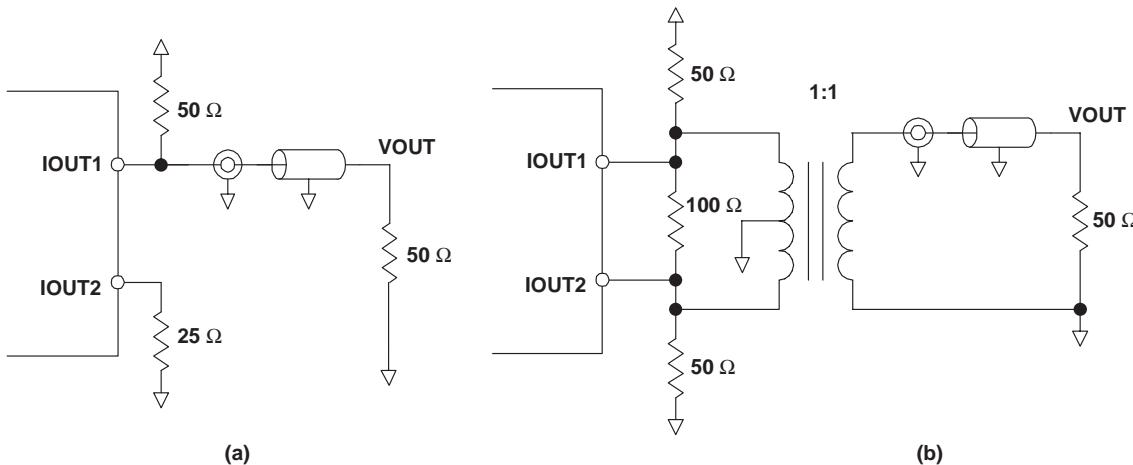

**Figure 27. Differential and Single-Ended Output Configuration**

The THS5641A can be easily configured to drive a doubly terminated 50 Ω cable. Figure 28(a) shows the single-ended output configuration, where the output current IOUT1 flows into an equivalent load resistance of 25 Ω. Node IOUT2 should be connected to ground or terminated with a resistor of 25 Ω. Differential-to-single conversion (e.g., for measurement purposes) can be performed using a properly selected RF transformer, as shown in Figure 28(b). This configuration provides maximum rejection of common-mode noise sources and even order distortion components, thereby doubling the power to the output. The center tap on the primary side of the transformer is connected to AGND, enabling a dc current flow for both IOUT1 and IOUT2. Note that the ac performance of the THS5641A is optimum using this differential transformer coupled output, limiting the voltage swing at IOUT1 and IOUT2 to  $\pm 0.5$  V.

**Figure 28. Driving a Doubly Terminated 50 Ω Cable**

---

## APPLICATION INFORMATION

### **sleep mode**

The THS5641A features a power-down mode that turns off the output current and reduces the supply current to less than 5 mA over the analog supply range of 3 V to 5.5 V and temperature range. The power-down mode is activated by applying a logic level 1 to the SLEEP pin (e.g., by connecting pin SLEEP to AVDD). An internal pulldown circuit at node SLEEP ensures that the THS5641A is enabled if the input is left disconnected. Power-up and power-down activation times depend on the value of external capacitor at node SLEEP. For a nominal capacitor value of 0.1  $\mu$ F power down takes less than 5  $\mu$ s, and approximately 3 ms to power backup. The SLEEP mode should not be used when an external control amplifier is used, as shown in Figure 25.

### **definitions of specifications and terminology**

#### **integral nonlinearity (INL)**

The relative accuracy or integral nonlinearity (INL), sometimes referred to as linearity error, is the maximum deviation of the output from the line between zero and full scale excluding the effects of zero code and full-scale errors.

#### **differential nonlinearity (DNL)**

The differential nonlinearity (DNL), sometimes referred to as differential error, is the difference between the measured and ideal 1 LSB amplitude change of any two adjacent codes. Monotonic means the output voltage changes in the same direction (or remains constant) as a change in the digital input code.

#### **offset error**

Offset error is defined as the deviation of the output current from the ideal of zero at a digital input value of 0.

#### **gain error**

Gain error is the error in slope of the DAC transfer function.

#### **signal-to-noise and distortion ratio (S/N+D or SINAD)**

S/N+D or SINAD is the ratio of the rms value of the output signal to the rms sum of all other spectral components below the Nyquist frequency, including harmonics but excluding dc. The value for S/N+D is expressed in decibels.

#### **spurious free dynamic range (SFDR)**

SFDR is the difference between the rms value of the output signal and the rms value of the largest spurious signal within a specified bandwidth. The value for SFDR is expressed in decibels.

#### **total harmonic distortion (THD)**

THD is the ratio of the rms sum of the first six harmonic components to the rms value of the fundamental signal and is expressed in decibels.

#### **output compliance range**

The maximum and minimum allowable voltage of the output of the DAC, beyond which either saturation of the output stage or breakdown may occur.

#### **settling time**

The time required for the output to settle within a specified error band.

#### **glitch energy**

The time integral of the analog value of the glitch transient.

---

**THS5641A**

**8-BIT, 100 MSPS, CommsDAC™**

**DIGITAL-TO-ANALOG CONVERTER**

SLAS277A –MARCH 2000 – REVISED SEPTEMBER 2002**offset drift**

The change in offset error versus temperature from the ambient temperature ( $T_A = 25^\circ\text{C}$ ) in ppm of full-scale range per  $^\circ\text{C}$ .

**gain drift**

The change in gain error versus temperature from the ambient temperature ( $T_A = 25^\circ\text{C}$ ) in ppm of full-scale range per  $^\circ\text{C}$ .

**reference voltage drift**

The change in reference voltage error versus temperature from the ambient temperature ( $T_A = 25^\circ\text{C}$ ) in ppm of full-scale range per  $^\circ\text{C}$ .

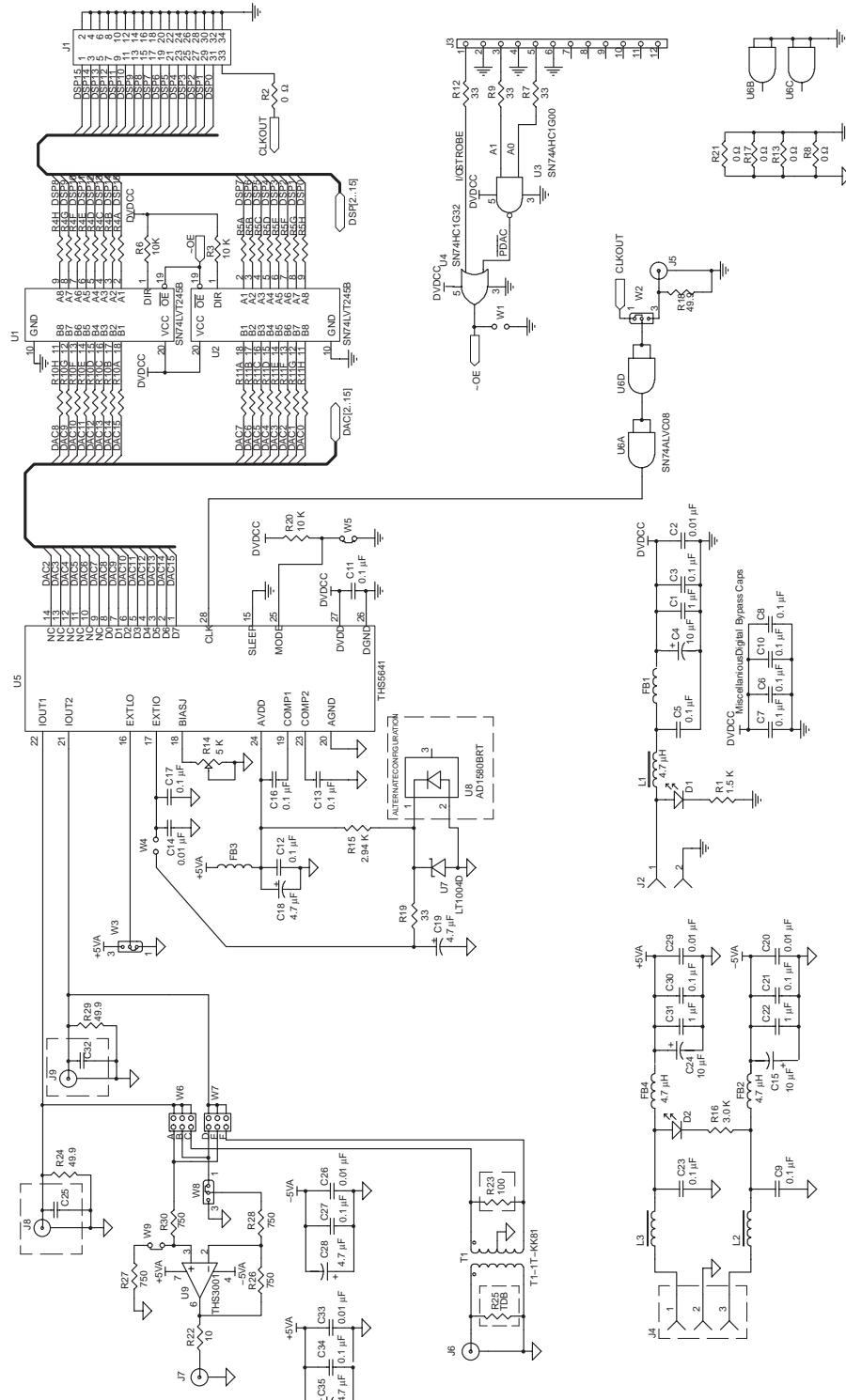

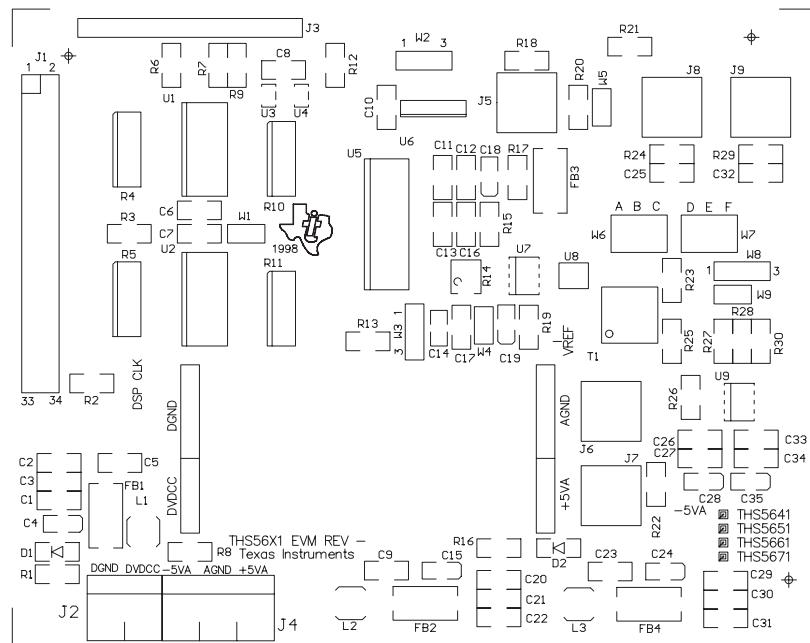

**THS5641A evaluation board**

An evaluation module (EVM) board for the THS5641A digital-to-analog converter is available for evaluation. This board allows the user the flexibility to operate the THS5641A in various configurations. Possible output configurations include transformer coupled, resistor terminated, and inverting/noninverting amplifier outputs. The digital inputs are designed to interface with the TMS320 C5000 or C6000 family of DSPs or to be driven directly from various pattern generators with the onboard option to add a resistor network for proper load termination.

See the *THS56x1 Evaluation Module User's Guide* for more details (SLAU032).

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

## APPLICATION INFORMATION

**Figure 29. Schematic**

**THS5641A**

**8-BIT, 100 MSPS, CommsDAC™**

**DIGITAL-TO-ANALOG CONVERTER**

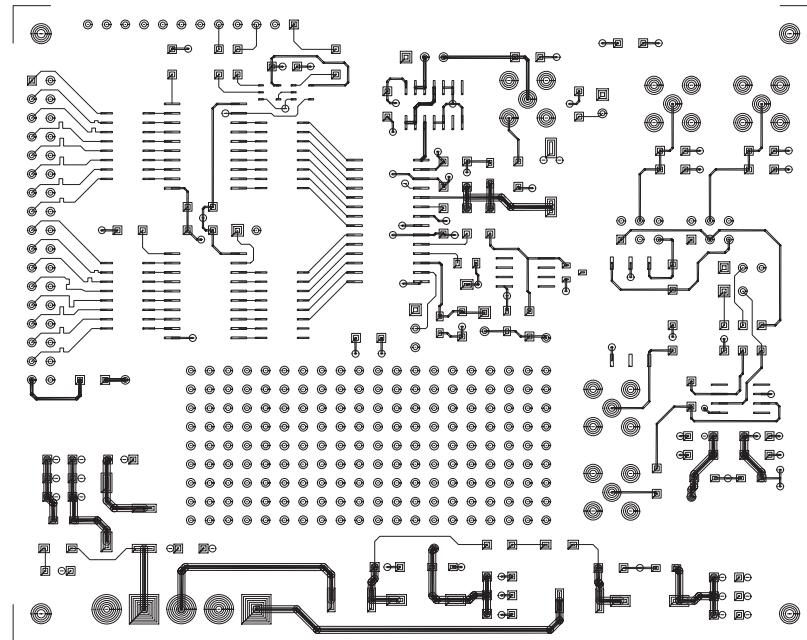

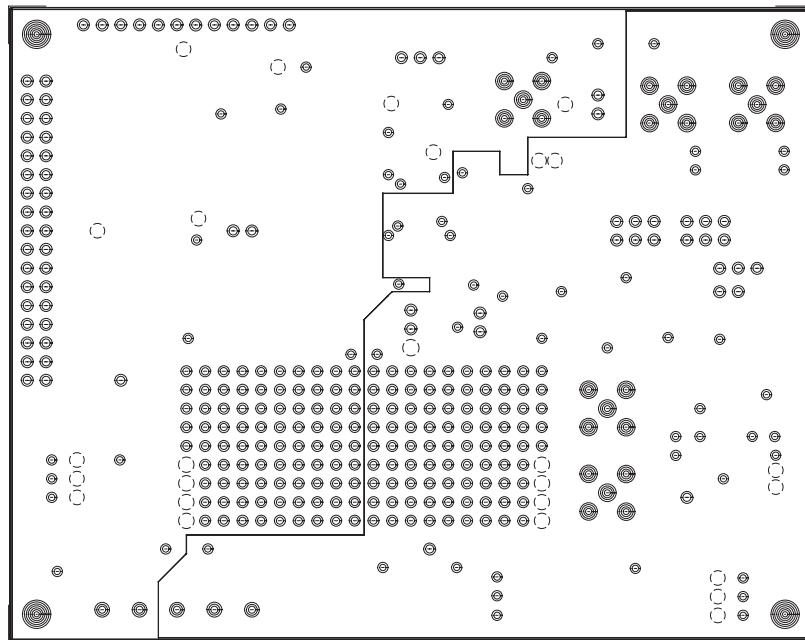

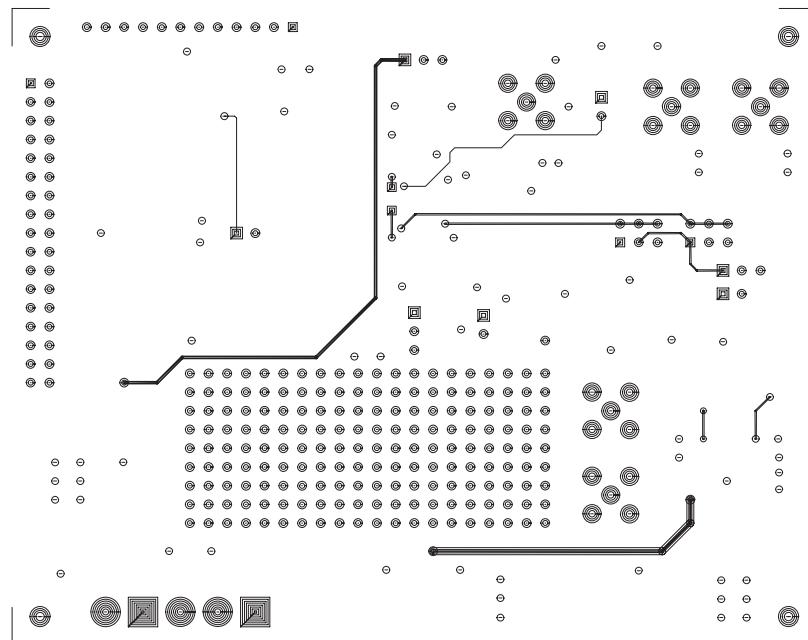

SLAS277A -MARCH 2000 – REVISED SEPTEMBER 2002**APPLICATION INFORMATION****Figure 30. Board Layout, Layer 1****Figure 31. Board Layout, Layer 2**

**THS5641A**

**8-BIT, 100 MSPS, CommsDAC™**

**DIGITAL-TO-ANALOG CONVERTER**

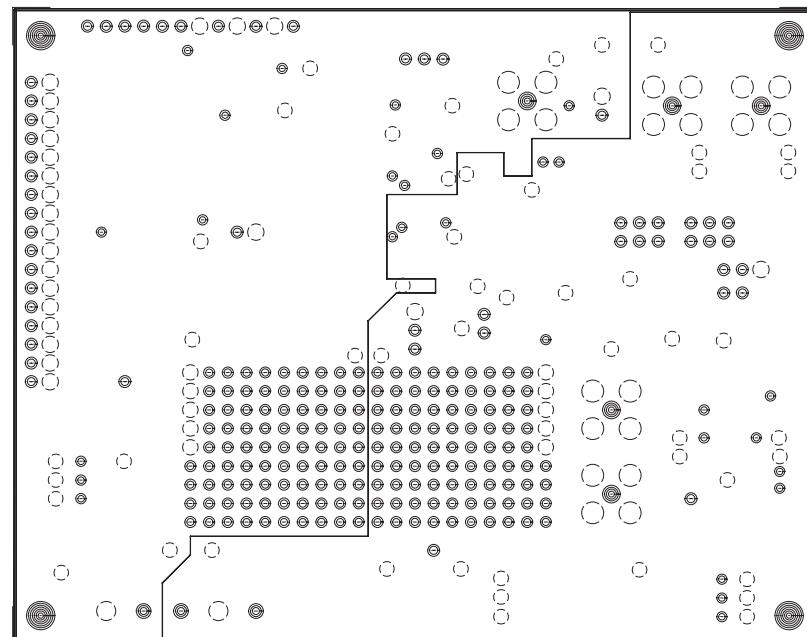

SLAS277A –MARCH 2000 – REVISED SEPTEMBER 2002**APPLICATION INFORMATION****Figure 32. Board Layout, Layer 3****Figure 33. Board Layout, Layer 4**

**THS5641A**

**8-BIT, 100 MSPS, CommsDAC™**

**DIGITAL-TO-ANALOG CONVERTER**

SLAS277A –MARCH 2000 – REVISED SEPTEMBER 2002

## APPLICATION INFORMATION

**Figure 34. Board Layout, Layer 5**

**Table 2. Bill of Materials**

| QTY | REF. DES                                                                      | PART NUMBER                  | DESCRIPTION                                   | MFG.               |

|-----|-------------------------------------------------------------------------------|------------------------------|-----------------------------------------------|--------------------|

| 3   | C1, C22, C31                                                                  | 1206ZC105KAT2A               | Ceranucm 1 $\mu$ F, 10 V, X7R, 10%            | AVX                |

| 4   | C18, C19, C28, C35                                                            | ECSTOJY475                   | 6.3 V, 4.7 $\mu$ F, tantalum                  | Panasonic          |

| 3   | C15, C24, C4                                                                  | ECSTOJY106                   | 6.3 V, 10 $\mu$ F, tantalum                   | Panasonic          |

| 0   | C25, C32                                                                      |                              | Ceramic, not installed, 50 V, X7R, 10%        |                    |

| 6   | C14, C2, C20, C26, C29, C33                                                   | 12065C103KAT2A               | Ceramic, 0.01 $\mu$ F, 50 V, X7R, 10%         | AVX                |

| 17  | C10, C11, C12, C13, C16, C17, C21, C23, C27, C3, C30, C34, C5, C6, C7, C8, C9 | 12065C104KAT2A               | Ceramic, 0.1 $\mu$ F, 50 V, X7R, 10%          | AVX                |

| 2   | D1, D2                                                                        | AND/AND5GA or equivalent     | GREEN LED, 1206 size SM chip LED              |                    |

| 4   | FB1, FB2, FB3, FB4                                                            | 27-43-037447                 | Fair-Rite SM beads #27-037447                 | FairRite           |

| 1   | J1                                                                            | TSW-117-07-L-D or equivalent | 34-Pin header for IDC                         | Samtec             |

| 1   | J2                                                                            | KRMZ2 or equivalent          | 2 Terminal screw connector, 2TERM_CON         | Lumberg            |

| 1   | J3                                                                            | TSW-112-07-L-S or equivalent | Single row 12-pin header                      | Samtec             |

| 1   | J4                                                                            | KRMZ3 or equivalent          | 3 Terminal screw connector                    | Lumberg            |

| 3   | J5, J6, J7                                                                    | 142-0701-206 or equivalent   | PCB Mount SMA jack, SMA_PCB_MT                | Johnson Components |

| 0   | J8, J9                                                                        | 142-0701-206 or equivalent   | PCB Mount SMA jack, not installed             | Johnson Components |

| 3   | L1, L2, L3                                                                    | DO1608C-472                  | DO1608C-series, DS1608C-472                   | Coil Craft         |

| 1   | R1                                                                            | 1206                         | 1206 Chip resistor, 1.5K, 1/4 W, 1%           |                    |

| 4   | R10, R11, R4, R5                                                              | CTS/CTS766-163-(R)330-G-TR   | 8 Element isolated resistor pack, 33 $\Omega$ |                    |

**THS5641A**

**8-BIT, 100 MSPS, CommsDAC™**

**DIGITAL-TO-ANALOG CONVERTER**

SLAS277A –MARCH 2000 – REVISED SEPTEMBER 2002

**APPLICATION INFORMATION**

**Table 2. Bill of Materials (Continued)**

| QTY | REF. DES              | PART NUMBER                           | DESCRIPTION                                  | MFG.         |

|-----|-----------------------|---------------------------------------|----------------------------------------------|--------------|

| 4   | R12, R19, R7, R9      | 1206                                  | 1206 Chip resistor, 33 Ω, 1/4 W, 1%          |              |

| 5   | R13, R17, R2, R21, R8 | 1206                                  | 1206 Chip resistor, 0 Ω, 1/4 W, 1%           |              |

| 1   | R14                   | 3214W-1-502 E or equivalent           | 4 mm SM Pot, 5K                              | Bourns       |

| 1   | R15                   | 1206                                  | 1206 Chip resistor, 2.94K, 1/4 W, 1%         |              |

| 1   | R16                   | 1206                                  | 1206 Chip resistor, 3K, 1/4 W, 1%            |              |

| 3   | R18, R24, R29         | 1206                                  | 1206 Chip resistor, 49.94K, 1/4 W, 1%        |              |

| 3   | R20, R3, R6           | 1206                                  | 1206 Chip resistor, 10K, 1/4 W, 1%           |              |

| 1   | R22                   | 1206                                  | 1206 Chip resistor, 10K, 1/4 W, 1%           |              |

| 1   | R23                   | 1206                                  | 1206 Chip resistor, 100K, 1/4 W, 1%          |              |

| 1   | R25                   | 1206                                  | 1206 Chip resistor, TBD, 1/4 W, 1%           |              |

| 4   | R26, R27, R28, R30    | 1206                                  | 1206 Chip resistor, 750K, 1/4 W, 1%          |              |

| 1   | T1                    | T1-1T-KK81                            | RF Transformer, T1-1T-KK81                   | MiniCircuits |

| 2   | U1, U2                | SN74LVT245BDW                         | Octal bus transceiver, 3-state, SN74LVT245B  | TI           |

| 1   | U3                    | SN74AHCT1G00DBVR/<br>SN74AHC1G00DBVR  | Single gate NAND, SN74AHC1G00                | TI           |

| 1   | U4                    | SN74AHCT1G32DBVR/<br>SN74AHCC1G32DBVR | Single 2 input positive or gate, SN74AHC1G32 | TI           |

|     | THS5641A              | THS5641AIDW                           | DAC, 3–5.5 V, 8 Bit, 100 MSPS                | TI           |

|     | THS5651A              | THS5651AIDW                           | DAC, 3–5.5 V, 10 Bit, 125 MSPS               | TI           |

|     | THS5661A              | THS5661AIDW                           | DAC, 3–5.5 V, 12 Bit, 125 MSPS               | TI           |

|     | THS5671A              | THS5671AIDW                           | DAC, 3–5.5 V, 14 Bit, 125 MSPS               | TI           |

| 1   | SN74ALVC08            | SN74ALVC08D                           | Quad AND gate                                | TI           |

| 1   | LT1004D               | LT1004CD-1-2/LT1004ID-1-2             | Precision 1.2 V reference                    | TI           |

| 0   | NOT INSTALLED         | AD1580BRT                             | Precision voltage reference, not installed   |              |

| 1   | THS3001               | THS3001CD/THS2001ID                   | THS3001 high-speed op amp                    | TI           |

| 4   | W2                    | TSW-102-07-L-S or equivalent          | 2 position jumper_.1" spacing, W2            | Samtec       |

| 3   | W3                    | TSW-102-07-L-S or equivalent          | 3 position jumper_.1" spacing, W3            | Samtec       |

| 2   | 2X3_JUMPER            | TSW-102-07-L-S or equivalent          | 6-Pin header dual row, 0.025×0.1, 2X3_JUMPER | Samtec       |

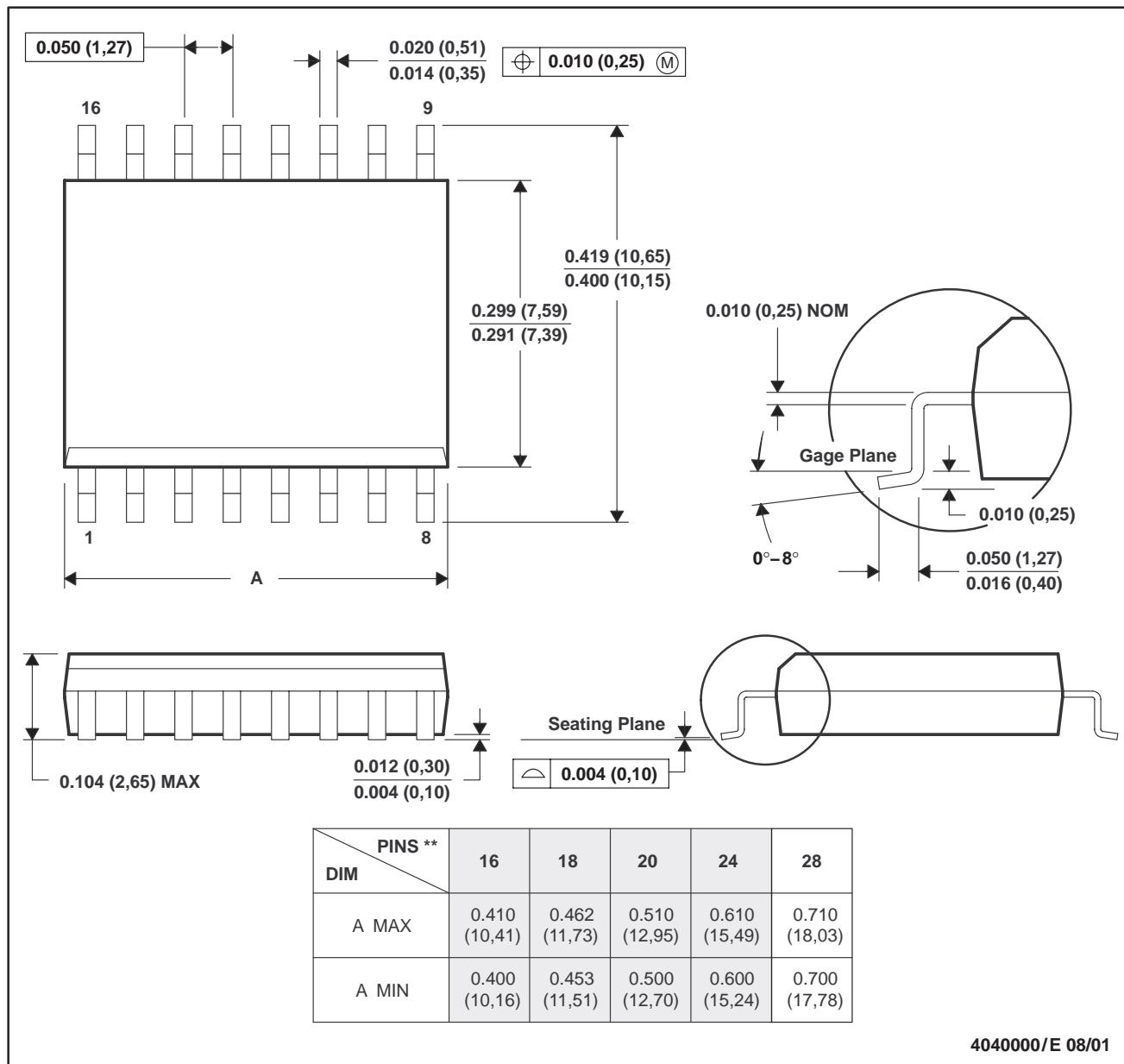

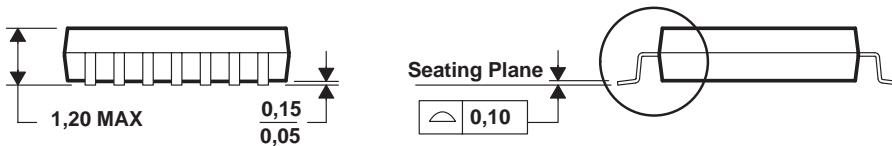

**MECHANICAL DATA**

**DW (R-PDSO-G\*\*)**

16 PINS SHOWN

**PLASTIC SMALL-OUTLINE PACKAGE**

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

D. Falls within JEDEC MS-013

**THS5641A**

**8-BIT, 100 MSPS, CommsDAC™**

**DIGITAL-TO-ANALOG CONVERTER**

SLAS277A –MARCH 2000 – REVISED SEPTEMBER 2002

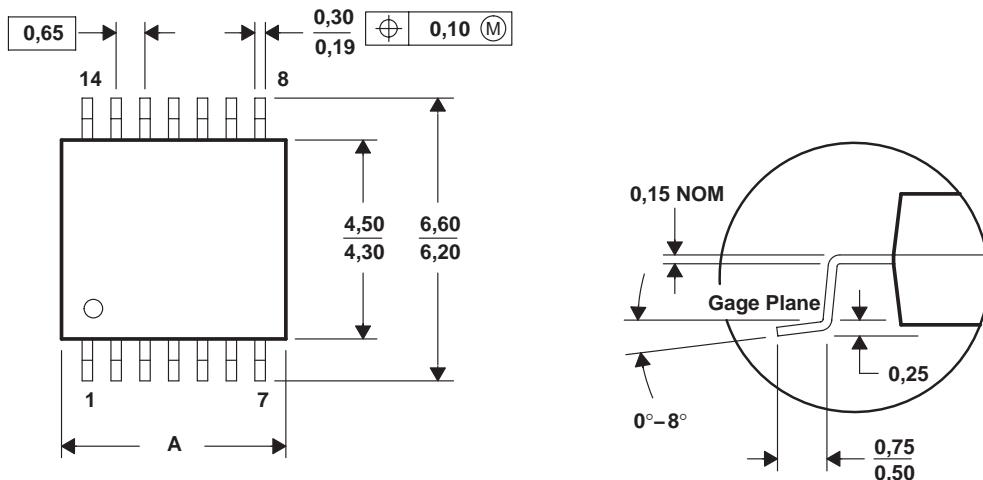

**MECHANICAL DATA**

**PW (R-PDSO-G\*\*)**

14 PINS SHOWN

**PLASTIC SMALL-OUTLINE PACKAGE**

| DIM   | PINS ** | 8    | 14   | 16   | 20   | 24   | 28   |

|-------|---------|------|------|------|------|------|------|

| A MAX |         | 3,10 | 5,10 | 5,10 | 6,60 | 7,90 | 9,80 |

| A MIN |         | 2,90 | 4,90 | 4,90 | 6,40 | 7,70 | 9,60 |

4040064/F 01/97

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

D. Falls within JEDEC MO-153

**PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package Type | Package Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|--------------|-----------------|------|-------------|-------------------------|------------------|------------------------------|

| THS5641AIDW      | ACTIVE                | SOIC         | DW              | 28   | 20          | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

| THS5641AIDWG4    | ACTIVE                | SOIC         | DW              | 28   | 20          | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

| THS5641AIDWR     | ACTIVE                | SOIC         | DW              | 28   | 1000        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

| THS5641AIDWRG4   | ACTIVE                | SOIC         | DW              | 28   | 1000        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

| THS5641AIPW      | ACTIVE                | TSSOP        | PW              | 28   | 50          | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

| THS5641AIPWG4    | ACTIVE                | TSSOP        | PW              | 28   | 50          | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

| THS5641AIPWR     | ACTIVE                | TSSOP        | PW              | 28   | 2000        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

| THS5641AIPWRG4   | ACTIVE                | TSSOP        | PW              | 28   | 2000        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

<sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check <http://www.ti.com/productcontent> for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

**Green (RoHS & no Sb/Br):** TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

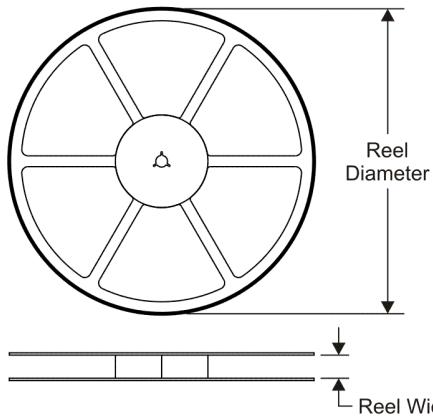

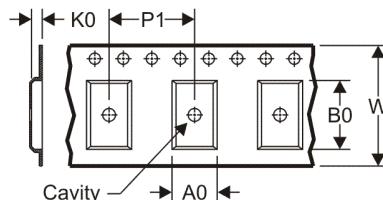

**TAPE AND REEL INFORMATION**

**REEL DIMENSIONS**

**TAPE DIMENSIONS**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

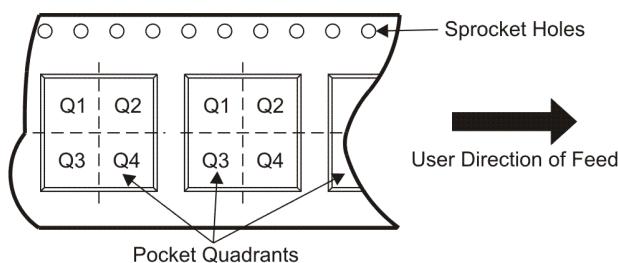

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| THS5641AIDWR | SOIC         | DW              | 28   | 1000 | 330.0              | 32.4               | 11.35   | 18.67   | 3.1     | 16.0    | 32.0   | Q1            |

| THS5641AIPWR | TSSOP        | PW              | 28   | 2000 | 330.0              | 16.4               | 6.9     | 10.2    | 1.8     | 12.0    | 16.0   | Q1            |

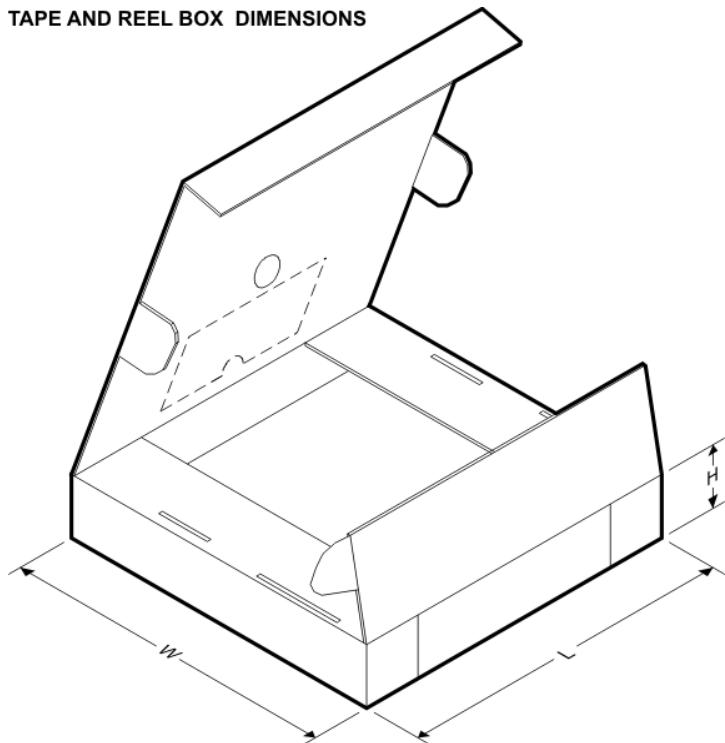

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| THS5641AIDWR | SOIC         | DW              | 28   | 1000 | 346.0       | 346.0      | 49.0        |

| THS5641AIPWR | TSSOP        | PW              | 28   | 2000 | 346.0       | 346.0      | 33.0        |

**IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

**Products**

|                             |                                                                    |

|-----------------------------|--------------------------------------------------------------------|

| Amplifiers                  | <a href="http://amplifier.ti.com">amplifier.ti.com</a>             |

| Data Converters             | <a href="http://dataconverter.ti.com">dataconverter.ti.com</a>     |

| DLP® Products               | <a href="http://www.dlp.com">www.dlp.com</a>                       |

| DSP                         | <a href="http://dsp.ti.com">dsp.ti.com</a>                         |

| Clocks and Timers           | <a href="http://www.ti.com/clocks">www.ti.com/clocks</a>           |

| Interface                   | <a href="http://interface.ti.com">interface.ti.com</a>             |

| Logic                       | <a href="http://logic.ti.com">logic.ti.com</a>                     |

| Power Mgmt                  | <a href="http://power.ti.com">power.ti.com</a>                     |

| Microcontrollers            | <a href="http://microcontroller.ti.com">microcontroller.ti.com</a> |

| RFID                        | <a href="http://www.ti-rfid.com">www.ti-rfid.com</a>               |

| RF/IF and ZigBee® Solutions | <a href="http://www.ti.com/lprf">www.ti.com/lprf</a>               |

**Applications**

|                    |                                                                          |

|--------------------|--------------------------------------------------------------------------|

| Audio              | <a href="http://www.ti.com/audio">www.ti.com/audio</a>                   |

| Automotive         | <a href="http://www.ti.com/automotive">www.ti.com/automotive</a>         |

| Broadband          | <a href="http://www.ti.com/broadband">www.ti.com/broadband</a>           |

| Digital Control    | <a href="http://www.ti.com/digitalcontrol">www.ti.com/digitalcontrol</a> |

| Medical            | <a href="http://www.ti.com/medical">www.ti.com/medical</a>               |

| Military           | <a href="http://www.ti.com/military">www.ti.com/military</a>             |

| Optical Networking | <a href="http://www.ti.com/opticalnetwork">www.ti.com/opticalnetwork</a> |

| Security           | <a href="http://www.ti.com/security">www.ti.com/security</a>             |

| Telephony          | <a href="http://www.ti.com/telephony">www.ti.com/telephony</a>           |

| Video & Imaging    | <a href="http://www.ti.com/video">www.ti.com/video</a>                   |

| Wireless           | <a href="http://www.ti.com/wireless">www.ti.com/wireless</a>             |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2009, Texas Instruments Incorporated