## **Excellent Integrated System Limited**

Stocking Distributor

Click to view price, real time Inventory, Delivery & Lifecycle Information:

Maxim Integrated MAX3280EAUK-T

For any questions, you can email us directly: <u>sales@integrated-circuit.com</u>

Distributor of Maxim Integrated: Excellent Integrated System Limited Datasheet of MAX3280EAUK-T - IC RCVR 52MBPS RS-485/422 SOT23 Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

19-2320; Rev 0; 1/02

## ±15kV ESD-Protected 52Mbps, 3V to 5.5V, SOT23 RS-485/RS-422 True Fail-Safe Receivers

### **General Description**

The MAX3280E/MAX3281E/MAX3283E/MAX3284E are single receivers designed for RS-485 and RS-422 communication. These devices guarantee data rates up to 52Mbps, even with a 3V power supply. Excellent propagation delay (15ns max) and package-to-package skew time (8ns max) make these devices ideal for multidrop clock distribution applications.

The MAX3280E/MAX3281E/MAX3283E/MAX3284E have true fail-safe circuitry, which guarantees a logichigh receiver output when the receiver inputs are opened or shorted. The receiver output will be a logic high if all transmitters on a terminated bus are disabled (high impedance). These devices feature 1/4-unit-load receiver input impedance, allowing up to 128 receivers on the same bus.

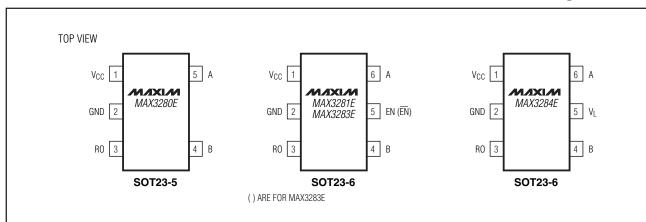

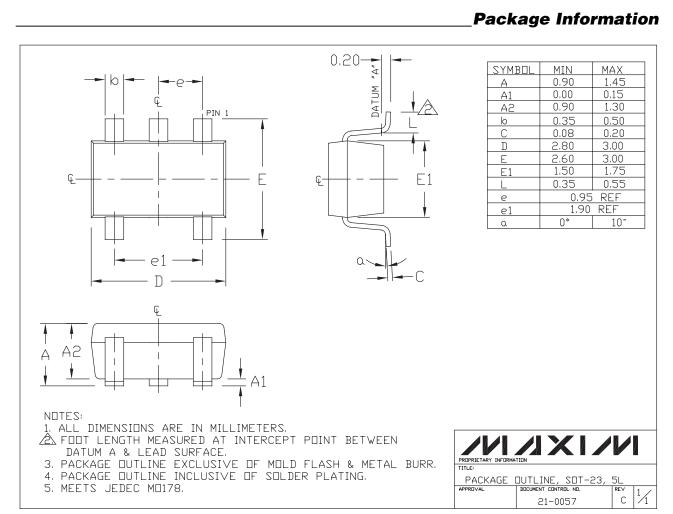

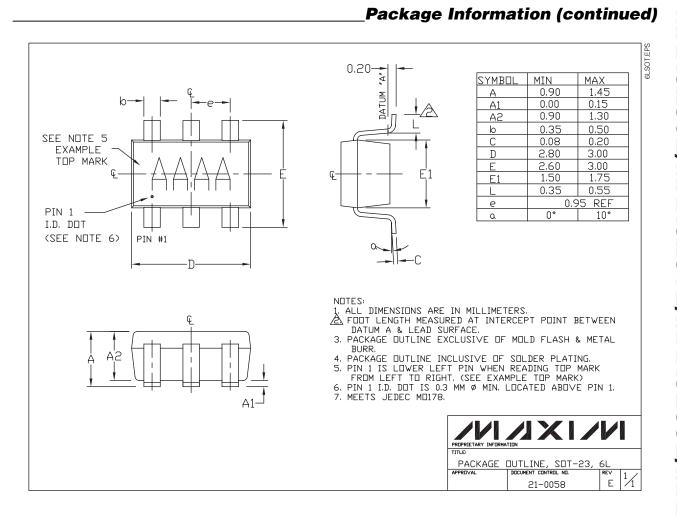

The MAX3280E is a single receiver available in a 5-pin SOT23 package. The MAX3281E/MAX3283E single receivers have a receiver enable (EN or EN) function and are offered in a 6-pin SOT23 package. The MAX3284E features a voltage logic pin that allows compatibility with low-voltage logic levels, as in digital FPGAs/ASICs. On the MAX3284E, the voltage threshold for a logic high is user-defined by setting VL in the range from 1.65V to VCC. The MAX3284E is also offered in a 6-pin SOT23 package.

- ESD Protection: ±15kV-Human Body Model ±6kV-IEC 1000-4-2, Contact Discharge ±12kV-IEC 1000-4-2, Air-Gap Discharge

- Guaranteed 52Mbps Data Rate

- Guaranteed 15ns Receiver Propagation Delay

- Guaranteed 2ns Receiver Skew

- Guaranteed 8ns Package-to-Package Skew Time

- VL Pin for Connection to FPGAs/ASICs

- Allow Up to 128 Transceivers on the Bus (1/4-unit-load)

- Tiny SOT23 Package

- True Fail-Safe Receiver

- -7V to +12V Common-Mode Range

- ♦ 3V to 5.5V Power-Supply Range

- Enable (High and Low) Pins for Redundant Operation

- Three-State Output Stage (MAX3281E/MAX3283E)

- Thermal Protection Against Output Short Circuit

Applications

**Clock Distribution Telecom Racks Base Stations** Industrial Control

Local Area Networks

Pin Configurations appear at end of data sheet.

### **Ordering Information**

| PART          | TEMP RANGE      | PIN-<br>PACKAGE | TOP<br>MARK |

|---------------|-----------------|-----------------|-------------|

| MAX3280EAUK-T | -40°C to +125°C | 5 SOT23-5       | ADVM        |

| MAX3281EAUT-T | -40°C to +125°C | 6 SOT23-6       | ABAT        |

| MAX3283EAUT-T | -40°C to +125°C | 6 SOT23-6       | ABAU        |

| MAX3284EAUT-T | -40°C to +125°C | 6 SOT23-6       | ABAV        |

### Selector Guide

| PART     | VL       | ENABLE      | DATA RATE       | PACKAGE     |

|----------|----------|-------------|-----------------|-------------|

| MAX3280E | _        | —           | 52Mbps          | 5-Pin SOT23 |

| MAX3281E | —        | Active High | 52Mbps          | 6-Pin SOT23 |

| MAX3283E | —        | Active Low  | 52Mbps          | 6-Pin SOT23 |

| MAX3284E | <b>v</b> | —           | 52Mbps (Note 1) | 6-Pin SOT23 |

Note 1: MAX3284E data rate is dependent on VL.

### M/XI/M

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

**Features**

### **ABSOLUTE MAXIMUM RATINGS**

(All Voltages Referenced to GND)

| (                                                            |                                                       |

|--------------------------------------------------------------|-------------------------------------------------------|

| Supply Voltage (V <sub>CC</sub> )0.3V to +6V                 | Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

| Control Input Voltage (EN, EN)0.3V to +6V                    | 5-Pin SOT23 (derate 7.1mW/°C above +70°C)571mW        |

| VL Input Voltage0.3V to +6V                                  | 6-Pin SOT23 (derate 8.7mW/°C above +70°C)696mW        |

| Receiver Input Voltage (A, B)7.5V to +12.5V                  | Operating Temperature Range                           |

| Receiver Output Voltage (RO)0.3V to (V <sub>CC</sub> + 0.3V) | MAX328_EA40°C to +125°C                               |

| Receiver Output Voltage                                      | Storage Temperature Range65°C to +150°C               |

| (RO) (MAX3284E)0.3V to (V <sub>L</sub> + 0.3V)               | Junction Temperature+150°C                            |

| Receiver Output Short-Circuit CurrentContinuous              | Lead Temperature (soldering, 10s)+300°C               |

|                                                              |                                                       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### ELECTRICAL CHARACTERISTICS

$(V_{CC} = 3V \text{ to } 5.5V, V_L = V_{CC}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } V_{CC} = 5V \text{ and } T_A = +25^{\circ}C.)$  (Notes 2, 3)

| PARAMETER                                  | SYMBOL            | CONDITIONS                                                                              |                 | MIN                   | ТҮР  | MAX  | UNITS |

|--------------------------------------------|-------------------|-----------------------------------------------------------------------------------------|-----------------|-----------------------|------|------|-------|

| Supply Voltage                             | Vcc               |                                                                                         |                 | 3.0                   |      | 5.5  | V     |

| Supply Current                             | Icc               | No load                                                                                 |                 |                       | 9    | 15   | mA    |

| V <sub>L</sub> Input Range                 | VL                | MAX3284E                                                                                |                 | 1.65                  |      | Vcc  | V     |

| V <sub>L</sub> Supply Current              | ١L                | No load (MAX3284E)                                                                      |                 |                       |      | 10   | μΑ    |

| RECEIVER                                   |                   |                                                                                         |                 |                       |      |      |       |

|                                            | 1                 |                                                                                         | $V_{IN} = +12V$ |                       |      | 250  |       |

| Input Current (A and B)                    | I <sub>A, B</sub> | $V_{CC} = GND \text{ or } 5.5V$                                                         | $V_{IN} = -7V$  |                       |      | -200 | μA    |

| Receiver Differential Threshold<br>Voltage | V <sub>TH</sub>   | -7V ≤ V <sub>CM</sub> ≤ +12V<br>(Note 4)                                                |                 | -200                  | -125 | -50  | mV    |

| Receiver Input Hysteresis                  | ΔVTH              | $V_A + V_B = 0$                                                                         |                 |                       | 25   |      | mV    |

| Receiver Enable Input Low                  | VENIL             | MAX3281E, MAX3283                                                                       | E only          |                       |      | 0.4  | V     |

| Receiver Enable Input High                 | VENIH             | MAX3281E, MAX3283                                                                       | E only          | 2                     |      |      | V     |

| Receiver Enable Input Leakage              | ILEAK             | MAX3281E, MAX3283                                                                       | E only          |                       |      | ±10  | μA    |

|                                            |                   | MAX3280E/MAX3281E/MAX3283E,<br>I <sub>OH</sub> = -4mA, RO high                          |                 | V <sub>CC</sub> - 0.4 |      |      |       |

| Receiver Output High Voltage               | Vон               | MAX3284E, $I_{OH}$ = -1mA, 1.65V $\leq$ V <sub>L</sub> $\leq$ V <sub>CC</sub> , RO high |                 | V <sub>L</sub> - 0.4  |      |      | V     |

|                                            |                   | MAX3280E/MAX3281E/MAX3283E,<br>I <sub>OL</sub> = 4mA, RO low                            |                 |                       |      | 0.4  |       |

| Receiver Output Low Voltage                | Vol               | MAX3284E, $I_{OL}$ = 1mA, 1.65V $\leq$ V <sub>L</sub> $\leq$ V <sub>CC</sub> , RO low   |                 |                       |      | 0.4  | V     |

| Three-State Output Current at Receiver     | Iozr              | $0 \le V_0 \le V_{CC}$ , RO = high impedance                                            |                 |                       |      | ±5   | μA    |

| Receiver Input Resistance                  | R <sub>IN</sub>   | $-7V \le V_{CM} \le +12V$ (Note 5)                                                      |                 | 48                    |      |      | kΩ    |

| Receiver Output Short-Circuit<br>Current   | IOSR              | $0 \le V_{RO} \le V_{CC}$                                                               |                 |                       |      | ±130 | mA    |

| ESD PROTECTION                             | •                 | •                                                                                       |                 | •                     |      |      |       |

|                                            |                   | Human Body Model                                                                        |                 |                       | ±15  |      |       |

| ESD Protection (A, B)                      |                   | IEC1000-4-2 (Air-Gap Discharge)                                                         |                 |                       | ±12  |      | kV    |

|                                            |                   | IEC1000-4-2 (Contact                                                                    | Discharge)      |                       | ±6   |      | 1     |

M/IXI/M

2

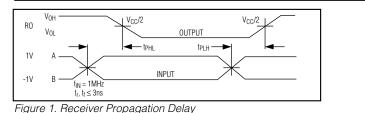

### SWITCHING CHARACTERISTICS

(V<sub>CC</sub> = 3V to 5.5V, V<sub>L</sub> = V<sub>CC</sub>, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at V<sub>CC</sub> = 5V and T<sub>A</sub> = +25°C.) (Notes 2, 3)

| PARAMETER                                      | SYMBOL            | CONDITIONS                                                                                | MIN | ТҮР | МАХ | UNITS |

|------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Maximum Data Rate                              | fMAX              | C <sub>L</sub> = 15pF (Notes 5, 6)                                                        | 52  |     |     | Mbps  |

| Pageiver Propagation Delay                     | t <sub>PLH</sub>  | Figure 1, $C_L$ = 15pF, $V_{ID}$ = 2V, $V_{CM}$ = 0                                       |     | 7   | 15  | 20    |

| Receiver Propagation Delay                     | <b>t</b> PHL      | Figure 1, $C_L$ = 15pF, $V_{ID}$ = 2V, $V_{CM}$ = 0                                       |     | 8   | 15  | ns    |

| Receiver Output ItpLH - tpHLI                  | <b>t</b> PSKEW    | Figure 1, $C_L$ = 15pF, $T_A$ = +25°C                                                     |     |     | 2   | ns    |

| Device-to-Device Propagation<br>Delay Matching |                   | Same power supply, maximum temperature<br>difference between devices = +30°C.<br>(Note 5) |     |     | 8   | ns    |

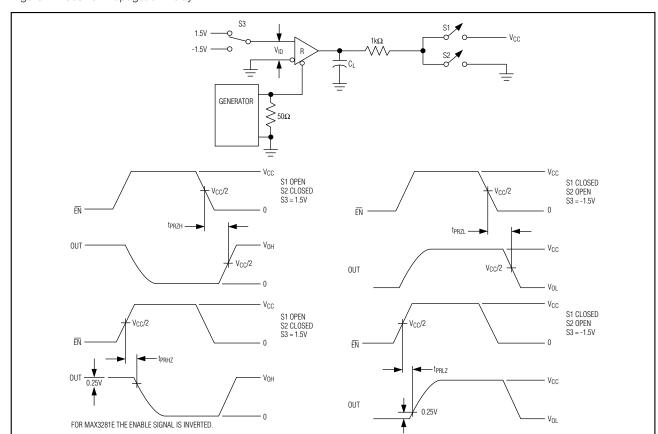

| ENABLE/DISABLE TIME FOR MAX3281E/MAX3283E      |                   |                                                                                           |     |     |     |       |

| Receiver Enable to Output Low                  | t <sub>PRZL</sub> | Figure 2, $C_L = 15pF$                                                                    |     |     | 500 | ns    |

| Receiver Enable to Output High                 | t <sub>PRZH</sub> | Figure 2, $C_L = 15pF$                                                                    |     |     | 500 | ns    |

| Receiver Disable Time from Low                 | t <sub>PRLZ</sub> | Figure 2, $C_L = 15 pF$                                                                   |     |     | 500 | ns    |

| Receiver Disable Time from High                | t <sub>PRHZ</sub> | Figure 2, $C_L = 15 pF$                                                                   |     |     | 500 | ns    |

Note 2: Parameters are 100% production tested at +25°C, limits over temperature are guaranteed by design.

Note 3: All currents into the device are positive; all currents out of the device are negative. All voltages are referenced to device ground, unless otherwise noted.

Note 4:  $V_{CM}$  is the common-mode input voltage.  $V_{ID}$  is the differential input voltage.

Note 5: Not production tested. Guaranteed by design.

Note 6: See Table 2 for MAX3284E data rates with  $V_L < V_{CC}$ .

5

4

3

2

1

0

OUTPUT VOLTAGE (V)

4

| Pin | Description |  |

|-----|-------------|--|

|     |             |  |

| PIN      |          |          | TUNGTION |                            |                                                                                                                                                                                                                      |

|----------|----------|----------|----------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX3280E | MAX3281E | MAX3283E | MAX3284E | NAME                       | FUNCTION                                                                                                                                                                                                             |

| 1        | 1        | 1        | 1        | V <sub>CC</sub>            | Positive Supply: $3V \le V_{CC} \le 5.5V$ . Bypass with a 0.1µF capacitor to GND.                                                                                                                                    |

| 2        | 2        | 2        | 2        | GND                        | Ground                                                                                                                                                                                                               |

| 3        | 3        | 3        | 3        | RO                         | Receiver Output. RO will be high if $(A-B) \ge -50$ mV. RO will be low if $(A-B) \le -200$ mV.                                                                                                                       |

| 4        | 4        | 4        | 4        | B Inverting Receiver Input |                                                                                                                                                                                                                      |

| _        | _        | 5        | _        | ĒN                         | Receiver Output Enable. Drive $\overline{\text{EN}}$ low to enable RO. When $\overline{\text{EN}}$ is high, RO is high impedance.                                                                                    |

| _        | 5        | _        | _        | EN                         | Receiver Output Enable. Drive EN high to enable RO. When EN is low, RO is high impedance.                                                                                                                            |

|          |          |          | 5        | VL                         | Low-Voltage Logic-Level Supply Voltage. V <sub>L</sub> is a user-defined voltage, ranging from 1.65V to V <sub>CC</sub> . RO output high is pulled up to V <sub>L</sub> . Bypass with a $0.1\mu$ F capacitor to GND. |

| 5        | 6        | 6        | 6        | А                          | Noninverting Receiver Input                                                                                                                                                                                          |

### **Detailed Description**

The MAX3280E/MAX3281E/MAX3283E/MAX3284E are single, true fail-safe receivers designed to operate at data rates up to 52Mbps. The fail-safe architecture guarantees a high output signal if both input terminals are open or shorted together. See the *True Fail-Safe* section. This feature assures a stable and predictable output logic state with any transmitter driving the line. These receivers function with a 3.3V or 5V supply voltage and feature excellent propagation delay times (15ns).

The MAX3280E is a single receiver available in a 5-pin SOT23 package. The MAX3281E (EN, active high) and MAX3283E (EN, active low) are single receivers that also contain an enable pin. Both the MAX3281E and MAX3283E are available in a 6-pin SOT23 package. The MAX3284E is a single receiver that contains a V<sub>L</sub> pin, which allows communication with low-level logic included in digital FPGAs. The MAX3284E is available in a 6-pin SOT23 package.

The MAX3284E's low-level logic application allows users to set the logic levels. A logic high level of 1.65V will limit the maximum data rate to 20Mbps.

### ±15kV ESD Protection

ESD-protection structures are incorporated on the receiver input pins to protect against ESD encountered during handling and assembly. The MAX3280E/MAX3281E/MAX3283E/MAX3284E receiver inputs (A, B) have extra protection against static electricity found in normal operation. Maxim's engineers developed state-of-the-art structures to protect these pins against

±15kV ESD without damage. After an ESD event, this family of parts continues working without latchup.

ESD protection can be tested in several ways. The receiver inputs are characterized for protection to the following:

- ±15kV using the Human Body Model

- ±6kV using the Contact Discharge method specified in IEC 1000-4-2 (formerly IEC 801-2)

- ±12kV using the Air-Gap Discharge method specified in IEC 1000-4-2 (formerly IEC 801-2)

### **ESD Test Conditions**

ESD performance depends on a number of conditions. Contact Maxim for a reliability report that documents test setup, methodology, and results.

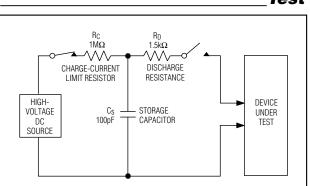

### Human Body Model

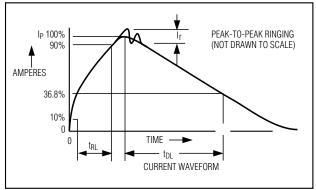

Figure 3a shows the Human Body Model, and Figure 3b shows the current waveform it generates when discharged into a low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the device through a  $1.5 k\Omega$  resistor.

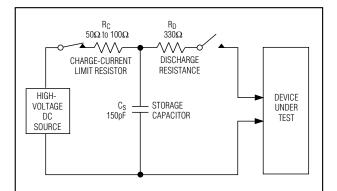

### IEC 1000-4-2

Since January 1996, all equipment manufactured and/or sold in the European community has been required to meet the stringent IEC 1000-4-2 specification. The IEC 1000-4-2 standard covers ESD testing and performance of finished equipment; it does not specifically refer to integrated circuits. The MAX3280E/MAX3281E/MAX3283E/MAX3284E help

users design equipment that meets Level 3 of IEC 1000-4-2, without additional ESD-protection components.

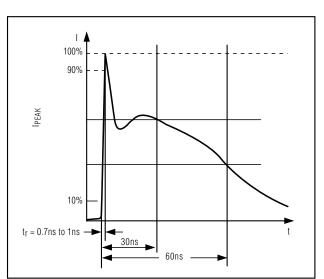

The main difference between tests done using the Human Body Model and IEC 1000-4-2 is higher peak current in IEC 1000-4-2. Because series resistance is lower in the IEC 1000-4-2 ESD test model (Figure 4a), the ESD-withstand voltage measured to this standard is generally lower than that measured using the Human Body Model. Figure 4b shows the current waveform for the ±8kV IEC 1000-4-2 Level 4 ESD Contact Discharge test. The Air-Gap test involves approaching the device with a charger probe. The Contact Discharge method connects the probe to the device before the probe is energized.

### **Machine Model**

The Machine Model for ESD testing uses a 200pF storage capacitor and zero-discharge resistance. It mimics the stress caused by handling during manufacturing and assembly. All pins (not just the RS-485 inputs) require this protection during manufacturing. Therefore, the Machine Model is less relevant to the I/O ports than are the Human Body Model and IEC 1000-4-2.

### **True Fail-Safe**

The MAX3280E/MAX3281E/MAX3283E/MAX3284E guarantee a logic-high receiver output when the receiver inputs are shorted or open, or when they are connected to a terminated transmission line with all drivers disabled. This guaranteed logic high is achieved by setting the receiver threshold between -50mV and -200mV. If the differential receiver input voltage (A-B) is greater than or equal to -50mV, RO is logic high. If (A-B) is less than or equal to -200mV, RO is logic low.

In the case of a terminated bus with all transmitters disabled, the receiver's differential input voltage is pulled to ground by the termination. This results in a logic high with a 50mV minimum noise margin. Unlike previous fail-safe devices, the -50mV to -200mV threshold comples with the  $\pm$ 200mV EIA/TIA-485 standard.

### Receiver Enable (MAX3281E and MAX3283E only)

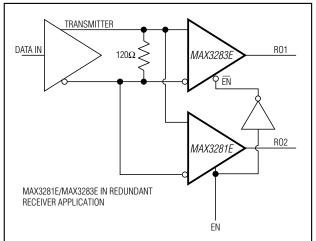

The MAX3281E and MAX3283E feature a receiver output enable (EN, MAX3281E or EN, MAX3283E) input that controls the receiver. The MAX3281E receiver enable (EN) pin is active high, meaning the receiver outputs are active when EN is high. The MAX3283E receiver enable (EN) pin is active low. Receiver outputs are high impedance when the MAX3281E's EN pin is low and when the MAX3283E's EN pin is high.

# Table 1. MAX3281E/MAX3283E EnableTable

| PART     | ENABLE = HIGH | ENABLE = LOW |

|----------|---------------|--------------|

| MAX3281E | Active        | High Z       |

| MAX3283E | High Z        | Active       |

### Low-Voltage Logic Levels (MAX3284E only)

An increasing number of applications now operate at low-voltage logic levels. To enable compatibility with these low-voltage logic level applications, such as digital FPGAs, the MAX3284E V<sub>L</sub> pin is a user-defined supply voltage that designates the voltage threshold for a logic high.

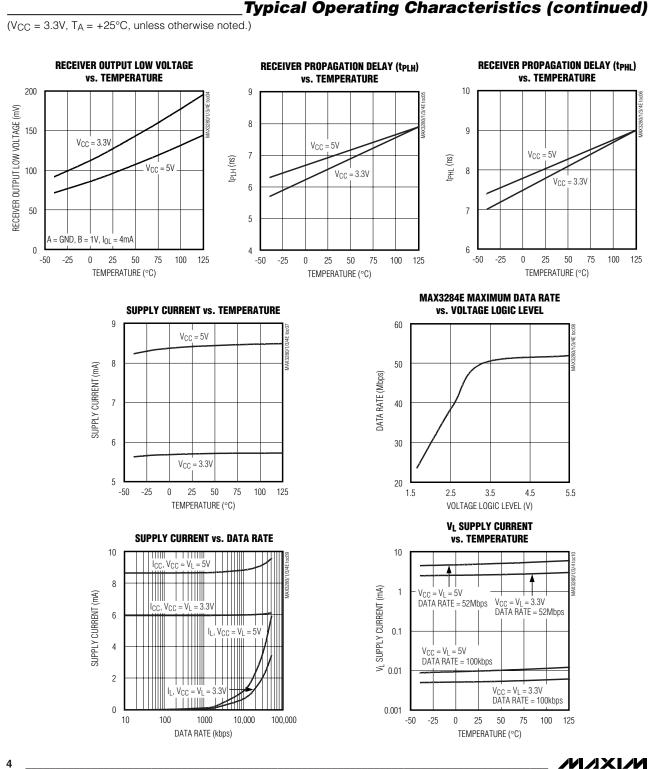

At lower V<sub>L</sub> voltages, the data rate will also be lower. A logic-high level of 1.65V will receive data at 20Mbps. Table 2 gives data rates at various voltages at V<sub>L</sub>.

### Table 2. MAX3284E Data Rate Table

| V <sub>CC</sub> = 3V TO 5.5V |                   |  |  |  |

|------------------------------|-------------------|--|--|--|

| VL                           | MAXIMUM DATA RATE |  |  |  |

| 1.65V                        | 20Mbps            |  |  |  |

| 2.2V                         | 33Mbps            |  |  |  |

| ≥3.3V                        | 52Mbps            |  |  |  |

### **Applications Information**

### **Propagation Delay Matching**

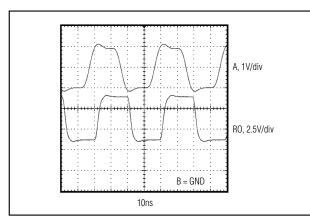

The MAX3280E/MAX3281E/MAX3283E/MAX3284E (V<sub>CC</sub> = V<sub>L</sub>) exhibit propagation delays that are closely matched from one device to another, even between devices from different production lots. This feature allows multiple data lines to receive data and clock signals with minimal skew with respect to each other. Figure 5 shows the typical propagation delays. Small receiver skew times, the difference between the low-to-high and high-to-low propagation delay, help maintain a symmetrical ratio (50% duty cycle). The receiver skew time I tPLH - tPHL I is under 2ns for either a 3.3V supply or a 5V supply.

### **Multidrop Clock Distribution**

Low package-to-package skew (8ns max) makes the MAX3280E/MAX3281E/MAX3283E/MAX3284E ( $V_{CC} = V_L$ ) ideal for multidrop clock distribution. When distributing a clock signal to multiple circuits over long transmission lines, receivers in separate locations, and possibly at two different temperatures, would ideally

provide the same clock to their respective circuits. Thus, minimal package-to-package skew is critical. The skew must be kept well below the period of the clock signal to ensure that all of the circuits on the network are synchronized.

### **128 Receivers on the Bus**

The standard RS-485 input impedance is  $12 k \Omega$  (one-unit load). The standard RS-485 transmitter can drive 32 unit loads. The MAX3280E/MAX3281E/MAX3283E/MAX3284E present a 1/4-unit-load input impedance

(48k $\Omega$ ), which allows up to 128 receivers on the bus. Any combination of these RS-485 receivers with a total of 32 unit loads can be connected to the same bus.

#### **Thermal Protection**

The MAX3280E/MAX3281E/MAX3283E/MAX3284E feature thermal protection. Thermal protection sets the output stage in high-impedance mode when a short circuit occurs at the output, limiting both the power dissipation and temperature. The thermal temperature threshold is +165°C, with a hysteresis of 20°C.

### Test Circuits/Timing Diagrams

Figure 2. MAX3281E/MAX3283E Receiver Enable/Disable Timing

MAX3280E/MAX3281E/MAX3283E/MAX3284E

Figure 3a. Human Body ESD Test Model

Figure 4a. IEC 1000-4-2 ESD Test Model

Figure 5. Receiver Propagation Delay Driven by External RS-485 Device

### Test Circuits/Timing Diagrams (continued)

Figure 3b. Human Body Model Current Waveform

Figure 4b. IEC 1000-4-2 ESD Generator Current Waveform

### Typical Operating Circuit

## Chip Information

PROCESS: BICMOS

### Pin Configurations

### ///XI///

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_\_\_\_

© 2002 Maxim Integrated Products

electronic components

Printed USA

MAXIM is a registered trademark of Maxim Integrated Products.

11