## AN32051A

http://www.semicon.panasonic.co.jp/en/

## 7 x 7 Dots Matrix LED Driver LSI

### FEATURES

- 7 x 7 LED Matrix Driver

- (Total LED that can be driven = 49)

- Built-in memory (ROM, RAM)

- LDO : 2-ch

- SPI interface : 1-ch

- LED driver for RGB : 1-ch

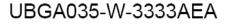

- 35 pin Wafer Level Chip Size Package (WLCSP)

#### DESCRIPTION

AN32051A is a 49 Dots Matrix LED Driver. It can drive up to 16 RGB LEDs.

#### **APPLICATIONS**

- Mobile Phone

- Smart Phone

- PCs

- Game Consoles

- Home Appliances etc.

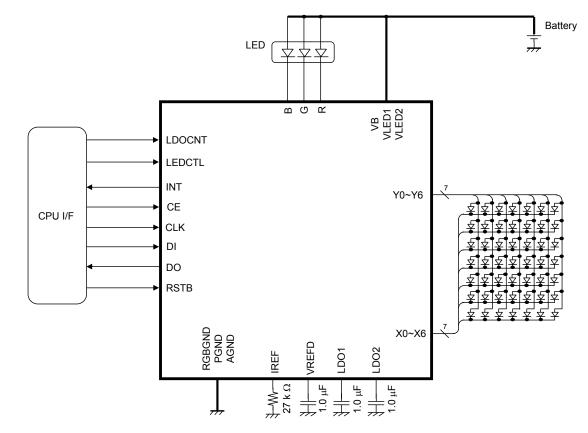

## TYPICAL APPLICATION

#### Note)

The application circuit is an example. The operation of the mass production set is not guaranteed. Sufficient evaluation and verification is required in the design of the mass production set. The Customer is fully responsible for the incorporation of the above illustrated application circuit in the design of the equipment.

## **CONTENTS**

| FEATURES                         | 1   |

|----------------------------------|-----|

| DESCRIPTION                      | 1   |

| APPLICATIONS                     | . 1 |

| TYPICAL APPLICATION              |     |

| CONTENTS                         | 2   |

| ABSOLUTE MAXIMUM RATINGS         |     |

| POWER DISSIPATION RATING         | . 3 |

| RECOMMENDED OPERATING CONDITIONS | 4   |

| ELECTRICAL CHARACTERISTICS       |     |

| PIN CONFIGURATION                | 13  |

| PIN FUNCTIONS                    |     |

| FUNCTIONAL BLOCK DIAGRAM         | 15  |

| OPERATION                        |     |

| PACKAGE INFORMATION              |     |

| IMPORTANT NOTICE                 | 63  |

### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                      | Symbol                                                                               | Rating        | Unit | Note |

|--------------------------------|--------------------------------------------------------------------------------------|---------------|------|------|

| Supply voltage                 | VB <sub>MAX</sub>                                                                    | 6.0           | V    | *1   |

| Supply voltage                 | VLED <sub>MAX</sub>                                                                  | 6.5           | V    | *1   |

| Operating ambience temperature | T <sub>opr</sub>                                                                     | – 30 to + 85  | °C   | *2   |

| Operating junction temperature | Тj                                                                                   | – 30 to + 125 | °C   | *2   |

| Storage temperature            | T <sub>stg</sub>                                                                     | – 55 to + 125 | °C   | *2   |

| Input Voltage Range            | LEDCTL, RSTB, CE,<br>CLK, DI                                                         | – 0.3 to 3.4  | V    | _    |

|                                | LDOCNT                                                                               | – 0.3 to 6.0  | V    | _    |

|                                | INT, DO                                                                              | – 0.3 to 3.4  | V    | —    |

| Output Voltage Range           | R, G, B,<br>LDO1, LDO2,<br>X0, X1, X2, X3, X4, X5, X6,<br>Y0, Y1, Y2, Y3, Y4, Y5, Y6 | – 0.3 to 6.5  | v    | _    |

| ESD                            | НВМ                                                                                  | 2.0           | kV   |      |

Note) This product may sustain permanent damage if subjected to conditions higher than the above stated absolute maximum rating. This rating is the maximum rating and device operating at this range is not guaranteeable as it is higher than our stated recommended operating range.

When subjected under the absolute maximum rating for a long time, the reliability of the product may be affected. \*1:  $VB_{MAX} = VB$ ,  $VLED_{MAX} = VLED$ .

The values under the condition not exceeding the above absolute maximum ratings and the power dissipation.

\*2: Except for the power dissipation, operating ambient temperature, and storage temperature, all ratings are for  $T_a = 25^{\circ}C$ .

### **POWER DISSIPATION RATING**

| PACKAGE                                      | $\theta_{JA}$ | P <sub>D</sub> (Ta=25 °C) | Р <sub>D</sub> (Та=85 °С) |

|----------------------------------------------|---------------|---------------------------|---------------------------|

| 35 pin Wafer Level Chip Size Package (WLCSP) | 141.5 °C /W   | 0.706 W                   | 0.304 W                   |

Note) For the actual usage, please refer to the P<sub>D</sub>-Ta characteristics diagram in the package specification, follow the power supply voltage, load and ambient temperature conditions to ensure that there is enough margin and the thermal design does not exceed the allowable value.

#### CAUTION

Although this IC has built-in ESD protection circuit, it may still sustain permanent damage if not handled properly. Therefore, proper ESD precautions are recommended to avoid electrostatic damage to the MOS gates.

## **RECOMMENDED OPERATING CONDITIONS**

| Parameter            | Symbol                                                                               | Min.  | Тур. | Max.       | Unit | Note |

|----------------------|--------------------------------------------------------------------------------------|-------|------|------------|------|------|

|                      | VB                                                                                   | 3.1   | 3.7  | 4.6        | V    | *1   |

| Supply voltage range | VLED                                                                                 | 3.1   | 5.0  | 5.6        | V    | *1   |

| Input Voltage Range  | LEDCTL, RSTB, CE,<br>CLK, DI                                                         | - 0.3 | —    | 3.0        | V    |      |

|                      | LDOCNT                                                                               | - 0.3 | —    | VB + 0.3   | V    | *2   |

|                      | INT, DO                                                                              | - 0.3 | —    | 3.0        | V    |      |

| Output Voltage Range | R, G, B,<br>LDO1, LDO2,<br>X0, X1, X2, X3, X4, X5, X6,<br>Y0, Y1, Y2, Y3, Y4, Y5, Y6 | - 0.3 | _    | VLED + 0.3 | V    | *2   |

Note) \*1: The values under the condition not exceeding the above absolute maximum ratings and the power dissipation. Do not apply external currents and voltages to any pin not specifically mentioned. Voltage values, unless otherwise specified, are with respect to GND. GND is voltage for AGND, RGBGND and PGND. VB is voltage for VB. VLED is voltage for VLED1 and VLED2.

\*2: ( VB + 0.3 ) V must not exceed 6 V. ( VLED + 0.3 ) V must not exceed 6.5 V.

## **ELECTRICAL CHARACTERISTICS**

VB = 3.6 V, VLED1 = VLED2 = 4.9 V

Note) T<sub>a</sub> = 25 °C  $\pm$  2 °C unless otherwise specified.

|    | Devementer                       | Symbol | Condition                                                                                                           |      | Limits |      | Unit | Note |

|----|----------------------------------|--------|---------------------------------------------------------------------------------------------------------------------|------|--------|------|------|------|

|    | Parameter                        | Symbol | Condition                                                                                                           | Min  | Тур    | Max  | Unit | Note |

| Cu | rrent consumption                |        |                                                                                                                     |      |        |      |      |      |

|    | Current consumption (1)          | ICC1   | At OFF mode<br>LDOCNT = Low                                                                                         | _    | 0      | 1    | μA   | _    |

|    | Current consumption (2)          | ICC2   | At Standby mode<br>LDOCNT = Low<br>LDO2 is active.                                                                  |      | 8      | 12   | μA   |      |

|    | Current consumption (3)          | ICC3   | LDOCNT = High<br>LDO1 and LDO2 are active.                                                                          |      | 18     | 24   | μA   |      |

| Re | ference voltage                  |        |                                                                                                                     |      |        |      |      |      |

|    | Output voltage                   | VREF   | I <sub>VREF</sub> = 0 μA                                                                                            | 1.22 | 1.25   | 1.28 | V    | _    |

| Re | ference current                  |        |                                                                                                                     |      |        |      |      |      |

|    | Output voltage                   | VIREF  | I <sub>IREF</sub> = 0 μA                                                                                            | 0.44 | 0.54   | 0.64 | V    | _    |

| Vo | Itage regulator (LDO1)           |        | ·                                                                                                                   |      |        |      |      |      |

|    | Output voltage                   | VL1    | I <sub>LDO1</sub> = – 30 mA                                                                                         | 1.79 | 1.85   | 1.91 | V    | _    |

|    | Short circuit protection current | IPT1   | LDOCNT = High<br>REG18 = High<br>V <sub>LDO1</sub> = 0 V, IPT1 = I <sub>LDO1</sub>                                  | 50   | 100    | 200  | mA   |      |

|    | Ripple rejection (1)             | PSL11  | VB = $3.6 V + 0.2 V[p-p]$<br>f = 1 kHz<br>I <sub>LDO1</sub> = $-15 mA$<br>PSL11 = 20log (acV <sub>LDO1</sub> / 0.2) | _    | - 45   | - 40 | dB   |      |

|    | Ripple rejection (2)             | PSL12  | VB = 3.6 V + 0.2 V[p-p]<br>f = 10 kHz<br>I <sub>LDO1</sub> = - 15 mA<br>PSL12 = 20log (acV <sub>LDO1</sub> / 0.2)   |      | - 35   | - 25 | dB   |      |

## ELECTRICAL CHARACTERISTICS (continued)

VB = 3.6 V, VLED1 = VLED2 = 4.9 V

Note)  $T_a = 25 \ ^\circ C \pm 2 \ ^\circ C$  unless otherwise specified.

|    | Parameter                        |        | Condition                                                                                                                        |      | Limits |      | Unit | Note |

|----|----------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------|------|--------|------|------|------|

|    | Parameter                        | Symbol | Condition                                                                                                                        | Min  | Тур    | Max  | Unit | Note |

| Vo | Itage regulator (LDO2)           |        |                                                                                                                                  |      |        |      |      |      |

|    | Output voltage                   | VL2    | I <sub>LDO2</sub> = – 30 mA                                                                                                      | 2.76 | 2.85   | 2.94 | V    | _    |

|    | Short circuit protection current | IPT2   | LDOCNT = High<br>$V_{LDO2} = 0V$<br>IPT2 = I <sub>LDO2</sub>                                                                     | 50   | 100    | 300  | mA   | _    |

|    | Ripple rejection (1)             | PSL21  | VB = $3.6 V + 0.2 V[p-p]$<br>f = 1 kHz<br>I <sub>LDO2</sub> = $-15 mA$<br>PSL21 = 20log (acV <sub>LDO2</sub> / 0.2)              | _    | - 40   | - 30 | dB   | _    |

|    | Ripple rejection (2)             | PSL22  | VB = $3.6 V + 0.2 V[p-p]$<br>f = $10 \text{ kHz}$<br>I <sub>LDO2</sub> = $-15 \text{ mA}$<br>PSL22 = $20\log (acV_{LDO2} / 0.2)$ | _    | - 25   | - 15 | dB   | _    |

| Os | cillator                         |        |                                                                                                                                  |      |        |      |      |      |

|    | Oscillation frequency            | FDC    | _                                                                                                                                | 0.96 | 1.20   | 1.44 | MHz  | _    |

| sc | CAN Switch                       |        |                                                                                                                                  |      |        |      |      |      |

|    | Resistance at the Switch ON      | RSCAN  | I <sub>Y0, Y1, Y2, Y3, Y4, Y5, Y6</sub> = 5 mA<br>RSCAN<br>= V <sub>Y0, Y1, Y2, Y3, Y4, Y5, Y6</sub> / 5 mA                      |      | 2      | 4.8  | Ω    | _    |

## ELECTRICAL CHARACTERISTICS (continued)

VB = 3.6 V, VLED1 = VLED2 = 4.9 V

Note)  $~~T_a$  = 25  $^{\circ}C$   $\pm$  2  $^{\circ}C$  unless otherwise specified.

|    | Parameter                                    | Symbol      | Condition                                                                                                                 |        | Limits |        | Unit | Noto |

|----|----------------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|------|------|

|    | Farameter                                    | Symbol      | Condition                                                                                                                 | Min    | Тур    | Max    | Unit | Note |

| Cu | rrent generator (For $7 \times 7$ dots       | s matrix Ll | ED)                                                                                                                       |        |        |        |      |      |

|    | Output current (1)                           | IMX1        | At 1mA setup<br>$V_{X0, X1, X2, X3, X4, X5, X6} = 1 V$<br>IMX1 = I <sub>X0, X1, X2, X3, X4, X5, X6</sub>                  | 0.952  | 1.035  | 1.118  | mA   | *1   |

|    | Output current (2)                           | IMX2        | At 2 mA setup<br>V <sub>x0, x1, x2, x3, x4, x5, x6</sub> = 1 V<br>IMX2 = I <sub>x0, x1, x2, x3, x4, x5, x6</sub>          | 1.923  | 2.090  | 2.258  | mA   | *1   |

|    | Output current (3)                           | IMX4        | At 4 mA setup<br>$V_{x0, x1, x2, x3, x4, x5, x6} = 1 V$<br>IMX4 = $I_{x0, x1, x2, x3, x4, x5, x6}$                        | 3.843  | 4.177  | 4.512  | mA   | *1   |

|    | Output current (4)                           | IMX8        | At 8 mA setup<br>V <sub>x0, x1, x2, x3, x4, x5, x6</sub> = 1 V<br>IMX8 = I <sub>x0, x1, x2, x3, x4, x5, x6</sub>          | 7.692  | 8.361  | 9.030  | mA   | *1   |

|    | Output current (5)                           | IMX15       | At 15 mA setup<br>$V_{x0, x1, x2, x3, x4, x5, x6} = 1 V$<br>IMX15 = I <sub>x0, x1, x2, x3, x4, x5, x6</sub>               | 14.399 | 15.651 | 16.903 | mA   | *1   |

|    | Leakage Current<br>when matrix LED turns off | IMXOFF      | Current OFF setup<br>V <sub>x0, x1, x2, x3, x4, x5, x6</sub> = 4.75 V<br>IMXOFF = I <sub>x0, x1, x2, x3, x4, x5, x6</sub> |        | _      | 1      | μΑ   | _    |

|    | The error between channels                   | IMXCH       | The average value of all channels, and the current error of each channel                                                  | - 5    |        | 5      | %    | _    |

\*1 : Values when recommended parts (ERJ2RHD273X) are used for IREF terminal. The other current settings are combination of above items.

## ELECTRICAL CHARACTERISTICS (continued)

VB = 3.6 V, VLED1 = VLED2 = 4.9 V

Note)  $T_a = 25 \ ^\circ C \pm 2 \ ^\circ C$  unless otherwise specified.

|                                        | Parameter                            | Symbol  | Condition                                                                      |       | Limits |       | Unit | Note |  |  |

|----------------------------------------|--------------------------------------|---------|--------------------------------------------------------------------------------|-------|--------|-------|------|------|--|--|

|                                        | Farameter                            | Symbol  | Condition                                                                      | Min   | Тур    | Max   | Unit | Note |  |  |

| Current generator (For RGB color unit) |                                      |         |                                                                                |       |        |       |      |      |  |  |

|                                        | Output current (1)                   | IRGB1   | At 1mA setup<br>V <sub>R, G, B</sub> = 1 V                                     | 0.949 | 1.031  | 1.114 | mA   | *1   |  |  |

|                                        | Output current (2)                   | IRGB2   | At 2 mA setup<br>V <sub>R, G, B</sub> = 1 V                                    | 1.901 | 2.066  | 2.231 | mA   | *1   |  |  |

|                                        | Output current (3)                   | IRGB4   | At 4 mA setup<br>V <sub>R, G, B</sub> = 1 V                                    | 3.781 | 4.110  | 4.438 | mA   | *1   |  |  |

|                                        | Output current (4)                   | IRGB8   | At 8 mA setup<br>V <sub>R, G, B</sub> = 1 V                                    | 7.554 | 8.210  | 8.867 | mA   | *1   |  |  |

|                                        | Leakage Current<br>when RGB turn off | IRGBOFF | Current OFF setup<br>$V_{R, G, B}$ = 4.75 V<br>IRGBOFF = I <sub>R, G, B</sub>  |       |        | 1     | μA   | _    |  |  |

|                                        | The error between channels           | IRGBCH  | The average value of all<br>channels, and the current<br>error of each channel | - 5   |        | 5     | %    | _    |  |  |

\*1 : Values when recommended parts (ERJ2RHD273X) are used for IREF terminal. The other current settings are combination of above items.

## ELECTRICAL CHARACTERISTICS (continued)

VB = 3.6 V, VLED1 = VLED2 = 4.9 V

Note) T<sub>a</sub> = 25 °C  $\pm$  2 °C unless otherwise specified.

|     | Parameter                             | Symbol | Condition                                                                                       |               | Limits |               | Unit | Note |

|-----|---------------------------------------|--------|-------------------------------------------------------------------------------------------------|---------------|--------|---------------|------|------|

|     | Farameter                             | Symbol | Condition                                                                                       | Min           | Тур    | Max           | Unit | Note |

| SP  | I I/F, LEDCTL, RSTB                   |        |                                                                                                 |               |        |               |      |      |

|     | Input voltage range of High-<br>level | VIH    | High-level recognition voltage                                                                  | 1.38          |        | LDO2<br>+ 0.3 | V    |      |

|     | Input voltage range of Low-<br>level  | VIL    | Low-level recognition voltage                                                                   | -0.3          | _      | 0.4           | V    |      |

|     | Input current of High-level           | ШΗ     | V <sub>LEDCTL, RSTB, CE, CLK, DI</sub> = 1.85 V<br>IIH = I <sub>LEDCTL, RSTB, CE, CLK, DI</sub> | _             | 0      | 1             | μA   |      |

|     | Input current of Low-level            | IIL    | $V_{\text{LEDCTL, RSTB, CSB, CLK, DI}} = 0 V$<br>IIL = I <sub>LEDCTL, RSTB, CE, CLK, DI</sub>   | _             | 0      | 1             | μA   |      |

| ΙΝ٦ | г                                     |        |                                                                                                 |               |        |               |      |      |

|     | Output voltage of High-level (1)      | VOH1   | I <sub>INT</sub> = – 2 mA<br>VDDSEL = LDO2                                                      | LDO2<br>× 0.8 |        |               | V    |      |

|     | Output voltage of Low-level (1)       | VOL1   | I <sub>INT</sub> = 2 mA<br>VDDSEL = LDO2<br>(I <sub>INT</sub> = 0.5 mA )                        | _             | _      | LDO2<br>× 0.2 | V    | _    |

|     | Output voltage of High-level (2)      | VOH2   | I <sub>INT</sub> = – 2 mA<br>VDDSEL = LDO1                                                      | LDO1<br>× 0.8 | _      | _             | V    | _    |

|     | Output voltage of Low-level (2)       | VOL2   | I <sub>INT</sub> = 2 mA<br>VDDSEL = LDO1<br>(I <sub>INT</sub> = 0.5 mA )                        | _             |        | LDO1<br>× 0.3 | V    | _    |

## ELECTRICAL CHARACTERISTICS (continued)

VB = 3.6 V, VLED1 = VLED2 = 4.9 V

Note) T<sub>a</sub> = 25 °C  $\pm$  2 °C unless otherwise specified.

|    | Parameter                         | Symbol | Condition                                         |               | Limits |               | Unit | Note |

|----|-----------------------------------|--------|---------------------------------------------------|---------------|--------|---------------|------|------|

|    | Farameter                         |        |                                                   | Min           | Тур    | Max           | Unit | Note |

| LD | OCNT                              |        |                                                   |               |        |               |      |      |

|    | Input voltage range of High-level | VIH    | High-level recognition voltage                    | VB<br>× 0.7   | _      | VB<br>+ 0.3   | V    | _    |

|    | Input voltage range of Low-level  | VIL    | Low-level recognition voltage                     | - 0.3         |        | 0.4           | V    |      |

|    | Input current of High-level       | ШН     | $V_{LDOCNT} = 3.6 V$<br>IIH = I <sub>LDOCNT</sub> |               | 0      | 1             | μA   | _    |

|    | Input current of Low-level        | IIL    | $V_{LDOCNT} = 0 V$<br>IIL = I <sub>LDOCNT</sub>   | _             | 0      | 1             | μA   | _    |

| DO |                                   |        |                                                   |               |        |               |      |      |

|    | Output voltage of High-level      | VOH    | I <sub>DO</sub> = – 2 mA                          | LDO1<br>× 0.8 |        |               | V    |      |

|    | Output voltage of Low-level       | VOL    | I <sub>DO</sub> = 2 mA                            |               |        | LDO1<br>× 0.2 | V    |      |

## ELECTRICAL CHARACTERISTICS (continued)

VB = 3.6 V, VLED1 = VLED2 = 4.9 V

Note)  $T_a = 25 \circ C \pm 2 \circ C$  unless otherwise specified.

| Parameter                       | Symbol    | Condition                                                                                  |        | Limits |     | Unit | Note     |

|---------------------------------|-----------|--------------------------------------------------------------------------------------------|--------|--------|-----|------|----------|

| Parameter                       | Symbol    | Condition                                                                                  | Min    | Тур    | Max | Unit | Note     |

| Voltage regulator (LDO1) Output | capacitor | 1 $\mu$ F, Output capacitor's ESR less t                                                   | than 0 | .1 Ω   |     |      |          |

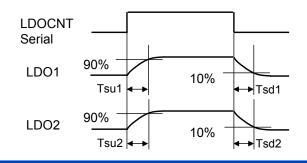

| Rise time                       | Tsu1      | Time until output voltage reaches to 0 V to 90%                                            | _      | 0.25   | _   | ms   | *2<br>*3 |

| Fall time                       | Tsd1      | Time until output voltage reaches to 10%                                                   | _      | 5      | _   | ms   | *2<br>*3 |

| Maximum load current            | IOMAX1    | _                                                                                          |        | 15     |     | mA   | *3       |

| Load transient response (1)     | Vtr11     | $I_{LDO1}$ = – 50 $\mu$ A $\rightarrow$ – 15 mA (1 $\mu$ s)                                |        | 70     | _   | mV   | *3       |

| Load transient response (2)     | Vtr12     | $I_{LDO1}$ = – 15 mA $\rightarrow$ – 50 $\mu$ A (1 $\mu$ s)                                |        | 70     |     | mV   | *3       |

| Voltage regulator (LDO2) Output | capacitor | 1 μF, Output capacitor's ESR less t                                                        | than 0 | .1 Ω   |     |      |          |

| Rise time                       | Tsu2      | Time until output voltage reaches to 0 V to 90%                                            |        | 0.25   |     | ms   | *2<br>*3 |

| Fall time                       | Tsd2      | Time until output voltage reaches to 10%                                                   | _      | 5      | _   | ms   | *2<br>*3 |

| Maximum load current            | IOMAX2    | _                                                                                          | _      | 15     |     | mA   | *3       |

| Load transient response (1)     | Vtr21     | $I_{LDO2}$ = – 50 $\mu$ A $\rightarrow$ – 15 mA (1 $\mu$ s)                                |        | 70     |     | mV   | *3       |

| Load transient response (2)     | Vtr22     | $I_{LDO2}$ = – 15 mA $\rightarrow$ – 50 $\mu$ A (1 $\mu$ s)                                |        | 70     | _   | mV   | *3       |

| TSD (Thermal shutdown circuit)  |           |                                                                                            |        |        |     |      |          |

| Detection temperature           | Tdet      | Temperature which LDO1, LDO2,<br>Constant current circuit, Matrix SW<br>and RGB turns off. | _      | 160    | _   | °C   | *3<br>*4 |

| Return temperature              | Tsd11     | Returning temperature                                                                      | _      | 110    | _   | °C   | *3<br>*5 |

\*2 : Rise time and Fall time are defined as below. Note)

Actual evaluation result of rise time : LDO1 : 290 to 400 µs, LDO2 : 220 to 310  $\mu\text{s}$ Actual evaluation result of fall time : LDO1: 6.2 to 8.5 ms, LDO2 : 5.8 to 7.9 ms

\*3 : Typical Design Value

\*4 : LDO1, LDO2, Constant current circuit, and Matrix SW and RGB are turned off when TSD is High.

When TSD is High, the register is set as 14hD1 = 1. However, data can be read only when the register is read immediately after INT occurs since internal regulator is turned off.

\*5 : Only LDO1 and LDO2 return after ON state of TSD. A logic part will be in Reset state.

## ELECTRICAL CHARACTERISTICS (continued)

VB = 3.6 V, VLED1 = VLED2 = 4.9 V

Note) T<sub>a</sub> = 25 °C  $\pm$  2 °C unless otherwise specified.

| Devenueder                        | Gumbal      | Condition               |          | Limits |     | 11   | Nata |

|-----------------------------------|-------------|-------------------------|----------|--------|-----|------|------|

| Parameter                         | Symbol      | Condition               | Min      | Тур    | Мах | Unit | Note |

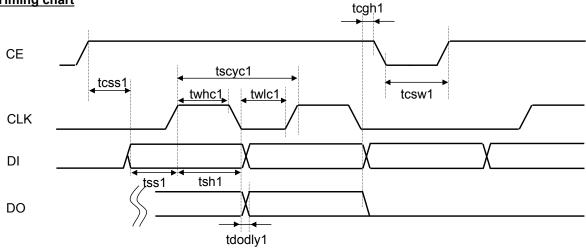

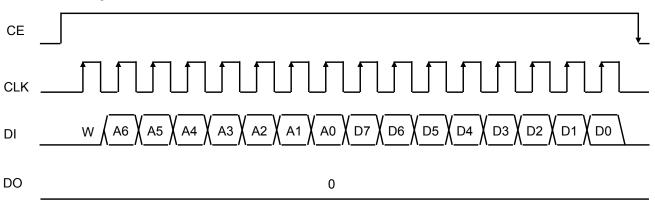

| Microcomputer interface character | stic (Vdd = | = 1.85 V ± 3 %) Write a | ccess Ti | ming   |     |      |      |

| CLK cycle time                    | tscyc1      | —                       | _        | 125    |     | ns   | *3   |

| CLK cycle time High period        | twhc1       | _                       | —        | 60     | _   | ns   | *3   |

| CLK cycle time Low period         | twlc1       |                         | _        | 60     |     | ns   | *3   |

| Serial-data setup time            | tss1        |                         | _        | 62     |     | ns   | *3   |

| Serial-data hold time             | tsh1        |                         | _        | 62     |     | ns   | *3   |

| Transceiver interval              | tcsw1       |                         | _        | 62     |     | ns   | *3   |

| Chip enable setup time            | tcss1       |                         | _        | 5      |     | ns   | *3   |

| Chip enable hold time             | tcgh1       |                         | _        | 5      |     | ns   | *3   |

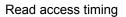

| Microcomputer interface character | stic (Vdd = | 1.85 V ± 3 %) Read ad   | ccess Ti | ming   |     |      |      |

| CLK cycle time                    | tscyc1      | _                       | _        | 125    | _   | ns   | *3   |

| CLK cycle time High period        | twhc1       |                         | _        | 60     |     | ns   | *3   |

| CLK cycle time Low period         | twlc1       |                         | _        | 60     |     | ns   | *3   |

| Serial-data setup time            | tss1        |                         | _        | 62     |     | ns   | *3   |

| Serial-data hold time             | tsh1        | _                       | _        | 62     | _   | ns   | *3   |

| Transceiver interval              | tcsw1       | _                       | _        | 62     |     | ns   | *3   |

| Chip enable setup time            | tcss1       |                         | _        | 5      |     | ns   | *3   |

| Chip enable hold time             | tcgh1       |                         |          | 5      |     | ns   | *3   |

| DC delay time                     | tdodly1     | Only read mode          |          | 25     |     | ns   | *3   |

Note) \*3 : Typical Design Value

#### Timing chart

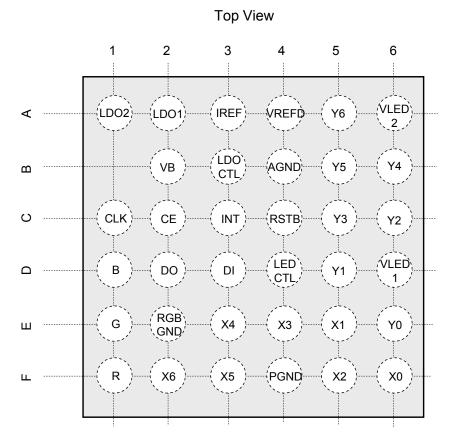

## **PIN CONFIGURATION**

### **PIN FUNCTIONS**

| Pin No. | Pin name | Туре         | Description                                         |

|---------|----------|--------------|-----------------------------------------------------|

| B2      | VB       | Power supply | Power supply for Bandgap circuit and LDO circuit    |

| A2      | LDO1     | Output       | LDO1(1.85 V)output pin                              |

| C4      | RSTB     | Input        | Reset input ( Active : High )                       |

| A3      | IREF     | Output       | Resistor connection pin for constant current setup  |

| B3      | LDOCNT   | Input        | ON/OFF control pin for LDO1 and LDO2                |

| A4      | VREFD    | Output       | Bandgap circuit output                              |

| B4      | AGND     | Ground       | GND for analog block                                |

| A5      | Y6       | Output       | Constant current circuit, output pin of PWM control |

|         | 10       | Output       | It connects with the G column of matrix LED.        |

| B5      | Y5       | Output       | Constant current circuit, output pin of PWM control |

|         | 10       | Output       | It connects with the F column of matrix LED.        |

| B6      | Y4       | Output       | Constant current circuit, output pin of PWM control |

| ВО      | 14       | Output       | It connects with the E column of matrix LED.        |

| C5      | Y3       | Quitout      | Constant current circuit, output pin of PWM control |

| 05      | 13       | Output       | It connects with the D column of matrix LED.        |

| C6      | Y2       | Output       | Constant current circuit, output pin of PWM control |

| 0       | 12       | Output       | It connects with the C column of matrix LED.        |

## **PIN FUNCTIONS (Continued)**

| Pin No.  | Pin name       | Туре         | Description                                                                                         |

|----------|----------------|--------------|-----------------------------------------------------------------------------------------------------|

| D6<br>A6 | VLED1<br>VLED2 | Power supply | Power supply connection pin for matrix LED                                                          |

| D5       | Y1             | Output       | Constant current circuit, output pin of PWM control<br>It connects with the B column of matrix LED. |

| E6       | Y0             | Output       | Constant current circuit, output pin of PWM control<br>It connects with the A column of matrix LED. |

| D4       | LEDCTL         | Input        | ON/OFF operation control of LED lighting (by serial address 0Ah)                                    |

| F6       | X0             | Output       | Constant current circuit, output pin of PWM control<br>It connects with the 1st row of matrix LED.  |

| E5       | X1             | Output       | Constant current circuit, output pin of PWM control<br>It connects with the 2nd row of matrix LED.  |

| F5       | X2             | Output       | Constant current circuit, output pin of PWM control<br>It connects with the 3rd row of matrix LED.  |

| E4       | Х3             | Output       | Constant current circuit, output pin of PWM control<br>It connects with the 4th row of matrix LED.  |

| F4       | PGND           | Ground       | GND for matrix LED                                                                                  |

| E3       | X4             | Output       | Constant current circuit, output pin of PWM control<br>It connects with the 5th row of matrix LED.  |

| F3       | X5             | Output       | Constant current circuit, output pin of PWM control<br>It connects with the 6th row of matrix LED.  |

| F2       | X6             | Output       | Constant current circuit, output pin of PWM control<br>It connects with the 7th row of matrix LED.  |

| F1       | R              | Output       | LED connection pin                                                                                  |

| E2       | RGBGND         | Ground       | GND for RGB pin                                                                                     |

| E1       | G              | Output       | LED connection pin                                                                                  |

| D1       | В              | Output       | LED connection pin                                                                                  |

| D2       | DO             | Output       | SPI interface data output                                                                           |

| D3       | DI             | Input        | SPI interface data input                                                                            |

| C1       | CLK            | Input        | SPI interface clock input                                                                           |

| C2       | CE             | Input        | SPI interface chip enable (Active : High )                                                          |

| C3       | INT            | Output       | Interrupt output                                                                                    |

| A1       | LDO2           | Output       | LDO2 ( 2.85 V ) output                                                                              |

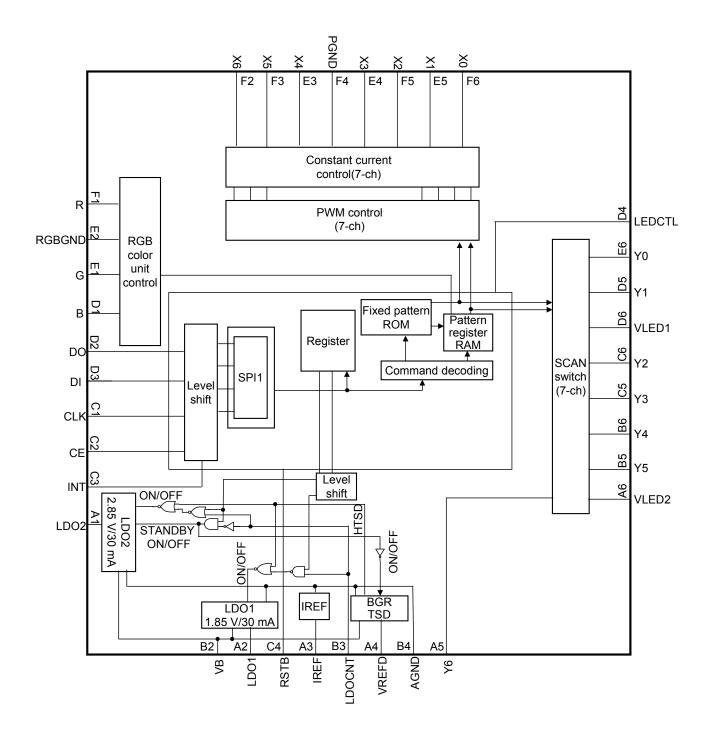

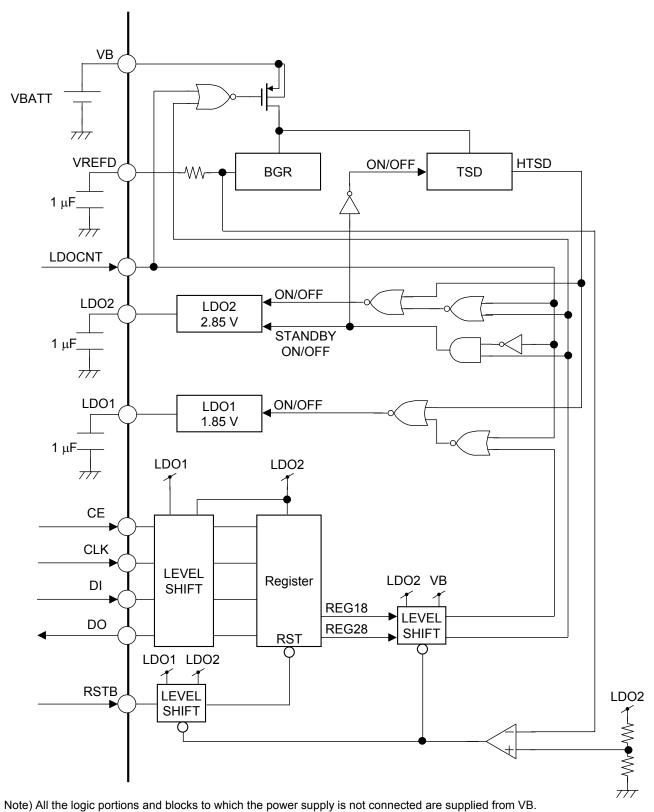

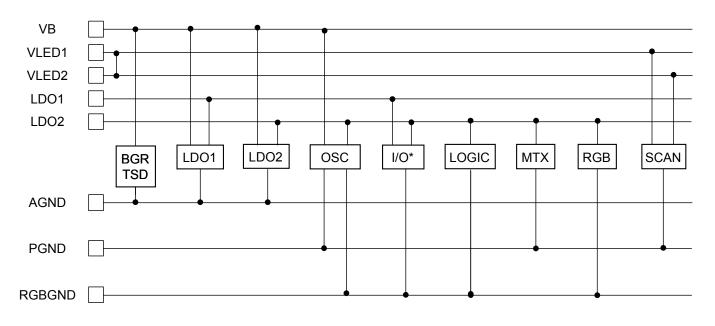

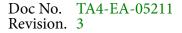

## FUNCTIONAL BLOCK DIAGRAM

Notes: This block diagram is for explaining functions. Part of the block diagram may be omitted, or it may be simplified.

## **OPERATION**

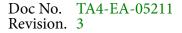

### 1. Explanation of each mode ( Power supply startup sequence )

| Mode                                | LDOCNT                 | REG18 | REG28 | Note                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------|------------------------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OFF mode                            | Low                    | 0     | 0     | - LDOCNT should be set to High in order to recover from OFF mode.                                                                                                                                                                                                                                                                                                                                                                        |

| OFF mode                            | Low $\rightarrow$ High | 0/1   | 0/1   | <ul> <li>Serial signal is not received at LDOCNT = Low and<br/>REG28 = [0] or REG18 = [0].</li> <li>This LSI shifts to Standby mode at LDOCNT = Low,<br/>REG28 = [1] and REG18 = [0].</li> <li>Serial signal is not received at Standby mode.</li> <li>(Downs supplies for logic are LDO1 and LDO2.)</li> </ul>                                                                                                                          |

| →<br>Normal mode                    | High                   | 0/1   | 0/1   | <ul> <li>(Power supplies for logic are LDO1 and LDO2.)<br/>Therefore, Standby mode cannot be released by serial signal.</li> <li>When LDOCNT is changed from Low to High, it is impossible to shift Standby mode to Normal mode.</li> <li>It is impossible to shift Standby mode to OFF mode.<br/>Once returning to Normal mode, shift to OFF mode.</li> </ul>                                                                           |

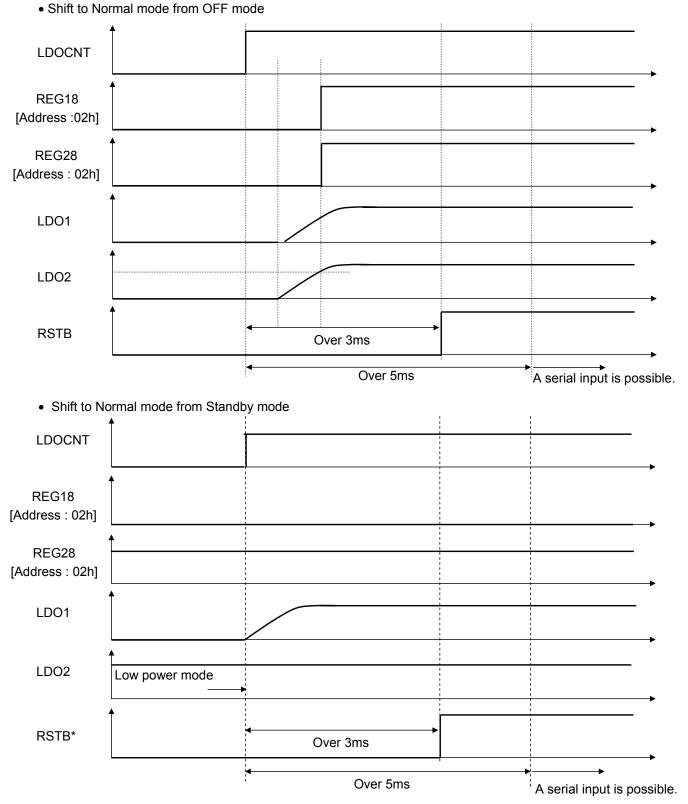

| Normal mode<br>→<br>OFF mode        | High                   | 0     | 0     | <ul> <li>At LDOCNT = High, LDO1 turns on regardless of REG18.</li> <li>At LDOCNT = High, LDO2 turns on regardless of REG28.</li> <li>At RSTB = Low, serial signal is not received.</li> <li>It is possible to receive the serial signal at 5 ms or more after LDOCNT is set to High.</li> <li>The Low interval of RSTB should be one internal clock or more.</li> <li>Don't input a signal except rectangle wave to RSTB pin.</li> </ul> |

| Normal mode<br>→<br>Standby<br>mode | High → Low             | 0     | 1     | <ul> <li>All register's settings become default values if RSTB is set to Low. (The default value of REG18 and REG28 bit is [1]. Note that LDO1 and LDO2 don't turn off when RSTB is set to Low before LDOCNT is set to Low.)</li> <li>All register's settings are reset when LDO2 turns off. (Register setting initialization)</li> <li>The setup step to OFF mode is as follows. REG18, 28 = [0] → LDOCNT = Low → RSTB = Low</li> </ul> |

#### 1. Explanation of each mode ( Power supply startup sequence ) (continued)

Note) The above waveform is under the condition that the register setup is reset in standby mode. Maintain the state of RSTB = High to hold the register setup.

#### 1. Explanation of each mode ( Power supply startup sequence ) (continued)

Shift to OFF mode from Normal mode

#### 1. Explanation of each mode ( Power supply startup sequence ) (continued)

Mode which is specified by VBAT / LDOCNT

| VBAT | LDOCNT | MODE        |

|------|--------|-------------|

| Low  | Low    | OFF         |

| Low  | High   | Prohibition |

| High | Low    | OFF         |

| High | High   | ON          |

Note) "Low" in column of VBAT and LDOCNT means 0 V.

"High" in column of VBAT and LDOCNT means 3.1 V to 4.6 V (operation supply voltage range).

Logic pin conditions

The following setting is common for OFF, Standby and Normal mode. The pin setting when RSTB = Low, under Normal mode is as follows.

| Pin name | Pin state | Logic state*               |

|----------|-----------|----------------------------|

| INT      | Output    | Low                        |

| CE       | Input     | Low                        |

| CLK      | Input     | Low                        |

| DI       | Input     | Low                        |

| DO       | Output    | Low                        |

| LEDCTL   | Input     | Low                        |

| LDOCNT   | Input     | Depends on each mode setup |

Note)\*: Logic state for pins indicated as "Output" under Pin state shows the output level.

Logic state for pins indicated as "Input" under Pin state shows the input level to be set to the pins.

#### 2. Explanation of operation

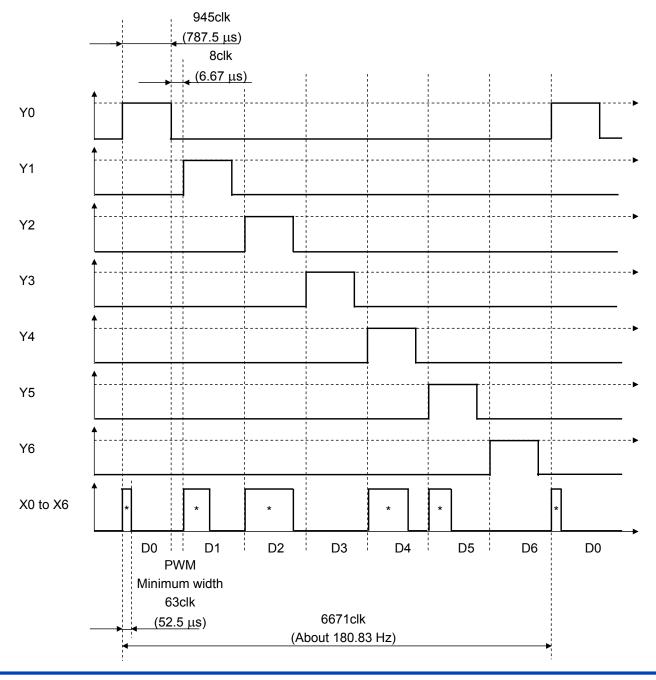

Matrix part operation waveform

The following waveform is a timing chart example at operation.

It is controlled by internal 1.2 MHz clock under the default condition.

Y side switches from Y0 to Y6 in that order. The ON period of each pin is constant 945clk (787.5  $\mu$ s). The ON period includes an 8clk(6.67  $\mu$ s) interval.

In the case of the following figure, "\*" mark shows ON period. Therefore, D3 and D4 are OFF period.

$7 \times 7$  matrix display is controlled by the lines of X1 to X6.

The following waveforms are internal signals. The actual waveform of Yx pin becomes Hi-Z at Yx = Xx = Low.

#### 3. Block configuration

RESET part block configuration

#### 3. Block configuration (continued)

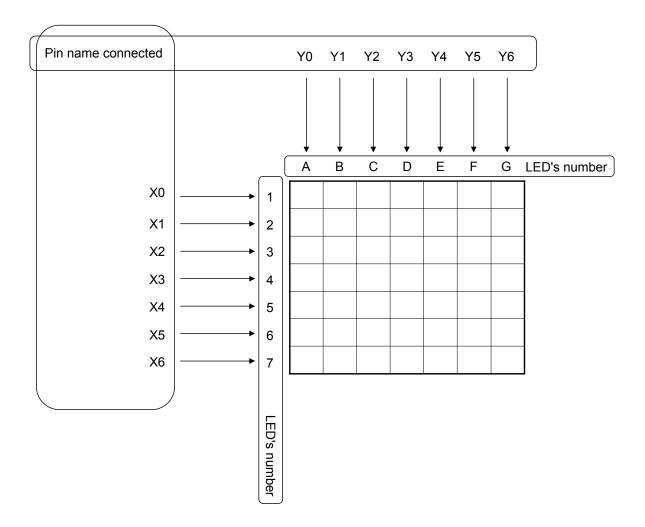

Explanation of matrix LED part, matrix LED's number

LED matrix driver can display characters and patterns by controlling 7  $\times$  7 matrix LED individually. In this product standards, LED's number controlled by each pin is as the following figure.

An internal logic circuit is controlled by internal clock.

In scroll mode, the display of character specified in the following arrangement is moved from right to left.

#### 3. Block configuration (continued)

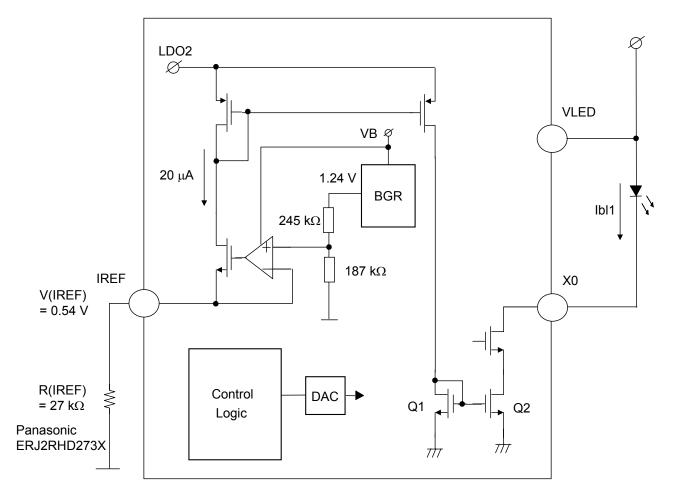

Equivalent circuit example of constant current driver

In case of X0 pin

The constant current equivalent circuit example (X0 pin) for LED driver is shown in the above figure. The reference current for constant current driver is calculated by the following formula.

$V(IREF) / R(IREF) = 0.54 V / 27 k\Omega = 20 \mu A$

The LED driver current can be set to the range of 0 mA to 30 mA by setting the mirror ratio between Q1 and Q2 by DAC via serial interface.

The constant current can be changed by the resistor connected to IREF pin, but the accuracy in case of this setting is not guaranteed.

It is recommended that ERJ2RHD273X is used as R(IREF) to keep the accuracy of constant current of LED driver.

#### 4. Register and Address

Register map

| Sub     |     | Dete nome |         |    |     |      | Data       |        |         |       |

|---------|-----|-----------|---------|----|-----|------|------------|--------|---------|-------|

| address | R/W | Data name | D7      | D6 | D5  | D4   | D3         | D2     | D1      | D0    |

| 01h     | W   | POWERCNT  | —       |    |     |      | _          | OSCEN  |         | —     |

| 02h     | W   | LDOCNT    | —       |    |     |      | _          | —      | REG18   | REG28 |

| 03h     |     |           |         |    | For | test |            |        |         |       |

| 04h     |     |           |         |    | For | test |            |        |         |       |

| 05h     |     |           |         |    | For | test |            |        |         |       |

| 06h     |     |           |         |    | For | test |            |        |         |       |

| 07h     |     |           |         |    | For | test |            |        |         |       |

| 08h     |     |           |         |    | For | test |            |        |         |       |

| 09h     |     |           |         |    | For | test |            |        |         |       |

| 0Ah     | W   | LEDCTL    | LEDACT  |    | _   | _    | _          | DISMTX | DISRGB  | —     |

| 1       |     |           |         |    |     |      |            |        |         |       |

| 10h     |     |           |         |    | For | test |            |        |         |       |

| 11h     |     |           |         |    | For | test |            |        |         |       |

| 12h     |     |           |         |    | For | test |            |        |         |       |

| 13h     |     |           |         |    | For | test |            |        |         |       |

| 14h     | R   | IOFACTOR  | FACGD1  | _  | _   | _    | RAM<br>ACT | FRMINT | CPUWRER | TSD   |

| 15h     |     |           |         |    | For | test | ·          | •      |         |       |

| 16h     |     |           |         |    | For | test |            |        |         |       |

| 17h     |     |           |         |    | For | test |            |        |         |       |

| 18h     |     |           |         |    | For | test |            |        |         |       |

| 19h     |     |           |         |    | For | test |            |        |         |       |

| 1Ah     | W/R | VDDSEL    | INTVSEL |    | _   | _    |            | _      |         |       |

#### 4. Register and Address (continued)

Register map (continued)

|             |     | Dete memor |    |    |     |      | Data     |        |        |               |

|-------------|-----|------------|----|----|-----|------|----------|--------|--------|---------------|

| Sub address | R/W | Data name  | D7 | D6 | D5  | D4   | D3       | D2     | D1     | D0            |

| 20h         | R/W | MTXON      | _  |    | _   | _    |          | _      | —      | MTXON         |

| 21h         | R/W | MTXDATA    |    |    |     | MTX  | (DATA[7  | : 0]   |        |               |

| 22h         | R/W | FFROM      |    |    |     |      |          | _      | ROM    | 77[1 : 0]     |

| 23h         | R/W | ROMSEL     |    |    |     | SEI  | _ROM[7   | : 0]   |        |               |

| 24h         | R/W | RAMCOPY    | _  |    | _   | _    |          | _      | SELRAM | COPY<br>START |

| 25h         | R/W | SETFROM    |    |    |     | SET  | FROM[7   | : 0]   | 11     |               |

| 26h         | R/W | SETTO      |    |    |     | SE   | ETTO[7 : | 0]     |        |               |

| 27h         | R/W | REPON      |    |    |     |      |          |        | _      | REPON         |

| 28h         | R/W | SETTIME    |    |    |     |      |          | _      | SETTI  | ME[1 : 0]     |

| 29h         | R/W | RAMRST     |    |    |     |      |          | _      | RAM1   | RAM2          |

| 2Ah         | R/W | SCROLL     | _  |    | _   | _    | _        | _      | _      | SCLON         |

| 2Bh         |     |            |    |    | For | test |          |        |        |               |

| 2Ch         | R/W | RGBON      |    |    |     |      |          | _      | —      | RGBON         |

| 2Dh         | R/W | RGBDATA    |    |    |     |      | RG       | BDATA[ | 5 : 0] |               |

| 2Eh         |     |            |    |    | For | test |          |        |        |               |

| 30h         | R/W | RAMNUM     |    |    |     |      |          | _      | _      | RAMNUM        |

|             |     |            |    |    |     |      |          |        |        |               |

| 6Bh         |     |            |    |    | For | test |          |        |        |               |

| 6Dh         |     |            |    |    | For | test |          |        |        |               |

| 6Fh         |     |            |    |    | For | test |          |        |        |               |

| 70h         |     |            |    |    | For | test |          |        |        |               |

| 71h         |     |            |    |    | For | test |          |        |        |               |

| 72h         |     |            |    |    | For | test |          |        |        |               |

| 73h         |     |            |    |    | For | test |          |        |        |               |

| 74h         |     |            |    |    | For | test |          |        |        |               |

| 75h         |     |            |    |    | For | test |          |        |        |               |

| 76h         |     |            |    |    | For | test |          |        |        |               |

| 77h         |     |            |    |    | For | test |          |        |        |               |

## AN32051A

## **OPERATION** (continued)

## 4. Register and Address (continued)

RAM address map

| Sub     | Data |    |      |                  | Da | ta                  |          |       |        |

|---------|------|----|------|------------------|----|---------------------|----------|-------|--------|

| address | name | D7 | D6   | D5               | D4 | D3                  | D2       | D1    | D0     |

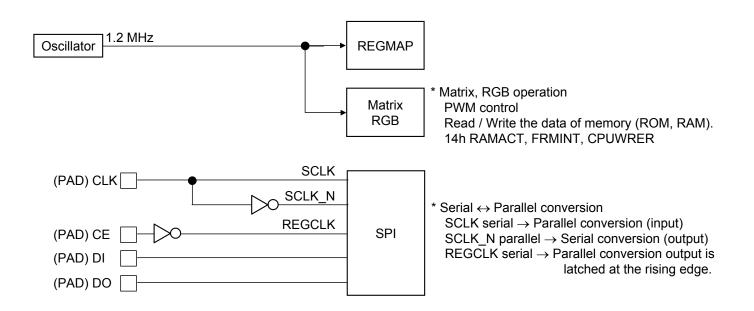

| 31h     | A1   |    | BLA1 | [3 : 0]          |    | FRA1[1:0] DLA1[1:0] |          |       | 1 : 0] |

| 32h     | A2   |    | BLA2 | 2[3 : 0]         |    | FRA2[1:0] DLA2[1:0  |          |       | 1 : 0] |

| 33h     | A3   |    | BLAS | 3[3 : 0]         |    | FRA                 | 3[1 : 0] | DLA3[ | 1:0]   |

| 34h     | A4   |    | BLA4 | <b>!</b> [3 : 0] |    | FRA                 | 4[1:0]   | DLA4[ | 1:0]   |

| 35h     | A5   |    | BLAS | 5[3 : 0]         |    | FRA                 | 5[1:0]   | DLA5[ | 1:0]   |

| 36h     | A6   |    | BLA  | 6[3:0]           |    | FRA                 | 6[1:0]   | DLA6[ | 1:0]   |

| 37h     | A7   |    | BLA7 | <b>'[</b> 3 : 0] |    | FRA                 | 7[1:0]   | DLA7[ | 1:0]   |

| 38h     | B1   |    | BLB1 | [3 : 0]          |    | FRB                 | 1[1 : 0] | DLB1[ | 1:0]   |

| 39h     | B2   |    | BLB2 | 2[3 : 0]         |    | FRB                 | 2[1:0]   | DLB2[ | 1:0]   |

| 3Ah     | B3   |    | BLB3 | 8[3 : 0]         |    | FRB                 | 3[1:0]   | DLB3[ | 1:0]   |

| 3Bh     | B4   |    | BLB4 | <b>I[3</b> : 0]  |    | FRB                 | 4[1:0]   | DLB4[ | 1:0]   |

| 3Ch     | B5   |    | BLB  | 5[3 : 0]         |    | FRB5[1:0] DLB5[1:   |          |       | 1:0]   |

| 3Dh     | B6   |    | BLB6 | 6[3 : 0]         |    | FRB6[1:0] DLB6[1:0] |          |       | 1:0]   |

| 3Eh     | B7   |    | BLB7 | <b>'[3</b> : 0]  |    | FRB7[1:0] DLB7[1:0] |          |       | 1:0]   |

| 3Fh     | C1   |    | BLC  | [3 : 0]          |    | FRC1[1:0] DLC       |          |       | 1:0]   |

| 40h     | C2   |    | BLC2 | 2[3 : 0]         |    | FRC                 | 2[1:0]   | DLC2[ | 1:0]   |

| 41h     | C3   |    | BLC  | 3[3 : 0]         |    | FRC                 | 3[1:0]   | DLC3[ | 1:0]   |

| 42h     | C4   |    | BLC4 | <b>I[3</b> : 0]  |    | FRC                 | 4[1:0]   | DLC4[ | 1:0]   |

| 43h     | C5   |    | BLC  | 5[3 : 0]         |    | FRC                 | 5[1:0]   | DLC5[ | 1:0]   |

| 44h     | C6   |    | BLC  | 6[3 : 0]         |    | FRC                 | 6[1:0]   | DLC6[ | 1:0]   |

| 45h     | C7   |    | BLC7 | 7[3:0]           |    | FRC                 | 7[1:0]   | DLC7[ | 1:0]   |

| 46h     | D1   |    | BLD  | [3 : 0]          |    | FRD                 | 1[1 : 0] | DLD1[ | 1:0]   |

| 47h     | D2   |    | BLD2 | 2[3 : 0]         |    | FRD                 | 2[1 : 0] | DLD2[ | 1:0]   |

| 48h     | D3   |    | BLD  | 3[3 : 0]         |    | FRD                 | 3[1 : 0] | DLD3[ | 1 : 0] |

| 49h     | D4   |    | BLD4 | <b>I</b> [3 : 0] |    | FRD                 | DLD4[    | 1:0]  |        |

| 4Ah     | D5   |    | BLD  | 5[3 : 0]         |    | FRD                 | 5[1 : 0] | DLD5[ | 1:0]   |

| 4Bh     | D6   |    | BLD6 | 6[3 : 0]         |    | FRD6[1:0] DLD6[1:0] |          |       | 1:0]   |

| 4Ch     | D7   |    | BLD7 | 7[3:0]           |    | FRD                 | 7[1 : 0] | DLD7[ | 1:0]   |

#### 4. Register and Address (continued)

RAM address map (continued)

| Sub     | Data |    |       |                  | Da | ta                 |                  |             |          |

|---------|------|----|-------|------------------|----|--------------------|------------------|-------------|----------|

| address | name | D7 | D6    | D5               | D4 | D3                 | D2               | D1          | D0       |

| 4Dh     | E1   |    | BLE1  | [3 : 0]          |    | FRE1[1:0] DLE1[1:0 |                  |             | [1:0]    |

| 4Eh     | E2   |    | BLE2  | 2[3 : 0]         |    | FRE2               | 2[1 : 0]         | DLE2[       | 1:0]     |

| 4Fh     | E3   |    | BLE3  | 8[3 : 0]         |    | FRE                | 3[1:0]           | DLE3[       | 1:0]     |

| 50h     | E4   |    | BLE4  | [3 : 0]          |    | FRE4               | <b>I</b> [1 : 0] | DLE4[       | [1:0]    |

| 51h     | E5   |    | BLE5  | i[3 : 0]         |    | FRE                | 5[1:0]           | DLE5[       | [1:0]    |

| 52h     | E6   |    | BLE6  | 6[3 : 0]         |    | FRE                | 6[1:0]           | DLE6[       | [1:0]    |

| 53h     | E7   |    | BLE7  | <b>'[</b> 3 : 0] |    | FRE7               | <b>'</b> [1:0]   | DLE7[       | [1:0]    |

| 54h     | F1   |    | BLF1  | [3 : 0]          |    | FRF1               | [1:0]            | DLF1[       | 1:0]     |

| 55h     | F2   |    | BLF2  | [3 : 0]          |    | FRF2               | 2[1:0]           | DLF2[1:0]   |          |

| 56h     | F3   |    | BLF3  | [3 : 0]          |    | FRF3[1:0]          |                  | DLF3[1:0]   |          |

| 57h     | F4   |    | BLF4  | [3 : 0]          |    | FRF4[1:0]          |                  | DLF4[1:0]   |          |

| 58h     | F5   |    | BLF5  | i[3 : 0]         |    | FRF5[1:0]          |                  | DLF5[1:0]   |          |

| 59h     | F6   |    | BLF6  | 6[3:0]           |    | FRF6[1:0]          |                  | DLF6[       | 1:0]     |

| 5Ah     | F7   |    | BLF7  | [3:0]            |    | FRF7               | '[1:0]           | DLF7[       | 1:0]     |

| 5Bh     | G1   |    | BLG1  | [3 : 0]          |    | FRG1[1 : 0]        |                  | DLG1        | [1 : 0]  |

| 5Ch     | G2   |    | BLG2  | 2[3 : 0]         |    | FRG2               | 2[1 : 0]         | DLG2        | [1 : 0]  |

| 5Dh     | G3   |    | BLG   | 8[3 : 0]         |    | FRG                | 3[1:0]           | DLG3        | [1 : 0]  |

| 5Eh     | G4   |    | BLG4  | <b>I</b> [3 : 0] |    | FRG4               | 4[1:0]           | DLG4        | [1 : 0]  |

| 5Fh     | G5   |    | BLG   | 5[3 : 0]         |    | FRG                | 5[1:0]           | DLG5        | [1 : 0]  |

| 60h     | G6   |    | BLG6  | 6[3 : 0]         |    | FRG                | 6[1:0]           | DLG6        | [1 : 0]  |

| 61h     | G7   |    | BLG7  | 7[3:0]           |    | FRG7[1:0]          |                  | DLG7        | [1 : 0]  |

| 62h     | LEDR |    | BLLED | PR[3 : 0]        |    | FRLEDR[1:0]        |                  | DLLED       | R[1:0]   |

| 63h     | LEDG |    | BLLED | G[3 : 0]         |    | FRLED              | )G[1 : 0]        | DLLEDG[1:0] |          |

| 64h     | LEDB |    | BLLED | )B[3 : 0]        |    | FRLED              | )B[1:0]          | DLLEDI      | B[1 : 0] |

#### 4. Register and Address (continued)

#### ROM address map

[00000000] – [10010101] : ROM (Luminance only) 7 × 7 pattern No.0 (default) to pattern No.149

| Pattern No. | Contents of pattern  | Display | Pattern No. | Contents of pattern  | Display |

|-------------|----------------------|---------|-------------|----------------------|---------|

| 0           | All lights out       | Nothing | 31          | Alphabetic character | U       |

| 1           | Number               | 0       | 32          | Alphabetic character | V       |

| 2           | Number               | 1       | 33          | Alphabetic character | W       |

| 3           | Number               | 2       | 34          | Alphabetic character | Х       |

| 4           | Number               | 3       | 35          | Alphabetic character | Y       |

| 5           | Number               | 4       | 36          | Alphabetic character | Z       |

| 6           | Number               | 5       | 37          | Alphabetic character | а       |

| 7           | Number               | 6       | 38          | Alphabetic character | b       |

| 8           | Number               | 7       | 39          | Alphabetic character | С       |

| 9           | Number               | 8       | 40          | Alphabetic character | d       |

| 10          | Number               | 9       | 41          | Alphabetic character | е       |

| 11          | Alphabetic character | А       | 42          | Alphabetic character | f       |

| 12          | Alphabetic character | В       | 43          | Alphabetic character | g       |

| 13          | Alphabetic character | С       | 44          | Alphabetic character | h       |

| 14          | Alphabetic character | D       | 45          | Alphabetic character | i       |

| 15          | Alphabetic character | E       | 46          | Alphabetic character | j       |

| 16          | Alphabetic character | F       | 47          | Alphabetic character | k       |

| 17          | Alphabetic character | G       | 48          | Alphabetic character | I       |

| 18          | Alphabetic character | Н       | 49          | Alphabetic character | m       |

| 19          | Alphabetic character | I       | 50          | Alphabetic character | n       |

| 20          | Alphabetic character | J       | 51          | Alphabetic character | 0       |

| 21          | Alphabetic character | К       | 52          | Alphabetic character | р       |

| 22          | Alphabetic character | L       | 53          | Alphabetic character | q       |

| 23          | Alphabetic character | М       | 54          | Alphabetic character | r       |

| 24          | Alphabetic character | N       | 55          | Alphabetic character | S       |

| 25          | Alphabetic character | 0       | 56          | Alphabetic character | t       |

| 26          | Alphabetic character | Р       | 57          | Alphabetic character | u       |

| 27          | Alphabetic character | Q       | 58          | Alphabetic character | v       |

| 28          | Alphabetic character | R       | 59          | Alphabetic character | w       |

| 29          | Alphabetic character | S       | 60          | Alphabetic character | х       |

| 30          | Alphabetic character | Т       | 61          | Alphabetic character | У       |

#### 4. Register and Address (continued)

ROM address map (continued)

[00000000] - [10010101] : ROM (Luminance only) 7 × 7 pattern No.0 (default) to pattern No.149

| Pattern No. | Contents of pattern  | Display | Pattern No. | Contents of pattern | Display |

|-------------|----------------------|---------|-------------|---------------------|---------|

| 62          | Alphabetic character | Z       | 93          | Number              | 30      |

| 63          | Number               | 00      | 94          | Number              | 31      |

| 64          | Number               | 01      | 95          | Number              | 32      |

| 65          | Number               | 02      | 96          | Number              | 33      |

| 66          | Number               | 03      | 97          | Number              | 34      |

| 67          | Number               | 04      | 98          | Number              | 35      |

| 68          | Number               | 05      | 99          | Number              | 36      |

| 69          | Number               | 06      | 100         | Number              | 37      |

| 70          | Number               | 07      | 101         | Number              | 38      |

| 71          | Number               | 08      | 102         | Number              | 39      |

| 72          | Number               | 09      | 103         | Number              | 40      |

| 73          | Number               | 10      | 104         | Number              | 41      |

| 74          | Number               | 11      | 105         | Number              | 42      |

| 75          | Number               | 12      | 106         | Number              | 43      |

| 76          | Number               | 13      | 107         | Number              | 44      |

| 77          | Number               | 14      | 108         | Number              | 45      |

| 78          | Number               | 15      | 109         | Number              | 46      |

| 79          | Number               | 16      | 110         | Number              | 47      |

| 80          | Number               | 17      | 111         | Number              | 48      |

| 81          | Number               | 18      | 112         | Number              | 49      |

| 82          | Number               | 19      | 113         | Number              | 50      |

| 83          | Number               | 20      | 114         | Number              | 51      |

| 84          | Number               | 21      | 115         | Number              | 52      |

| 85          | Number               | 22      | 116         | Number              | 53      |

| 86          | Number               | 23      | 117         | Number              | 54      |

| 87          | Number               | 24      | 118         | Number              | 55      |

| 88          | Number               | 25      | 119         | Number              | 56      |

| 89          | Number               | 26      | 120         | Number              | 57      |

| 90          | Number               | 27      | 121         | Number              | 58      |

| 91          | Number               | 28      | 122         | Number              | 59      |

| 92          | Number               | 29      | 123         | Number              | 60      |

#### 4. Register and Address (continued)

ROM address map (continued)

[00000000] - [10010101] : ROM (Luminance only) 7 × 7 pattern No.0 (default) to pattern No.149

| Pattern No. | Contents of pattern | Display       | Pattern No. | Contents of pattern | Display |

|-------------|---------------------|---------------|-------------|---------------------|---------|

| 124         | Symbol              | Zero antenna  |             |                     |         |

| 125         | Symbol              | One antenna   | 144         | Symbol              |         |

| 126         | Symbol              | Two antenna   |             |                     |         |

| 127         | Symbol              | Three antenna | 145         | Symbol              |         |

| 128         | Symbol              | ►             |             | Gymbol              |         |

| 129         | Symbol              |               |             |                     |         |

| 130         | Symbol              | II            | 146         | Symbol              |         |

| 131         | Symbol              | >>            |             |                     |         |

| 132         | Symbol              | <<            | 147         | Symbol              |         |

| 133         | Symbol              | :             |             |                     |         |

| 134         | Symbol              | !             |             |                     |         |

| 135         | Symbol              | ?             | 148         | Symbol              |         |

| 136         | Symbol              |               |             |                     |         |

| 137         | Symbol              | ▼             | 149         | Symbol              |         |

| 138         | Symbol              | ←             | 149         | Symbol              |         |

| 139         | Symbol              | $\rightarrow$ |             |                     |         |

| 140         | Symbol              | +             |             |                     |         |

| 141         | Symbol              | -             |             |                     |         |

| 142         | Symbol              | /             |             |                     |         |

| 143         | Symbol              |               |             |                     |         |

#### 4. Register and Address (continued)

ROM address map (continued)

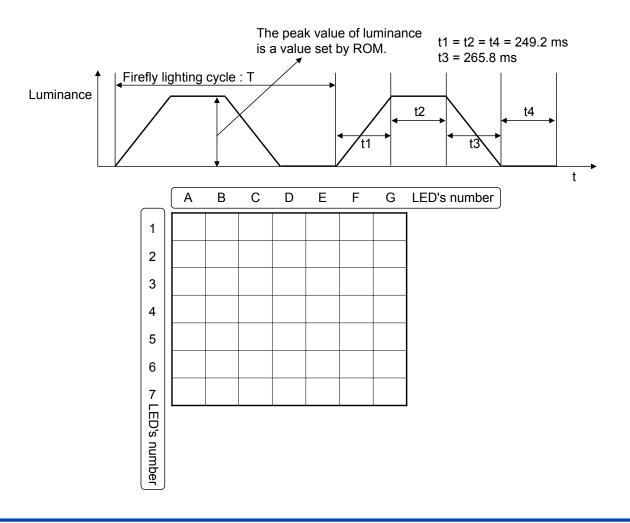

[10010110] - [11010000] : ROM (Luminance + Cycle + Delay) 7 × 7 pattern No.150 to pattern No.208

| Pattern No. | Contents of pattern | Display         | Pattern No. | Contents of pattern | Display         |

|-------------|---------------------|-----------------|-------------|---------------------|-----------------|

| 150         | Symbol              | Firefly display | 159         | Symbol              | Firefly display |

| 151         | Symbol              | Firefly display | 160         | Symbol              | Firefly display |

| 152         | Symbol              | Firefly display | 161         | Symbol              | Firefly display |

| 153         | Symbol              | Firefly display | 162         | Symbol              | Firefly display |

| 154         | Symbol              | Firefly display | 163         | Symbol              | Firefly display |

| 155         | Symbol              | Firefly display | 164         | Symbol              | Firefly display |

| 156         | Symbol              | Firefly display | 165         | Symbol              | Firefly display |

| 157         | Symbol              | Firefly display | 166         | Symbol              | Firefly display |

| 158         | Symbol              | Firefly display | 167         | Symbol              | Firefly display |

#### 4. Register and Address (continued)

ROM address map (continued)

[10010110] - [11010000] : ROM (Luminance + Cycle + Delay) 7 × 7 pattern No.150 to pattern No.208

| Pattern No. | Contents of pattern | Display         | Pattern No. | Contents of pattern | Display         |

|-------------|---------------------|-----------------|-------------|---------------------|-----------------|

| 168         | Symbol              | Firefly display | 177         | Symbol              | Firefly display |

| 169         | Symbol              | Firefly display | 178         | Symbol              | Firefly display |

| 170         | Symbol              | Firefly display | 179         | Symbol              | Firefly display |

| 171         | Symbol              | Firefly display | 180         | Symbol              | Firefly display |

| 172         | Symbol              | Firefly display | 181         | Symbol              | Firefly display |

| 173         | Symbol              | Firefly display | 182         | Symbol              | Firefly display |

| 174         | Symbol              | Firefly display | 183         | Symbol              | Firefly display |

| 175         | Symbol              | Firefly display | 184         | Symbol              | Firefly display |

| 176         | Symbol              | Firefly display | 185         | Symbol              | Firefly display |

#### 4. Register and Address (continued)

ROM address map (continued)

[10010110] - [11010000] : ROM (Luminance + Cycle + Delay) 7 × 7 pattern No.150 to pattern No.208

| Pattern No. | Contents of pattern | Display         | Pattern No. | Contents of pattern | Display         |

|-------------|---------------------|-----------------|-------------|---------------------|-----------------|

| 186         | Symbol              | Firefly display | 195         | Symbol              | Firefly display |

| 187         | Symbol              | Firefly display | 196         | Symbol              | Firefly display |

| 188         | Symbol              | Firefly display | 197         | Symbol              | Firefly display |

| 189         | Symbol              | Firefly display | 198         | Symbol              | Firefly display |

| 190         | Symbol              | Firefly display | 199         | Symbol              | Firefly display |

| 191         | Symbol              | Firefly display | 200         | Symbol              | Firefly display |

| 192         | Symbol              | Firefly display | 201         | Symbol              | Firefly display |

| 193         | Symbol              | Firefly display | 202         | Symbol              | Firefly display |

| 194         | Symbol              | Firefly display | 203         | Symbol              | Firefly display |

#### 4. Register and Address (continued)

ROM address map (continued)

[10010110] – [11010000] : ROM (Luminance + Cycle + Delay) 7 × 7 pattern No.150 to pattern No.208

| Pattern No. | Contents of pattern | Display         |

|-------------|---------------------|-----------------|

| 204         | Symbol              | Firefly display |

| 205         | Symbol              | Firefly display |

| 206         | Symbol              | Firefly display |

| 207         | Symbol              | Firefly display |

| 208         | Symbol              | Firefly display |

#### 4. Register and Address (continued)

Register list which needs a clock

The following addresses can be read / written even if there is not an internal clock or an external clock. However, it is impossible to achieve the operation finally needed.

| Sub<br>Address | R/W   | W Data Name | DATA             |    |    |    |            |         |              |               |

|----------------|-------|-------------|------------------|----|----|----|------------|---------|--------------|---------------|

|                | FK/VV |             | D7               | D6 | D5 | D4 | D3         | D2      | D1           | D0            |

| 01h            | W     | POWERCNT    | _                | _  |    | _  | _          | OSCEN   | _            | —             |

| 14h            | R     | IOFACTOR    | FACG<br>D1       | _  |    | _  | RAM<br>ACT | FRMINT  | CPU<br>WRER  | TSD           |

| 20h            | R/W   | MTXON       | —                | _  | _  | _  |            | _       | _            | MTXON         |

| 21h            | R/W   | MTXDATA     |                  |    |    |    | MTXDA      | TA[7:0] |              |               |

| 22h            | R/W   | FFROM       | _                | _  | _  | _  | —          | —       | ROM7         | 77[1:0]       |

| 23h            | R/W   | ROMSEL      | SELROM[7:0]      |    |    |    |            |         |              |               |

| 24h            | R/W   | RAMCOPY     | _                | _  | _  | _  | _          | _       | SELRAM       | COPY<br>START |

| 25h            | R/W   | SETFROM     | SETFROM[7:0]     |    |    |    |            |         |              |               |

| 26h            | R/W   | SETTO       |                  |    |    |    | SETT       | O[7:0]  |              |               |

| 27h            | R/W   | REPON       | _                | _  | _  | _  | _          | _       | _            | REPON         |

| 28h            | R/W   | SETTIME     | —                | _  | _  | _  | —          | —       | SETTIME[1:0] |               |

| 29h            | R/W   | RAMRST      | —                | _  | _  | _  | —          | —       | RAM1         | RAM2          |

| 2Ah            | R/W   | SCROLL      | —                | _  | _  | _  | _          | _       | _            | SCLON         |

| 2Bh            | R/W   | SCLTIME     | _                | _  | _  | _  | _          |         |              | VE[1:0]       |

| 2Ch            | R/W   | RGBON       | _                | _  | _  | _  | _          | _       | _            | RGBON         |

| 2Dh            | R/W   | RGBDATA     | — — RGBDATA[5:0] |    |    |    |            |         |              |               |

| 30h            | R/W   | RAMNUM      | —                | _  | _  | _  | _          | _       | _            | RAMNUM        |

#### 4. Register and Address (continued)

Register list which needs a clock (continued)

The following addresses can not be read / written if there is not an internal clock or an external clock.

| Sub     | Dete nome | Data        |      |                  |           |                 |           |             |             |  |

|---------|-----------|-------------|------|------------------|-----------|-----------------|-----------|-------------|-------------|--|

| address | Data name | D7 D6 D5 D4 |      | D3               | D2        | D1              | D0        |             |             |  |

| 31h     | A1        |             | FRA1 | [1:0]            | DLA1[1:0] |                 |           |             |             |  |

| 32h     | A2        |             | BLA2 | 2[3 : 0]         | FRA2      | 2[1:0]          | DLA2[1:0] |             |             |  |

| 33h     | A3        | BLA3[3 : 0] |      |                  |           |                 | 8[1:0]    | DLA3[1 : 0] |             |  |

| 34h     | A4        | BLA4[3 : 0] |      |                  |           |                 | [1:0]     | DLA4        | DLA4[1:0]   |  |

| 35h     | A5        |             | BLA5 | 5[3 : 0]         |           | FRA5            | 5[1:0]    | DLA         | DLA5[1:0]   |  |

| 36h     | A6        |             | BLA6 | 6[3:0]           |           | FRA6            | 5[1:0]    | DLA         | 8[1:0]      |  |

| 37h     | A7        |             | BLA7 | <b>'[</b> 3 : 0] |           | FRA7            | '[1 : 0]  | DLA         | 7[1:0]      |  |

| 38h     | B1        |             | BLB1 | [3 : 0]          |           | FRB1            | [1:0]     | DLB1        | [1:0]       |  |

| 39h     | B2        |             | BLB2 | 2[3 : 0]         |           | FRB2            | 2[1:0]    | DLB2        | 2[1:0]      |  |

| 3Ah     | B3        |             | BLB3 | 8[3 : 0]         |           | FRB3            | 8[1:0]    | DLB         | DLB3[1:0]   |  |

| 3Bh     | B4        |             | BLB4 | [3 : 0]          |           | FRB4            | [1:0]     | DLB4[1 : 0] |             |  |

| 3Ch     | B5        | BLB5[3 : 0] |      |                  |           | FRB5            | j[1 : 0]  | DLB5[1:0]   |             |  |

| 3Dh     | B6        | BLB6[3 : 0] |      |                  |           | FRB6            | 6[1:0]    | DLB6        | DLB6[1 : 0] |  |

| 3Eh     | B7        | BLB7[3 : 0] |      |                  |           | FRB7            | '[1 : 0]  | DLB7        | 7[1:0]      |  |

| 3Fh     | C1        |             | BLC1 | [3 : 0]          |           | FRC1            | [1:0]     | DLC         | I[1:0]      |  |

| 40h     | C2        |             | BLC2 | 2[3 : 0]         |           | FRC2            | 2[1:0]    | DLC2        | 2[1:0]      |  |

| 41h     | C3        |             | BLC3 | 8[3:0]           |           | FRC3            | 8[1:0]    | DLC         | 3[1:0]      |  |

| 42h     | C4        |             | BLC4 | <b>I</b> [3 : 0] |           | FRC4            | [1:0]     | DLC4        | 4[1:0]      |  |

| 43h     | C5        |             | BLC5 | 5[3 : 0]         |           | FRC5            | 5[1:0]    | DLC         | 5[1:0]      |  |

| 44h     | C6        |             | BLC6 | 6[3:0]           |           | FRC6            | 6[1:0]    | DLC6[1:0]   |             |  |

| 45h     | C7        | BLC7[3 : 0] |      |                  | FRC7      | <b>'[1</b> : 0] | DLC7[1:0] |             |             |  |

| 46h     | D1        | BLD1[3 : 0] |      |                  | FRD1      | [1:0]           | DLD       | I[1 : 0]    |             |  |

| 47h     | D2        | BLD2[3 : 0] |      |                  | FRD2      | 2[1:0]          | DLD2[1:0] |             |             |  |

| 48h     | D3        | BLD3[3 : 0] |      |                  | FRD3      | 8[1:0]          | DLD3[1:0] |             |             |  |

| 49h     | D4        | BLD4[3 : 0] |      |                  | FRD4      | [1:0]           | DLD4[1:0] |             |             |  |

| 4Ah     | D5        | BLD5[3 : 0] |      |                  | FRD5      | 5[1:0]          | DLD5[1:0] |             |             |  |

| 4Bh     | D6        |             | BLD6 | 6[3:0]           |           | FRD6[1:0] DLI   |           |             | 6[1:0]      |  |

| 4Ch     | D7        |             | FRD7 | FRD7[1:0] D      |           |                 |           |             |             |  |

#### 4. Register and Address (continued)

Register list which needs a clock (continued)