# **Excellent Integrated System Limited**

Stocking Distributor

Click to view price, real time Inventory, Delivery & Lifecycle Information:

Texas Instruments

PT4741A

For any questions, you can email us directly: <a href="mailto:sales@integrated-circuit.com">sales@integrated-circuit.com</a>

Datasheet of PT4741A - CONVERTER DC-DC 48VIN 70W HORZ

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

PT4741—48V

**◆EXCALIBUR**

70-W Quad-Output DC/DC Converter for DSL

SLTS167A - APRIL 2002 - REVISED NOVEMBER 2002

### **Features**

- Input Voltage: 36V to 75V

- Designed for AC6 ADSL Line-Interface Driver/Receivers

- Powers up to 64 Channels

- Quad Outputs (±8V, ±3.75V)

- Dual Logic On/Off Control

- Output Current Limit

- Unbalanced Load Protection

- Fixed Frequency Operation

- Over-Temperature Shutdown

- Under-Voltage Lockout

- 1500VDC Isolation

- Solderable Copper Case

- Space-Saving Package1.9 sq. in. PCB Area (suffix N)

- Safety Approvals:

UĹ60950

CSA 22.2 950

VDE EN60950 (Pending)

### **Description**

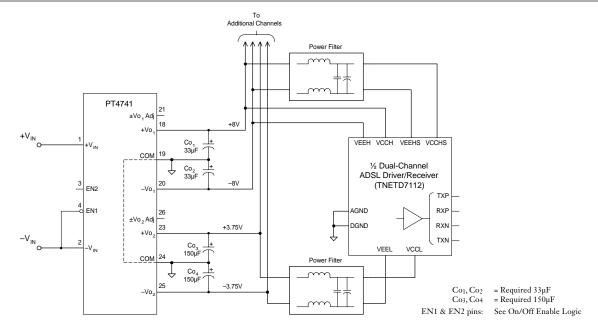

The PT4741 Excalibur™ power module is a 70-watt quad-output DC/DC converter that is designed to meet the power requirements of Texas Instruments' TNETD7112. The TNETD7112 is a dual-channel line-interface driver/receiver that compliments the AC6 ADSL chipset for use in POTS (plain old telephone service) applications. To conserve power, the TNETD7112 line drivers require two pairs of complimentary power supply voltages. These are ±8V and ±3.75V respectively.

The PT4741 module operates from a standard (-48V) telecom central office supply and provides all four supply voltages as two com-

plimentary balanced loads. (This product is not suitable for unbalanced load applications.) The load capacity allows the PT4741 to operate up to 32 line-driver ICs, representing 64 ADSL channels.

The PT4741 incorporates many features to simplify system integration. These include a flexible On/Off enable control, input under-voltage lock-out, and over-temperature protection. All outputs are short-circuit protected, and internally sequenced to meet the TNETD7112 power-up and power-down requirements.

The module is packaged in a space-saving solderable copper case, requires no heat sink, and can occupy as little as 1.9 in<sup>2</sup> of PCB area.

### **Ordering Information**

$PT4741\Box = \pm 8.0/\pm 3.75V$

### PT Series Suffix (PT1234x)

| Case/Pin<br>Configuration | Order<br>Suffix | Package<br>Code |

|---------------------------|-----------------|-----------------|

| Vertical                  | N               | (EKD)           |

| Horizontal                | A               | (EKA)           |

| SMD                       | С               | (EKC)           |

(Reference the applicable package code drawing for the dimensions and PC layout)

### **Typical Application**

Datasheet of PT4741A - CONVERTER DC-DC 48VIN 70W HORZ

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

#### PT4741 **-48V**

70-W Quad-Output DC/DC Converter for DSL

SLTS167A - APRIL 2002 - REVISED NOVEMBER 2002

### **Environmental Specifications**

| Characteristics             | Symbols      | Conditions                                                             | Min | Тур                    | Max      | Units   |

|-----------------------------|--------------|------------------------------------------------------------------------|-----|------------------------|----------|---------|

| Operating Temperature Range | $T_a$        | Over V <sub>in</sub> Range                                             | -40 | _                      | 85 (i)   | °C      |

| Solder Reflow Temperature   | $T_{reflow}$ | Surface temperature of module pins or case                             | _   | _                      | 215 (ii) | °C      |

| Storage Temperature         | $T_s$        | _                                                                      | -40 | _                      | 125      | °C      |

| Reliability                 | MTBF         | Per Bellcore TR-332<br>50% stress, T <sub>c</sub> =40°C, ground benign | 1.6 | _                      | _        | 106 Hrs |

| Mechanical Shock            |              | Per Mil-STD-883D, Method 2002.3<br>1 msec, ½ Sine, mounted             | _   | TBD                    | _        | G's     |

| Mechanical Vibration        |              | Mil-STD-883D, Method 2007.2 Suffix N<br>20-2000 Hz Suffix A, C         | _   | TBD (iii)<br>TBD (iii) | _        | G's     |

| Weight                      | _            | Vertical/Horizontal                                                    | _   | 90                     | _        | grams   |

| ShutdownTemperature         | OTP          |                                                                        |     | 115                    | 125      | °C      |

| Flammability                | _            | Meets UL 94V-O                                                         |     |                        |          |         |

- (i) See SOA curves or consult factory for appropriate derating.

(ii) During solder reflow of SMD package version, do not elevate the module case, pins, or internal component temperatures above a peak of 215°C. For further guidance refer to the application note, "Reflow Soldering Requirements for Plug-in Power Surface Mount Products," (SLTA051).

(iii) Only the case pins on through-hole pin configurations (N & A) must be soldered. For more information see the applicable package outline drawing.

### **Pin Configuration**

| Pin | Function       |

|-----|----------------|

| 1   | +Vin           |

| 2   | -Vin           |

| 3   | EN 2           |

| 4   | EN 1           |

| 5   | Do Not Connect |

| 6   | Do Not Connect |

| 7   | Do Not Connect |

| 8   | Do Not Connect |

| 9   | Do Not Connect |

| Pin | Function         |

|-----|------------------|

| 10  | Do Not Connect   |

| 11  | Pin Not Present  |

| 12  | Pin Not Present  |

| 13  | Pin Not Present  |

| 14  | Pin Not Present  |

| 15  | Pin Not Present  |

| 16  | Pin Not Present  |

| 17  | Pin Not Present  |

| 18  | +Vo <sub>1</sub> |

|     |                  |

| _Pin | Function                |

|------|-------------------------|

| 19   | COM                     |

| 20   | -Vo <sub>1</sub>        |

| 21   | ±Vo <sub>1</sub> Adjust |

| 22   | Do Not Connect          |

| 23   | +Vo <sub>2</sub>        |

| 24   | COM                     |

| 25   | -Vo <sub>2</sub>        |

| 26   | ±Vo <sub>2</sub> Adjust |

|      |                         |

### **On/Off Enable Logic**

| Pin 3 | Pin 4 | Output Status |

|-------|-------|---------------|

| ×     | 1     | Off           |

| 1     | 0     | On            |

| 0     | ×     | Off           |

Logic 1 =Open collector Logic 0 = -Vin (pin 2) potential

For positive Enable function, connect pin 4 to pin 2 and use pin 3.

For negative Enable function, leave pin 3 open and use pin 4.

### **Pin Descriptions**

**+Vin:** The positive input supply for the module with respect to -Vin. When powering the module from a -48V telecom central office supply, this input is connected to the primary system ground.

Note: Shaded functions indicate those pins that are at primary-side potential.

**-Vin:** The negative input supply for the module, and the 0VDC reference for the EN 1, and EN 2 inputs. When powering the module from a +48V supply, this input is connected to the 48V(Return).

**EN 1:** The negative logic input that activates the module output. This pin must be connected to -Vin to enable the module's outputs. A high impedance disables the module's outputs.

**EN 2:** The positive logic input that activates the module output. If not used, this pin should be left open circuit. Connecting this input to -V<sub>in</sub> disables the module's outputs.

**+Vo 1:** This is the positive high-output voltage. It is the balanced compliment of (-Vo1) and referenced to the secondary COM node.

**-Vo 1:** The negative high-output voltage, which is the balanced compliment of (+Vo<sub>1</sub>) with respect to COM.

- **+Vo 2:** This is the positive low-output voltage. It is the balanced complement of (-Vo2) and referenced to the secondary COM node.

- **-Vo 2:** The negative low-output voltage, which is the balanced compliment of (+Vo<sub>2</sub>) with respect to COM.

**COM:** This is the common node and the secondary reference for all four regulated output voltages. It provides a return for any unbalanced load current, and is DC isolated from the input supply pins.

**±Vo₁ Adjust:** Using a single resistor, this pin allows the simultaneous adjustment of both +Vo1 and -Vo1 magnitude with respect to the COM node. Adjustment can be higher or lower than the preset value. If not used this pin should be left open circuit.

**±Vo<sub>2</sub> Adjust:** Using a single resistor, this pin allows the simultaneous adjustment of both +Vo2 and -Vo2 magnitudes with respect to the COM node. Adjustment can be higher or lower than the preset value. If not used this pin should be left open circuit.

Datasheet of PT4741A - CONVERTER DC-DC 48VIN 70W HORZ

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

PT4741-**-48V**

70-W Quad-Output **DC/DC Converter for DSL**

SLTS167A - APRIL 2002 - REVISED NOVEMBER 2002

**PT4741 Electrical Specifications** (Unless otherwise stated, the operating conditions are:-  $T_a$  =25°C,  $V_{in}$  =48V, and  $I_o$  =I\_omax)

|                                                                                    |                                                     |                                                                                 |                                                      |                   | PT4741         |                                              |                           |

|------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------|-------------------|----------------|----------------------------------------------|---------------------------|

| Characteristics                                                                    | Symbols                                             | Conditions                                                                      |                                                      | Min               | Тур            | Max                                          | Units                     |

| Output Current                                                                     | $Io_1, Io_2$                                        | Balanced load                                                                   | ±Vo <sub>1</sub><br>±Vo <sub>2</sub>                 | 0                 | =              | 2.5 (1)<br>3.5 (1)                           | A                         |

|                                                                                    |                                                     | Load imbalance                                                                  | ±Vo <sub>1</sub><br>±Vo <sub>2</sub>                 | _                 | =              | ±100 (2)<br>±100 (2)                         | mA                        |

|                                                                                    |                                                     | Transient imbalance (<1ms)                                                      | ±Vo <sub>1</sub><br>±Vo <sub>2</sub>                 | _                 | =              | ±200<br>±200                                 | mA                        |

| Input Voltage Range                                                                | V <sub>in</sub>                                     | Continuous<br>Surge (1 minute)                                                  |                                                      | 36                | =              | 75<br>80                                     | V                         |

| Set-Point Voltage                                                                  | Vo <sub>1</sub> , Vo <sub>2</sub>                   | Either output to COM                                                            | ±Vo <sub>1</sub> (8.0 V)<br>±Vo <sub>2</sub> (3.75V) | 7.76<br>3.82      | 8.0<br>3.94    | 8.24<br>4.06 (3)                             | V                         |

| Temperature Variation                                                              | Reg <sub>temp</sub>                                 | $-40$ °C $\leq$ T <sub>a</sub> $\leq$ +85°C, I <sub>o</sub> =I <sub>o</sub> min | ±Vo <sub>1</sub><br>±Vo <sub>2</sub>                 | _                 | ±TBD<br>±TBD   | _                                            | $%V_{o}$                  |

| Line Regulation                                                                    | Regline                                             | All outputs, Over V <sub>in</sub> range                                         |                                                      | _                 | ±0.05          | ±0.25                                        | $%V_{o}$                  |

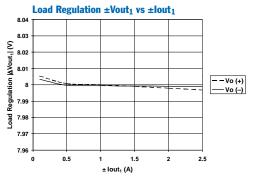

| Load Regulation                                                                    | Regload                                             | All outputs, 0≤I₀≤I₀max                                                         |                                                      | _                 | ±0.2           | ±0.5                                         | $%V_{o}$                  |

| Total Output Voltage Variation                                                     | $\Delta V_{o}$ tot                                  | Includes set-point, line, load,<br>-40°C≤Ta≤+85°C                               | ±Vo <sub>1</sub> (8.0 V)<br>±Vo <sub>2</sub> (3.75V) | 7.6<br>3.75       | _              | 8.4<br>4.13 (3)                              | V                         |

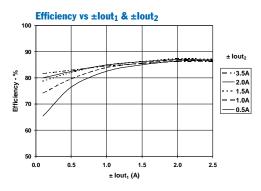

| Efficiency                                                                         | η                                                   |                                                                                 |                                                      | _                 | 86             | _                                            | %                         |

| V <sub>o</sub> Ripple (pk-pk)                                                      | V <sub>n</sub>                                      | Measured from each output to C 0 to 20MHz bandwidth                             | COM, ±Vo <sub>1</sub><br>±Vo <sub>2</sub>            | _                 | _              | 75<br>50                                     | $\mathrm{mV}_\mathrm{pp}$ |

| Transient Response                                                                 | $egin{array}{c} t_{tr} \ V_{os} \end{array}$        | 0.1A/μs load step, 50% to 75% I<br>V <sub>o</sub> over/undershoot               | omax                                                 | _                 | 75<br>2        | _                                            | μSec<br>%V <sub>o</sub>   |

| Output Adjust Range                                                                | Vo <sub>x</sub> adj                                 | Each ±Vo adjusted as pair                                                       |                                                      | _                 | ±10            | _                                            | $%V_{o}$                  |

| Balanced Load<br>Current Limit Threshold                                           | IoLIM                                               | Shutdown, auto restart                                                          | ±Vo <sub>1</sub><br>±Vo <sub>2</sub>                 | _                 | 3 (1)<br>4 (1) | =                                            | A                         |

| Unbalanced Load<br>Shutdown Threshold                                              | $I_{o}com_{sc}$                                     | Shutdown & latch off<br>(within 1 ms)                                           |                                                      | _                 | 300 (2)        | _                                            | mA                        |

| Switching Frequency                                                                | $f_{s}$                                             | Over V <sub>in</sub> and I <sub>o</sub> ranges                                  |                                                      | 550               | 600            | 650                                          | kHz                       |

| Under Voltage Lockout                                                              | $egin{array}{c} V_{ m on} \ V_{ m off} \end{array}$ | $V_{ m in}$ increasing $V_{ m in}$ decreasing                                   |                                                      | _                 | 34<br>32       | _                                            | V                         |

| Enable Control (pins 3 & 4)<br>High-Level Input Voltage<br>Low-Level Input Voltage | V <sub>IH</sub><br>V <sub>IL</sub>                  | Referenced to $-V_{in}$ (pin 2)                                                 |                                                      | 4<br>-0.2         | _              | Open (4)<br>0.8 (4)                          | V                         |

| Low-Level Input Current                                                            | ${ m I}_{ m IL}$                                    | Pin connected to –V <sub>in</sub> (pin 2)                                       |                                                      | _                 | -0.16          | -0.27                                        | mA                        |

| Standby Input Current                                                              | I <sub>in</sub> standby                             | pins 3 & 4 open circuit                                                         |                                                      | _                 | 5              | 20                                           | mA                        |

| Internal Input Capacitance                                                         | Cint                                                |                                                                                 |                                                      | _                 | 2.4            | _                                            | μF                        |

| External Output Capacitance                                                        | Co                                                  | Each output to COM                                                              | ±Vo <sub>1</sub><br>±Vo <sub>2</sub>                 | 33<br>150         | _              | 1,000 <sup>(5)</sup><br>1,000 <sup>(5)</sup> | μF                        |

| Primary/Secondary Isolation                                                        | $V_{iso}$ $C_{iso}$ $R_{iso}$                       |                                                                                 |                                                      | $\frac{1500}{10}$ |                |                                              | V<br>pF<br>MΩ             |

Notes: (1) A balanced load is defined as the current flowing out of (+Vo<sub>x</sub>) being to equal that flowing into (-Vo<sub>x</sub>). The current flowing in the COM terminal is zero.

(2) The load imbalance is the difference between the current flowing out of (+Vo<sub>x</sub>) and flowing into (-Vo<sub>x</sub>). The difference flows in the COM terminal.

(3) The nominal output voltage of ±Vo<sub>2</sub> is 3.94V. The output voltage and tolerance is defined as 3.75V, -0%, +10%.

(4) The Enable inputs (pins 3 & 4) have internal pull-ups. Leaving pin 3 open-circuit and connecting pin 4 to -V<sub>in</sub> allows the the converter to operate when input power is applied. The maximum open-circuit ivoltage is 5V.

(5) Capacitance added to each pair of complimentary output voltages (±Vo<sub>x</sub>) must be divided equally between (+Vo<sub>x</sub>) and (-Vo<sub>x</sub>) with respect to the COM terminal. E.g. Co<sub>1</sub> must equal Co<sub>2</sub>, and Co<sub>3</sub> must equal Co<sub>4</sub>.

Datasheet of PT4741A - CONVERTER DC-DC 48VIN 70W HORZ

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

PT4741—48V

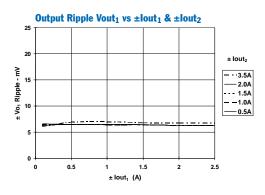

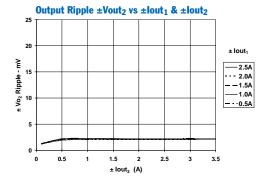

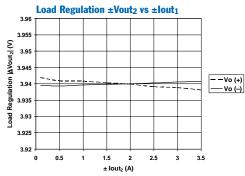

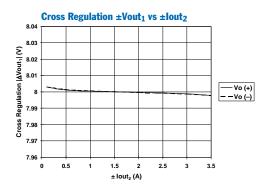

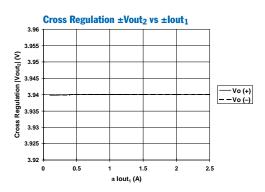

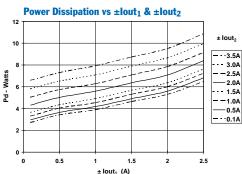

# Typical Characteristics

70-W Quad-Output DC/DC Converter for DSL

SLTS167A - APRIL 2002 - REVISED NOVEMBER 2002

### Performance Characteristics; V<sub>in</sub> =48V (See Note A)

Note A: All Characteristic data in the above graphs has been developed from actual products tested at 25°C. This data is considered typical data for the ISR.

Datasheet of PT4741A - CONVERTER DC-DC 48VIN 70W HORZ

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

PT4741—48V

# Typical Characteristics

70-W Quad-Output DC/DC Converter for DSL

SLTS167A - APRIL 2002 - REVISED NOVEMBER 2002

### Performance Characteristics; V<sub>in</sub> =48V (See Note A)

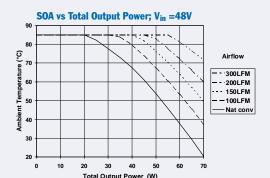

# PT4741 Safe Operating Area (SOA) (See Note B) (All outputs proportionally loaded from 0 to 100% of full load)

Note A: All Characteristic data in the above graphs has been developed from actual products tested at 25°C. This data is considered typical data for the ISR.

Note B: SOA curves represent operating conditions at which the internal components are at or below the manufacturer's maximum rated operating temperatures.

Datasheet of PT4741A - CONVERTER DC-DC 48VIN 70W HORZ

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

# **Application Notes**

PT4741

# Operating Features of the PT4741 Quad-Output DC/DC Converter for DSL Line Drivers

#### **Balanced Load Fault Protection**

A balanced load fault is the result of excess current flowing from one +V<sub>o</sub> output directly to the corresponding -V<sub>o</sub> output. The current flowing in or out of the COM node (pins 19 & 24) under this condition is within normal operating limits. Both (±)dual outputs from the PT4741 DC/DC converter incorporate protection against this type of load fault. This includes an absolute current limit in combination with a fault timeout period. When the balanced fault current from either ±dual output exceeds the "Balanced Load Current Limit Threshold" (see data sheet specifications), the converter initially limits the fault current to approximately 200% of the maximum output current rating. If the fault persists for more than 200ms the converter shuts down, forcing the voltage at all four regulated outputs to simultaneously fall to zero. Following shutdown the converter will periodically attempt to recover by executing a soft-start power-up. The converter will continually cycle through successive over-current shutdowns and restarts until the fault is removed.

### **Imbalanced Load Fault Protection**

An imbalanced load fault is the result of excess current flowing between any one of the  $+V_o$  (or the  $-V_o$ ) outputs, and the COM node (pins 19 & 24). When the current sensed in the COM node exceeds the "Unbalanced Load Shutdown Threshold" (see data sheet specifications), the PT4741 shuts down and latches off within 1ms. Once latched off, the module must be reset by momentarily interrupting the input power source.

### **Over-Temperature Protection**

The PT4741 DC/DC converter has an internal temperature sensor, which monitors the temperature of the module's internal components. If the sensed temperature exceeds a nominal 115°C, the converter will shut down. The converter will automatically restart when the sensed temperature returns to about 100°C.

### **Under-Voltage Lock-Out**

The Under-Voltage Lock-Out (UVLO) circuit prevents operation of the converter whenever the input voltage to the module is insufficient to maintain output regulation. The UVLO has approximately 2V of hysterisis. This is to prevent oscillation with a slowly changing input voltage. Below the UVLO threshold the module is off and the enable control inputs, EN1 and EN2 are inoperative.

### **Primary-Secondary Isolation**

The PT4741 DC/DC converter incorporates electrical isolation between the input terminals (primary) and the output terminals (secondary). All converters are production tested to a withstand voltage of 1500VDC. The isolation complies with UL60950 and EN60950, and the requirements for operational isolation. This allows the converter to be configured for either a positive or negative input voltage source.

The regulation control circuitry for these modules is located on the secondary (output) side of the isolation barrier. Control signals are passed between the primary and secondary sides of the converter. The data sheet 'Pin Descriptions' and 'Pin-Out Information' provides guidance as to which reference (primary or secondary) that must be used for each of the external control signals.

### **Input Current Limiting**

The converter is not internally fused. For safety and overall system protection, the maximum input current to the converter must be limited. Active or passive current limiting can be used. Passive current limiting can be a fast acting fuse. A 125-V fuse, rated no more than 10A, is recommended. Active current limiting can be implemented with a current limited "Hot-Swap" controller.

# **Application Notes**

PT4741

# Adjusting the Output Voltages of the PT4701 & PT4741 Quad-Output DC/DC Converters

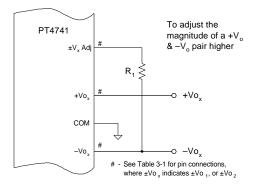

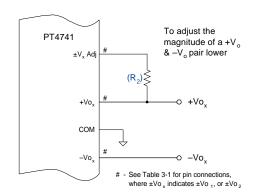

The PT4741 quad-output DC/DC converter produces two pairs of balanced  $\pm V_0$  complimentary output voltages. The magnitude of each balanced pair of outputs may be adjusted higher or lower by up to  $\pm 10\%$ . The adjustment method uses a single external resistor 1, which adjusts the magnitude of the respective  $\pm V_0$  and  $\pm V_0$  simultaneously. The value of the resistor determines the magnitude of adjustment, and the placement of the resistor determines the direction of adjustment (increase or decrease). The resistor values can be calculated using the appropriate formula (see below). The formula constants are provided in Table 3-2. Alternatively the resistor value may be selected directly from Table 3-3 and Table 3-4, for  $\pm V_{01}$  and  $\pm V_{02}$  respectively. The placement of each resistor is as follows.

**Adjust Up:** To increase the magnitude of the complimentary output voltages, add a resistor  $R_1$  between the appropriate  $\pm Vo_x$  Adj (' $\pm Vo_1$  Adj' or ' $\pm Vo_2$  Adj') and the  $-Vo_x$  voltage rail. See Figure 3-1(a) and Table 3-1 for the resistor placement and pin connections.

Figure 3-1a

### Notes:

- 1. Use only a single 1% (or better) tolerance resistor in either the  $R_1$  or  $(R_2)$  location to adjust a specific output. Place the resistor as close to the ISR as possible.

- 2. Never connect capacitors to any of the  ${}^{\backprime}Vo_x$  Adj ${}^{\backprime}$  pins. Any capacitance added to these control pins will affect the stability of the respective regulated output.

**Adjust Down:** To decrease the magnitude of the complimentary output voltages, add a resistor (R<sub>2</sub>), between the appropriate  $Vo_x$  Adj (Vo<sub>1</sub> Adj or Vo<sub>2</sub> Adj,) and the  $+Vo_x$  voltage rail. See Figure 3-1(b) and Table 3-1 for the resistor placement and pin connections.

Figure 3-1b

Table 3-1; Adjust Resistor Pin Connections

|                  | To Adjust Up<br>Connect R <sub>1</sub> |                  | To Adjust Down<br>Connect (R <sub>2</sub> ) |                  |  |

|------------------|----------------------------------------|------------------|---------------------------------------------|------------------|--|

|                  | from                                   | to               | from                                        | to               |  |

|                  | ±Vo <sub>x</sub> Adj                   | –Vo <sub>x</sub> | ±Vo <sub>x</sub> Adj                        | +Vo <sub>x</sub> |  |

| Vo <sub>1</sub>  | 21                                     | 20               | 21                                          | 18               |  |

| ·Vo <sub>2</sub> | 26                                     | 25               | 26                                          | 23               |  |

### **Calculation of Resistor Adjust Values**

The adjust resistor value may also be calculated using an equation. Note that the equation for  $R_1$  [Adjust Up] is different to that for  $(R_2)$  [Adjust Down].

$$R_1 \text{ [Adjust Up]} = \frac{2 V_r R_o}{V_a - V_o} - R_s \quad k\Omega$$

$$\begin{array}{lll} (R_2) \; [ \mbox{Adjust Down} ] & = & \frac{R_o \left( 2 \; V_a \! - \! V_r \right)}{2 \left( V_o \! - \! V_a \right)} & - \, R_s & k \Omega \end{array}$$

Where:  $V_o$  = Original output voltage ( $\pm Vo_x$ )

$V_a$  = Adjusted output voltage ( $\pm Va_x$ )

$V_r$  = The reference voltage from Table 3-2

$R_0$  = The resistance value in Table 3-2

$R_s$  = The series resistance from Table 3-2

# **Application Notes** continued

PT4741

Table 3-2

| ADJUSTMENT RANGE AND FORMULA PARAMETERS |                      |                      |  |

|-----------------------------------------|----------------------|----------------------|--|

|                                         | ±Vo <sub>1</sub> Bus | ±Vo <sub>2</sub> Bus |  |

| V <sub>o</sub> (nom)                    | 8.0V                 | 3.94V                |  |

| V <sub>a</sub> (min)                    | 7.2V                 | 3.55                 |  |

| V <sub>a</sub> (max)                    | 8.8V                 | 4.33                 |  |

| V <sub>r</sub>                          | 2.5V                 | 1.24V                |  |

| $R_0$ (k $\Omega$ )                     | 14.3                 | 13.0                 |  |

| R <sub>s</sub> (kΩ)                     | 20.0                 | 16.2                 |  |

Table 3-3

| Adj. Resistor |                  | $R_1/(R_2)$          |

|---------------|------------------|----------------------|

| 6 Adjust      | $\pm V_a(req'd)$ |                      |

| -10%          | 7.20V            | (86.4)kΩ             |

| - 9%          | 7.28V            | (99.8)kΩ             |

| - 8%          | 7.36V            | (117.0)kΩ            |

| - 7%          | 7.44V            | $(138.0)$ k $\Omega$ |

| - 6%          | 7.52V            | (167.0)kΩ            |

| - 5%          | 7.60V            | $(207.0)$ k $\Omega$ |

| - 4%          | 7.68V            | $(267.0)$ k $\Omega$ |

| - 3%          | 7.76V            | $(368.0)$ k $\Omega$ |

| - 2%          | 7.84V            | (569.0)kΩ            |

| - 1%          | 7.92V            | $(1.17)M\Omega$      |

| 0%            | 8.00V            |                      |

| + 1%          | 8.08V            | 203.0kΩ              |

| + 2%          | 8.16V            | 91.7kΩ               |

| + 3%          | 8.24V            | 54.5kΩ               |

| + 4%          | 8.32V            | 35.9kΩ               |

| + 5%          | 8.40V            | 24.7kΩ               |

| + 6%          | 8.48V            | 17.2kΩ               |

| + 7%          | 8.56V            | 11.9kΩ               |

| + 8%          | 8.64V            | 7.9kΩ                |

| + 9%          | 8.72V            | 4.8kΩ                |

| +10%          | 8.80V            | 2.3kΩ                |

$R_1 = Black, R_2 = (Blue)$

Table 3-4

| ADJUSTMENT RESISTOR VALUES FOR Vo |                                   |  |  |

|-----------------------------------|-----------------------------------|--|--|

| Adj. Resistor                     | R <sub>1</sub> /(R <sub>2</sub> ) |  |  |

| ±Va(req'd)                        |                                   |  |  |

| 3.546V                            | $(80.3)$ k $\Omega$               |  |  |

| 3.585V                            | $(92.5)$ k $\Omega$               |  |  |

| 3.625V                            | $(108.0)$ k $\Omega$              |  |  |

| 3.664V                            | $(127.0)$ k $\Omega$              |  |  |

| 3.704V                            | $(153.0)$ k $\Omega$              |  |  |

| 3.743V                            | $(190.0)$ k $\Omega$              |  |  |

| 3.782V                            | $(245.0)$ k $\Omega$              |  |  |

| 3.822V                            | $(336.0)$ k $\Omega$              |  |  |

| 3.861V                            | $(519.0)$ k $\Omega$              |  |  |

| 3.900V                            | $(1.07)M\Omega$                   |  |  |

| 3.940V                            |                                   |  |  |

| 3.979V                            | 188.0kΩ                           |  |  |

| 4.019V                            | 86.1kΩ                            |  |  |

| 4.058V                            | $52.0$ k $\Omega$                 |  |  |

| 4.098V                            | $34.9$ k $\Omega$                 |  |  |

| 4.137V                            | $24.7k\Omega$                     |  |  |

| 4.176V                            | $17.9 \mathrm{k}\Omega$           |  |  |

| 4.216V                            | 13.0kΩ                            |  |  |

| 4.255V                            | 9.4kΩ                             |  |  |

| 4.295V                            | $6.5 \mathrm{k}\Omega$            |  |  |

| 4.334V                            | 4.3kΩ                             |  |  |

|                                   |                                   |  |  |

Datasheet of PT4741A - CONVERTER DC-DC 48VIN 70W HORZ

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

# **Application Notes**

PT4741

# Using the On/Off Enable Controls on the PT4741 Quad-Output DC/DC Converter

The PT4741 is a quad-output DC/DC converter that is specifically designed for powering DSL line driver ICs. The converter incorporates two output enable controls. EN1 (pin 4) is the *Negative Enable* input, and EN2 (pin 3) is the *Positive Enable* input. Both inputs are electrically referenced to  $-V_{\rm in}$  (pin 2) on the primary or input side of the converter. A pull-up resistor is not required, but may be added if desired. Voltages of up to 70V can be safely applied to the either of the *Enable* pins.

### **Automatic (UVLO) Power-Up**

Connecting EN1 (pin 4) to  $-V_{in}$  (pin 2) and leaving EN2 (pin 3) open-circuit configures the converter for automatic power up. (See data sheet "Typical Application"). The converter control circuitry incorporates an "Under Voltage Lockout" (UVLO) function, which disables the converter until the minimum specified input voltage is present at  $\pm V_{in}$ . (See data sheet Specifications). The UVLO circuitry ensures a clean transition during power-up and power-down, allowing the converter to tolerate a slow-rising input voltage. For most applications EN1 and EN2, can be configured for automatic power-up.

### **Positive Output Enable (Negative Inhibit)**

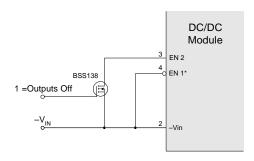

To configure the converter for a positive enable function, connect EN1 (pin 4) to -V $_{\rm in}$  (pin 2), and apply the system On/Off control signal to EN2 (pin 3). In this configuration, a low-level input voltage (-V $_{\rm in}$  potential) applied to pin 3 disables the converter outputs. Figure 1 is an example of this configuration.

Figure 1; Positive Enable Configuration

### **Negative Output Enable (Positive Inhibit)**

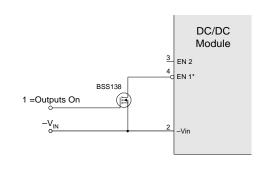

To configure the converter for a negative enable function, EN2 (pin 3) is left open circuit, and the system On/Off control signal is applied to EN1 (pin 4). A low-level input voltage (- $V_{\rm in}$  potential) must then be applied to

pin 4 in order to enable the outputs of the converter. An example of this configuration is detailed in Figure 2. Note: The converter will only produce and output voltage if a valid input voltage is applied to  $\pm V_{in}$ .

Figure 2; Negative Enable Configuration

### **On/Off Output Voltage Sequencing**

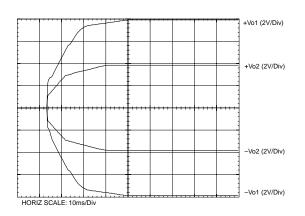

The PT4741 converter power-up characteristics meet the requirements of Texas Instruments' TNETD7112 dual-channel line-interface driver/receiver ICs. All four outputs from the converter are internally sequenced to power up in unison. Figure 3 shows the waveforms from a PT4741 following the application of power. There is a delay of appoximately 25ms from the application power to the point that the output voltages begin to rise. The converter typically produces a fully regulated output within 75ms. The waveforms of Figure 3 were measured with loads of approximately 50% on each output, with an input source of 48VDC.

Figure 3; PT4741 Power-up Sequence

Datasheet of PT4741A - CONVERTER DC-DC 48VIN 70W HORZ

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated