# A 1.55V to 5.25V, 1.9µA, 9kHz to 300kHz Silicon Timer

## **FEATURES**

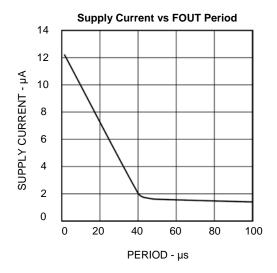

- ♦ Ultra Low Supply Current: 1.9µA at 25kHz

- ♦ Supply Voltage Operation: 1.55V to 5.25V

- ♦ Single Resistor Sets FOUT at 50% Duty Cycle

- ♦ Programmable FOUT Period:

- 9kHz ≤ FOUT ≤ 300kHz

- ♦ FOUT Period Accuracy: 3%

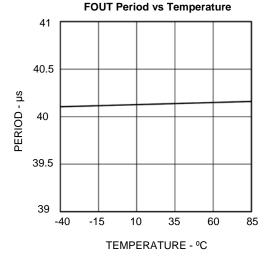

- ♦ FOUT Period Drift: 0.02%/°C

- Single Resistor Sets Output Frequency

- ♦ Separate PWM Control and Buffered Output

- FOUT/PWMOUT Output Driver Resistance: 160Ω

## **APPLICATIONS**

Portable and Battery-Powered Equipment Low-Parts-Count Nanopower Oscillator Compact Micropower Replacement for Crystal and Ceramic Oscillators

Micropower Pulse-width Modulation Control Micropower Pulse-position Modulation Control

Micropower Clock Generation Micropower Sequential Timing

## **DESCRIPTION**

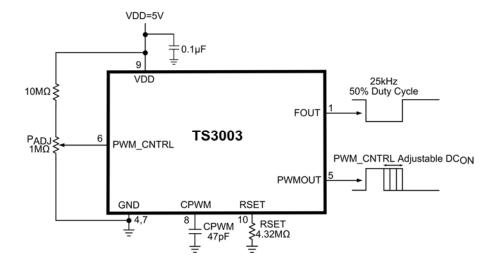

The TS3003 is a single-supply, second-generation oscillator/timer fully specified to operate at a supply voltage range of 1.55 V to 5.25 V while consuming less than 2.4 µA(max) supply current. Requiring only a resistor to set the base output frequency (or output period) at 25 kHz (or 40 µs) with a 50% duty cycle, the TS3003 timer/oscillator is compact, easy-to-use, and versatile. Optimized for ultra-long life, low frequency, battery-powered/portable applications, the TS3003 joins the TS3001, TS3002, TS3004, and TS3006 in the CMOS timer family of "NanoWatt Analog™" high-performance analog integrated circuits.

The TS3003 output frequency can be user-adjusted from 9 kHz to 300 kHz with a single resistor. In addition, the TS3003 represents a 25% reduction in pcb area and a factor-of-10 lower power consumption over other CMOS-based integrated circuit oscillators/timers. When compared against industry-standard 555-timer-based products, the TS3003 offers up to 84% reduction in pcb area and over three orders of magnitude lower power consumption.

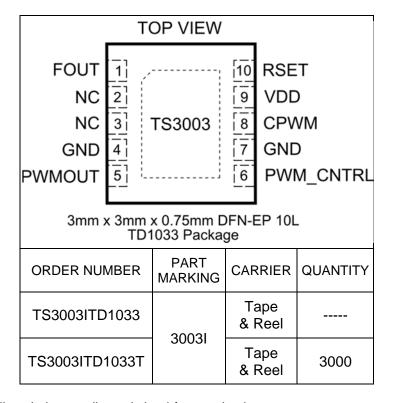

The TS3003 is fully specified over the -40°C to +85°C temperature range and is available in a low-profile, 10-pin 3x3 mm TDFN package with an exposed back-side paddle.

# TYPICAL APPLICATION CIRCUIT

## **ABSOLUTE MAXIMUM RATINGS**

| VDD to GND | Continuous Power Dissipation ( $T_A = +70^{\circ}\text{C}$ ) 10-Pin TDFN (Derate at 13.48mW/°C above +70°C) 1078mW Operating Temperature Range40°C to +85°C Storage Temperature Range65°C to +150°C Lead Temperature (Soldering, 10s)+300°C |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Electrical and thermal stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to any absolute maximum rating conditions for extended periods may affect device reliability and lifetime.

# PACKAGE/ORDERING INFORMATION

Lead-free Program: Silicon Labs supplies only lead-free packaging.

Consult Silicon Labs for products specified with wider operating temperature ranges.

Page 2 TS3003 Rev. 1.0

# **ELECTRICAL CHARACTERISTICS**

$V_{\text{DD}} = 3V, \ V_{\text{PWM\_CNTRL}} = V_{\text{DD}}, \ R_{\text{SET}} = 4.32 \text{M}\Omega, \ R_{\text{LOAD(FOUT)}} = \text{Open Circuit, } C_{\text{LOAD(FOUT)}} = \text{OpF, } C_{\text{LOAD(FWM)}} = \text{OpF, } C_{\text{PWM}} = 47 \text{pF, unless otherwise noted.} \\ \text{Values are at } T_{\text{A}} = 25^{\circ}\text{C unless otherwise noted.} \\ \text{See Note 1.} \\ \text{Note 1} = 1.0 \text{ Note 2} + 1.0 \text{ Note 3} + 1.0 \text{ Note$

| PARAMETER                                       | SYMBOL                            | CONDITIONS                                     |                               | MIN  | TYP   | MAX  | UNITS |

|-------------------------------------------------|-----------------------------------|------------------------------------------------|-------------------------------|------|-------|------|-------|

| Supply Voltage                                  | $V_{DD}$                          |                                                |                               | 1.55 |       | 5.25 | V     |

| <u> </u>                                        |                                   | CPWM = V <sub>DD</sub>                         |                               |      | 1.9   | 2.4  |       |

| Supply Current                                  | I <sub>DD</sub>                   | CI VVIVI — V DD                                | -40°C ≤ T <sub>A</sub> ≤ 85°C |      |       | 2.7  | μA    |

| Cappiy Carrent                                  | טטי                               |                                                |                               |      | 3.3   | 3.6  | μ/ (  |

|                                                 |                                   |                                                | -40°C ≤ T <sub>A</sub> ≤ 85°C |      |       | 4.5  |       |

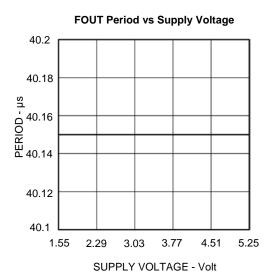

| FOUT Period                                     | t <sub>FOUT</sub>                 |                                                |                               | 39   | 40.1  | 41.2 | μs    |

|                                                 | 4 001                             |                                                | -40°C ≤ T <sub>A</sub> ≤ 85°C | 38   |       | 42   | F     |

| FOUT Period Line<br>Regulation                  | $\Delta t_{FOUT} / V$             | 1.55V ≤ V <sub>DD</sub> ≤ 5.25V                |                               |      | 0.17  |      | %/V   |

| FOUT Duty cycle                                 |                                   |                                                |                               | 49   |       | 51   | %     |

| FOUT Period<br>Temperature<br>Coefficient       | Δt <sub>FOUT</sub> /ΔT            |                                                |                               |      | 0.02  |      | %/°C  |

| PWMOUT Duty Cycle                               | DC(PWMOUT)                        |                                                |                               | 37   | 41.6  | 48   | %     |

|                                                 | DO(I WINIOUT)                     | V <sub>PWM_CNTRL</sub> = 0V                    |                               | 15   |       | 24   | 70    |

| PWMOUT Duty Cycle<br>Line Regulation            | ΔDC(PWMOUT)/V                     | 1.55V < V <sub>DD</sub> < 5.25V, FDIV2:0 = 000 |                               |      | -3    |      | %     |

| C <sub>PWM</sub> Sourcing Current               | I <sub>CPWM</sub>                 |                                                |                               | 930  |       | 1050 | nA    |

|                                                 | <u> </u>                          |                                                | -40°C ≤ T <sub>A</sub> ≤ 85°C | 810  |       | 1150 |       |

| UVLO Hysteresis                                 | $V_{\text{UVLO}}$                 | $(V_{DD}=1.55V) - (V_{DD\_SHUTDOWN\ VOLTAGE}$  | .)                            | 150  |       | 250  | mV    |

| FOUT, PWMOUT<br>Rise Time                       | t <sub>RISE</sub>                 | See Note 2, C <sub>L</sub> = 15pF              |                               |      | 10    |      | ns    |

| FOUT, PWMOUT<br>Fall Time                       | t <sub>FALL</sub>                 | See Note 2, C <sub>L</sub> = 15pF              |                               |      | 10    |      | ns    |

| FOUT Jitter                                     |                                   | See Note 3                                     |                               |      | 0.001 |      | %     |

| RSET Pin Voltage                                | V(RSET)                           |                                                |                               |      | 0.3   |      | V     |

| FDIV Input Current                              | , ,                               |                                                |                               |      |       | 10   | nA    |

|                                                 | $I_{FDIV}$                        |                                                | -40°C ≤ T <sub>A</sub> ≤ 85°C |      |       | 20   | i"`   |

| Maximum Oscillator<br>Frequency                 | Fosc                              | RSET= 360K                                     |                               |      |       | 300  | kHz   |

| High Level Output                               |                                   |                                                |                               |      |       |      |       |

| Voltage, FOUT and PWMOUT                        | V <sub>DD</sub> - V <sub>OH</sub> | I <sub>OH</sub> = 1mA                          |                               |      | 160   |      | mV    |

| Low Level Output<br>Voltage, FOUT and<br>PWMOUT | V <sub>OL</sub>                   | I <sub>OL</sub> = 1mA                          |                               |      | 140   |      | mV    |

| Dead Time                                       | T <sub>DT</sub>                   | FOUT edge falling and PWMOUT edge rising       |                               |      | 106   |      | ns    |

**Note 1:** All devices are 100% production tested at  $T_A = +25$ °C and are guaranteed by characterization for  $T_A = T_{MIN}$  to  $T_{MAX}$ , as specified.

Note 2: Output rise and fall times are measured between the 10% and 90% of the V<sub>DD</sub> power-supply voltage levels. The specification is based on lab bench characterization and is not tested in production.

**Note 3:** Timing jitter is the ratio of the peak-to-peak variation of the period to the mean of the period. The specification is based on lab bench characterization and is not tested in production.

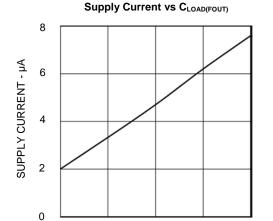

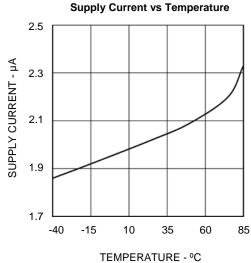

# TYPICAL PERFORMANCE CHARACTERISTICS

$V_{\text{DD}} = 3\text{V}, \ V_{\text{PWM\_CNTRL}} = V_{\text{DD}}, \ R_{\text{SET}} = 4.32\text{M}\Omega, \ R_{\text{LOAD(FOUT)}} = \text{Open Circuit, } C_{\text{LOAD(FOUT)}} = \text{OpF, } C_{\text{LOAD(FWM)}} = \text{OpF, CPWM} = V_{\text{DD}}, \ \text{unless otherwise noted.}$

20

$C_{\text{LOAD}}$ - pF

30

40

0

10

Page 4 TS3003 Rev. 1.0

# **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_{\text{DD}} = 3V, \ V_{\text{PWM\_CNTRL}} = V_{\text{DD}}, \ R_{\text{SET}} = 4.32 \text{M}\Omega, \ R_{\text{LOAD(FOUT)}} = \text{Open Circuit, } C_{\text{LOAD(FOUT)}} = \text{OpF, } C_{\text{LOAD(PWM)}} = \text{OpF, CPWM} = V_{\text{DD}}, \ \text{unless otherwise noted.}$

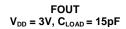

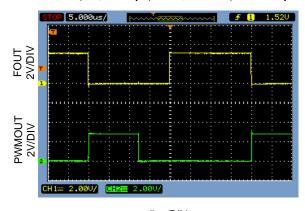

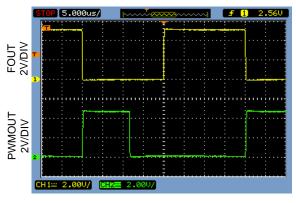

5µs/DIV

5µs/DIV

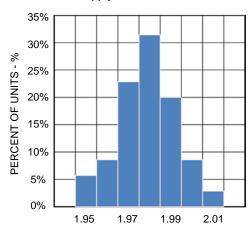

#### **Supply Current Distribution**

SUPPLY CURRENT -  $\mu A$

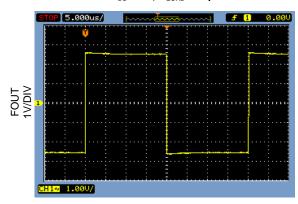

# FOUT $V_{DD} = 5V$ , $C_{LOAD} = 15pF$

5µs/DIV

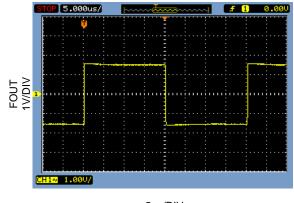

# FOUT and PWMOUT

5µs/DIV

# **PIN FUNCTIONS**

| PIN  | NAME      | FUNCTION                                                                                                                                                                                                                                                                                                                    |

|------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | FOUT      | Fixed Frequency Output. A push-pull output stage with an output resistance of $160\Omega$ . FOUT pin swings from GND to VDD. For lowest power operation, capacitance loads should be minimized and resistive loads should be maximized.                                                                                     |

| 2,3, | NC        | Non-Connect.                                                                                                                                                                                                                                                                                                                |

| 5    | PWMOUT    | Pulse-width Modulated Output. A push-pull output stage with an output resistance of $160\Omega$ , the PWMOUT pin is wired antiphase with respect to FOUT and swings from GND to VDD. For lowest power operation, capacitance loads should be minimized and resistive loads should be maximized.                             |

| 6    | PWM_CNTRL | PWM Output Pulse Control Pin. Applying a voltage between GND and V <sub>RSET</sub> will reduce the duty cycle of the PWMOUT output that is set by the capacitor connected to the CPWM pin. Connect PWM_CNTRL to VDD for fixed PWMOUT output pulse time (determined only by capacitor at CPWM).                              |

| 4,7  | GND       | Ground. Connect this pin to the system's analog ground plane.                                                                                                                                                                                                                                                               |

| 8    | CPWM      | PWMOUT Pulse Width Programming Capacitance Input. A target capacitance connected from this pin to GND sets the duty cycle of the PMW output. Minimize any stray capacitance on this pin. The voltage on this pin will swing from GND to VRSET. Connect CPWM to VDD to disable PWM function (saves PWM current).             |

| 9    | VDD       | Power Supply Voltage Input. The supply voltage range is $1.55V \le V_{DD} \le 5.25V$ . Bypass this pin with a $0.1uF$ ceramic coupling capacitor in close proximity to the TS3003.                                                                                                                                          |

| 10   | RSET      | FOUT Programming Resistor Input. A 4.32MOhm resistor connected from this pin to ground sets the T3003's internal oscillator's output period to 40µs (25KHz). For optimal performance, the composition of the RSET resistor shall be consistent with a tolerance of 1% or lower. The RSET pin voltage is approximately 0.3V. |

Page 6 TS3003 Rev. 1.0

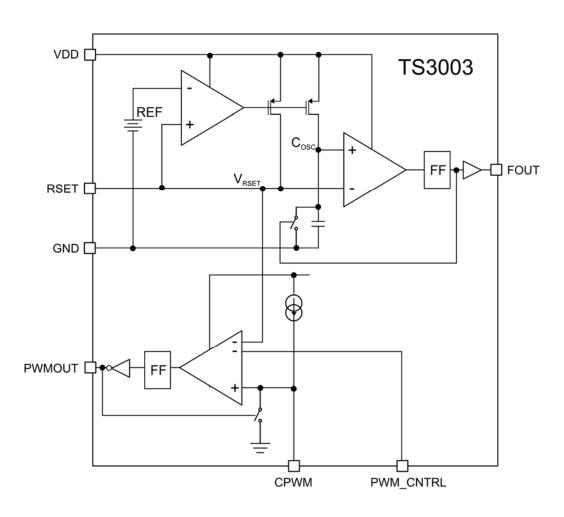

# **BLOCK DIAGRAM**

# THEORY OF OPERATION

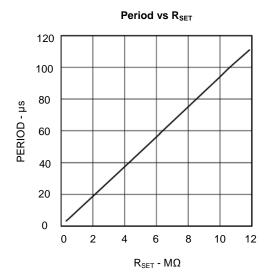

The TS3003 is a user-programmable oscillator where the period of the square wave at its FOUT terminal is generated by an external resistor connected to the RSET pin. The output frequency is given by:

$$FOUT (kHz) = \frac{1.08E11}{RSET}$$

**Equation 1. FOUT Frequency Calculation**

| R <sub>SET</sub> (MΩ) | FOUT (kHz) |

|-----------------------|------------|

| 0.360                 | 300        |

| 1                     | 108        |

| 2.49                  | 43.37      |

| 4.32                  | 25         |

| 6.81                  | 15.86      |

| 9.76                  | 11.07      |

| 12                    | 9          |

Table 1: FOUT vs R<sub>SET</sub>

With an  $R_{SET}=4.32M\Omega$ , the output frequency is approximately 25kHz with a 50% duty cycle. As design aids, Tables 1 lists TS3003's typical FOUT for various standard values for  $R_{SET}$ .

The output frequency can be user-adjusted from 9kHz to 300kHz with a single resistor. The TS3003 also provides a separate PWM output signal at its PWMOUT terminal that is anti-phase with respect to FOUT. A dead time of approximately 106ns exists between FOUT and PWMOUT. To adjust the pulse width of the PWMOUT output, a single capacitor can be placed at the CPWM pin. To determine the capacitance needed for a desired pulse width, the following equation is to be used:

$$CPWM(F) = \frac{Pulse \ Width(s) \ x \ I_{CPWM}}{V_{CPWM} \cong 300mV}$$

### **Equation 2.** CPWM Capacitor Calculation

where  $I_{\text{CPWM}}$  and  $V_{\text{CPWM}}$  is the current supplied and voltage applied to the CPWM capacitor, respectively. The pulse width is determined based on the period of FOUT and should never be greater than the period at FOUT. Make sure the PWM\_CNTRL pin is set to at least 400mV when calculating the pulse width of PWMOUT. Note  $V_{\text{CPWM}}$  is approximately 300mV, which is the RSET voltage. Also note that  $I_{\text{CPWM}}$  is approximately 1 $\mu$ A.

The PWMOUT output pulse width can be adjusted further after selecting a CPWM capacitor. This can be achieved by applying a voltage to the PWM\_CNTRL pin between V<sub>RSET</sub> and GND. With a voltage of at least V<sub>RSET</sub>, the pulse width is set based on Equation 2. For example, with a period of 40µs( 25kHz) a 47pF capacitor at the CPWM pin generates a pulse width of approximately 16µs. This can be calculated using equation 2. By reducing the PWM CNTRL voltage from  $V_{RSET} \cong 300 \text{mV}$  to GND, the pulse width is reduced from 16µs to approximately 8µs. This is a pulse width reduction of 50%. Note that as the FOUT frequency increases, the amount of pulse width reduction reduces and vice versa. Furthermore, if the PWMOUT output is half the frequency of the FOUT output, this means your CPWM capacitor is too large and as a result, the pulse width is greater than the FOUT period. In this case, use Equation 2 and reduce the capacitor value to less than the period. Connect CPWM to VDD to disable the PWM function and in turn, save power. Connect PWM CNTRL to VDD for a fixed PWMOUT output pulse width, which is determined by the CPWM pin capacitor only.

## **APPLICATIONS INFORMATION**

### **Minimizing Power Consumption**

To keep the TS3003's power consumption low, resistive loads at the FOUT and PWMOUT terminals increase dc power consumption and therefore should be as large as possible. Capacitive loads at the FOUT and PWMOUT terminals increase the TS3003's transient power consumption and, as well, should be as small as possible.

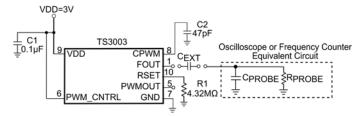

One challenge to minimizing the TS3003's transient power consumption is the probe capacitance of oscilloscopes and frequency counter instruments. Most instruments exhibit an input capacitance of 15pF or more. Unless buffered, the increase in transient load current can be as much as 400nA.

To minimize capacitive loading, the technique shown in Figure 1 can be used. In this circuit, the principle of

Figure 1: Using an External Capacitor in Series with Probes Reduces Effective Capacitive Load.

series-connected capacitors can be used to reduce the effective capacitive load at the TS3003's FOUT and PWMOUT terminals.

To determine the optimal value for  $C_{\text{EXT}}$  once the probe capacitance is known by simply solving for  $C_{\text{EXT}}$  using the following expression:

$$C_{EXT} = \frac{1}{\frac{1}{C_{LOAD(EFF)}} - \frac{1}{C_{PROBE}}}$$

**Equation 3:**External Capacitor Calculation

For example, if the instrument's input probe capacitance is 15pF and the desired effective load capacitance at either or both FOUT and PWMOUT terminals is to be  $\leq$ 5pF, then the value of C<sub>EXT</sub> should be  $\leq$ 7.5pF.

Page 8 TS3003 Rev. 1.0

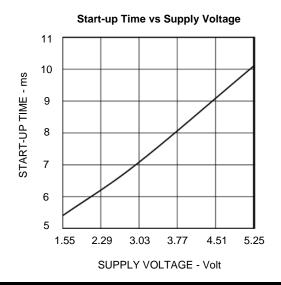

#### TS3003 Start-up Time

As the TS3003 is powered up, its FOUT terminal (and PWMOUT terminal, if enabled) is active once the applied VDD is higher than 1.55V. Once the applied VDD is higher than 1.55V, the master oscillator achieves steady-state operation within 8ms.

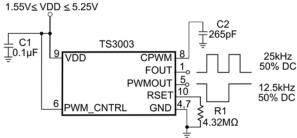

# Divide the PWMOUT Output Frequency by Two with the TS3003

Using a single resistor and capacitor, the TS3003 can be configured to a divide by two circuit as shown in Figure 2. To achieve a divide by two function with the TS3003, the pulse width of the PWMOUT output must be at least a factor of 2 greater than the period set at FOUT by resistor RSET. The CPWM capacitor selected must meet this pulse width requirement and can be calculated using Equation 2. In Figure 3, a value of 4.32M $\Omega$  for RSET sets the FOUT output period to 40 $\mu$ s. A CPWM capacitor of 265pF was chosen, which sets the pulse width of PWMOUT to approximately 80 $\mu$ s. This is well above the required minimum pulse width of 40 $\mu$ s.

**Figure 2:** Configuring the TS3003 into a Divide by Two Frequency Divider

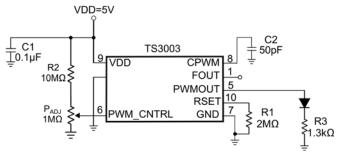

# Using the TS3003 and a Potentiometer to Dim an LED

The TS3003 can be configured to dim an LED by modulating the pulse width of the PWMOUT output. With an RSET=  $2M\Omega$ , the FOUT output frequency is approximately 51kHz (or 19.5µs period). Refer to Figure 3. The CPWM capacitor was calculated using Equation 2 with a pulse width of 15µs. To reduce the pulse width from 15µs and in turn, dim the LED, a  $1M\Omega$  potentiometer is used. The potentiometer is connected to the PWM\_CNTRL pin in a voltage divider configuration. The supply voltage of the circuit is 5V.

Figure 3: TS3003 Configured to Dim an LED with a Potentiometer

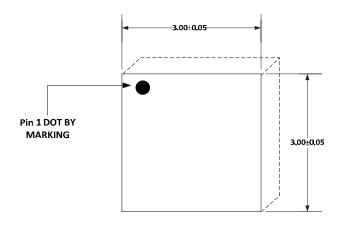

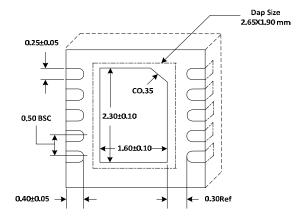

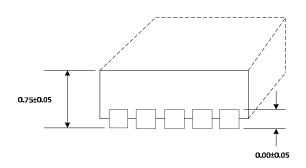

## PACKAGE OUTLINE DRAWING

## 10-Pin TDFN33 Package Outline Drawing

(N.B., Drawings are not to scale)

### **TOP VIEW**

### **BOTTOM VIEW**

### NOTE!

- All dimensions in mm.

- Compliant with JEDEC MO-229

### **SIDE VIEW**

#### **Patent Notice**

Silicon Labs invests in research and development to help our customers differentiate in the market with innovative low-power, small size, analog-intensive mixed-signal solutions. Silicon Labs' extensive patent portfolio is a testament to our unique approach and world-class engineering team.

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where personal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc.

Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific written consent of Silicon Laboratories. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA