# **Excellent Integrated System Limited**

Stocking Distributor

Click to view price, real time Inventory, Delivery & Lifecycle Information:

STMicroelectronics L9925

For any questions, you can email us directly: <a href="mailto:sales@integrated-circuit.com">sales@integrated-circuit.com</a>

# DMOS DUAL FULL BRIDGE DRIVER

- 2 INDEPENDENTLY CONTROLLED H-BRIDGES

- RDS,ON <  $0.9\Omega$  @ Tamb =  $25^{\circ}$ C, Vs = 14V

- 0.8A DC CURRENT WITHOUT HEAT SINK

- LOW QUIESCENT MODE Iq <200µA

- THEMAL PROTECTION

- CROSS CONDUCTION PROTECTION

- SUPPLY VOLTAGE UP TO 40V

- CMOS COMPATIBLE INPUTS

- OUTPUT SHORT-CIRCUIT PROTECTION

## **DESCRIPTION**

The L9925 is a dual full bridge driver for stepper motor applications. Realized in BCD (Bipolar, CMOS & DOS) techology, logic circuits, precise linear blocks and power transistors are combined to optimize circuit performance and minimize off chip components. Schmitt triggers are used for all input stages and are fully compatible with 5V CMOS logic levels. When both enable signals are low, the IC is commanded to a low quiescent current state and will draw less than 200µA from the battery.

The charge purp is integrated on chip; no external components are required. Full performance is maintaned for 9V <Vs <16V. Extended ranges of 6V <<'/s <3V and 16V <Vs <40V yields full functionally but with relaxed performance. Over temperature protection and ESD protection to all pins ansures relability and reduces system integration failures.

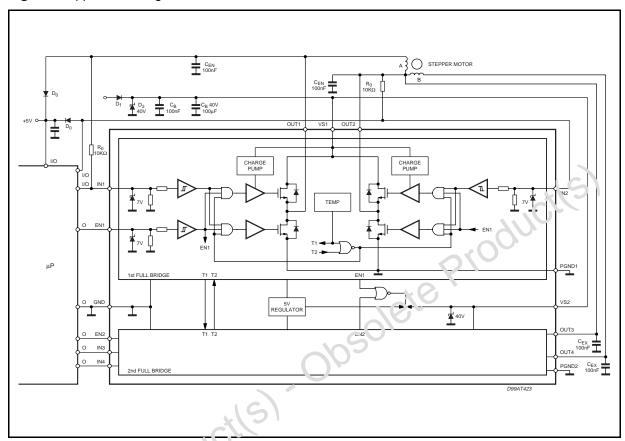

# **BLOCK DIAGRAM**

March 1999 1/9

## ABSOLUTE MAXIMUM RATINGS

Absolute Maximum Ratings are those values beyond whih damage to the device may occur. Functional operation under these condition isn't implied.

For voltages and currents applied externally to the device:

| Symbol                            | Parameter                                                                                                                                                                                 | Value          | Unit        |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|

| Vvsdc                             | Dc Supply Voltage                                                                                                                                                                         | -0.3 to 26     | V           |

| Vvsp                              | Supply Voltage Pulse (T ≤400ms) (1)                                                                                                                                                       | 40             | V           |

| Іоит                              | DC Output Load Current                                                                                                                                                                    | ±1.2           | Α           |

| IOUT MAX                          | DC Output Current: for VOUT > VVS +0.3V or VOUT < -0.3V the internal DMOS reverse and/or substrate diode become conductive and the applied current should not exceed the specified limit. | ±1.8           | A           |

| VIN1,2                            | DC Input Voltage                                                                                                                                                                          | -0.3 to 7      | V           |

| VEN                               | Enable Input Voltage                                                                                                                                                                      | -0.3 ic /      | V           |

| T <sub>stg</sub> , T <sub>j</sub> | Storage and Junction Temperature                                                                                                                                                          | -40 o 150      | °C          |

| Ptot                              | Total Power Dissipation (T <sub>pins</sub> = 80°C)<br>(T <sub>amb</sub> = 70°C no copper area on PCB)<br>(T <sub>amb</sub> =70°C 8cm <sup>2</sup> copper area on PCS,                     | 5<br>1.23<br>2 | W<br>W<br>W |

<sup>(1)</sup> Device may be overstressed if pulsed simultaneous with short circuit at one or ruc e or une outputs will be present.

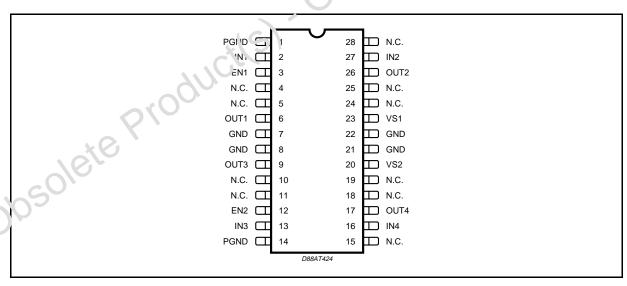

# PIN CONNECTION

# **THERMAL DATA**

| Symbol                | Parameter                                    | Value | Unit |

|-----------------------|----------------------------------------------|-------|------|

| Тјтѕ                  | Thermal Shut-down junction temperature min.  | 150   | °C   |

| T <sub>jTSH</sub>     | Thermal Shut-down thereshold hysteresis typ. | 25    | °C   |

| R <sub>th j-amb</sub> | Thermal Resistance Junction-ambient (2)      | 50    | °C/W |

| Rth j-pins            | Thermal Resistance Junction-pins             | 15    | °C/W |

<sup>(2)</sup> With 6cm<sup>2</sup> on board heat sink area

# **PIN FUNCTIONS**

| N.     | Name  | Function                                         |

|--------|-------|--------------------------------------------------|

| 1      | PGND1 | Ground for DMOS sources in bridge 1              |

| 2      | IN1   | Digital Input from motor controller for bridge 1 |

| 3      | EN1   | Logic enable/disable for bridge 1 (active high)  |

| 4, 5   | NC    | No connect                                       |

| 6      | OUT1  | Output of one half of bridge 1                   |

| 7, 8   | GND   | Ground                                           |

| 9      | OUT3  | Output of one half of bridge 2                   |

| 10, 11 | NC    | No connect                                       |

| 12     | EN2   | Logic enable/disable for bridge 2 (active high)  |

| 13     | IN3   | Digital Input from motor controller for bridge 2 |

| 14     | PGND2 | Ground for DMOS sources in bridge 2              |

| 15     | NC    | No connect                                       |

| 16     | IN4   | Digital Input from motor controller for bridge 2 |

| 17     | OUT4  | Output of one half of bridge 2                   |

| 18, 19 | NC    | No connect                                       |

| 20     | VS2   | Supply Voltage for bridge 2                      |

| 21, 22 | GND   | Ground                                           |

| 23     | VS1   | Supply Voltage for bridge 1                      |

| 24, 25 | NC    | No connect                                       |

| 26     | OUT2  | Output of one half or bridge 1                   |

| 27     | IN2   | Digital Input from motor controller for bridge 1 |

| 28     | NC    | No connext                                       |

# **ELECTRICAL CHAP.ACTERISTICS** (Vs = 9 to 16V; $T_j$ = -40 to 150°C <sup>(3)</sup>, unless otherwise specified.)

| Symbol            | Parameter                    | Test Condition                                 | Min. | Тур. | Max. | Unit |

|-------------------|------------------------------|------------------------------------------------|------|------|------|------|

| Is                | Ouicscent Current            | EN1 = EN2 =0V; T <sub>j</sub> = 85°C           |      |      | 200  | μΑ   |

|                   |                              | EN1 = EN2 =5V; I <sub>load</sub> = 0A          |      | 5    | 12   | mA   |

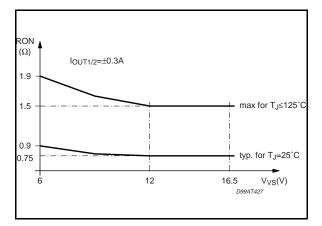

| Pas               | Switch on Resistance         | $T_j = 25$ °C; $V_S = 14V$ ; $I_O = 300$ mA    |      | 0.75 | 0.8  | Ω    |

| iQ -              |                              | $T_j = 125$ °C; $V_S = 6V$ ; $I_0 = 300$ mA    |      | 1.5  | 1.9  | Ω    |

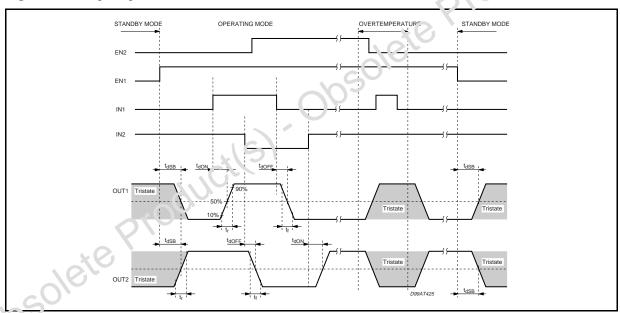

| Td-on             | Turn-on delay                | See Fig 1                                      |      | 10   | 50   | μs   |

| T <sub>d-SB</sub> | Standby setting time         | See Fig 1                                      |      | 50   | 200  | μs   |

| Td-off            | Turn-off delay               | See Fig 1                                      |      | 10   | 50   | μs   |

| trise             | Output rise time (10 to 90%) | See Fig 1                                      | 0.5  | 5    | 20   | μs   |

| t <sub>fall</sub> | Output fall time (90 to 10%) | See Fig 1                                      | 0.5  | 5    | 20   | μs   |

| ILo               | Output leakage current       | EN = 0V; V <sub>o</sub> =V <sub>S</sub> or GND | -10  |      | 10   | mA   |

| INx, ENx          | Logic Input Low voltage      |                                                | -0.3 |      | 1.5  | V    |

|                   | Logic Input High voltage     |                                                | 3.5  |      | 6    | V    |

|                   | Hysteresis                   |                                                | 0.5  | 1.0  | 2.0  | V    |

| Ibias             | Input bias current           |                                                | -50  |      | 300  | μΑ   |

The voltage refered to GND and currents are assumed positive, when the current flows into the pin. (3) Tested up to  $125^{\circ}$ C, parameter guaranted by correlation up to  $150^{\circ}$ C

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

## L9925

# **Logic Levels**

All inputs are positive, non inverting logic

| Logic State | Voltage Range |

|-------------|---------------|

| 0           | -0.3 to 1.5V  |

| 1           | 3.5 to 6.0V   |

## **Truth Table** Enable/ Disable

| EN1 | EN0 | Bridge 1 | Bridge 2 | lq     |

|-----|-----|----------|----------|--------|

| 0   | 0   | Disabled | Disabled | <200μΑ |

| 0   | 1   | Disabled | Enabled  | <12mA  |

| 1   | 0   | Enabled  | Disabled | <12mA  |

| 1   | 1   | Enabled  | Enabled  | <12mA  |

# **General Operation**

With the bridge enabled, each input INx, maps directly to the corresponding output OUTx.

The output voltage will be equal to the difference between the supply rail and the product of the load current ad the on resistance of the output switch.  $V_{out} = V_{supply} - (RDS,ON \cdot ILOAD)$ .

Sourced load currents are positive.

| IN1 | OUT1 | IN2 | OUT2 | IN3 | OUT3 | IN4 | OUT4 |

|-----|------|-----|------|-----|------|-----|------|

| 0   | 0    | 0   | 0    | 0   | 0    | 0   | 0    |

| 1   | Vs   | 1   | Vs   | 1   | VS   | 19  | ۱'S  |

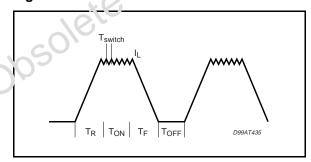

Figure 1. Timing Diagram

Figure 2. Typical Ron - Characteristics of Source and Sink Stage

Figure 3. ON - Resistance vs Supply Voltage

Datasheet of L9925 - IC MOTOR DRIVER PAR 28SO

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

L9925

Figure 4. Application Diagram

Figure 4 shows a typical application diagram for DC motor driving. To assure the safety of the circuit in the reverse battery condition a reverse protetion diode D1 is necessary. The transient protection diode Do must assure that themaximum supply voltage V3 during the transients at the VBAT line value lower than the absolute maximu ratings for VVSP. The capacities CB are used to lower Vs-EMR and its values depend on the driving load.

The resistance feedback loop realized by Ro limited to the  $\mu P$  power supply line by the diode  $D_0$ allows open load detection. To protect the device at the outputs against EMI or ESD > 2KV external capacitors Cex may be used.

# **CIRCUIT DESCRIPTION**

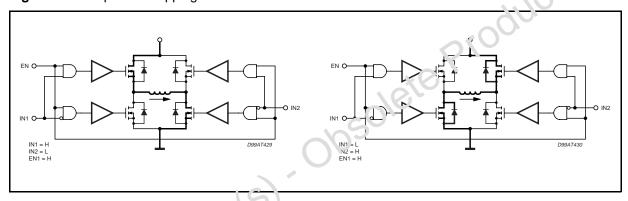

L9925 is a dual full bridge IC designed to drive DC motors, stepper motors and other inductive loads. Eah bridge has 4 power DMOS transistor with RDson =  $0.75\Omega$  and the relative protection and control circuitry (see fig. 5). The 4 half bridges can be controlled independently by means of the 4 inputs IN1, IN3, IN4 and 2 enable inputs ENABLE1 and ENABLE2.

LOGIC DRIVE (true table for the two full bridges)

| INPUT         | S           | OUTPUT      |                                                                       |

|---------------|-------------|-------------|-----------------------------------------------------------------------|

|               | IN1<br>IN3  | IN2<br>IN4  | MOSFETS                                                               |

| EN1 = EN2 = H | L<br>H<br>H | L<br>H<br>L | Sink 1, Sink2<br>Sink1, Source2<br>Source1, Sink2<br>Source1, Source2 |

| @Tj > 150°C   | Х           | Х           | All transistors turned OFF                                            |

| EN1 = EN2 = L | Х           | Х           | All transistors turned OFF                                            |

L = Low; H = High; X = Don't care

# **CROSS CONDUCTION**

The device guarantees the absence of cross-conduction by watching internal gate-source voltage of the driving power DMOS.

# TRANSISTOR OPERATION

#### ON STATE

When one of POWER DMOS transistors is ON it can be considered as a resistor RDS(ON) =  $0.75\Omega$ at a junction temperature of 25°C

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

Datasheet of L9925 - IC MOTOR DRIVER PAR 28SO

# L9925

In this condition the dissipated power is ginen by:

$Pon = Rds(on) \cdot Ids^2$

The low RDS(ON) of the Multipower BCD process can provide high currents with low power dissipation.

## **OFF STATE**

When one of the POWER DMOS transistor is OFF the VDs voltage is equal to the supply voltage and only the leakage current IDSS flows.

The power dissipation during this period is given

Poff = Vs · IDSS

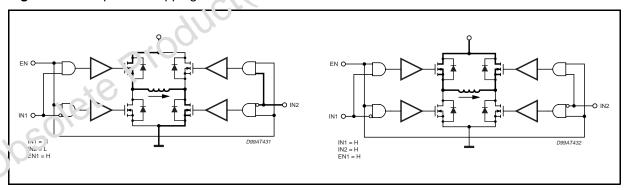

Figure 5a. Two phase chopping

## **TRANSITIONS**

Like all MOS power transistors the DMOS POWER transistors have an intrinsic diode between their source and drain that can operate as a fast freewheeling diode in switched mode applications. During recirculation with the ENABLE input is low, the POWER MOS is OFF and the diode voltage it is clamped to its characteristics. When the ENABLE input is low, the POWER MOS is OFF and the diode carries all of the recirculation current. The power dissipated in the transitional times in the cycle depends upon the voltage and current waveforms in the application.

$P_{trans} = I_{DS}(t) \cdot V_{DS}(t)$

Figure 5b. One phase chopping

Figure 5c. Enable chopping

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

L9925

#### THERMAL PROTECTION

A thermalprotection circuit has been included that will disable the device if the junction temperature reaches 150°C. When the temperature has fallen to a safe level the device restarts under the control of the input and enable signals.

## APPLICATION INFORMATION

#### RECIRCULATION

During recirculationwith the ENALBE input high, the voltage drop across the transistor is RDS(ON). for voltages less than 0.6V and is clamped at a voltages depending on the characteristics of the source-drain diode for greater voltages. Although the device is protected against cross conduction.

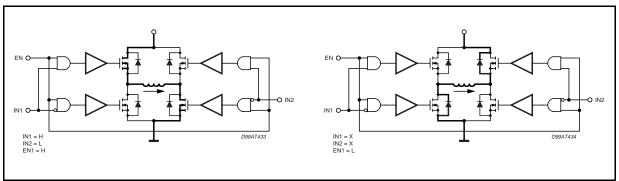

# POWER DISSIPATION each bridge

In order to achieve the high performance provided by the L9925 some attention must be paid t ensure that it has an adequate PCB area to dissipate the heat. The forst stage of any thermal design is to calculate the dissipated power in the application, for this example the half step operation shown in Fig. 6 is considered.

# RISE TIME TR

When an arm of the half bridge is turned or, current begins to flow in the inductive load at til the maximum current IL is reached after a time TR, The dissipated energy EOFF/ON.

EOFF/ON =

$$[PDS(CN) \cdot IL^2 \cdot TR] \cdot \frac{2}{3}$$

Figure 6.

#### ON TIME TON

During this time the energy dissipated is due to the ON resistance of the transistors EoN and the commutation Ecom. As two of the POWER DMOS transistors are ON Eon is given by:

$$Eon = IL^2 \cdot RDS(ON) \cdot 2 \cdot TON$$

In the commutation the energy dissipated is:

$$Econ = Vs \cdot IL \cdot Tcom \cdot fswitch \cdot Ton$$

Where:

TCOM = Communication Time and it is assumed that:;

TCOM = trise = tfall  $\leq 20\mu$ s

Tswitch = Chopper frequency

# FALL TIME TF

For this example it is assumed that the energy dissipated in this part of the cycle takes the same form as that shown for the rise time:

$$E_{OFF/ON} = [RDS(ON) \cdot IL^2 \cdot TF] \cdot \frac{2}{3}$$

# QUIESCENT ENERGY

The last contribution of the energy dissipation is due to the quiescrent supply current and is given by:

Equiescent = Iquiescent

$$\cdot$$

Vs  $\cdot$  T

# TOTAL ENERGY PER CYCLE

ETOT =

$$(2 \cdot \text{EOFF/ON} + \text{EON} + \text{ECOM})$$

bridge1+

+  $(2 \cdot \text{EOFF/ON} + \text{EON} + \text{ECOM})$  bridg2 + EQUIESCENT

The total power dissipation PDIS is simply:

$$P_{DIS} = \frac{E_{tot}}{T}$$

$T_R$  = Rise time

$T_{ON} = ON time$

T<sub>F</sub> = Fall time

$T_{OFF} = OFF$  time

T = Period

$$T = TR + TON + TF + TOFF$$

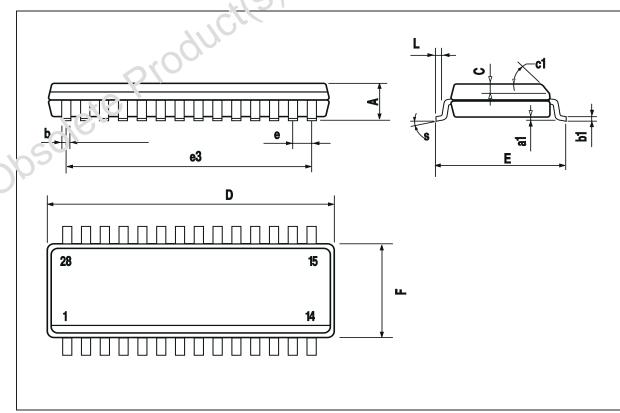

| DIM. | mm         |       |       | inch   |       |       |

|------|------------|-------|-------|--------|-------|-------|

|      | MIN.       | TYP.  | MAX.  | MIN.   | TYP.  | MAX.  |

| Α    |            |       | 2.65  |        |       | 0.104 |

| a1   | 0.1        |       | 0.3   | 0.004  |       | 0.012 |

| b    | 0.35       |       | 0.49  | 0.014  |       | 0.019 |

| b1   | 0.23       |       | 0.32  | 0.009  |       | 0.013 |

| С    |            | 0.5   |       |        | 0.020 |       |

| с1   |            |       | 45° ( | (typ.) |       |       |

| D    | 17.7       |       | 18.1  | 0.697  |       | 0.713 |

| Е    | 10         |       | 10.65 | 0.394  |       | 0.419 |

| е    |            | 1.27  |       |        | 0.050 |       |

| е3   |            | 16.51 |       |        | 0.65  |       |

| F    | 7.4        |       | 7.6   | 0.291  |       | 0.299 |

| L    | 0.4        |       | 1.27  | 0.016  |       | 0.050 |

| S    | 8 ° (max.) |       |       |        |       |       |

# OUTLINE AND MECHANICAL DATA

57

# Distributor of STMicroelectronics: Excellent Integrated System Limited

Datasheet of L9925 - IC MOTOR DRIVER PAR 28SO

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

L9925

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics © 1999 STMicroelectronics – Printed in Italy – All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco - The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.

http://www.st.com