# **Excellent Integrated System Limited**

Stocking Distributor

Click to view price, real time Inventory, Delivery & Lifecycle Information:

NXP Semiconductors/Freescale Semiconductor, Inc. GTL2006PW,118

For any questions, you can email us directly: <u>sales@integrated-circuit.com</u>

## INTEGRATED CIRCUITS

Product data Supersedes data of 2003 Dec 18 2004 Jun 21

**Philips Semiconductors**

Product data

# 13-bit GTL–/GTL/GTL+ to LVTTL translator

### GTL2006

### **FEATURES**

- Operates as a GTL–/GTL/GTL+ to LVTTL sampling receiver or LVTTL to GTL–/GTL/GTL+ driver

- 3.0 V to 3.6 V operation

- LVTTL I/O not 5 V tolerant

- Series termination on the LVTTL outputs of 30  $\Omega$

- ESD protection exceeds 2000 V HBM per JESD22-A114, 200 V MM per JESD22-A115 and 250 V CDM per JESD22-C101

- Latch-up testing is done to JESDEC Standard JESD78 which exceeds 500 mA

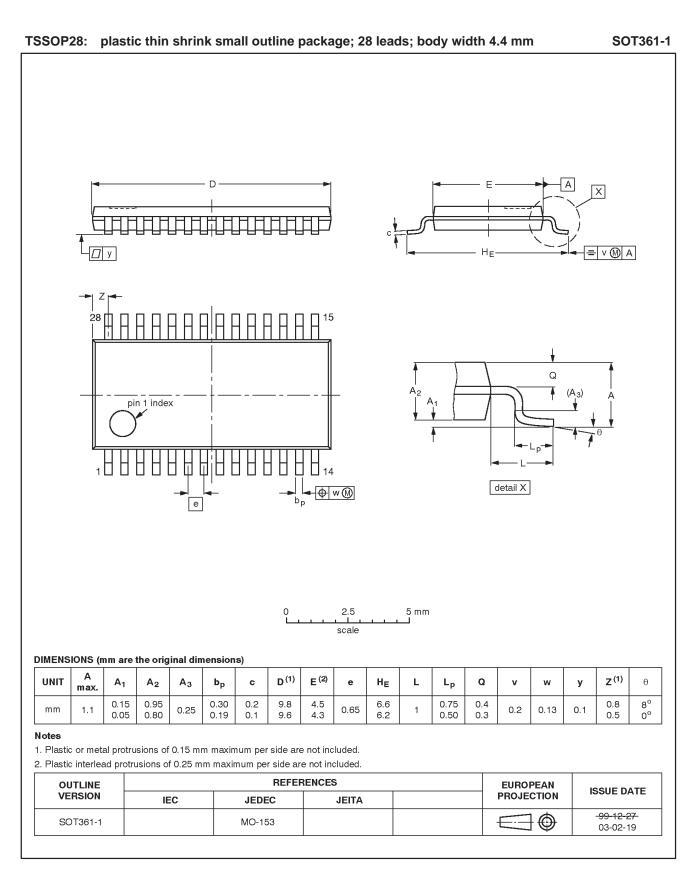

- Package offered: TSSOP28

### DESCRIPTION

The GTL2006 is a 13-bit translator to interface between the 3.3 V LVTTL chip set I/O and the Xeon™ processor GTL–/GTL/GTL+ I/O. The GTL2006 is designed for platform health management in dual processor applications.

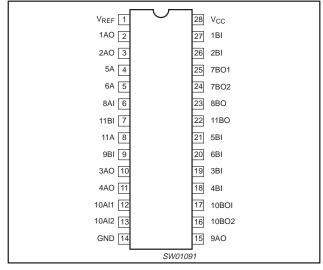

### **PIN CONFIGURATION**

Figure 1. Pin configuration

#### **PIN DESCRIPTION**

| PIN NUMBER           | SYMBOL           | NAME AND FUNCTION                      |

|----------------------|------------------|----------------------------------------|

| 1                    | V <sub>REF</sub> | GTL reference voltage                  |

| 2–6, 8,<br>10–13, 15 | nAn              | Data inputs/outputs<br>(LVTTL)         |

| 7, 9, 16,<br>17–27   | nBn              | Data inputs/outputs<br>(GTL–/GTL/GTL+) |

| 14                   | GND              | Ground (0 V)                           |

| 28                   | V <sub>CC</sub>  | Positive supply voltage                |

#### QUICK REFERENCE DATA

| SYMBOL                               | PARAMETER                                 | CONDITIONS TYPICAL                                  |        | CAL    | UNIT |  |

|--------------------------------------|-------------------------------------------|-----------------------------------------------------|--------|--------|------|--|

| STMBOL                               | PARAMETER                                 | T <sub>amb</sub> = 25 ℃                             | B to A | A to B | UNIT |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>An to Bn or Bn to An | $C_L = 50 \text{ pF}; V_{CC} = 3.3 \text{ V}$       | 5.5    | 5.5    | ns   |  |

| C <sub>I/O</sub>                     | I/O pin capacitance                       | Outputs disabled; $V_{I/O} = 0 V \text{ or } 3.0 V$ | 7.8    | 4.5    | pF   |  |

#### ORDERING INFORMATION

| PACKAGES             | TEMPERATURE RANGE | ORDER CODE | TOPSIDE MARK | DWG NUMBER |  |

|----------------------|-------------------|------------|--------------|------------|--|

| 28-Pin Plastic TSSOP | –40 °C to +85 °C  | GTL2006PW  | GTL2006      | SOT361-1   |  |

Standard packing quantities and other packaging data are available at www.philipslogic.com/packaging.

**Philips Semiconductors**

Product data

## 13-bit GTL-/GTL/GTL+ to LVTTL translator

### GTL2006

### **FUNCTION TABLES**

| INPUT               | OUTPUT              |  | INPUT | OUTPUT |

|---------------------|---------------------|--|-------|--------|

| 1BI/2BI/3BI/4BI/9BI | 1AO/2AO/3AO/4AO/9AO |  | 8AI   | 8BO    |

| L                   | L                   |  | L     | L      |

| Н                   | Н                   |  | Н     | Н      |

| INPUT       | INPUT | OUTPUT      |

|-------------|-------|-------------|

| 10AI1/10AI2 | 9BI   | 10BO1/10BO2 |

| L           | L     | L           |

| L           | Н     | L           |

| Н           | L     | L           |

| Н           | Н     | Н           |

| INPUT   | INPUT/OUTPUT       | OUTPUT         |

|---------|--------------------|----------------|

| 5BI/6BI | 5A/6A (OPEN DRAIN) | 7B01/7B02      |

| L       | L                  | H <sup>1</sup> |

| н       | L <sup>2</sup>     | L              |

| Н       | Н                  | Н              |

| INPUT | INPUT/OUTPUT     | OUTPUT |

|-------|------------------|--------|

| 11BI  | 11A (OPEN DRAIN) | 11BO   |

| L     | н                | L      |

| L     | L <sup>2</sup>   | Н      |

| Н     | L                | Н      |

H = HIGH voltage level

L = LOW voltage level

1. The enable on 7BO1/7BO2 include a delay that prevents the transient condition where 5BI/6BI go from LOW to HIGH, and the LOW to HIGH on 5A/6A lags up to 100 ns from causing a low glitch on the 7BO1/7BO2 outputs.

2. Open Drain Input/Output terminal is driven to logic LOW state by other driver.

NOTES:

**Philips Semiconductors**

Product data

# 13-bit GTL-/GTL/GTL+ to LVTTL translator

GTL2006

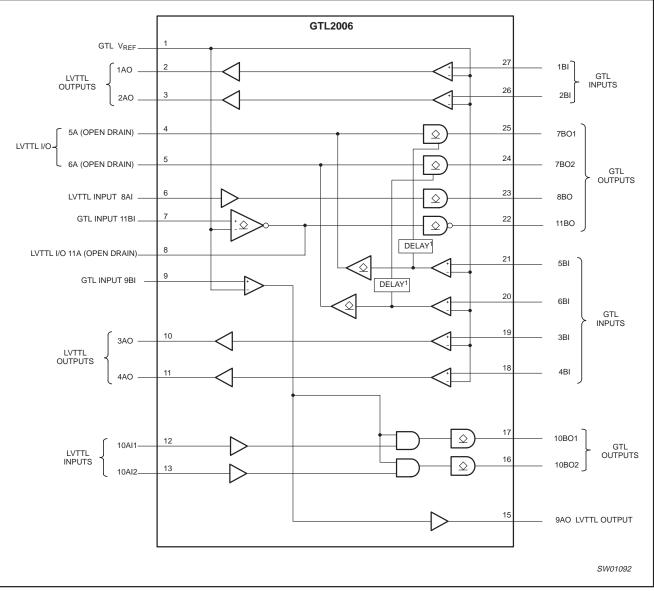

### LOGIC SYMBOL

NOTE:

1. The enable on 7BO1/7BO2 include a delay that prevents the transient condition where 5BI/6BI go from LOW to HIGH, and the LOW to HIGH on 5A/6A lags up to 100 ns from causing a low glitch on the 7BO1/7BO2 outputs.

### Figure 2. Logic symbol

**Philips Semiconductors**

## 13-bit GTL-/GTL/GTL+ to LVTTL translator

### GTL2006

Product data

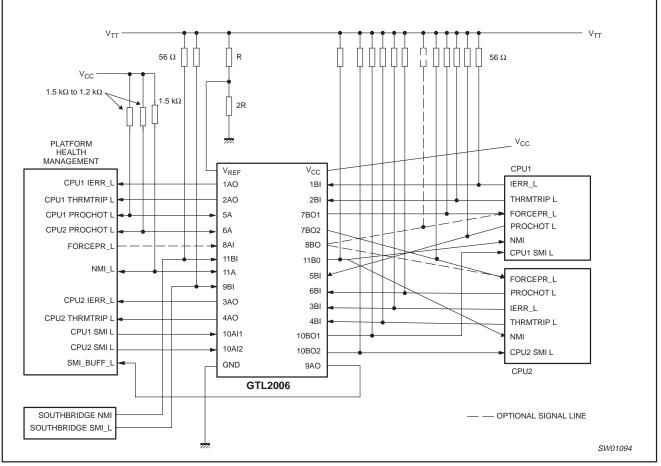

### **APPLICATION INFORMATION**

Figure 3. Application diagram

Philips Semiconductors

Product data

## 13-bit GTL-/GTL/GTL+ to LVTTL translator

GTL2006

#### **Frequently Asked Questions**

**Question 1:** On the GTL2006 LVTTL inputs, specifically 10AI1 and 10AI2, when the GTL2006 is unpowered, these inputs may be pulled up to 3.3 V S/B and we want to make sure that there is no leakage path to the power rail under this condition. Are the LVTTL inputs HIGH Impedance when the device is unpowered and will there be any leakage?

**Answer 1:** When the device is unpowered, the LVTTL inputs will be in a high-impedance state and will not leak to  $V_{DD}$  if they are pulled high while the device is unpowered.

**Question 2:** Do all the LVTTL inputs have the same unpowered characteristic?

Answer 2: Yes.

**Question 3:** What is the condition of the other GTL I/O and LVTTL output pins when the device is unpowered?

**Answer 3:** The open drain outputs, both GTL and LVTTL, will not leak to the power supply if they are pulled high while the device is unpowered. The GTL inputs will also not leak to the power supply under the same conditions. The LVTTL totem pole outputs, however, are not open drain type outputs and there will be current flow on these pins if they are pulled high when V<sub>DD</sub> is at ground.

**Question 4:** When this sequence occurs:

1) Pin 11BI is driven LOW (at time t0)

2) Pin 11A is driven LOW (at time t1)

3) Pin 11BI stops driving LOW (at time t2)

4)Pin 11A stops driving LOW (at time t3)

Are there wired-OR glitches at pin 11BO at time t1 and t2? **Answer 4:** The output of 11BI is physically wired to the 11A pin. There will be no glitch at t1 when the external driver turns on and drives LOW, unless the external driver is a long distance away and the pull-up is a low value. If the pull-up  $R = Z_0$  of the line and the current were equally shared, the bounce would be to  $1/_2$  the pull-up voltage, presumably V<sub>DD</sub>. The input is a  $1/_2$  V<sub>DD</sub> threshold input, so the glitch may propagate to the 11BO. If the glitch is very short it may not propagate, or if the pull-up were higher the amplitude would be too small to propagate, or if the external driver were sinking more than half of the total current, it would not propagate. If the external driver is weak and a long way away you will most likely see a glitch on 11BO, because there will be a large glitch on 11A.

**Question 5:** Can you give us some guideline on how high the pull-up resistor value at pin 11A needs to be to avoid glitches on 11BO?

**Answer 5:** The 11A pin is a TTL pin, generally the pull-up resistor used on TTL pins are chosen to minimize power rather than to match the line impedance. Most line impedances are in the range of 50  $\Omega$ . If the pull-up is  $3 \times Z_0$ , that is 150  $\Omega$ ; even if all the current is being sunk by the GTL2006, the initial bounce on 11A would only be  $1/_3 V_{DD}$ , and would only last for the round trip time to the external driver, provided that the external driver can sink all of the current, the bounce will return LOW. The  $1/_3 V_{DD}$  is not a high level to the GTL2006 11A pin, so no bounce would show up on the 11BO pin. Normal choices for the pull-up on 11A would be in the 1 k $\Omega$  to several k $\Omega$  range, depending on speed and current considerations.

**Question 6:** Please explain the timing specification of Bn to Bn in the AC Characteristics table. Which specific inputs/outputs does it cover, and why is the H > L transition so slow?

**Answer 6:** The Bn to Bn refers to the 4Bl to 7BO1 path and to the 6Bl to 7BO2 path. The times are disable and enable times since a LOW on 5Bl or 6Bl should not be reflected as a LOW on 7BO1 or 7BO2.

The t<sub>PLH</sub> corresponds to the disable time, and the t<sub>PHL</sub> corresponds to the enable time. The enable time is deliberately slow to prevent glitches/false LOWs on the 7BOn outputs, because a LOW on 5BI drives a LOW on 5A, which is an open-drain I/O and may have a slow rise time. And a LOW on 6BI drives a LOW on 6A that is an open-drain I/O that may also have a slow rise time.

**Question 6A:** Now that I try to examine the circuit from the data sheet, I am just a little bit concerned. Let me try to describe the function first:

This circuit is used for monitoring and driving the CPU PROCHOT#.

The monitor device is a Heceta7 part and its output is bi-directional, CPU1\_PROCHOT# and is connected to 5A.

The CPU has an output called PROCHOT#, which goes to 5BI and an input call FRCPROCHOT# that comes from 7BO1.

When the CPU is generating PROCHPT# (5BI), we do not want the CPU input FRCPROCHOT# (7BO1) to also see this signal.

#### Scenario 1: CPU driving PROCHOT#

- 5BI input is HIGH and goes LOW; output 5A is HIGH and goes LOW following 5BI. The output 7BO should stay HIGH.

- 5BI input is LOW and goes HIGH; output 5A is LOW and goes HIGH following 5BI. The output 7BO1 should stay HIGH.

#### Scenario 2: Heceta7 driving CPU1\_PROCHOT#

- 5A input is HIGH and goes LOW; output 7BO1 is HIGH and goes LOW following 5A. The input 5BI should stay HIGH.

- 5A input is LOW and goes HIGH; output 7BO1 is LOW and goes HIGH following 5A. The output 5BI should stay HIGH.

Now I can see the reason for the delay in the enable path so that we keep the output disabled to account for the potentially slow riser time on 5A. In my mind, there should also be a delay block shown in the path 5BI to 5A so that the 5BI H-to-L can disable the driver for 7BO1 before the signal appears on the 5A input/output, thus appearing as an input to the driver for 7BO1.

Have you characterized what sort of glitch you get on the 7BO1 output on an H-to-L transition on 5BI?

**Answer 6A:** The disable for 7BO1 comes directly from the internal 5BI signal, and by design it always disables the LOW on 7BO1 before the LOW on the 5BI can propagate to the 5AI/O and back to the 7BO1.

**Question 7:** Can I operate the GTL2006 at V<sub>TT</sub> of 1.2 V and V<sub>REF</sub> of 0.6 V?

Answer 7: Yes; you can operate V<sub>TT</sub> up to 3.6 V and V<sub>REF</sub> between 0.5 V to 1.8 V at any V<sub>TT</sub> to adjust the high and low noise margins to your application. You don't have to follow the GTL–/GTL/GTL+ specifications. The GTL V<sub>IL</sub> and V<sub>IH</sub> will be 50 mV around V<sub>REF</sub> within the range of 0.5 V to 1.8 V.

Philips Semiconductors

### Product data

# 13-bit GTL-/GTL/GTL+ to LVTTL translator

GTL2006

### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

In accordance with the Absolute Maximum System (IEC 134); voltages are referenced to GND (ground = 0 V).

| SYMBOL              | PARAMETER                                    | CONDITIONS                          | RATING       | UNIT |

|---------------------|----------------------------------------------|-------------------------------------|--------------|------|

| V <sub>CC</sub>     | DC supply voltage                            |                                     | -0.5 to +4.6 | V    |

| I <sub>IK</sub>     | DC input diode current                       | V <sub>1</sub> < 0 V                | -50          | mA   |

| N                   |                                              | A port (LVTTL)                      | -0.5 to +4.6 | V    |

| VI                  | DC input voltage <sup>3</sup>                | B port(GTL)                         | -0.5 to +4.6 | V    |

| I <sub>OK</sub>     | DC output diode current V <sub>O</sub> < 0 V |                                     | -50          | mA   |

| V                   | DC output voltage <sup>3</sup>               | Output in Off or HIGH state; A port | -0.5 to +4.6 | V    |

| Vo                  | DC ouput voitage                             | Output in Off or HIGH state; B port | -0.5 to +4.6 | V    |

|                     | Current into any output in the LOW state     | A port                              | 32           | mA   |

| IOL                 | Current into any output in the LOW state     | B port                              | 30           | mA   |

| I <sub>OH</sub>     | Current into any output in the HIGH state    | A port                              | -32          | mA   |

| T <sub>stg</sub>    | Storage temperature range                    |                                     | -60 to +150  | °C   |

| T <sub>J(MAX)</sub> | Maximum junction temperature                 |                                     | +125         | °C   |

NOTES:

Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

The performance capability of a high-performance integrated circuit in conjunction with its thermal environment can create junction temperatures which are detrimental to reliability. The maximum junction temperature of this integrated circuit should not exceed 150°C.

The input and output negative voltage ratings may be exceeded if the input and output clamp current ratings are observed.

#### RECOMMENDED OPERATING CONDITIONS

| SYMBOL                 | PARAMETER                            | CONDITIONS | MIN                      | TYP                                         | MAX                      | UNIT |  |

|------------------------|--------------------------------------|------------|--------------------------|---------------------------------------------|--------------------------|------|--|

| V <sub>CC</sub>        | Supply voltage                       |            | 3.0                      | 3.3                                         | 3.6                      | V    |  |

|                        |                                      | GTL-       | 0.85                     | 0.9                                         | 0.95                     |      |  |

| V <sub>TT</sub> Termin | Termination voltage                  | GTL        | 1.14                     | 1.2                                         | 1.26                     | V    |  |

|                        | Γ                                    | GTL+       | 1.35                     | 1.5                                         | 1.65                     |      |  |

|                        |                                      | Overall    | 0.5                      | <sup>2</sup> / <sub>3</sub> V <sub>TT</sub> | 1.8                      |      |  |

| M                      |                                      | GTL-       | 0.5                      | 0.6                                         | 0.63                     | N    |  |

| $V_{REF}$              | Supply voltage                       | GTL        | 0.76                     | 0.8                                         | 0.84                     | V    |  |

|                        | Γ                                    | GTL+       | 0.87                     | 1.0                                         | 1.10                     |      |  |

|                        |                                      | A port     | 0                        | 3.3                                         | 3.6                      | v    |  |

| VI                     | Input voltage                        | B port     | 0                        | V <sub>TT</sub>                             | 3.6                      |      |  |

| M                      |                                      | A port     | 2                        | —                                           | —                        | v    |  |

| VIH                    | HIGH-level input voltage             | B port     | V <sub>REF</sub> + 50 mV | _                                           | —                        | v    |  |

| M                      |                                      | A port     | —                        | —                                           | 0.8                      | v    |  |

| VIL                    | LOW-level input voltage              | B port     | —                        | —                                           | V <sub>REF</sub> – 50 mV |      |  |

| I <sub>OH</sub>        | HIGH-level output current            | A port     | —                        | —                                           | -16                      | mA   |  |

|                        |                                      | A port     | _                        | —                                           | 16                       | mA   |  |

| I <sub>OL</sub>        | LOW-level output current             | B port     | —                        | —                                           | 15                       | mA   |  |

| T <sub>amb</sub>       | Operating free-air temperature range |            | -40                      | —                                           | 85                       | °C   |  |

**Philips Semiconductors**

Product data

# 13-bit GTL-/GTL/GTL+ to LVTTL translator

GTL2006

### DC ELECTRICAL CHARACTERISTICS

Over recommended operating conditions. Voltages are referenced to GND (ground = 0 V).

| SYMBOL            | PARAMETER                | TEST CONDITIONS                                                                                                   | -40                  | UNIT             |     |                |  |  |  |

|-------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------|------------------|-----|----------------|--|--|--|

|                   |                          |                                                                                                                   | MIN                  | TYP <sup>1</sup> | MAX |                |  |  |  |

| M                 | A port                   | $V_{CC}$ = 3.0 V to 3.6 V; $I_{OH}$ = -100 $\mu$ A                                                                | V <sub>CC</sub> -0.2 | —                | —   | v              |  |  |  |

| V <sub>OH</sub>   | A port                   | $V_{CC} = 3.0 V_{;} I_{OH} = -16 mA$                                                                              | 2.1                  | —                | —   | ٦ <sup>v</sup> |  |  |  |

| Max               | A port                   | $V_{CC} = 3.0 V_{;} I_{OL} = 16 mA$                                                                               | —                    | —                | 0.8 | v              |  |  |  |

| V <sub>OL</sub>   | B port                   | $V_{CC} = 3.0 V_{;} I_{OL} = 15 mA$                                                                               | —                    | —                | 0.4 | v              |  |  |  |

|                   | Aport                    | $V_{CC} = 3.6 \text{ V}; \text{ V}_{I} = V_{CC}$                                                                  | —                    | —                | ± 1 |                |  |  |  |

| li -              | A port                   | $V_{CC} = 3.6 \text{ V}; \text{ V}_{I} = 0 \text{ V}$                                                             |                      | —                | ± 1 | μA             |  |  |  |

|                   | B port                   | $V_{CC} = 3.6 \text{ V}; \text{ V}_{I} = \text{V}_{TT} \text{ or GND}$                                            | —                    | —                | ± 1 |                |  |  |  |

| I <sub>CC</sub>   | A or B port              | $V_{CC} = 3.6 \text{ V}; \text{V}_{\text{I}} = \text{V}_{CC} \text{ or GND}; \text{ I}_{\text{O}} = 0 \text{ mA}$ | —                    | —                | 12  | mA             |  |  |  |

| $\Delta l_{CC}^3$ | A port or control inputs | $V_{CC} = 3.6 \text{ V}; \text{ V}_{I} = V_{CC} - 0.6 \text{ V}$                                                  | _                    | —                | 500 | μΑ             |  |  |  |

| 0                 | A port                   | V <sub>O</sub> = 3.0 V or 0 V                                                                                     | —                    | 7.8              | —   | ~ 5            |  |  |  |

| C <sub>IO</sub>   | B port                   | $V_{O} = V_{TT} \text{ or } 0 \text{ V}$                                                                          | —                    | 4.5              | —   | pF             |  |  |  |

NOTES:

All typical values are measured at V<sub>CC</sub> = 3.3 V and T<sub>amb</sub> = 25 °C.

The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

This is the increase in supply current for each input that is at the specified LVTTL voltage level rather than V<sub>CC</sub> or GND.

### AC CHARACTERISTICS (3.3 V ± 0.3 V RANGE)

|                                        |                    |   | LIN      | /ITS (GT                          | L)        | LIMITS (GTL) |                                   |           | LIMITS (GTL+) |                                   |           |      |

|----------------------------------------|--------------------|---|----------|-----------------------------------|-----------|--------------|-----------------------------------|-----------|---------------|-----------------------------------|-----------|------|

| SYMBOL                                 | PARAMETER WAVEFORM |   |          | = 3.3 V ±<br><sub>REF</sub> = 0.6 |           |              | = 3.3 V ±<br><sub>REF</sub> = 0.8 |           |               | = 3.3 V ±<br><sub>REF</sub> = 1.0 |           | UNIT |

|                                        |                    |   | MIN      | TYP <sup>1</sup>                  | MAX       | MIN          | TYP <sup>1</sup>                  | MAX       | MIN           | TYP <sup>1</sup>                  | MAX       |      |

| t <sub>PLH</sub><br>t <sub>PHL</sub>   | An to Bn           | 1 | 2<br>2   | 4<br>5.5                          | 8<br>10   | 2<br>2       | 4<br>5.5                          | 8<br>10   | 2<br>2        | 4<br>5.5                          | 8<br>10   | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub>   | Bn to An           | 2 | 2<br>2   | 5.5<br>5.5                        | 10<br>10  | 2<br>2       | 5.5<br>5.5                        | 10<br>10  | 2<br>2        | 5.5<br>5.5                        | 10<br>10  | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub>   | 9BI to 10BOn       |   | 2<br>2   | 6<br>6                            | 11<br>11  | 2<br>2       | 6<br>6                            | 11<br>11  | 2<br>2        | 6<br>6                            | 11<br>11  | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> 2 | 11BI to 11BO       |   | 2<br>2   | 8<br>14                           | 13<br>21  | 2<br>2       | 8<br>14                           | 13<br>21  | 2<br>2        | 8<br>14                           | 13<br>21  | ns   |

| t <sub>PLZ</sub><br>t <sub>PZH</sub>   | Bn to An (I/O)     | 3 | 2<br>2   | 5<br>5                            | 10<br>10  | 2<br>2       | 5<br>5                            | 10<br>10  | 2<br>2        | 5<br>5                            | 10<br>10  | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub>   | Bn to Bn           | 3 | 4<br>120 | 7<br>205                          | 11<br>350 | 4<br>120     | 7<br>205                          | 11<br>350 | 4<br>120      | 7<br>205                          | 11<br>350 | ns   |

NOTES:

All typical values are at V<sub>CC</sub> = 3.3 V and T<sub>amb</sub> = 25 °C.

Includes ~7.6 ns RC rise time of test load pull-up on 11A, 1.5 kΩ pull-up and 21 pF load on 11A has about 23 ns RC rise time.

**Philips Semiconductors**

## 13-bit GTL-/GTL/GTL+ to LVTTL translator

# GTL2006

Product data

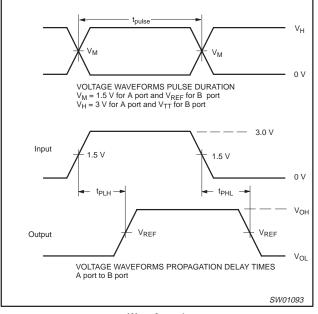

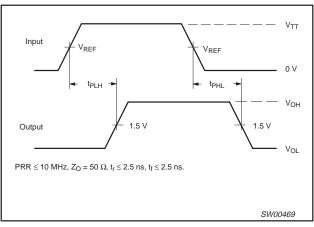

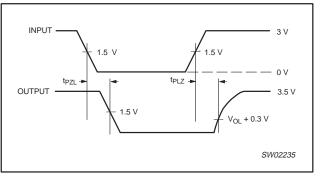

### AC WAVEFORMS

$V_M$  = 1.5 V at  $V_{CC} \geq$  3.0 V for A ports;  $V_M$  =  $V_{REF}$  for B ports

Waveform 1.

Waveform 3.

**Philips Semiconductors**

# 13-bit GTL-/GTL/GTL+ to LVTTL translator

### GTL2006

Product data

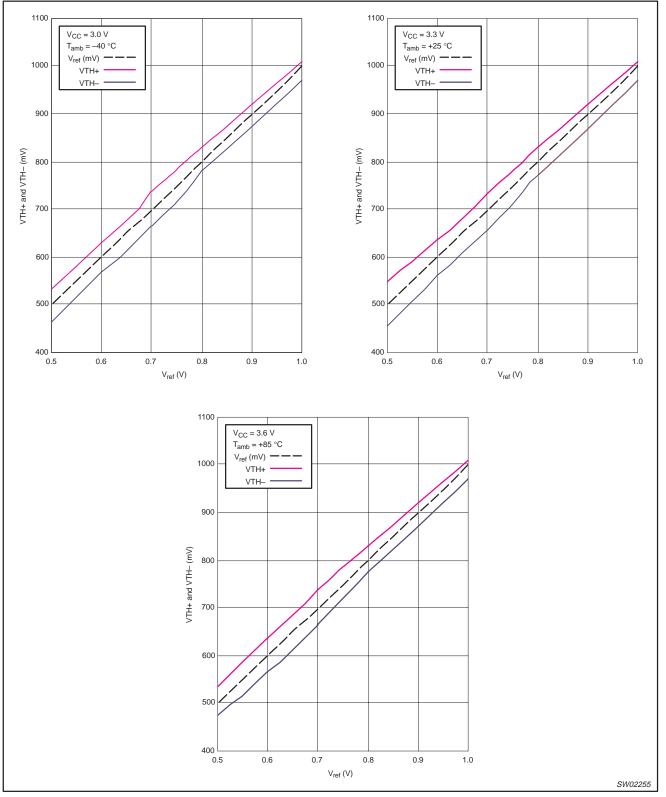

### PERFORMANCE CURVES

Figure 4. GTL  $V_{TH+}$  and  $V_{TH-}$  versus  $V_{REF}$

### Distributor of NXP Semiconductors/Freescale Semiconductor, Inc. : Excellent Integrated 3 Datasheet of GTL2006PW,118 - IC XLATR GTL/LVTTL 13BIT 28TSSOP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

Philips Semiconductors

## 13-bit GTL-/GTL/GTL+ to LVTTL translator

# GTL2006

Product data

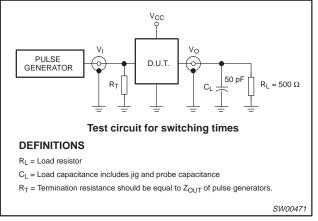

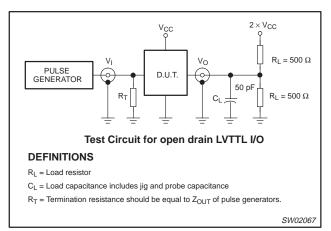

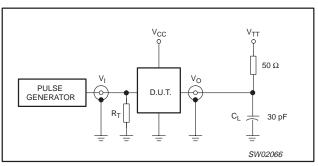

### **TEST CIRCUIT**

Figure 5. Load circuitry for A outputs

Figure 6. Load circuitry for open drain LVTTL I/O

Figure 7. Load circuit for B outputs

**Philips Semiconductors**

Product data

# 13-bit GTL-/GTL/GTL+ to LVTTL translator

Philips Semiconductors

Product data

# 13-bit GTL-/GTL/GTL+ to LVTTL translator

## GTL2006

### **REVISION HISTORY**

| Rev | Date     | Description                                                                                                                |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------|

| _2  | 20040621 | Product data (9397 750 13063). Supersedes data of 2003 Dec 18.                                                             |

|     |          | Modifications:                                                                                                             |

|     |          | • All figures numbered.                                                                                                    |

|     |          | • Figure 2, "Logic symbol" modified.                                                                                       |

|     |          | • Page 6, Frequently asked Questions: add questions/answers 4, 5, 6, 6A, and 7.                                            |

|     |          | • Page 8, AC Characteristics (3.3 V ± 0.3 Range); t <sub>PHL</sub> An to Bn, GTL+ maximum: change from '1. ns' to '10 ns'. |

|     |          | • Add "Performance curves" section on page 10.                                                                             |

| _1  | 20031218 | Product data (9397 750 12562); ECN 853-2440 01-A14985 dated 15 December 2003.                                              |

**Philips Semiconductors**

Product data

## 13-bit GTL-/GTL/GTL+ to LVTTL translator

## GTL2006

#### Data sheet status

| Level | Data sheet status <sup>[1]</sup> | Product<br>status <sup>[2] [3]</sup> | Definitions                                                                                                                                                                                                                                                                                    |

|-------|----------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I     | Objective data                   | Development                          | This data sheet contains data from the objective specification for product development.<br>Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                 |

| II    | Preliminary data                 | Qualification                        | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.             |

| 111   | Product data                     | Production                           | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). |

[1] Please consult the most recently issued data sheet before initiating or completing a design.

[2] The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

[3] For data sheets describing multiple type numbers, the highest-level product status determines the data sheet status.

#### Definitions

Short-form specification — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### Disclaimers

Life support — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes in the products—including circuits, standard cells, and/or software—described or contained herein in order to improve design and/or performance. When the product is in full production (status 'Production'), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right to the specified.

#### **Contact information**

For additional information please visit http://www.semiconductors.philips.com. Fax: +31 40 27 24825

© Koninklijke Philips Electronics N.V. 2004 All rights reserved. Printed in U.S.A.

For sales offices addresses send e-mail to: sales.addresses@www.semiconductors.philips.com

Document order number:

Date of release: 06-04 9397 750 13063

Let's make things better.