January 2006

# **The Programmable Solutions Company**

Altera's success is built on a commitment to innovation exemplified by the invention of the world's first reprogrammable logic device over twenty years ago. Our latest product portfolio combines the inherent value of programmable logic—flexibility and time-to-market advantages—with higher levels of performance and integration. It was specifically developed to address the wide range of today's system needs. Altera's programmable solutions include:

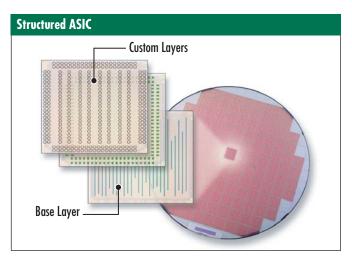

- The industry's most advanced FPGA, CPLD, and structured ASIC technologies

- Customizable embedded processors

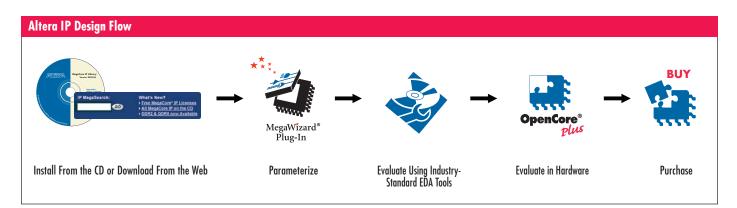

- Optimized intellectual property (IP) cores

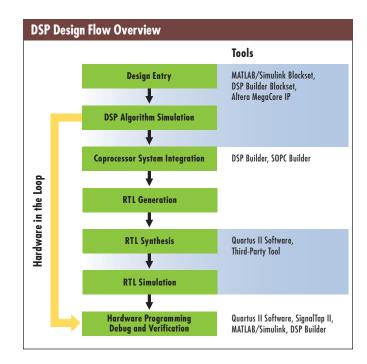

- A fully integrated software development tool

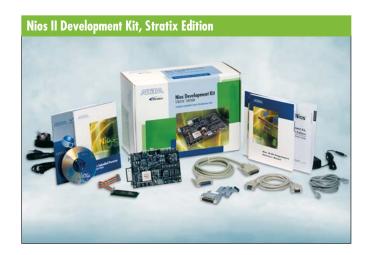

- Off-the-shelf development kits

For more information about Altera® products, please go to www.altera.com. If you have feedback on this catalog, please email us at catalog@altera.com.

### **Contents**

| MAX CPLD Series                  | 4  |

|----------------------------------|----|

| Cyclone Low-Cost FPGA Series     | 7  |

| Stratix High-Density FPGA Series | 10 |

| HardCopy Structured ASIC Series  | 16 |

| Nios II Embedded Processors      | 19 |

| Intellectual Property Solutions  | 21 |

| Quartus II Design Software       | 29 |

| Development Kits                 |    |

| Training                         | 35 |

| Package Matrix                   |    |

| Ordering Codes                   | 38 |

| Product Websites & Information   | 39 |

### **MAX CPLD Series**

The industry-leading MAX® series of CPLDs are world-class, low-cost solutions for a wide variety of digital applications. Instant-on MAX CPLDs represent the ultimate in flexibility, as they can be independent programmable solutions or complement other semi-conductors in a system. MAX CPLDs are non-volatile, single-chip solutions that do not require additional configuration devices. This means that they can be preprogrammed and reprogrammed using in-system programmability (ISP) and will retain the programming algorithm securely, even when the device is powered off.

#### **Key Features**

- Low cost

- Low power

- Instant-on and non-volatile

- ISF

- Free Quartus® II Web Edition software support

### MAX®II

#### The Lowest-Cost CPLD Ever

MAX II devices are based on a ground-breaking new CPLD architecture that delivers the lowest cost per I/O pin of any CPLD family. MAX II devices deliver one-tenth the power, four times the density, and twice the performance of previous MAX devices at half the cost. This instant-on, non-volatile device family targets general-purpose control logic applications. In addition to delivering the lowest cost for traditional CPLD designs, MAX II devices drive cost

and power improvements to higher densities, enabling you to use these devices in place of higher-cost or higher-power ASSPs and standard logic devices.

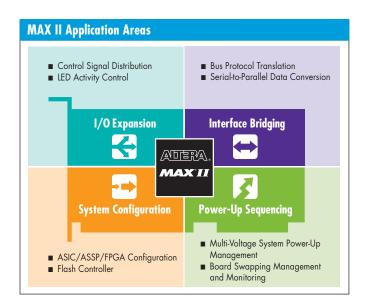

MAX II CPLDs optimally support four key applications: I/O expansion, interface bridging, system configuration, and power-up sequencing.

| MAX II Family Features Summary            |                                                                                                                           |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Cost-Optimized Architecture               | Delivers four times the density at half the price of competing CPLDs with the revolutionary MAX II architecture.          |

| Low Power                                 | Reduces power consumption and increases system reliability.                                                               |

| Highest-Density CPLDs                     | Implements more applications in a single, low-cost device.                                                                |

| Non-Volatile and Instant-On Functionality | Reduces system cost and board space with a single-chip solution.                                                          |

| User Flash Memory                         | Minimizes system cost and chip count by integrating discrete serial or parallel non-volatile storage onto MAX II devices. |

| Real-Time ISP                             | Reduces maintenance costs by enabling updates while the device is in operation.                                           |

| MultiVolt™ Core                           | Operates with a 1.8-, 2.5-, or 3.3-V power supply, minimizing power rails and simplifying board design.                   |

| MultiVolt I/O Interface                   | Interfaces seamlessly to other devices at 1.5-, 1.8-, 2.5-, or 3.3-V logic levels.                                        |

| Parallel Flash Loader                     | Simplifies board management by using MAX II devices to configure external non-JTAG-compliant flash devices.               |

## **General-Purpose CPLDs**

Altera's 3.3-V MAX 3000A devices are cost-optimized for high-volume applications, while the 5.0-, 3.3-, and 2.5-V MAX 7000 families offer world-class, high-performance solutions for a broad array of applications. The non-volatile, EEPROM-based MAX 3000A and MAX 7000 families provide instant-on capability and offer densities from 32 to 512 macrocells. These devices support ISP and can be easily reconfigured in the field.

| MAX 3000A Family Features                           |                                                                     |

|-----------------------------------------------------|---------------------------------------------------------------------|

| Low Price per Macrocell                             | Ideal for low-cost, high-volume applications.                       |

| 4.5-ns Propagation Delays                           | Provides fast system performance.                                   |

| 5.0-V Tolerant I/O Pins                             | Inherently interfaces to 5.0-V devices.                             |

| Commercial and Industrial Temperature               | Reduces overall system cost for temperature-sensitive applications. |

| MAX 7000 Family Features                            |                                                                     |

| 4.5-ns Propagation Delays                           | Provides fast system performance.                                   |

| Support for Advanced I/O Standards                  | Supports GTL+ and SSTL-2/-3 I/O standards (MAX 7000B CPLDs).        |

| Programmable Power-Saving Mode                      | Reduces power consumption by over 50 percent.                       |

| Commercial, Industrial, and Extended<br>Temperature | Provides support for all environmental conditions.                  |

| MAX CPLD Series Package & I/O Matrix                                                                                                                                                                                                                                                 |                         |                     |                     |                      |                      |                    |                    | <b>AX 300</b><br>3.3 V | X 3000A MAX 7000AE 3.3 V |            |                    |                    |                    |                    |                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------------------|---------------------|----------------------|----------------------|--------------------|--------------------|------------------------|--------------------------|------------|--------------------|--------------------|--------------------|--------------------|-------------------|

| 36 Number indicates available user I/O pins.  Vertical migration (Same V <sub>CC</sub> , GND, ISP, and input pins). User I/O may be less than labelled for vertical migration.  All MAX series devices are offered in commercial and industrial temperatures and lead-free packages. |                         | EPM240/G            | EPM570/G            | EPM1270/G            | EPM2210/G            | EPM3032A           | EPM3064A           | EPM3128A               | EPM3256A                 | EPM3512A   | EPM7032AE          | EPM7064AE          | EPM7128AE          | EPM7256AE          | EPM7512AE         |

| Density & Speed                                                                                                                                                                                                                                                                      | Macrocells <sup>1</sup> | 192                 | 440                 | 980                  | 1,700                | 32                 | 64                 | 128                    | 256                      | 512        | 32                 | 64                 | 128                | 256                | 512               |

|                                                                                                                                                                                                                                                                                      | Logic Elements (LEs)    | 240                 | 570                 | 1,270                | 2,210                | _                  | _                  | _                      | _                        | _          | _                  | _                  | _                  | _                  | _                 |

|                                                                                                                                                                                                                                                                                      | Pin-to-Pin Delay (ns)   | 4.7,<br>6.2,<br>7.6 | 5.5,<br>7.1,<br>8.8 | 6.3,<br>8.2,<br>10.1 | 7.1,<br>9.2,<br>11.3 | 4.5,<br>7.5,<br>10 | 4.5,<br>7.5,<br>10 | 5.0,<br>7.5,<br>10     | 7.5,<br>10               | 7.5,<br>10 | 4.5,<br>7.5,<br>10 | 4.5,<br>7.5,<br>10 | 5.0,<br>7.5,<br>10 | 5.5,<br>7.5,<br>10 | 7.5,<br>10,<br>12 |

| PLCC <sup>2</sup> (L)                                                                                                                                                                                                                                                                | 44-Pin                  |                     |                     |                      |                      | 34                 | 34                 |                        |                          |            | 36                 | 36                 |                    |                    |                   |

|                                                                                                                                                                                                                                                                                      | 84-Pin                  |                     |                     |                      |                      |                    |                    |                        |                          |            |                    |                    | 68                 |                    |                   |

| TQFP <sup>3</sup> (T)                                                                                                                                                                                                                                                                | 44-Pin                  |                     |                     |                      |                      | 34                 | 34                 |                        |                          |            | 36                 | 36                 |                    |                    |                   |

|                                                                                                                                                                                                                                                                                      | 100-Pin                 | 80                  | 76                  |                      |                      |                    | 66                 | 80                     |                          |            |                    | 68                 | 84                 | 84                 |                   |

|                                                                                                                                                                                                                                                                                      | 144-Pin                 |                     | 116                 | 116                  |                      |                    |                    | 96                     | 116                      |            |                    |                    | 100                | 120                | 120               |

| PQFP <sup>4</sup> (Q)                                                                                                                                                                                                                                                                | 208-Pin                 |                     |                     |                      |                      |                    |                    |                        | 158                      | 172        |                    |                    |                    | 164                | 172               |

| BGA <sup>5</sup> (B)                                                                                                                                                                                                                                                                 | 256-Pin                 |                     |                     |                      |                      |                    |                    |                        |                          |            |                    |                    |                    |                    | 212               |

| FBGA <sup>6</sup> (F)                                                                                                                                                                                                                                                                | 100-Pin                 |                     |                     |                      |                      |                    |                    |                        |                          |            |                    | 68                 | 84                 | 84                 |                   |

|                                                                                                                                                                                                                                                                                      | 256-Pin                 |                     | 160                 | 212                  | 204                  |                    |                    | 98                     | 161                      | 208        |                    |                    | 100                | 164                | 212               |

|                                                                                                                                                                                                                                                                                      | 324-Pin                 |                     |                     |                      | 272                  |                    |                    |                        |                          |            |                    |                    |                    |                    |                   |

$<sup>^{\</sup>rm 1}$  Typical equivalent macrocells for MAX II devices.

<sup>&</sup>lt;sup>2</sup> Plastic J-Lead Chip Carrier

<sup>3</sup> Thin Quad Flat Pack

<sup>&</sup>lt;sup>4</sup> Plastic Quad Flat Pack

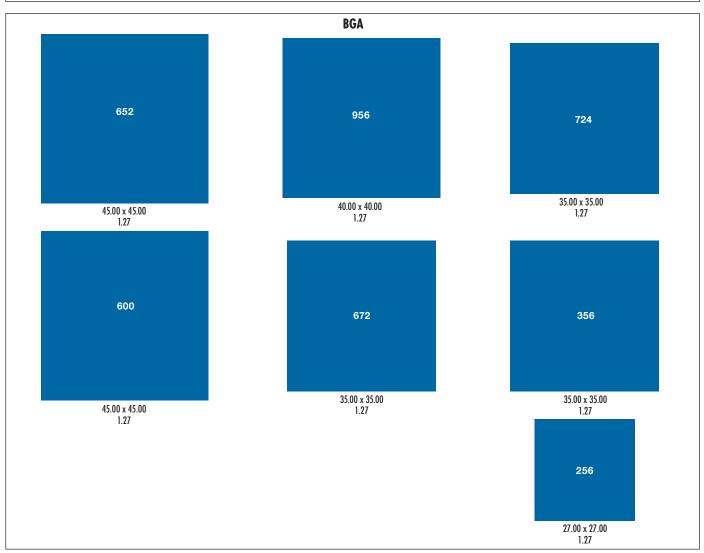

<sup>5</sup> Ball-Grid Array (1.27 mm)

<sup>6</sup> FineLine BGA® (1.0 mm)

|                            | X CPLD<br>ies Features                                    | <b>MAX II</b><br>3.3 V, 2.5 V, 1.8 V |           |           |           |          | MAX 3000A<br>3.3 V |          |          |          |           |           | <b>MAX 7000AE</b><br>3.3 V |           |           |  |  |  |

|----------------------------|-----------------------------------------------------------|--------------------------------------|-----------|-----------|-----------|----------|--------------------|----------|----------|----------|-----------|-----------|----------------------------|-----------|-----------|--|--|--|

|                            |                                                           | EPM240/G                             | EPM570/G  | EPM1270/G | EPM2210/6 | EPM3032A | EPM3064A           | EPM3128A | EPM3256A | EPM3512A | EPM7032AE | EPM7064AE | EPM7128AE                  | EPM7256AE | EPM7512AE |  |  |  |

|                            | User Flash Memory (Kbit)                                  |                                      |           | }         |           |          |                    | _        | l        |          |           |           | _                          |           |           |  |  |  |

|                            | Boundary Scan JTAG                                        |                                      | •         | /         |           |          |                    | 1        |          |          |           |           | 1                          |           |           |  |  |  |

|                            | JTAG ISP                                                  |                                      |           | /         |           |          |                    | 1        |          |          |           |           | 1                          |           |           |  |  |  |

|                            | Fast Input Registers                                      |                                      |           | /         |           |          |                    | -        |          |          |           |           | 1                          |           |           |  |  |  |

|                            | Programmable Register Power-Up                            |                                      | •         | /         |           |          |                    | -        |          |          |           |           | ✓                          |           |           |  |  |  |

| L GS                       | Programmable Ground Pins                                  |                                      |           | /         |           |          |                    | -        |          |          |           |           | 1                          |           |           |  |  |  |

| Features                   | Open-Drain Outputs                                        |                                      |           | /         |           |          |                    | 1        |          |          |           |           | /                          |           |           |  |  |  |

| -                          | Programmable Pull-Up Resistors                            |                                      |           | /         |           |          |                    | -        |          |          | -         |           |                            |           |           |  |  |  |

|                            | Bus Hold                                                  |                                      | •         | /         |           |          |                    | -        |          |          | -         |           |                            |           |           |  |  |  |

|                            | Parallel Flash Loader                                     |                                      | •         | /         |           |          |                    | -        |          |          | -         |           |                            |           |           |  |  |  |

|                            | Real-Time ISP                                             |                                      | •         | ✓         |           |          |                    | -        |          |          | _         |           |                            |           |           |  |  |  |

|                            | Core Voltage (V)                                          |                                      | 1.8       |           |           |          |                    | 3.3      |          |          | 3.3       |           |                            |           |           |  |  |  |

|                            | MultiVolt Core (V)                                        | 3.3, 2.5, 1.8                        |           |           |           | _        |                    |          |          |          |           |           | _                          |           |           |  |  |  |

|                            | MultiVolt I/O (V)                                         |                                      | 3.3, 2.5, | 1.8, 1.5  |           |          | 5.0, 3.3, 2.5      |          |          |          |           | .5        |                            |           |           |  |  |  |

| OHS                        | I/O Power Banks                                           | 2                                    | 2         | 4         | 4         |          |                    | 1        |          |          |           |           | 1                          |           |           |  |  |  |

| 9<br>F                     | Maximum I/O Pins                                          | 80                                   | 160       | 212       | 272       | 34       | 66                 | 98       | 161      | 208      | 34        | 68        | 100                        | 164       | 212       |  |  |  |

| 2                          | Maximum Output Enables                                    | 80                                   | 160       | 212       | 272       | 6        | 6                  | 6        | 6        | 10       | 6         | 6         | 6                          | 6         | 10        |  |  |  |

| Core Voltage & 1/0 Options | Transistor-to-Transistor Logic (TTL)<br>(5.0-V Tolerance) | 1                                    |           |           |           |          | ✓                  |          |          |          |           | 1         |                            |           |           |  |  |  |

| No.                        | LVTTL/LVCMOS                                              | /LVCMOS /                            |           |           |           |          | ✓                  |          |          |          |           | ✓         |                            |           |           |  |  |  |

| Gee                        | 32-Bit, 66-MHz PCI Compliant                              | -                                    | _         | 1         | 1         |          |                    | -        |          |          |           |           | -                          |           |           |  |  |  |

|                            | Schmitt Triggers                                          |                                      | •         | /         |           |          |                    | -        |          |          |           |           | _                          |           |           |  |  |  |

|                            | Programmable Slew Rate                                    |                                      | •         | /         |           |          |                    | ✓        |          |          | ✓         |           |                            |           |           |  |  |  |

|                            | Programmable Drive Strength                               |                                      | •         | /         |           |          |                    |          |          |          |           |           |                            |           |           |  |  |  |

$<sup>^{\</sup>rm 1}$  An external series resistor must be used for 5.0-V tolerance.

FOR MORE INFORMATION

MAX II CPLDs www.altera.com/max2 MAX 3000A CPLDs www.altera.com/products/devices/max3k MAX 7000 CPLDs www.altera.com/products/devices/max7k

# **Cyclone Low-Cost FPGA Series**

Altera forever changed the FPGA industry with the introduction of the Cyclone™ device family in 2002—bringing to market the first and only FPGA family designed from the ground up for the lowest cost, with each family member individually optimized for minimum die size. The Cyclone FPGA series—including the 90-nm Cyclone II and 130-nm Cyclone families—delivers a customer-defined feature set, industry-leading performance, and the lowest power consumption available. Competitive with ASICs and ASSPs, the Cyclone series gives you a high-volume solution for cost-sensitive applications.

#### **Key Features**

- The industry's lowest-cost FPGAs

- One-half the power consumption of competing FPGAs

- High-performance digital signal processing (DSP)

- Low-cost embedded processing

- Free Quartus II Web Edition software support

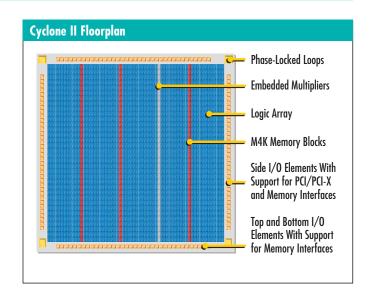

#### 90-nm Low-Cost FPGAs

The Cyclone II FPGA family is the second-generation family in the Cyclone series of low-cost FPGAs. Based on the 1.2-V, 90-nm, low-k dielectric process from TSMC, the Cyclone II FPGA family offers you more benefits than its predecessor, plus more density and features at dramatically lower costs. Cyclone II FPGAs include

dedicated DSP circuitry for very low-cost DSP solutions. In addition, when implementing Nios® II embedded processors on Cyclone II FPGAs, you can create cost-effective processing solutions for price-sensitive and compute-intensive applications.

| Cyclone II Family Features Summary                     |                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cost-Optimized Architecture                            | Offers from 4,608 to 68,416 LEs—three-and-a-half times the density of first-generation Cyclone FPGAs—and the lowest cost per LE.                                                                                                                                                                                                                                                       |

| Embedded Memory                                        | Up to 1.1 Mbits of RAM via 4,608-bit memory blocks capable of 250-MHz performance that support multiple configurations, including true dual-port and single-port RAM, ROM, and first-in first-out (FIFO) buffers.                                                                                                                                                                      |

| Embedded Multipliers                                   | 150 18-bit x 18-bit embedded multipliers running at 250 MHz that can implement common DSP functions such as finite impulse response (FIR) filters and fast Fourier transforms (FFTs). Each 18-bit x 18-bit multiplier can be configured as two independent 9-bit x 9-bit multipliers.                                                                                                  |

| Nios II Embedded Processor Support                     | Nios II embedded processors offer an ideal replacement for low-cost discrete microprocessors to reduce cost and increase flexibility. Nios II soft processor support for Cyclone II FPGAs offers over 100-DMIPS performance.                                                                                                                                                           |

| Differential and Single-Ended I/O<br>Standards Support | Support for LVTTL, LVCMOS, PCI, PCI-X, PCI Express <sup>1</sup> , SSTL, and high-speed transceiver logic (HSTL) single-ended I/O standards. Differential signaling support for LVDS (805 Mbps receiving and 640 Mbps transmitting), mini-LVDS, reduced swing differential signaling (RSDS), LVPECL, SSTL, and HSTL system interfaces.                                                  |

| External Memory Interfaces                             | Dedicated interfaces supporting external memory devices at 167 MHz for integration with external SDR, DDR, DDR2 SDRAM, and QDRII SRAM devices. Altera offers DDR, DDR2, and QDRII memory controller MegaCore® functions free with Quartus II software subscriptions.                                                                                                                   |

| Clock Management Circuitry                             | 16 low-skew, global clock networks span the entire device, fed by 16 dedicated input clock pins. Four phase-locked loops (PLLs), each with three output taps, feature programmable bandwidth, programmable duty cycle, spread-spectrum clocking, lock detection, and frequency synthesis with phase-shifting capabilities, provides complete system clock management on- and off-chip. |

| On-Chip Termination                                    | Single-ended on-chip termination support for driver impedance matching and series termination eliminates the need for external resistors, improves signal integrity, and simplifies board design.                                                                                                                                                                                      |

| Hot-Socketing and Power Sequencing                     | Robust on-chip hot-socketing and power-sequencing support that ensures proper device operation independent of the power-up sequence.                                                                                                                                                                                                                                                   |

| Automatic SEU Detection Circuitry                      | Features automatic single event upset (SEU) detection circuitry utilizing 32-bit cyclic redundancy check (CRC).                                                                                                                                                                                                                                                                        |

<sup>&</sup>lt;sup>1</sup> Requires external PHY device.

### 130-nm Low-Cost FPGAs

Based on extensive input from hundreds of customers like you, the Cyclone FPGA family was built from the ground up for the lowest cost. Cyclone devices provide application-focused features such as embedded memory, external memory interfaces, and clock management circuitry at price points optimal for high-volume applications.

| Cyclone Family Features Summary                  |                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cost-Optimized Architecture                      | Offers from 2,910 to 20,060 LEs; built for low cost.                                                                                                                                                                                                                                                                               |

| Embedded Memory                                  | 288 Kbits of RAM through 4,608-bit memory blocks that can be configured to support a wide range of operation modes including RAM, ROM, FIFO buffers, and single-port and dual-port modes.                                                                                                                                          |

| Nios II Embedded Processor Support               | Nios II embedded processors offer an ideal replacement for low-cost discrete microprocessors to reduce cost and increase flexibility.                                                                                                                                                                                              |

| Single-Ended I/O Support                         | Supports a variety of single-ended I/O interface standards, such as the 3.3-V, 2.5-V, 1.8-V, LVTTL, LVCMOS, SSTL, and PCI standards needed for today's systems.                                                                                                                                                                    |

| External Memory Interfaces                       | Dedicated external memory interfaces that allow you to integrate external SDR and DDR SDRAM devices into complex system designs without degrading data access performance.                                                                                                                                                         |

| Differential I/O Support                         | Support for 129 LVDS and RSDS channels with 640-Mbps LVDS data rates and 311-Mbps RSDS data rates.                                                                                                                                                                                                                                 |

| Clock Management Circuitry                       | Features up to two programmable PLLs and eight global clock lines that provide robust clock management and frequency synthesis capabilities enabling on- and off-chip system clock management. PLLs offer advanced features such as frequency synthesis, programmable phase shift, programmable delays, and external clock output. |

| Hot Socketing and Power Sequencing               | Robust on-chip hot-socketing and power-sequencing support that ensures that Cyclone devices operate no matter how the system is powered up.                                                                                                                                                                                        |

| Automatic Single Event Upset Detection Circuitry | Automatic single event upset detection circuitry utilizing 32-bit CRC to minimize radiation problems.                                                                                                                                                                                                                              |

| Cyclone FPGA Series Package & I/O Matrix                                                                                                                                                                                                                                              |              |       | Cyclone II (1.2 V)  Low Cost, High Volume  Cyclone (1.5 V)  Low Cost, High Volume |        |        |        |        |     |       |       |        |        |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|-----------------------------------------------------------------------------------|--------|--------|--------|--------|-----|-------|-------|--------|--------|--|

| Number indicates available user I/O pins.  Vertical migration (Same V <sub>CC</sub> , GND, ISP, and input pins). User I/O may be less than labelled for vertical migration.  All Cyclone series devices are offered in commercial and industrial temperatures and lead-free packages. |              | EP2C5 | EP2C8                                                                             | EP2C20 | EP2C35 | EP2C50 | EP2C70 | PIG | EP104 | EP106 | EP1C12 | EP1C20 |  |

| Thin Quad Flat Pack (T)                                                                                                                                                                                                                                                               | 100-Pin TQFP |       |                                                                                   |        |        |        |        | 65  |       |       |        |        |  |

|                                                                                                                                                                                                                                                                                       | 144-Pin TQFP | 89    | 85                                                                                |        |        |        |        | 104 |       | 98    |        |        |  |

| Plastic Quad Flat Pack (Q)                                                                                                                                                                                                                                                            | 208-Pin PQFP | 142   | 138                                                                               |        |        |        |        |     |       |       |        |        |  |

|                                                                                                                                                                                                                                                                                       | 240-Pin PQFP |       |                                                                                   | 142    |        |        |        |     |       | 185   | 173    |        |  |

| FineLine BGA (F)                                                                                                                                                                                                                                                                      | 256-Pin FBGA | 158   | 182                                                                               | 152    |        |        |        |     |       | 185   | 185    |        |  |

|                                                                                                                                                                                                                                                                                       | 324-Pin FBGA |       |                                                                                   |        |        |        |        |     | 249   |       | 249    | 233    |  |

|                                                                                                                                                                                                                                                                                       | 400-Pin FBGA |       |                                                                                   |        |        |        |        |     | 301   |       |        | 301    |  |

| 484-Pin FBGA 484-Pin UFBGA 672-Pin FBGA                                                                                                                                                                                                                                               |              |       |                                                                                   | 315    | 322    | 294    |        |     |       |       |        |        |  |

|                                                                                                                                                                                                                                                                                       |              |       |                                                                                   |        | 322    | 294    |        |     |       |       |        |        |  |

|                                                                                                                                                                                                                                                                                       |              |       |                                                                                   |        | 475    | 450    | 422    |     |       |       |        |        |  |

|                                                                                                                                                                                                                                                                                       | 896-Pin FBGA |       |                                                                                   |        |        |        | 622    |     |       |       |        |        |  |

<sup>&</sup>lt;sup>1</sup> Ultra FineLine BGA

| Cyclone FPGA Series Features  |                                                       |                           |                                                                  | <b>Cyclone I</b><br>Low Cost, H | <b>I (1.2 V)</b><br>igh Volume | Cyclone (1.5 V)<br>Low Cost, High Volume |          |         |                               |               |              |            |

|-------------------------------|-------------------------------------------------------|---------------------------|------------------------------------------------------------------|---------------------------------|--------------------------------|------------------------------------------|----------|---------|-------------------------------|---------------|--------------|------------|

|                               |                                                       | EP2C5                     | EP2C8                                                            | EP2C20                          | EP2C35                         | EP2C50                                   | EP2C70   | EP1G3   | EP1C4                         | EP1C6         | EP1C12       | EP1C20     |

| eed                           | LEs                                                   | 4,608                     | 8,256                                                            | 18,752                          | 33,216                         | 50,528                                   | 68,416   | 2,910   | 4,000                         | 5,980         | 12,060       | 20,060     |

| & Sp                          | Total RAM Bits (K) 1                                  | 120                       | 166                                                              | 240                             | 484                            | 594                                      | 1,152    | 60      | 78                            | 92            | 240          | 295        |

| Density & Speed               | M4K RAM Blocks (4 Kbits + 512 Parity Bits) 2          | 26                        | 36                                                               | 52                              | 105                            | 129                                      | 250      | 13      | 17                            | 20            | 52           | 64         |

| Den                           | Speed Grades (Fastest to Slowest)                     |                           |                                                                  | -6, -                           | 7, -8                          |                                          |          |         |                               | -6, -7, -8    |              |            |

|                               | Embedded Processor Available                          |                           |                                                                  | Nio                             | s II                           |                                          |          |         |                               | Nios II       |              |            |

| Architectural Features        | 18-Bit x 18-Bit/9-Bit x 9-Bit Embedded<br>Multipliers | 13/26                     | 18/36                                                            | 26/52                           | 35/70                          | 86/172                                   | 150/300  | _       | _                             | _             | -            | _          |

| Feat                          | I/O Registers per I/O Element                         | 1                         | 1                                                                | ✓                               | 1                              | 1                                        | 1        | 1       | 1                             | 1             | 1            | 1          |

|                               | True Dual-Port RAM                                    | 1                         | 1                                                                | ✓                               | 1                              | 1                                        | 1        | 1       | 1                             | 1             | 1            | 1          |

| fect                          | Global & Regional Clock Networks                      | 8                         | 8                                                                | 16                              | 16                             | 16                                       | 16       | 8       | 8                             | 8             | 8            | 8          |

| Archi<br>ida                  | PLLs/Unique Outputs                                   | 2/6                       | 2/6                                                              | 4/12                            | 4/12                           | 4/12                                     | 4/12     | 1/3     | 2/6                           | 2/6           | 2/6          | 2/6        |

|                               | Industrial Device Offering                            | 1                         | 1                                                                | ✓                               | 1                              | 1                                        | 1        | 1       | 1                             | 1             | 1            | 1          |

|                               | Lead-Free Device Offering                             | 1                         | 1                                                                | ✓                               | ✓                              | 1                                        | 1        | 1       | 1                             | 1             | 1            | 1          |

|                               | Configuration File Size (Mbits)                       | 1.26                      | 1.98                                                             | 3.89                            | 6.85                           | 9.96                                     | 14.31    | 0.63    | 0.93                          | 1.17          | 2.32         | 3.56       |

| 100                           | Number of EPCS1 Devices (1 Mbit)                      | 1                         | _                                                                | _                               | _                              | _                                        | _        | 1       | 1                             | 1             | _            | _          |

| Configuration Devices         | Number of EPCS4 Devices (4 Mbits)                     | 1                         | 1                                                                | 1                               | -                              | -                                        | -        | 1       | 1                             | 1             | 1            | 1          |

| a De                          | Number of EPCS16 Devices (16 Mbits)                   | 1                         | 1                                                                | 1                               | 1                              | 1                                        | 1        | _       | _                             | _             | _            | _          |

| a ţie                         | Number of EPCS64 Devices (64 Mbits)                   | 1                         | 1                                                                | 1                               | 1                              | 1                                        | 1        | -       | _                             | _             | -            | -          |

| igur                          | Number of EPC2 Devices (1.6 Mbits)                    | 1                         | 1                                                                | 2                               | 4                              | 5                                        | 7        | 1       | 1                             | 1             | 2            | 2          |

| 9                             | Number of EPC4 Devices (4 Mbits)                      | 1                         | 1                                                                | 1                               | -                              | -                                        | -        | 1       | 1                             | 1             | 1            | 1          |

|                               | Number of EPC8 Devices (8 Mbits)                      | 1                         | 1                                                                | 1                               | 1                              | 1                                        | _        | 1       | 1                             | 1             | 1            | 1          |

|                               | Number of EPC16 Devices (16 Mbits)                    | 1                         | 1                                                                | 1                               | 1                              | 1                                        | 1        | 1       | 1                             | 1             | 1            | 1          |

|                               | I/O Voltage Levels Supported (V)                      |                           |                                                                  | 1.5, 1.8,                       | 2.5, 3.3                       |                                          |          |         | 1.5                           | , 1.8, 2.5, 3 | 3.3          |            |

|                               | 1/O Standards Supported                               | Differention Differention | S, Mini-LVDS<br>al SSTL-2 (1 &<br>al HSTL (1 &<br>II), PCI, PCI- | & II), 1.5-V<br>II), SSTL-18    | Differential<br>(I & II), SSI  | HSTL (I & II<br>[L-2 (I & II),           | ), 1.8-V |         | S, Different<br>CI, LVTTL, LV |               | STL-2 (I & I | I), SSTL-3 |

| Features                      | LVDS Maximum Data Rate (Mbps)<br>(Receive/Transmit)   | 805/640                   | 805/640                                                          | 805/640                         | 805/640                        | 805/640                                  | 805/640  | 640/640 | 640/640                       | 640/640       | 640/640      | 640/640    |

| 9                             | LVDS Channels                                         | 60                        | 79                                                               | 136                             | 209                            | 197                                      | 265      | 34      | 129                           | 72            | 103          | 129        |

|                               | RSDS Maximum Data Rate (Mbps) (Transmit)              | 311                       | 311                                                              | 311                             | 311                            | 311                                      | 311      | 311     | 311                           | 311           | 311          | 311        |

|                               | Mini-LVDS Maximum Data Rate (Mbps)<br>(Transmit)      | 311                       | 311                                                              | 311                             | 311                            | 311                                      | 311      | -       | -                             | -             | -            | -          |

|                               | Series On-Chip Termination                            | 1                         | 1                                                                | 1                               | 1                              | 1                                        | 1        | _       | _                             | _             | _            | _          |

|                               | Programmable Drive Strength                           | 1                         | 1                                                                | ✓                               | ✓                              | ✓                                        | ✓        | 1       | ✓                             | ✓             | ✓            | 1          |

| ory                           | Memory Devices Supported                              |                           |                                                                  | QDRII, DDR                      | 2, DDR, SDR                    | l                                        |          |         |                               | DDR, SDR      |              |            |

| External Memory<br>Interfaces | MegaCore Controller With Clear<br>Text Datapath       |                           |                                                                  | V                               | /                              |                                          |          |         |                               | ✓             |              |            |

| in term                       | System Timing Analysis                                |                           |                                                                  | •                               | /                              |                                          |          |         |                               | ✓             |              |            |

| Ä                             | Board Layout Guidelines                               |                           |                                                                  | •                               | /                              |                                          |          |         |                               | ✓             |              |            |

$<sup>1 \</sup>text{ K} = 1,000$

FOR MORE INFORMATION

Cyclone FPGAs **Training**

Cyclone II FPGAs www.altera.com/cyclone2 www.altera.com/cyclone www.altera.com/training

$<sup>^2</sup>$  Kbits = 1,024 bits

$<sup>^{3}</sup>$  Requires external PHY device

# **Stratix High-Density FPGA Series**

The Stratix® FPGA series provides the richest feature set, highest performance, and largest FPGAs available in the industry. Stratix II FPGAs are the only FPGAs with a risk-free path to structured ASICs with reduced power and costs for volume applications. Only Altera high-density FPGAs use redundancy—a unique, patented Altera technology that dramatically increases yields and lowers device costs. The Stratix FPGA series delivers the density, performance, and features you need at both 90- and 130-nm process nodes.

#### **Key Features**

- The industry's biggest and fastest FPGAs

- Feature-rich I/O technology

- 3.1875- and 6.375-Gbps transceivers available

- Industry-leading DSP and memory capacity

- Support for Nios II soft processor

- Optimized for power

- Path to low-cost HardCopy® structured ASICs available

- Design security

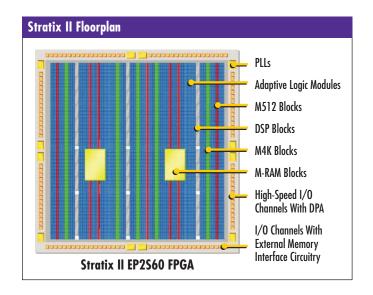

### 90-nm High-Performance, High-Density FPGAs

Stratix II devices are the industry's leading high-density, high-performance FPGAs. Built on a new, innovative logic structure to maximize performance and minimize power, Stratix II devices on average deliver 50 percent faster performance than prior-generation

FPGAs. Stratix II devices are the highest-density FPGAs from any vendor. They are the only FPGAs with a risk-free path to HardCopy II structured ASICs, which can further increase performance, reduce power, and minimize costs.

| Stratix II Family Features Summary  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Adaptive Logic Modules (ALMs)       | ALMs are part of a unique, innovative logic structure that delivers faster performance, minimizes area, and reduces power consumption. ALMs expand the traditional 4-input look-up table architecture to 7 inputs, increasing performance by reducing LEs, logic levels, and associated routing. In addition, ALMs maximize DSP performance with dedicated functionality to efficiently implement adder trees and other complex arithmetic functions.                  |

| MultiTrack™ Interconnect            | Connections between LEs, TriMatrix™ memory blocks, DSP blocks, and device I/O pins are provided by the MultiTrack interconnect structure with DirectDrive™ technology. The MultiTrack interconnect consists of continuous, performance-optimized routing lines of different lengths and speeds used for inter- and intradesign block connectivity. The Quartus II compiler automatically places critical design paths on faster interconnects to maximize performance. |

| TriMatrix Memory                    | TriMatrix memory in Stratix II FPGAs provides up to 9 Mbits of memory in three block sizes: 512 bits in the M512, 4 Kbits in the M4K, and 500 Kbits in the M-RAM blocks. TriMatrix memory includes parity checking and is capable of up to 550-MHz performance.                                                                                                                                                                                                        |

| DSP Blocks                          | Each DSP block includes multipliers with associated pipelining, adders, and accumulators. Stratix II FPGAs include up to 96 DSP blocks offering 384 18-bit x 18-bit multipliers that operate at up to 450 MHz. Each multiplier can be configured as 9-bit x 9-bit, 18-bit x 18-bit, or 36-bit x 36-bit multipliers.                                                                                                                                                    |

| External Memory Interface Circuitry | Fully characterized and hardware-validated circuitry provides flexible, high-performance interfaces to the latest external DRAM and SRAM memory technologies. Complete solutions, including easy-to-use IP, hardware development platforms, and comprehensive timing analysis, are available to minimize risk and speed time to market.                                                                                                                                |

| High-Speed Differential I/O Support | Optimized LVDS I/O pins provide high performance and excellent signal integrity. Wizards make differential I/O configuration straightforward and easy.                                                                                                                                                                                                                                                                                                                 |

| Dynamic Phase Alignment (DPA)       | DPA maximizes signal integrity and simplifies PCB layout and timing management for high-speed data transfer. DPA eliminates channel-to-channel and channel-to-clock skew in high-speed data transmission systems.                                                                                                                                                                                                                                                      |

| Stratix II Family Features Summary                  | (Continued)                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| On-Chip Termination                                 | Serial and differential on-chip termination simplifies design and reduces component count. Digital calibration circuitry provides industry-leading on-chip termination tolerance within 5 percent.                                                                                                         |

| Clock Management Features                           | Up to 12 PLLs and up to 48 system clocks. Advanced clock management features include PLL reconfiguration, spread-spectrum clocking, frequency synthesis, programmable phase shift, programmable delay shift, external feedback, and programmable bandwidth for all on- and off-chip clocking requirements. |

| Design Security                                     | Configuration bitstream encryption using 128-bit advanced encryption standard (AES); prevents IP thefts and product tampering. The non-volatile key storage makes the solution reliable, easy to use, and low cost.                                                                                        |

| Remote System Upgrades                              | Enables reliable and safe deployment of in-system enhancements and bug fixes.                                                                                                                                                                                                                              |

| Hot Socketing and Power Sequencing                  | Robust on-chip hot-socketing and power-sequencing support ensures proper device operation independent of the power-up sequence.                                                                                                                                                                            |

| Automatic Single Event Upset<br>Detection Circuitry | Features automatic single event upset detection circuitry utilizing 32-bit CRC.                                                                                                                                                                                                                            |

| Nios II Embedded Processor Support                  | Nios II embedded processors reduce cost, increase flexibility, and offer an ideal replacement for low-cost discrete microprocessors. Nios II soft processor support for Stratix II FPGAs offers over 200-DMIPS performance.                                                                                |

| HardCopy II Structured ASIC Support                 | Reduces cost for volume applications using this pin-compatible structured ASIC.                                                                                                                                                                                                                            |

# 90-nm High-Performance, High-Density FPGAs With 6.375-Gbps Transceivers

Altera's Stratix II GX devices deliver all the benefits of Stratix II devices plus up to 20 low-power, high-speed transceiver channels. The transceivers support all data rates spanning from 622 Mbps to 6.375 Gbps. They have dynamically configurable transmit preemphasis and receiver equalization to optimize signal integrity under adverse channel conditions. The transceivers are capable of driving FR-4 backplanes at 6.375 Gbps and have proven to be interoperable with backplanes and transceivers from multiple vendors.

In addition, the physical coding sublayer (PCS) hard IP, which is part of the transceiver block, saves valuable LE resources and simplifies protocol support. Stratix II GX devices incorporate protocolspecific PCS blocks for the following protocols: the PCI Express, Common Electrical Interface 6.375 Gbps (CEI-6G), serial digital interface (SDI), XAUI, SONET, Gigabit Ethernet, serial RapidIO™, and SerialLite II protocols. Stratix II GX devices also have 8b/10b encoder/decoders that are bypassable for proprietary protocols.

| Stratix II GX Family Features Summary             |                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Excellent Signal Integrity<br>622 Mbps—6.375 Gbps | The transmitter has low jitter generation and up to 500 percent pre-emphasis. The receiver has excellent jitter tolerance and up to 17-dB equalization.                                                                                          |  |  |  |  |  |  |

| Low Power                                         | The transceiver dissipates 225 mW per channel at 6.375 Gbps and only 125 mW per channel at 3.125 Gbps.                                                                                                                                           |  |  |  |  |  |  |

| PCS Support (Hard IP)                             | The transceiver supports the following PCS blocks: PCI Express, PIPE-Compliant PCS, CEI-6G, 8b/10b encoder/decoder, XAUI state machine and channel bonding, Gigabit Ethernet state machine, SONET, and 8/10/16/20/32/40-bit interface (to FPGA). |  |  |  |  |  |  |

| System-Level Diagnostics                          | Serial loopback, reverse serial loopback, psuedo-random binary sequence (PRBS) generator checker, and register-based interface facilitates dynamic reconfiguration of pre-emphasis, equalization, and differential output voltage.               |  |  |  |  |  |  |

### 130-nm High-Performance, High-Density FPGAs

The density of Stratix devices ranges from 10,570 to 79,040 LEs, with up to 7 Mbits of embedded RAM and 88 18-bit x 18-bit multipliers. Stratix devices have up to 12 PLLs, 40 system clocks, and support for many single-ended and differential I/O electrical

standards. Stratix FPGAs are based on a 1.5-V, 130-nm, all-layer-copper SRAM process. For new designs, Stratix II devices provide better performance and cost attributes than Stratix devices.

| Stratix Family Features Summary                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MultiTrack Interconnect                          | Connections between LEs, TriMatrix memory blocks, DSP blocks, and device I/O pins are provided by the MultiTrack interconnect structure with DirectDrive technology. The MultiTrack interconnect consists of continuous, performance-optimized routing lines of different lengths and speeds used for inter- and intra-design block connectivity. The Quartus II compiler automatically places critical design paths on faster interconnects to maximize performance. |

| TriMatrix Memory                                 | TriMatrix memory in Stratix FPGAs provides up to 7 Mbits of memory in three block sizes: 512 bits in the M512, 4 Kbits in the M4K, and 500 Kbits in the M-RAM blocks. TriMatrix memory includes parity checking and is capable of up to 320-MHz performance.                                                                                                                                                                                                          |

| DSP Blocks                                       | Each DSP block includes four 18-bit x 18-bit multipliers with associated pipelining, adders, and accumulators. Configurations can support any bit-width up to 36 bits x 36 bits. Stratix FPGAs include up to 22 DSP blocks offering 88 18-bit x 18-bit multipliers that operate at up to 275 MHz.                                                                                                                                                                     |

| High-Speed Differential I/O Support              | Optimized LVDS I/O pins provide high performance and excellent signal integrity. Wizards make differential I/O configuration straightforward and easy.                                                                                                                                                                                                                                                                                                                |

| On-Chip Termination                              | Serial and differential on-chip termination simplifies design and reduces component count. Digital calibration circuitry provides industry-leading on-chip termination tolerance.                                                                                                                                                                                                                                                                                     |

| Clock Management Features                        | Up to 12 PLLs and up to 48 system clocks. Advanced clock management features include PLL reconfiguration, spread-spectrum clocking, frequency synthesis, programmable phase shift, programmable delay shift, external feedback, and programmable bandwidth for all on- and off-chip clocking requirements.                                                                                                                                                            |

| Remote System Upgrades                           | Enables reliable, safe deployment of in-system upgrades and bug fixes.                                                                                                                                                                                                                                                                                                                                                                                                |

| Hot Socketing and Power Sequencing               | Robust on-chip hot-socketing and power-sequencing support that ensures proper device operation independent of the power-up sequence.                                                                                                                                                                                                                                                                                                                                  |

| Automatic Single Event Upset Detection Circuitry | Features automatic single event upset detection circuitry utilizing 32-bit CRC.                                                                                                                                                                                                                                                                                                                                                                                       |

| Nios II Embedded Processor Support               | Nios II embedded processors reduce cost, increase flexibility, and offer an ideal replacement for low-cost discrete microprocessors. Nios II soft processor support for Stratix FPGAs offers over 150-DMIPS performance.                                                                                                                                                                                                                                              |

| HardCopy Structured ASIC Support                 | Reduces cost for volume applications using this pin-compatible structured ASIC.                                                                                                                                                                                                                                                                                                                                                                                       |

# 130-nm High-Performance, High-Density FPGAs With 3.1875-Gbps Transceivers

Stratix GX FPGAs combine Altera's second-generation transceivers with the award-winning Stratix FPGA architecture. Stratix GX FPGAs have up to 20 transceivers operating from 500 Mbps to 3.1875 Gbps, which can easily drive 40-inch backplanes. Stratix GX devices, with their excellent built-in jitter control circuitry and tolerance, transmit pre-emphasis, receiver equalization, and 8b/10b encoder/decoder circuitry, deliver a robust transceiver solution.

Stratix GX devices also incorporate dedicated serializer/deserializer (SERDES) and DPA circuitry into 45 source-synchronous differential I/O pins, enabling the devices to operate at up to 1 Gbps. DPA automatically compensates for clock-to-channel skew on a channel-per-channel basis, thereby simplifying board layout and design. For new designs, Stratix II GX devices provide better performance and cost attributes than Stratix GX devices.

| Stratix GX Family Features Summary                        | <i>t</i>                                                                                                                                                                                                                                                                                     |