# **Excellent Integrated System Limited**

Stocking Distributor

Click to view price, real time Inventory, Delivery & Lifecycle Information:

Analog Devices Inc. AD5520JSTZ

For any questions, you can email us directly: <a href="mailto:sales@integrated-circuit.com">sales@integrated-circuit.com</a>

# Per Pin Parametric Measurement Unit/Source Measure Unit

AD5520

#### **FEATURES**

Force/measure functions

FIMV, FVMI, FVMV, FIMI, FNMV

Force/measure voltage range ±11 V

4 user programmable force/measure current ranges

±4 μA, ±40 μA, ±400 μA, ±4 mA (external resistors)

2 user programmable extended current ranges

Up to 6 mA without external driver

Higher currents with external driver

Clamp circuitry and window comparators on board

Guard amplifier

64-lead LQFP package

#### **APPLICATIONS**

Automatic test equipment

Per pin PMU, shared pin PMU, device power supply

instrumentation

Source measure, parametric measurement,

precision measurement

#### **GENERAL DESCRIPTION**

The AD5520 is a single-channel, per pin parametric measurement unit (PPMU) for use in semiconductor automatic test equipment. The part is also suited for use as a source measurement unit for instrumentation applications. It contains programmable modes to force a pin voltage and measure the corresponding current, or force a current and measure the voltage. The AD5520 can force/measure over a  $\pm 11~\rm V$  range or user-programmable currents up to  $\pm 4~\rm mA$  with its on-board force amplifier. An external amplifier is required for wider current ranges. The device provides a force sense capability to ensure accuracy at the tester pin. A guard output is also available to drive the shield of a force/sense pair. The AD5520 is available in a 64-lead LQFP package.

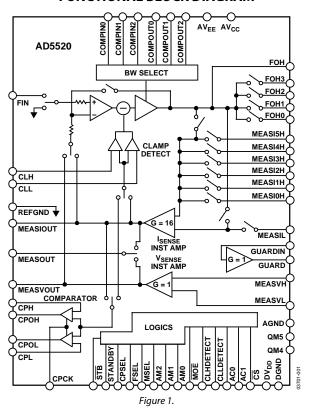

#### **FUNCTIONAL BLOCK DIAGRAM**

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 © 2005 Analog Devices, Inc. All rights reserved.

Datasheet of AD5520JSTZ - IC PPMU SNGL-CH 64-LQFP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

# AD5520

| TABLE OF CONTENTS                             |                                           |    |

|-----------------------------------------------|-------------------------------------------|----|

| Features                                      | Force Control Amplifier                   | 15 |

| Applications1                                 | Comparator Function and Strobing          | 15 |

| General Description                           | Clamp Function                            | 15 |

| Functional Block Diagram                      | High Current Ranges                       | 15 |

| Specifications                                | Circuit Operation                         | 16 |

| Timing Characteristics                        | Force Voltage                             | 16 |

| Absolute Maximum Ratings                      | Measure Current                           | 16 |

| ESD Caution                                   | Force Current                             | 17 |

| Pin Configuration and Function Descriptions 8 | Measure Voltage                           | 17 |

| Typical Performance Characteristics           | Short Circuit Protection                  | 17 |

| Theory of Operation                           | Settling Time Considerations              | 18 |

| Interface                                     | PCB Layout and Power Supply Decoupling    | 19 |

| Standby Mode                                  | Typical Connection Circuit for the AD5520 | 20 |

| Force Voltage or Force Current                | Typical Application Circuit               | 21 |

| Measured Parameter14                          | Evaluation Board for the AD5520           | 22 |

| Current Ranges14                              | Outline Dimensions                        | 24 |

| R <sub>S</sub> Selection                      | Ordering Guide                            | 24 |

| REVISION HISTORY                              |                                           |    |

| 9/05—Rev. A to Rev. B                         | 10/03—Rev. 0 to Rev. A                    |    |

| Updated FormatUniversal                       | Changes to Specifications                 |    |

| Changes to Features                           | Updated Ordering Guide                    | 5  |

| Changes to Figure 1                           | 0/02 B 1:1:0 D 1:11 137                   |    |

| Changes to Specifications                     | 9/03—Revision 0: Initial Version          |    |

| Changes to Force Current Section              |                                           |    |

| Changes to Figure 26                          |                                           |    |

| Updated Outline Dimensions                    |                                           |    |

Datasheet of AD5520JSTZ - IC PPMU SNGL-CH 64-LQFP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

AD5520

# **SPECIFICATIONS**

$AV_{CC}$  = +15 V ± 5%,  $AV_{EE}$  = -15 V ± 5%,  $DV_{DD}$  = 5 V ± 10%, AGND = 0 V, REFGND = 0 V, DGND = 0 V. All specifications 0°C to 70°C, unless otherwise noted.

Table 1.

| Parameter                                                          | Min | Typ <sup>1</sup> | Max      | Unit         | Test Conditions/Comments                                     |

|--------------------------------------------------------------------|-----|------------------|----------|--------------|--------------------------------------------------------------|

| VOLTAGE FORCE MODE                                                 |     |                  |          |              |                                                              |

| Force Control Output Voltage Range                                 | ±11 |                  |          | V            | $R_{LOAD} = 10 \text{ k}\Omega$ , $C_{LOAD} = 50 \text{ pF}$ |

| FOH Output Impedance                                               |     | 70               |          | Ω            |                                                              |

| FOH0                                                               |     | 2.5              |          | kΩ           |                                                              |

| FOH1                                                               |     | 3                |          | kΩ           |                                                              |

| FOH2                                                               |     | 500              |          | Ω            |                                                              |

| FOH3                                                               |     | 60               |          | Ω            |                                                              |

| Input Offset Error                                                 |     | ±1               | ±5       | mV           |                                                              |

| Input Offset Error Temperature Coefficient                         |     | ±10              |          | μV/°C        |                                                              |

| Gain Error                                                         |     |                  | 1        | %            |                                                              |

| Clamp Current Error <sup>2</sup>                                   |     |                  | ±1       | % FS         | of FIN                                                       |

| CURRENT MEASURE/FORCE                                              |     |                  |          |              | Suggested values; set with external sense resistors          |

| FOH0                                                               |     | ±4               |          | μΑ           | MODE0, $R_S = 125 \text{ k}\Omega$                           |

| FOH1                                                               |     | ±40              |          | μΑ           | MODE1, $R_S = 12.5 \text{ k}\Omega$                          |

| FOH2                                                               |     | ±400             |          | μΑ           | MODE2, $R_S = 12.5 \text{ k}\Omega$                          |

| FOH3                                                               |     | ±4               |          | mA           | MODE3, $R_S = 125 \Omega$                                    |

| CURRENT MEASURE MODE                                               |     |                  |          |              |                                                              |

| High Sense Input Range, V <sub>MEASIXH</sub>                       |     |                  | ±11      | V            |                                                              |

| Linearity <sup>3</sup>                                             |     |                  | ±0.01    | % FSR        | $+11 \text{ V} > \text{V}_{FOL} > -11 \text{ V}$             |

| Input Bias Current                                                 |     | ±1               | ±3       | nA           |                                                              |

| Input Bias Current Drift <sup>1</sup>                              |     | 50               | _0       | pA/°C        |                                                              |

| Output Offset Error                                                |     | 30               | ±100     | mV           | MODE0 (±4 μA)                                                |

| output offset Error                                                |     |                  | ±100     | mV           | MODE1 (±40 μA)                                               |

|                                                                    |     |                  | ±100     | mV           | MODE2 (±400 μA)                                              |

|                                                                    |     |                  | ±100     | mV           | MODE3 (±4 mA)                                                |

| Output Offset Error Temperature Coefficient                        |     | ±10              | ±100     | μV/°C        | MODES (±4 III/I)                                             |

| Gain Error                                                         |     | ±0.1             | ±0.35    | %            | Gain of 16                                                   |

| Gain Error Temperature Coefficient <sup>4</sup>                    |     | 30               | _0.55    | ppm/°C       | Gamerie                                                      |

| MEASIOUT Output Load Current                                       |     | ±4               |          | mA           |                                                              |

| CMRR                                                               |     | 95               |          | dB           | @ DC                                                         |

| CURRENT FORCE MODE                                                 |     |                  |          | ub           |                                                              |

| Input Offset Error                                                 |     |                  | ±10      | mV           | with MODE0, MODE1, MODE2, MODE3                              |

| Gain Error                                                         |     |                  | 1        | %            | With Mobel, Mobel, Mobel, Mobel                              |

| Clamp Voltage Error <sup>2</sup>                                   |     |                  | ±1       | % FS         | of FIN                                                       |

| VOLTAGE MEASURE MODE                                               |     |                  | <u> </u> | 7013         | OTTIN                                                        |

| Differential Input Range                                           |     |                  | ±11      | V            |                                                              |

| Low Sense Input Voltage Range                                      |     | ±100             | ±11      | mV           | MEASVL                                                       |

| Linearity <sup>3</sup>                                             |     | ±100             | +0.005   | % FSR        | +11 V > V <sub>MEASVH</sub> to V <sub>MEASVL</sub> > -11 V   |

| Input Offset Error                                                 |     | ±5               | ±10      | mV           | FIN = 0 V, measured @ MEASVOUT                               |

| Input Offset Error Temperature Coefficient <sup>1</sup>            |     | ±15              | -10      | μV/°C        | The - o v, measured w MEASVOOT                               |

| Gain Error                                                         |     | ±0.03            | ±0.15    | μν/ C<br>  % | Gain of 1                                                    |

| Gain Error<br>Gain Error Temperature Coefficient⁴                  |     | ±0.03            | -0.13    | ppm/°C       | Guinori                                                      |

| Input Bias Current                                                 |     | ±1               | ±3       | nA           |                                                              |

|                                                                    |     | ±1<br>50         | ±3       | pA/°C        |                                                              |

|                                                                    |     | 20               |          | pπ/ C        |                                                              |

| Input Bias Current Drift <sup>4</sup> MEASVOUT Output Load Current |     | ±4               |          | mA           |                                                              |

Datasheet of AD5520JSTZ - IC PPMU SNGL-CH 64-LQFP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

| Parameter                                         | Min | Typ <sup>1</sup> | Max | Unit     | Test Conditions/Comments              |

|---------------------------------------------------|-----|------------------|-----|----------|---------------------------------------|

| AMPLIFIER SETTLING TIME <sup>4, 5</sup>           |     |                  |     |          |                                       |

| V <sub>SENSE</sub> Amp                            |     | 20               |     | μs       | to 0.2%                               |

| I <sub>SENSE</sub> Amp                            |     | 12               |     | μs       | to 0.2%                               |

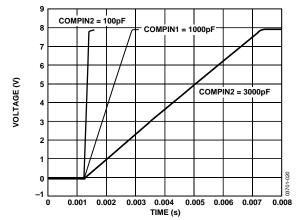

| LOOP SETTLING <sup>4,5</sup>                      |     |                  |     |          | Settling to within 0.024% of 8 V step |

| COMPIN2 = 100 pF                                  |     | 450              | 600 | μs       | MODE0                                 |

|                                                   |     | 285              | 390 | μs       | MODE1                                 |

|                                                   |     | 170              | 240 | μs       | MODE2, MODE3                          |

| COMPIN1 = 1000 pF                                 |     | 2                | 2.5 | ms       | MODE0                                 |

|                                                   |     | 1.8              | 2.4 | ms       | MODE1, MODE2, MODE3                   |

| COMPINO = 3000 pF                                 |     | 5.75             | 8.7 | ms       | MODE0, MODE1, MODE2, MODE3            |

| SLEW RATE <sup>4, 5</sup>                         |     | 50               |     | mV/μs    | COMPIN2 = 100 pF                      |

|                                                   |     | 4.3              |     | mV/μs    | COMPIN1 = 1000 pF                     |

|                                                   |     | 1.28             |     | mV/μs    | COMPINO = 3000 pF                     |

| COMPARATOR                                        |     |                  |     | <u>'</u> | ,                                     |

| CPH, CPL Input Range                              |     |                  | ±11 | V        | V <sub>CPH</sub> > V <sub>CPL</sub>   |

| Input Offset                                      |     |                  | ±7  | mV       |                                       |

| GUARD DRIVER                                      |     |                  |     |          |                                       |

| Output Voltage                                    |     |                  | ±11 | V        |                                       |

| Output Impedance                                  |     | 130              |     | Ω        | Capacitive load only                  |

| Output Offset Voltage                             |     | 400              |     | mV       | ,                                     |

| Load Current⁴                                     |     | ±4               |     | mA       |                                       |

| Output Settling Time⁴                             |     | 0.5              | 2   | μs       | 100 pF capacitive load                |

| ANALOG REFERENCE INPUTS                           |     |                  |     |          |                                       |

| Force Control Input Range                         | ±11 |                  |     | V        |                                       |

| Force Control Input Impedance                     |     | 1                |     | ΜΩ       |                                       |

| Clamp Control Input Range                         | ±11 |                  |     | V        | $V_{CLH} > V_{CLL}$                   |

| Clamp Control Input Impedance                     |     | 1                |     | ΜΩ       |                                       |

| Comparator Threshold Input Range                  | ±11 |                  |     | V        |                                       |

| Comparator Threshold Input Impedance              |     | 1                |     | ΜΩ       |                                       |

| Input Capacitance <sup>4</sup>                    |     | 3                |     | pF       |                                       |

| LEAKAGE CURRENT                                   |     |                  |     |          |                                       |

| MEASIxx, MEASVx, MEASOUT Leakage                  |     | ±3               | ±20 | nA       |                                       |

| ANALOG MEASUREMENT OUTPUTS                        |     | ·                |     |          |                                       |

| Voltage Measure Output Impedance                  |     | 2                |     | Ω        |                                       |

| Current Measure Output Impedance                  |     | 3                |     | Ω        |                                       |

| Multiplexed Sense Output Impedance                |     | 1                |     | kΩ       |                                       |

| Input Capacitance                                 |     |                  |     |          |                                       |

| MEASIxH, MEASVH, FOHx                             |     | 8                |     | pF       |                                       |

| LOGIC INPUTS                                      |     |                  |     |          |                                       |

| Input Current                                     |     |                  | ±1  | μΑ       | All digital inputs together           |

| Input Low Voltage, V <sub>INL</sub>               |     |                  | 0.8 | V        |                                       |

| Input High Voltage, V <sub>IH</sub> ∟             | 2.0 |                  |     | V        |                                       |

| Input Capacitance <sup>4</sup>                    |     | 3                |     | pF       |                                       |

| LOGIC OUTPUTS                                     |     |                  |     |          |                                       |

| Output Low Voltage, VoL4                          |     |                  | 0.4 | V        | I <sub>SINK</sub> = 2 mA              |

| Output High Voltage, V <sub>OH</sub> <sup>4</sup> | 2.4 |                  |     | V        | I <sub>SOURCE</sub> = 2 mA            |

Datasheet of AD5520JSTZ - IC PPMU SNGL-CH 64-LQFP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

| Parameter                                       | Min    | Typ <sup>1</sup> | Max    | Unit | Test Conditions/Comments              |

|-------------------------------------------------|--------|------------------|--------|------|---------------------------------------|

| POWER REQUIREMENTS                              |        |                  |        |      |                                       |

| <b>AV</b> <sub>CC</sub>                         | 14.25  | 15               | 15.75  | V    | for specific performance <sup>6</sup> |

| $AV_{EE}$                                       | -14.25 | -15              | +15.75 | V    |                                       |

| Power Supply Rejection Ratio, PSRR <sup>1</sup> |        |                  |        |      |                                       |

| FOH                                             |        | -25              |        | dB   | 100 kHz                               |

|                                                 |        | -16              |        | dB   | 500 kHz                               |

|                                                 |        | -15              |        | dB   | 1 MHz                                 |

| MEASOUT                                         |        | -55              |        | dB   | 100 kHz                               |

|                                                 |        | -10              |        | dB   | 500 kHz                               |

| DC PSR                                          |        | 90               |        | dB   |                                       |

| $DV_{DD}$                                       |        | 5                |        | V    |                                       |

| lavcc                                           |        |                  | 12     | mA   |                                       |

| lavee                                           |        |                  | 12     | mA   |                                       |

| l <sub>DVDD</sub>                               |        |                  | 0.5    | mA   | Digital inputs at supply rails        |

<sup>&</sup>lt;sup>1</sup> Typical values are at 25°C and nominal supply, unless otherwise noted.

<sup>&</sup>lt;sup>1</sup> Fypical values are at 25 C differential control of the state of th

# AD5520

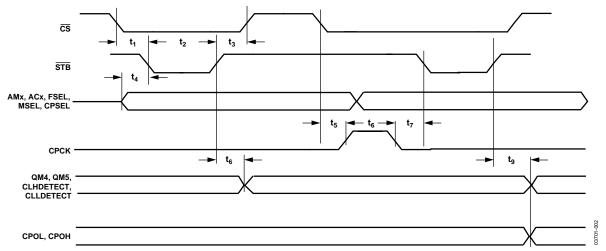

# TIMING CHARACTERISTICS

$AV_{CC}$  = +15 V ± 5%,  $AV_{EE}$  = -15 V ± 5%, AGND = 0 V, REFGND = 0 V, DGND = 0 V. All specifications 0°C to 70°C, unless otherwise noted. 1, 2

Table 2.

|                       | DV        | DD    |        |                                                |

|-----------------------|-----------|-------|--------|------------------------------------------------|

| Parameter             | 5 V ± 10% | 3.3 V | Unit   | Conditions/Comments                            |

| t <sub>1</sub>        | 0         | 0     | ns min | CS falling edge to STB falling edge setup time |

| $t_2$                 | 30        | 200   | ns min | STB pulse width                                |

| t <sub>3</sub>        | 40        | 70    | ns min | STB rising edge to CS rising edge setup time   |

| t <sub>4</sub>        | 0         | 40    | ns min | Data setup time                                |

| <b>t</b> <sub>5</sub> | 550       | 560   | ns min | CS falling edge to CPCK rising edge setup time |

| $t_6$                 | 320       | 320   | ns min | CPCK pulse width                               |

| t <sub>7</sub>        | 450       | 500   | ns min | CPCK to STB falling edge setup time            |

| t <sub>8</sub>        | 150       | 800   | ns min | STB rising edge to QMx, CLxDETECT valid        |

| t <sub>9</sub>        | 100       | 440   | ns min | STB rising edge to CPOH, CPOL valid            |

| t <sub>10</sub>       | 240       | 240   | μs min | Comparator setup time, MODE2, MODE3 settling   |

| t <sub>11</sub>       | 150       | 500   | ns min | Comparator hold time                           |

| t <sub>12</sub>       | 100       | 440   | ns min | Comparator output delay time                   |

| t <sub>13</sub>       | 320       | 320   | ns min | Comparator strobe pulse width                  |

<sup>&</sup>lt;sup>1</sup> See Figure 2.

<sup>&</sup>lt;sup>2</sup> All input signals are specified with tr = tf = 1 ns (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of  $(V_{IL} + V_{IH})/2$ .

Figure 2. Timing Diagram

Figure 3. Comparator Timing

Datasheet of AD5520JSTZ - IC PPMU SNGL-CH 64-LQFP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

AD5520

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

#### Table 3

| Table 3.                                              |                                             |

|-------------------------------------------------------|---------------------------------------------|

| Parameter                                             | Rating                                      |

| AV <sub>CC</sub> to AV <sub>EE</sub>                  | 34 V                                        |

| AV <sub>CC</sub> to AGND                              | −0.3 V, +17 V                               |

| AV <sub>EE</sub> to AGND                              | +0.3 V, -17 V                               |

| $DV_DD$                                               | −0.3 V to +6 V                              |

| Digital Inputs to DGND                                | $-0.3 \text{ V to DV}_{DD} + 0.3 \text{ V}$ |

| Analog Inputs to AGND                                 | $AV_{CC} + 0.3 V$ to $AV_{EE} - 0.3 V$      |

| CLH to CLL                                            | −0.3 V to +34 V                             |

| CPH to CPL                                            | −0.3 V to +34 V                             |

| REFGND, DGND                                          | $AV_{CC} + 0.3 V$ to $AV_{EE} - 0.3 V$      |

| Operating Temperature Range                           |                                             |

| Commercial (J Version)                                | 0°C to 70°C                                 |

| Storage Temperature Range                             | −65°C to +150°C                             |

| Maximum Junction Temperature,<br>(T <sub>J</sub> max) | 150°C                                       |

| Package Power Dissipation                             | $(T_J \max - T_A)/\theta_{JA}$              |

| Thermal Impedance $\theta_{JA}$                       | 47.8°C /W                                   |

| Lead Temperature<br>(Soldering 10 sec)                | 300°C                                       |

| IR Reflow, Peak Temperature                           | 220°C                                       |

|                                                       |                                             |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

Datasheet of AD5520JSTZ - IC PPMU SNGL-CH 64-LQFP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

# AD5520

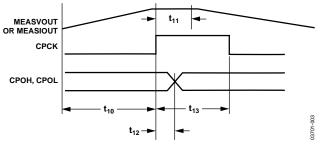

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 4. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic      | Description                                                                                                                                                                                                    |

|---------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | CPH           | Upper Comparator Threshold Voltage Input, CPH > CPL.                                                                                                                                                           |

| 2       | CPL           | Lower Comparator Threshold Voltage Input, CPL < CPH.                                                                                                                                                           |

| 3, 18   | $DV_DD$       | Digital Supply Voltage.                                                                                                                                                                                        |

| 4       | СРОН          | Logic Output. When high, indicates MEASVOUT or MEASIOUT > CPH.                                                                                                                                                 |

| 5       | CPOL          | Logic Output. When high, indicates MEASVOUT or MEASIOUT < CPL.                                                                                                                                                 |

| 6       | CPCK          | Logic Input. Used to initiate comparator sampling and update CPOH and CPOL.                                                                                                                                    |

| 7, 17   | DGND          | Digital Ground.                                                                                                                                                                                                |

| 8       | CLHDETECT     | Logic Output. When high, indicates upper clamp active. See the Clamp Function section.                                                                                                                         |

| 9       | CLLDETECT     | Logic Output. When high, indicates lower clamp active. See the Clamp Function section.                                                                                                                         |

| 10      | QM4           | Logic Output. When high, indicates current range Mode 4 is enabled. May be used to drive external relay or switch. See the High Current Ranges section.                                                        |

| 11      | QM5           | Logic Output. When high, indicates current range Mode 5 is enabled. May be used to drive external relay or switch. See the High Current Ranges section.                                                        |

| 12      | MOE           | Active Low MEASOUT Enable.                                                                                                                                                                                     |

| 13      | <del>CS</del> | Active Low Logic Input. The device is selected when this pin is low. See the Interface section.                                                                                                                |

| 14      | STB           | Active Low Logic Input. Used in conjunction with CPCK and $\overline{\text{CS}}$ to configure the device for different configurations. Rising edge of STB triggers sequence inputs. See the Interface section. |

| 15      | AC0           | Logic Input. Used in conjunction with AC1 to select one of three external compensation capacitors. See the Force Control Amplifier section.                                                                    |

| 16      | AC1           | Logic Input. Used in conjunction with AC0 to select one of three external compensation capacitors. See the Force Control Amplifier section.                                                                    |

| 19      | AM2           | Logic Input. Used in conjunction with AM1 and AM0 to select one of six current ranges or to enable standby mode. See the Current Ranges section.                                                               |

| 20      | AM1           | Logic Input. Used in conjunction with AM2 and AM0 to select one of six current ranges or to enable standby mode. See the Current Ranges section.                                                               |

| 21      | AM0           | Logic Input. Used in conjunction with AM2 and AM1 to select one of six current ranges or to enable standby mode. See the Current Ranges section.                                                               |

| 22      | STANDBY       | Logic Input. When high, device is in standby mode of operation. See the Standby Mode section.                                                                                                                  |

# **Distributor of Analog Devices Inc.: Excellent Integrated System Limited**Datasheet of AD5520JSTZ - IC PPMU SNGL-CH 64-LQFP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

| Pin No. | Mnemonic           | Description                                                                                                                                                |

|---------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23      | FSEL               | Logic Input. Force mode select. Used to select between current or voltage force operation. See the Force Voltage or Force Current section.                 |

| 24      | MSEL               | Logic Input. Measure mode select. Used to connect MEASOUT to either MEASIOUT when high or MEASVOUT when low.                                               |

| 25      | CPSEL              | Logic Input. Comparator select. Used to compare CPL, CPH to MEASVOUT when low, or to MEASIOUT when high. See the Comparator Function and Strobing section. |

| 26      | AVEE               | Most Negative Supply Voltage.                                                                                                                              |

| 27      | $AV_{CC}$          | Most Positive Supply Voltage.                                                                                                                              |

| 28      | AGND               | MEASx Input Ground.                                                                                                                                        |

| 29      | $AV_{EE\_G}$       | Most Negative Supply Voltage.                                                                                                                              |

| 30      | GUARD              | Guard Output.                                                                                                                                              |

| 31      | NC                 | No Connect.                                                                                                                                                |

| 32      | GUARDIN            | Guard Input.                                                                                                                                               |

| 33      | AV <sub>CC_G</sub> | Most Positive Supply Voltage.                                                                                                                              |

| 34      | MEASVL             | DUT Voltage Sense Inputs (Low Sense).                                                                                                                      |

| 35      | GUARD(NC)          | No Connect.                                                                                                                                                |

| 36      | MEASVH             | DUT Voltage Sense Inputs (High Sense).                                                                                                                     |

| 37      | MEASIL             | DUT Current Sense Inputs (Low Sense).                                                                                                                      |

| 38      | MEASIOH            | DUT Current Sense Inputs (High Sense).                                                                                                                     |

| 39      | FOH0               | Force Control Voltage Output.                                                                                                                              |

| 40      | MEASI1H            | DUT Current Sense Inputs (High Sense).                                                                                                                     |

| 41      | FOH1               | Force Control Voltage Output.                                                                                                                              |

| 42      | MEASI2H            | DUT Current Sense Inputs (High Sense).                                                                                                                     |

| 43      | FOH2               | Force Control Voltage Output.                                                                                                                              |

| 44      | MEASI3H            | DUT Current Sense Inputs (High Sense).                                                                                                                     |

| 45      | FOH3               | Force Control Voltage Output.                                                                                                                              |

| 46      | MEASI4H            | DUT Current Sense Inputs (High Sense).                                                                                                                     |

| 47      | MEASI5H            | DUT Current Sense Inputs (High Sense).                                                                                                                     |

| 48      | $AV_{EE\_B}$       | Most Negative Supply Voltage.                                                                                                                              |

| 49      | FOH                | External Force Driver Control Voltage Output.                                                                                                              |

| 50      | $AV_{CC\_B}$       | Most Positive Supply Voltage.                                                                                                                              |

| 51      | COMPOUT0           | Compensation Capacitor 0 Output.                                                                                                                           |

| 52      | COMPOUT1           | Compensation Capacitor 1 Output.                                                                                                                           |

| 53      | COMPOUT2           | Compensation Capacitor 2 Output.                                                                                                                           |

| 54      | COMPIN0            | Compensation Capacitor 0 Input.                                                                                                                            |

| 55      | COMPIN1            | Compensation Capacitor 1 Input.                                                                                                                            |

| 56      | COMPIN2            | Compensation Capacitor 2 Input.                                                                                                                            |

| 57, 59  | REFGND             | Analog Input/Output Reference Ground.                                                                                                                      |

| 58      | MEASOUT            | Multiplexed DUT Voltage/Current Sense Output. See the Measured Parameter section.                                                                          |

| 60      | MEASIOUT           | DUT Current Sense Output.                                                                                                                                  |

| 61      | MEASVOUT           | DUT Voltage Sense Output.                                                                                                                                  |

| 62      | FIN                | Force Control Voltage Input.                                                                                                                               |

| 63      | CLH                | Upper Clamp Voltage Input CLH > CLL.                                                                                                                       |

| 64      | CLL                | Lower Clamp Voltage CLL < CLH.                                                                                                                             |

# AD5520

# TYPICAL PERFORMANCE CHARACTERISTICS

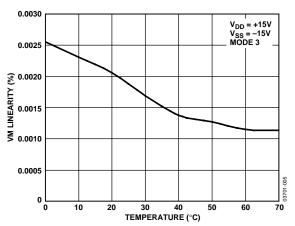

Figure 5. Voltage Sense Amplifier Linearity vs. Temperature

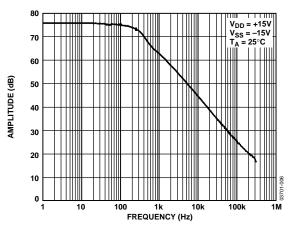

Figure 6. Voltage Sense Amplifier CMRR vs. Frequency

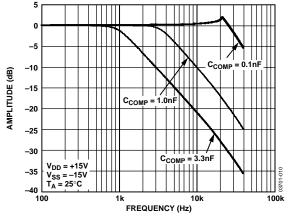

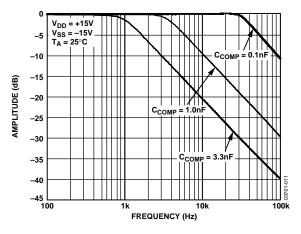

Figure 7. Force Amplifier Bandwidth, Mode 0 (4 μA)

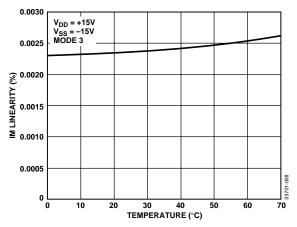

Figure 8. Current Sense Linearity vs. Temperature

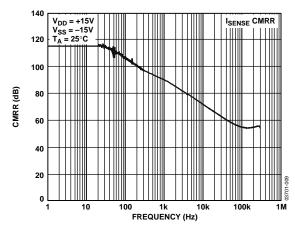

Figure 9. Current Sense Amplifier CMRR vs. Frequency

Figure 10. Force Amplifier Bandwidth, Mode 1 (40  $\mu$ A)

Datasheet of AD5520JSTZ - IC PPMU SNGL-CH 64-LQFP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

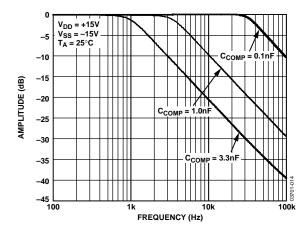

Figure 11. Force Amplifier Bandwidth, Mode 2 (400 μA)

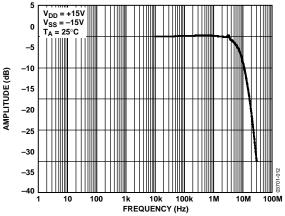

Figure 12. Guard Amplifier Bandwidth

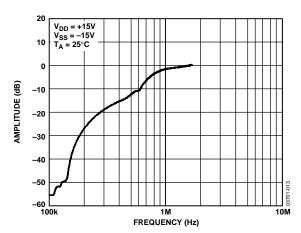

Figure 13. Current Sense Amplifier AC PSRR

Figure 14. Force Amplifier Bandwidth, Mode 3 (4 mA)

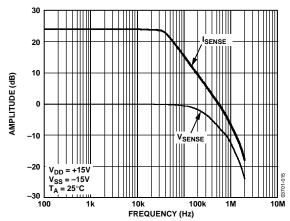

Figure 15. Voltage Sense and Current Sense Amplifier Bandwidths

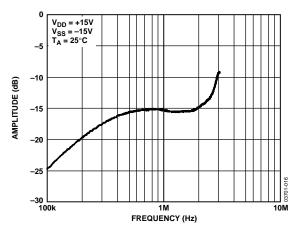

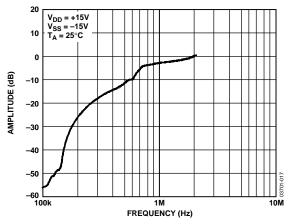

Figure 16. Force Amplifier AC PSRR, Mode 3, C<sub>COMP</sub> = 100 pF

Datasheet of AD5520JSTZ - IC PPMU SNGL-CH 64-LQFP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

Figure 17. Voltage Sense Amplifier AC PSRR

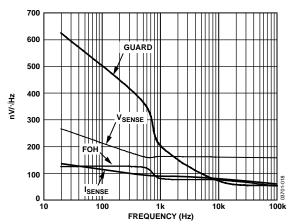

Figure 18. Noise Spectral Density

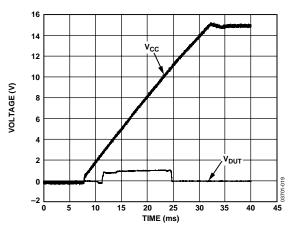

Figure 19. Power Up

Figure 20. Settling Time, Mode 2

Datasheet of AD5520JSTZ - IC PPMU SNGL-CH 64-LQFP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

AD5520

# THEORY OF OPERATION

The AD5520 is a single-channel per pin parametric measurement unit (PPMU) for use in semiconductor automatic test equipment. It contains programmable modes to force a pin voltage and measure the corresponding current (FVMI), force current measure voltage (FIMV), force current measure current (FIMI), force voltage measure voltage (FVMV), and force nothing measure voltage (FNMV). The PPMU can force or measure a voltage from -11~V to +11~V. It can force or measure currents up to 6 mA using the internal amplifier, while the addition of an external amplifier enables higher current ranges. External resistors allow users to choose the optimum ranges for their needs.

The device provides a force sense capability to ensure accuracy at the tester pin. A guard output is also available to drive the shield of a force/sense pair.

The AD5520 has an on-board window comparator that provides two bits of useful information, DUT too low or too high. Also provided on the chip is clamp circuitry that flags via CLHDETECT and CLLDETECT if the voltage applied to FIN or across the DUT exceeds the voltage applied to CLL and CLH.

On-chip is clamp circuitry that clamps the output of the force amplifier if the voltage at MEASIOUT and MEASVOUT exceeds CLL or CLH.

Datasheet of AD5520JSTZ - IC PPMU SNGL-CH 64-LQFP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

### AD5520

### INTERFACE

The AD5520 PPMU is controlled via a number of digital inputs, which are discussed in detail in the following sections. All inputs are TTL-compatible.  $\overline{CS}$  is used to select the device while  $\overline{STB}$  (active low input) latches data available on the other digital inputs and updates any required digital outputs. The rising edge of  $\overline{STB}$  triggers sequence inputs. The remaining digital inputs control the function of the PMU. They also determine which measure mode the PMU is in, the compensation capacitor used, and the selected current range.

#### **STANDBY MODE**

The AD5520 can be placed into standby mode via the standby logic input. In this mode, the force amplifier is disconnected from the force input (FIN). In addition, the switch in series with the force output pins (FOHx) is opened, and the current measure amplifier is disconnected from the sense resistors. The voltage measure amplifier is still connected across the DUT; therefore, DUT voltage measurements may still be made while in standby mode. Figure 21 shows the configuration of the PMU while in standby mode.

Table 5. Standby Mode

| Standby | Function          |

|---------|-------------------|

| Low     | Normal Force Mode |

| High    | Standby Mode      |

Figure 21. PMU in Standby Mode

#### **FORCE VOLTAGE OR FORCE CURRENT**

FSEL is an input that determines whether the PPMU forces a voltage or current.

**Table 6. FSEL Function**

| FSEL | Function                                              |

|------|-------------------------------------------------------|

| Low  | Voltage Force and Current Clamp with MEASIOUT Voltage |

| High | Current Force and Voltage Clamp with MEASVOUT Voltage |

#### **MEASURED PARAMETER**

MEASOUT is a muxed output that tracks the sensed parameter. MSEL (digital input) connects the MEASOUT to the output of the current sense amplifier or the voltage sense amplifier, depending on which is the measured parameter of interest.

The MEASOUT pin is connected back to an ADC to allow the measured value to be converted to a digital code.

Table 7. MEASOUT Connected to Voltage or Current

| MSEL | Function              |

|------|-----------------------|

| Low  | MEASOUT = DUT Voltage |

| High | MEASOUT = DUT Current |

The MEASOUT pin can also be made high impedance through the MOEB logic input.

Table 8. MOEB Allows MEASOUT to Go High Impedance

| MOEB | Function              |

|------|-----------------------|

| Low  | Enable MEASOUT Output |

| High | Hi-Z MEASOUT Output   |

#### **CURRENT RANGES**

A number of current ranges are possible with the AD5520. The AM0, AM1, and AM2 pins are digital inputs used to establish full-scale current range of the PMU.

Table 9. Selection of Current Range

|      | <u> </u> |      |                                               |  |

|------|----------|------|-----------------------------------------------|--|

| AMO  | AM1      | AM2  | Function                                      |  |

| Low  | Low      | Low  | Current Range MODE0 (4 µA)                    |  |

| High | Low      | Low  | Current Range MODE1 (40 μA)                   |  |

| Low  | High     | Low  | Current Range MODE2 (400 μA)                  |  |

| High | High     | Low  | Current Range MODE3 (4 mA)                    |  |

| Low  | Low      | High | Current Range MODE4<br>(External Buffer Mode) |  |

| High | Low      | High | Current Range MODE5<br>(External Buffer Mode) |  |

| Low  | High     | High | Standby (Same as STANDBY = High)              |  |

| High | High     | High | Standby (Same as STANDBY = High)              |  |

|      |          |      |                                               |  |

#### R<sub>c</sub> SELECTION

The AD5520 is designed to ensure the voltage drop across each of the  $R_S$  resistors is less than  $\pm 500$  mV when maximum current is flowing through them. To support other current ranges, these sense resistor values can be changed. The force amplifier can drive a maximum of 6 mA. It is not recommended to increase the maximum current above the nominal range.

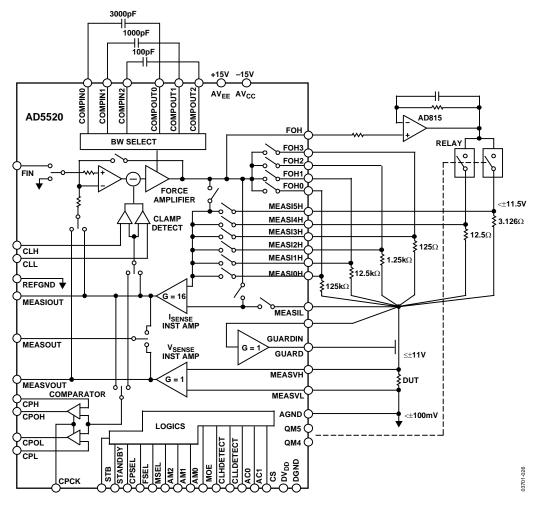

The two external current ranges use an external buffer to drive higher current. The example in Figure 26 uses 40 mA and 160 mA ranges. These ranges can be changed to suit user requirements for a high current range.

Datasheet of AD5520JSTZ - IC PPMU SNGL-CH 64-LQFP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

AD5520

#### **FORCE CONTROL AMPLIFIER**

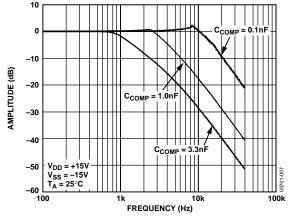

The force control amplifier requires external capacitors connected between the COMPOUTx and COMPINx pins. For stability with large capacitance at the DUT, the largest capacitance value (3000 pF) should be selected. The force control amplifier should always contribute the dominant pole in the control loop. Settling times increase with larger capacitances. ACx inputs select which external compensation capacitor is used.

Table 10. AC0, AC1 Compensation Capacitor Selection

| AC0  | AC1  | Function                                 |

|------|------|------------------------------------------|

| Low  | Low  | Select External Compensation Capacitor 0 |

| High | Low  | Select External Compensation Capacitor 1 |

| Low  | High | Select External Compensation Capacitor 2 |

#### **COMPARATOR FUNCTION AND STROBING**

The AD5520 has an on-board window comparator that provides two bits of useful information, DUT too low or DUT too high. CPSEL is the digital input that controls this function, selecting whether it should compare to the voltage sense or the current sense amplifier.

**Table 11. Comparator Function Select**

| CPSEL | Function                     |

|-------|------------------------------|

| Low   | Compare CPL, CPH to MEASVOUT |

| High  | Compare CPL, CPH to MEASIOUT |

After CPSEL has selected which amplifier output is of interest, logic input CPCK is used to initiate comparator sampling and update the logic outputs CPOH and CPOL. This indicates whether the voltages at MEASIOUT or MEASVOUT have exceeded voltages set at CPL or CPH (thus providing DUT too high or DUT too low information). A rising edge on STB is required to clock the CPOH and CPOL data out.

**Table 12. CPCK Synchronous Logic Outputs**

| СРОН        | Function                                              |  |

|-------------|-------------------------------------------------------|--|

| Low<br>High | MEASVOUT or MEASIOUT < CPH MEASVOUT or MEASIOUT > CPH |  |

| CPOL        | Function                                              |  |

| Low<br>High | MEASVOUT or MEASIOUT > CPL MEASVOUT or MEASIOUT < CPL |  |

#### **CLAMP FUNCTION**

Clamp circuitry, which is also included on-chip, clamps the force amplifier's output if the voltage or current applied to the DUT exceeds the clamp levels, CLL and CLH. The clamp circuitry also comes into play in the event of a short or open circuit. When in force current range, the voltage clamps protect the DUT from an open circuit. Likewise, when forcing a voltage and a short circuit occurs, the current clamps protect the DUT. The clamps also function to protect the DUT if a transient voltage or current spike occurs when changing to a different operating mode, or when programming the device to a different current range.

The digital output flags, which indicate a clamp limit has been hit, are CLHDETECT for the upper clamp, and CLLDETECT output for the lower clamp.

Table 13. Clamp Detect Outputs

| CLHDETECT | Function             |

|-----------|----------------------|

| Low       | Upper Clamp Inactive |

| High      | Upper Clamp Active   |

| CLLDETECT | Function             |

| Low       | Lower Clamp Inactive |

| High      | Lower Clamp Active   |

#### **HIGH CURRENT RANGES**

With the use of an external high current amplifier, two high current ranges are possible. The current range values can be set as required in the application through appropriate selection of the sense resistors connected between MEASI5H, MEASI4H, and MEASIL. When one of these high current ranges (Mode 4 or Mode 5) is selected via the AMx control lines, the appropriate QM4 or QM5 output is enabled. As a result, these outputs can be used to control relays connected in series with the high current amplifier, as shown in Figure 26.

Table 14. High Current Range Logic Outputs

| QM4  | QM5  | Function                           |

|------|------|------------------------------------|

| High | Low  | Current Range Mode 4 Enable Output |

| Low  | High | Current Range Mode 5 Enable Output |

Datasheet of AD5520JSTZ - IC PPMU SNGL-CH 64-LQFP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

# AD5520

### CIRCUIT OPERATION

#### **FORCE VOLTAGE**

Most PMU measurements are performed while in force voltage and measure current modes; for example, when the device is used as a device power supply, or in continuity or leakage testing. In the force voltage mode, the voltage at analog input FIN is mapped directly to the voltage forced at the DUT.

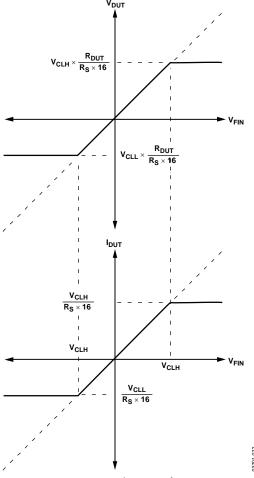

When in force voltage and measure current modes, the maximum voltage applied to the input corresponds to the maximum current outputs. Figure 22 shows the transfer function when forcing a voltage.

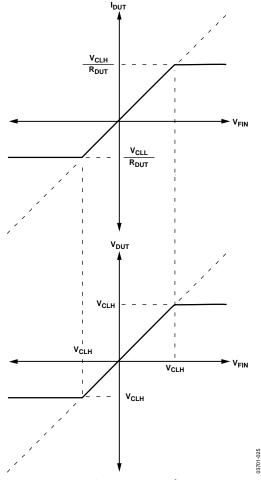

Figure 22. Force Voltage Transfer Function

#### **MEASURE CURRENT**

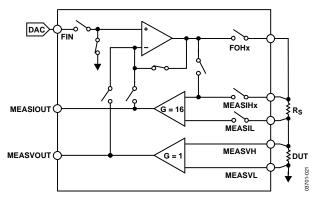

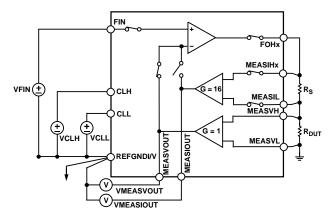

Figure 23 shows a simplified diagram of the PMU when in force voltage mode. The control loop consists of the force amplifier with the voltage sense amplifier making up the feedback path. Current flowing through the DUT is measured by sensing the current flowing through a selectable sense resistor, which is in series with the DUT. The current sense amplifier (Gain = 16) generates a voltage at its output, which is proportional to the current flowing through the DUT. This voltage is compared to the CLL and CLH levels to ensure the clamp voltages have not been exceeded. Strobing CPCK and  $\overline{\text{STB}}$  provides information about the voltage level with respect to the comparator levels, CPH and CPL.

| CONDITION | $\begin{aligned} &V_{CLH} > I_{DUT} \times R_S \times 16 \\ &V_{CLL} < I_{DUT} \times R_S \times 16 \end{aligned}$ | $\begin{aligned} &V_{CLH} < I_{DUT} \times R_S \times 16 \\ &V_{CLL} < I_{DUT} \times R_S \times 16 \end{aligned}$ | $V_{CLH} > I_{DUT} \times R_S \times 16$<br>$V_{CLL} > I_{DUT} \times R_S \times 16$ | 23    |

|-----------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------|

| OUTPUT    | V <sub>DUT</sub> = V <sub>FIN</sub>                                                                                | V <sub>DUT</sub> = V <sub>CLH</sub>                                                                                | V <sub>DUT</sub> = V <sub>CLL</sub>                                                  | 701-0 |

Figure 23. Force Voltage, Measure Current Mode

Datasheet of AD5520JSTZ - IC PPMU SNGL-CH 64-LQFP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

AD5520

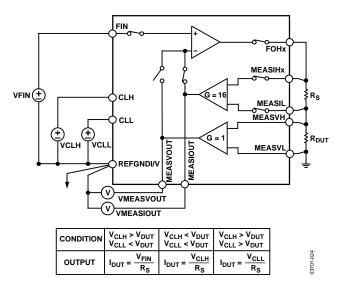

#### **FORCE CURRENT**

In force current mode, the voltage at FIN is now converted to a current through the following relationship:

Force Current =  $V_{FIN}/(R_{SENSE} \times 16)$

Figure 24 shows a simplified diagram of the PMU when in force current mode. The control loop consists of the force amplifier with the current sense amplifier making up the feedback path. In this case, voltage at the DUT is sensed across the voltage measure amplifier (Gain = 1) and presented at the MEASVOUT output.

Figure 24. Current Force, Voltage Measure Mode

#### **MEASURE VOLTAGE**

A DUT voltage is tested via the voltage measure amplifier by a window comparator to ensure that CPH and CPL levels are not exceeded. In addition, the DUT voltage is automatically tested against the voltage levels at the clamp, and clamp flags are enabled if the DUT voltage exceeds either of the levels.

#### **SHORT CIRCUIT PROTECTION**

The AD5520 is designed to withstand a direct short circuit on any of the amplifier outputs.

Figure 25 illustrates the transfer function of the current force mode.

Figure 25. Current Force Transfer Function

Datasheet of AD5520JSTZ - IC PPMU SNGL-CH 64-LQFP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

### AD5520

### **SETTLING TIME CONSIDERATIONS**

Fast throughput is a key requirement in automatic test equipment because it relates directly to the cost of manufacturing the DUT; thus reducing the time required to make a measurement is of greatest importance. When taking measurements using a PMU, the limiting factor is usually the time it takes the output to settle to the required accuracy so a measurement can be taken. DUT capacitance, measurement accuracy, and the design of the PMU are the major contributors to this time.

Figure 26 shows a simplified block diagram of the AD5520 PMU. In brief, the device consists of a force control amplifier, access to a number of selectable sense resistors, a voltage measure instrumentation amplifier, and a current measure instrumentation amplifier. To optimize the performance of the device, there are also nodes provided where external compensation capacitors are added. As mentioned, making an accurate measurement in the fastest time while avoiding overshoots and ringing is the key requirement in any automatic test equipment (ATE) system. Doing so provides challenges, however. The external compensation capacitors set up different settling times or bandwidths on the force control amplifier, and while one compensation capacitor value may suit one range, it may not suit other ranges. To optimize measurement performance and speed, differences in signal behavior on each range and frequency of use of each range need to be taken into account.

When selecting a faster settling time, there is a trade-off. A small compensation value results in faster settling, but may incur penalties in overshoots or ringing at the DUT. Compensation capacitor selection should be optimized to ensure minimum overshoots while still giving decent settling time performance.

While careful selection of the compensation capacitor is required to minimize the settling time, another factor can greatly contribute to the overall settling of the loop if the feedback loop is broken in some manner, and the force control amplifier goes to either the positive or negative rails. There is a finite amount of time required for the amplifier to recover from this condition, typically 85  $\mu$ s, which adds to the settling of the loop. Ensuring that the force control amplifier never goes into saturation is the best solution. This solution can be helped by putting the device into standby mode any time the operating mode or range selection is changed. In addition, ensure that the selected output range can supply the required current needed by the DUT.

Datasheet of AD5520JSTZ - IC PPMU SNGL-CH 64-LQFP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

AD5520

# PCB LAYOUT AND POWER SUPPLY DECOUPLING

In any circuit where accuracy is important, careful consideration to the power supply and the ground return layout helps to ensure the rated performance. The printed circuit board on which the AD5520 is mounted should be designed so that the analog and digital sections are separated and confined to certain areas of the board. If the PMU is in a system where multiple devices require an AGND-to-DGND connection, the connection should be made at one point only. The star ground point should be established as close as possible to the device.

This PMU should have ample supply bypassing of 10  $\mu F$  in parallel with 0.1  $\mu F$  on the supply and should be located as close as possible to the package, ideally right up against the device. The 0.1  $\mu F$  capacitor should have low effective series resistance (ESR) and effective series inductance (ESI), such as the common ceramic types that provide a low impedance path to ground at high frequencies, to handle transient currents due to internal logic switching. Low ESR (1  $\mu F$  to 10  $\mu F$ ) tantalum or electrolytic capacitors should also be applied at the supplies to minimize transient disturbance and filter out low frequency ripple.

Fast switching signals, such as clocks, should be shielded with digital ground to avoid radiating noise to other parts of the board and should never be run near the reference inputs.

Avoid crossover of digital and analog signals. Traces on opposite sides of the board should run at right angles to each other. This reduces the effects of feedthrough through the board. A microstrip technique is by far the best but not always possible with a double-sided board. In this technique, the component side of the board is dedicated to the ground plane while signal traces are placed on the solder side.

It is good practice to use compact, minimum lead length PCB layout design. Leads to the input should be as short as possible to minimize IR drops and stray inductance.

Datasheet of AD5520JSTZ - IC PPMU SNGL-CH 64-LQFP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

# AD5520

# TYPICAL CONNECTION CIRCUIT FOR THE AD5520

Figure 26 shows the AD5520 as connected in a typical application. The external components required are three compensation capacitors and six sense resistors, depending on the number of ranges required. If high current ranges >6 mA are required, an external amplifier must be used with relays (or some form of high current switch) to switch in the different current ranges to the DUT. Other components are also required to make the PMU function.

The PMU requires a number of discrete voltage levels: five DAC levels for each PMU used in the system, two levels each for the comparator and clamps, and one voltage level for the AD5520 force input voltage. To use the information measured at the DUT, an ADC such as the AD7665 (a 16-bit ADC), must be connected to the MEASOUT pin to convert the measured current or voltage to digital for analysis.

Figure 26. Typical Configuration of the AD5520 as Used in an ATE Circuit

Datasheet of AD5520JSTZ - IC PPMU SNGL-CH 64-LQFP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

AD5520

# TYPICAL APPLICATION CIRCUIT

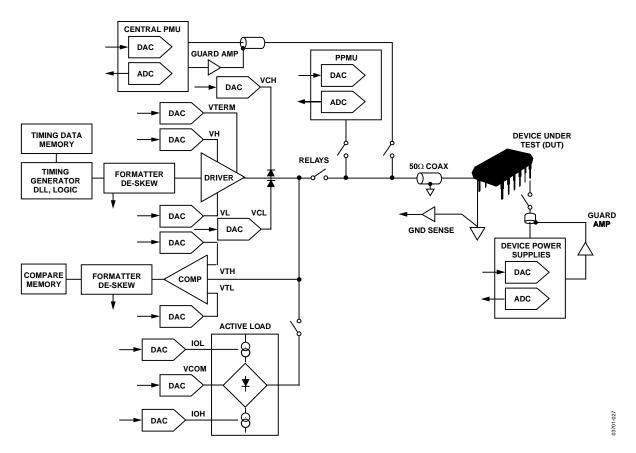

Figure 27 shows the AD5520 as in an ATE system. This device can used as a per pin parametric unit in order to speed up the rate at which testing can be done. It can also be used as a DUT power supply, as shown in the application circuit.

The central PMU shown in the block diagram (Figure 27) is usually a highly accurate PMU and is shared among a number of pins in the tester. In general, many discrete levels are required in an ATE system for the pin drivers, comparators, clamps, and active loads. DAC devices, such as the AD5379, offer a highly integrated solution for a number of these levels. The AD5379 is a dense 40-channel DAC designed with high channel requirements, such as ATE.

The flexible function of the AD5520 also makes it suited for use in instrumentation applications such as source measure units. Source measure units are programmable instruments capable of sourcing and measuring voltage or current simultaneously. The AD5520 provides a more integrated solution in such equipment.

Figure 27. Typical Application ATE Circuit

Datasheet of AD5520JSTZ - IC PPMU SNGL-CH 64-LQFP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

### AD5520

# **EVALUATION BOARD FOR THE AD5520**

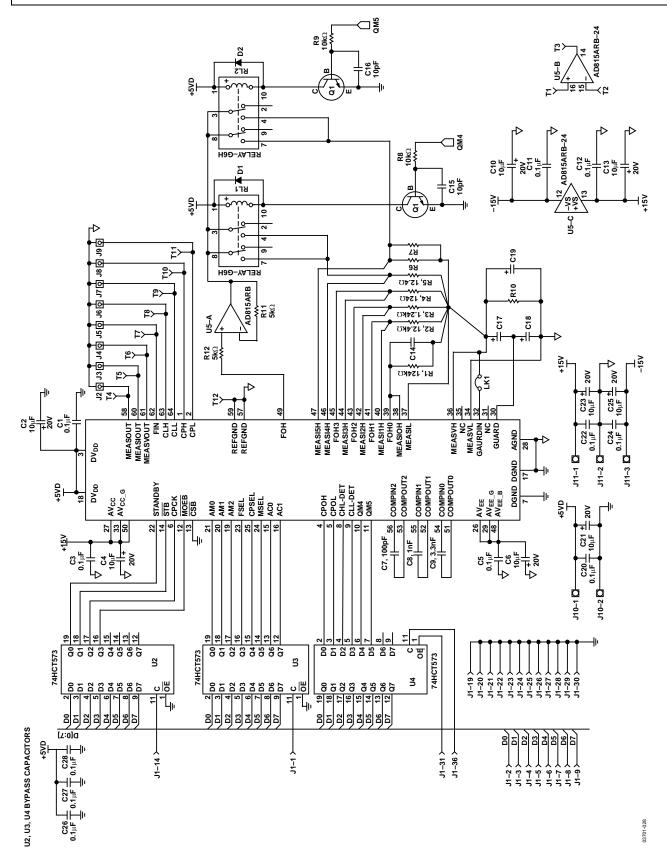

A full-featured evaluation kit is available for the AD5520. It includes an evaluation board with direct hookup via a 36-way Centronics connector to a PC. PC-based software to control the AD5520 is also part of the evaluation kit. The evaluation board schematic is shown in Figure 28.

Note that  $V_{\rm DD}$  and  $V_{\rm SS}$  must provide sufficient headroom for the force and measure voltage range. In addition to the supply voltages for the evaluation board, it is necessary to provide the voltage levels for the clamp, comparator, and the force input pins (CLL, CLH, CPL, CPH, and FIN). SMB connections are provided for these voltage inputs. To use the evaluation board, it is also necessary to provide a DUT connected via the gold pins.

Both AGND and DGND inputs are provided on the board. The AGND and DGND planes are connected at one location close to the AD5520. It is recommended not to connect AGND and DGND elsewhere in the system to avoid ground loop problems. REFGND is routed back to AGND at the power block to maintain a clean ground reference for accurate measurements.

Each supply is decoupled to the relevant ground plane with  $10~\mu F$  and  $0.1~\mu F$  capacitors. The device supply pin is again decoupled with a  $10~\mu F$  and  $0.1~\mu F$  capacitor pair to the relevant ground plane.

Care should be taken when replacing devices to ensure that the pins line up correctly with the PCB pads.

Figure 28. Evaluation Board Schematic

Datasheet of AD5520JSTZ - IC PPMU SNGL-CH 64-LQFP

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

# AD5520

**Preliminary Technical Data**

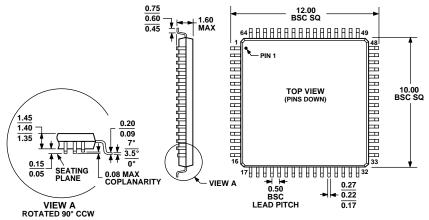

# **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MS-026-BCD

Figure 29. 64-Lead Low Profile Quad Flat Package [LQFP] (ST-64-2) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model                        | Temperature Range | Package Description                          | Package Option |

|------------------------------|-------------------|----------------------------------------------|----------------|

| AD5520JST                    | 0°C to 70°C       | 64-Lead Low Profile Quad Flat Package [LQFP] | ST-64-2        |

| AD5520JST-REEL               | 0°C to 70°C       | 64-Lead Low Profile Quad Flat Package [LQFP] | ST-64-2        |

| AD5520JSTZ-REEL <sup>1</sup> | 0°C to 70°C       | 64-Lead Low Profile Quad Flat Package [LQFP] | ST-64-2        |

| EVAL-AD5520EB                |                   | Evaluation Board and Software                |                |

<sup>&</sup>lt;sup>1</sup> Z = Pb-free part.