## **Excellent Integrated System Limited**

Stocking Distributor

Click to view price, real time Inventory, Delivery & Lifecycle Information:

[Xilinx](#)

[HW-XGI-VIDEO-US](#)

For any questions, you can email us directly:

[sales@integrated-circuit.com](mailto:sales@integrated-circuit.com)

# Video Input/Output Daughter Card

## *User Guide*

UG235 (v1.2.1) October 31, 2007

Xilinx is disclosing this user guide, manual, release note, and/or specification (the "Documentation") to you solely for use in the development of designs to operate with Xilinx hardware devices. You may not reproduce, distribute, republish, download, display, post, or transmit the Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors contained in the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU "AS-IS" WITH NO WARRANTY OF ANY KIND. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

© 2006–2007 Xilinx, Inc. All rights reserved.

XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

## Revision History

### Video Input/Output Daughter Card UG235 (v1.2.1) October 31, 2007

The following table shows the revision history for this document.

|          | <b>Version</b> | <b>Revision</b>                                                   |

|----------|----------------|-------------------------------------------------------------------|

| 01/25/06 | 1.0            | Initial Xilinx release.                                           |

| 02/13/06 | 1.1            | Added two sentences to pages 17 and 43.                           |

| 02/23/07 | 1.2            | Corrected 3 pins and column 6 heading in Table A-2.               |

| 10/31/07 | 1.2.1          | Defined the following acronyms on p. 48: EAV, CRC, NTSC, and PAL. |

# Contents

---

## Preface: About This Guide

|                            |    |

|----------------------------|----|

| Guide Contents .....       | 11 |

| Additional Resources ..... | 11 |

| Conventions .....          | 12 |

| Typographical.....         | 12 |

| Online Document.....       | 13 |

## Chapter 1: VIODC Overview

|                              |    |

|------------------------------|----|

| Introduction .....           | 15 |

| Video Interface Support..... | 16 |

## Chapter 2: VIODC to ML402 Card Interface

|                                |    |

|--------------------------------|----|

| VIOBUS Clocking .....          | 19 |

| VIOBUS Signal Definitions..... | 20 |

## Chapter 3: Component and S-Video Interfaces

|                                                  |    |

|--------------------------------------------------|----|

| Overview .....                                   | 21 |

| ADV7403 Video Decoder .....                      | 21 |

| ADV7321 Video Encoder .....                      | 22 |

| Video Signal Input and Output Conditioning ..... | 22 |

| S-Video Input and Output.....                    | 22 |

| S-Video Input .....                              | 22 |

| S-Video Input Signal Conditioning.....           | 22 |

| ADV7403 S-Video Input .....                      | 24 |

| S-Video Output.....                              | 24 |

| ADV7321 S-Video Output.....                      | 24 |

| S-Video Output Signal Conditioning .....         | 24 |

| Composite Video Input and Output .....           | 24 |

| Composite Video Input .....                      | 25 |

| Composite Video Input Conditioning Circuit.....  | 25 |

| ADV7403 Composite Video Input .....              | 25 |

| Composite Video Output .....                     | 25 |

| ADV7321A Composite Video Output.....             | 25 |

| Composite Video Conditioning Circuit .....       | 25 |

| Component Video Input and Output .....           | 26 |

| Component Video Input .....                      | 26 |

| Input Signal Conditioning .....                  | 26 |

| ADV7403 Connection to FPGA.....                  | 26 |

| Component Video Output .....                     | 27 |

| FPGA to ADV7321 Connection.....                  | 27 |

| Analog Output Signal Conditioning.....           | 28 |

| ADV7403 Configuration Modes .....                | 28 |

| ADV7321A Configuration Modes .....               | 30 |

## Chapter 4: DVI/VGA Input Interface

|                                               |    |

|-----------------------------------------------|----|

| <b>Interface Description</b> .....            | 33 |

| DVI Connectivity on VIODC .....               | 33 |

| Signals .....                                 | 33 |

| DVI Interface .....                           | 34 |

| VGA interface .....                           | 34 |

| Display Data Channel .....                    | 34 |

| <b>AD9887 Overview</b> .....                  | 34 |

| Analog Interface .....                        | 34 |

| Digital Interface .....                       | 34 |

| <b>VGA Standard Overview</b> .....            | 35 |

| <b>Setting the PLL and Phase</b> .....        | 36 |

| Setting Black Levels .....                    | 37 |

| Setting Gain .....                            | 37 |

| <b>Bus Interface</b> .....                    | 37 |

| DVI Input .....                               | 38 |

| I2C Initialization Table (in Hex) .....       | 38 |

| DVI .....                                     | 40 |

| <b>References to VGA, DVI Standards</b> ..... | 40 |

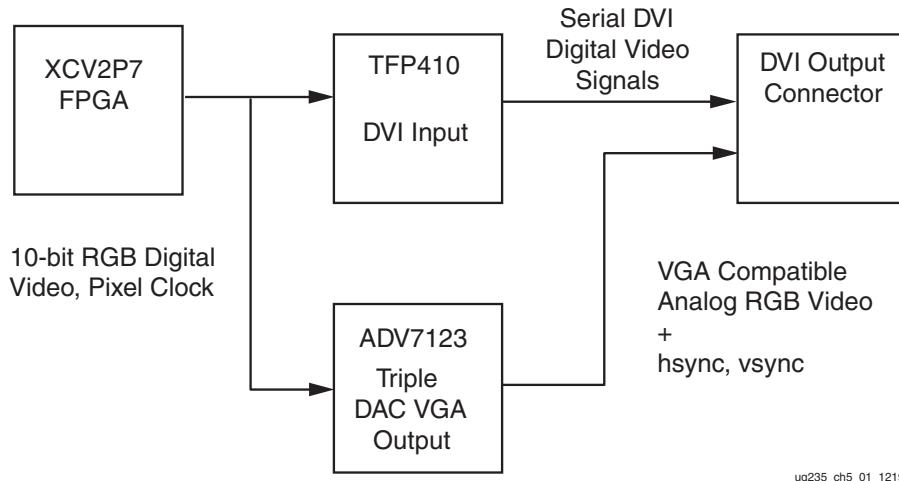

## Chapter 5: DVI/VGA Output Interface

|                                       |    |

|---------------------------------------|----|

| <b>Overview</b> .....                 | 41 |

| <b>TPF410 I2C Configuration</b> ..... | 42 |

## Chapter 6: SDI Interface

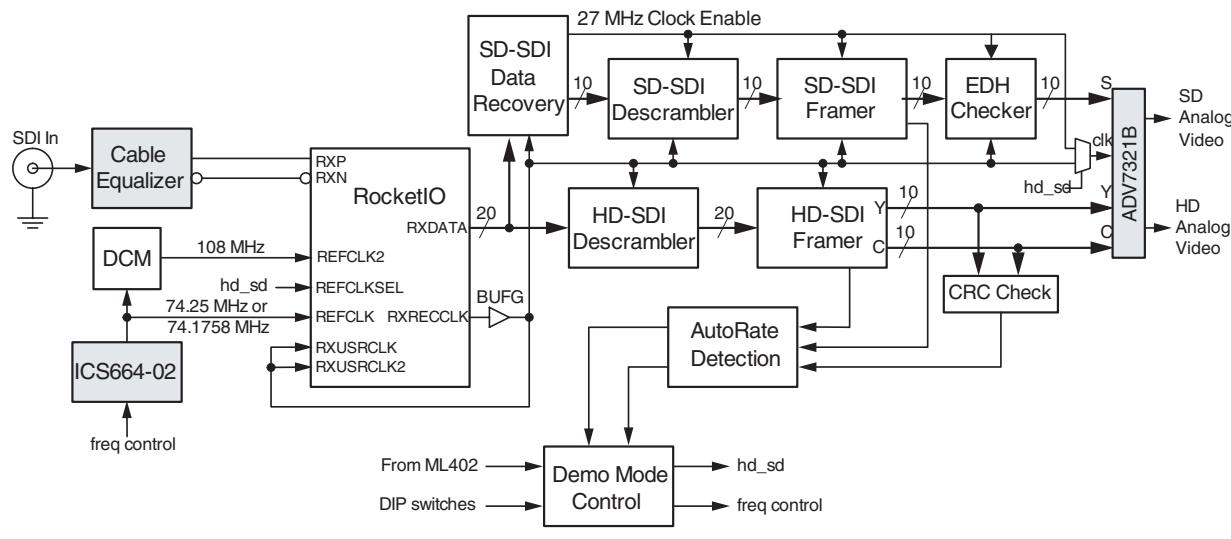

|                                                                  |    |

|------------------------------------------------------------------|----|

| <b>Introduction</b> .....                                        | 43 |

| <b>Reference Clocks</b> .....                                    | 43 |

| <b>SDI Receiver</b> .....                                        | 44 |

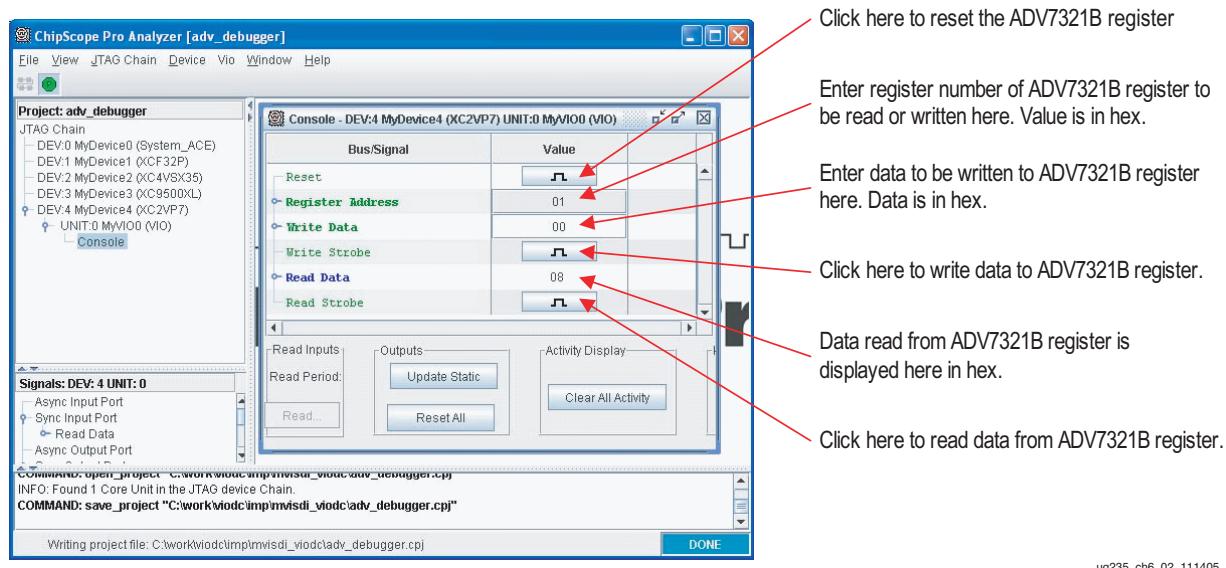

| <b>PicoBlaze Controller for the ADV7321B Video Encoder</b> ..... | 45 |

| <b>SDI Transmitter</b> .....                                     | 48 |

| <b>References</b> .....                                          | 49 |

## Chapter 7: Image Sensor Camera Interface

|                                       |    |

|---------------------------------------|----|

| <b>LVDS Camera Interface</b> .....    | 51 |

| <b>Camera Interface Signals</b> ..... | 51 |

## Chapter 8: Attaching the VIODC to the ML40x Development Board

### Appendix A: Reference Information

|                                             |    |

|---------------------------------------------|----|

| <b>Schematic and Data Sheet Links</b> ..... | 55 |

| <b>VIOBUS Pinouts</b> .....                 | 56 |

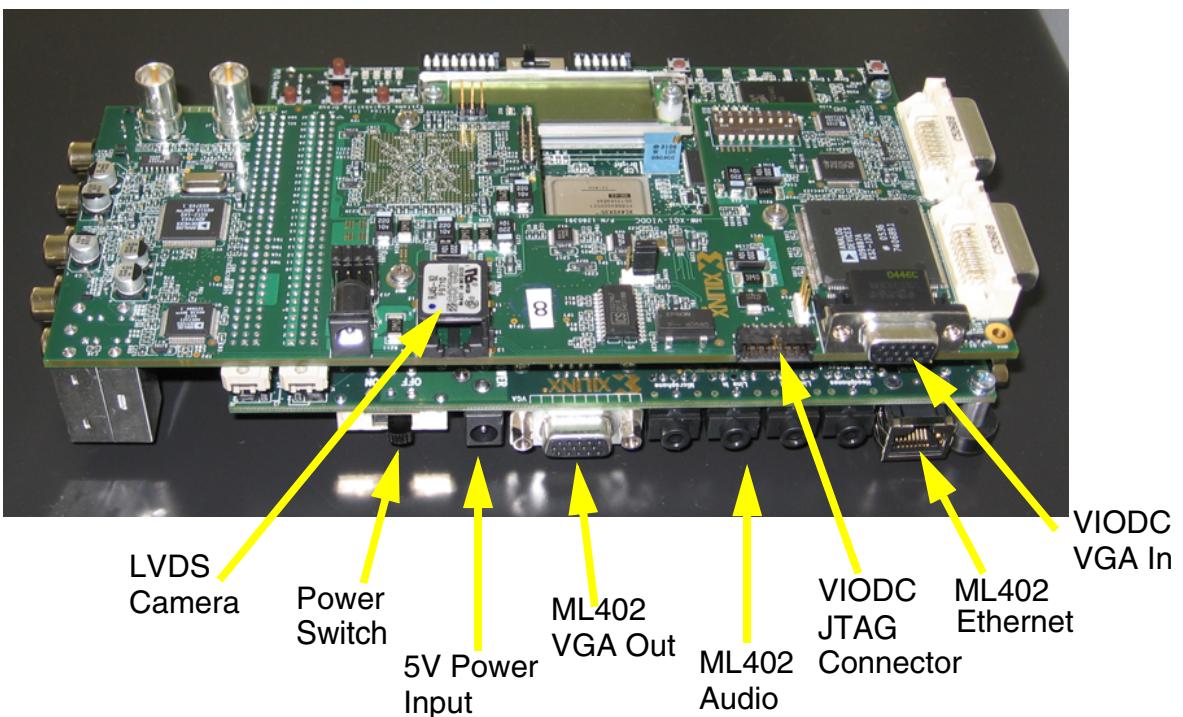

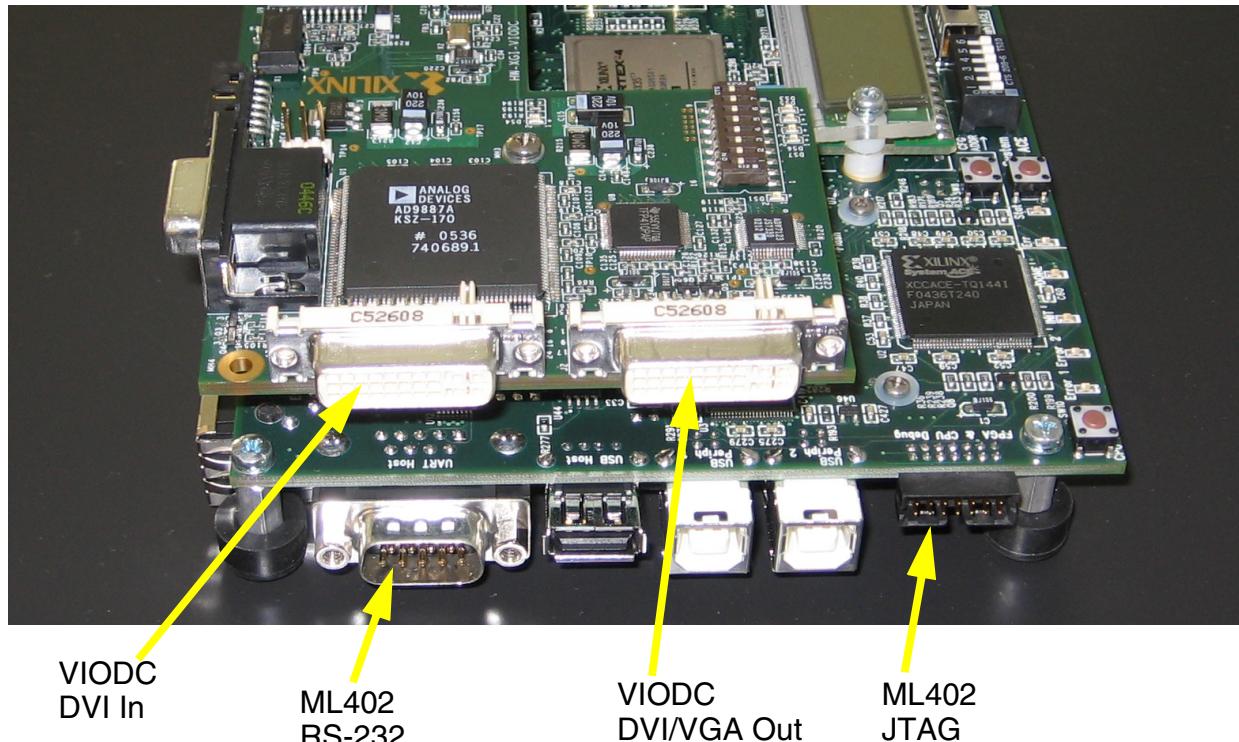

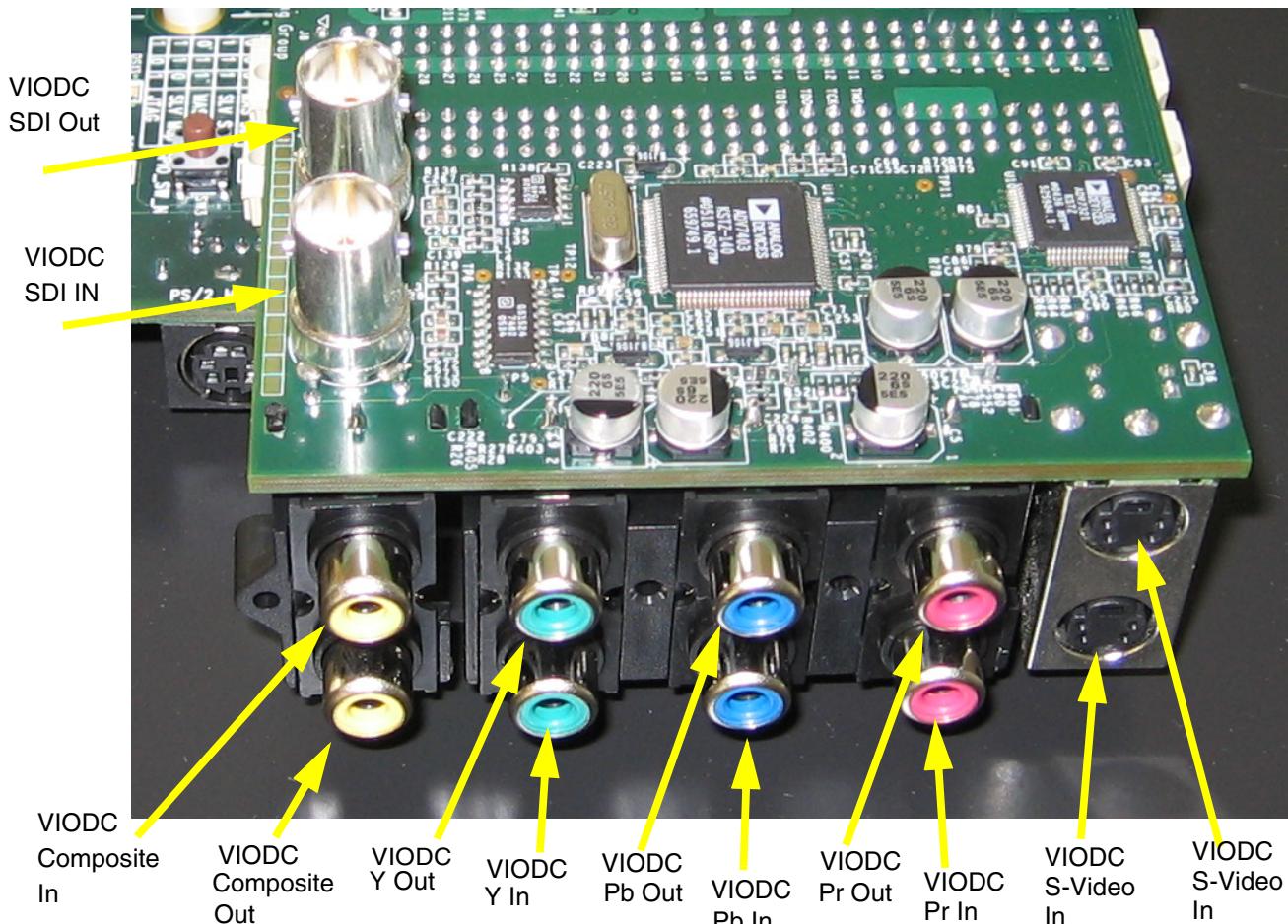

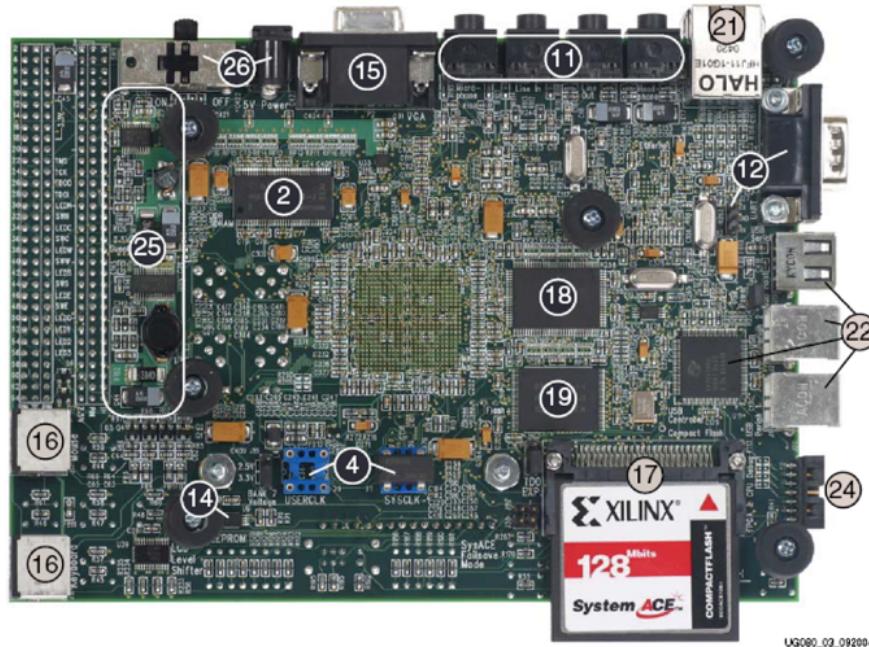

### Appendix B: VSK I/O Connector Location Pictures

|                               |    |

|-------------------------------|----|

| <b>VIODC Connectors</b> ..... | 63 |

|-------------------------------|----|

---

|                          |    |

|--------------------------|----|

| <b>LVDS Camera</b> ..... | 66 |

| <b>ML402 Board</b> ..... | 67 |

---

# *Schedule of Figures*

---

## **Chapter 1: VIODC Overview**

|                                                              |    |

|--------------------------------------------------------------|----|

| <i>Figure 1-1: VIODC Attached to an ML402 Platform</i> ..... | 15 |

| <i>Figure 1-2: VIODC Block Diagram</i> .....                 | 16 |

## **Chapter 2: VIODC to ML402 Card Interface**

|                                          |    |

|------------------------------------------|----|

| <i>Figure 2-1: VIOBUS Clocking</i> ..... | 19 |

|------------------------------------------|----|

## **Chapter 3: Component and S-Video Interfaces**

|                                                                                                         |    |

|---------------------------------------------------------------------------------------------------------|----|

| <i>Figure 3-1: S-Video, Composite, and Component Video Input and Output Block Diagram</i> .....         | 21 |

| <i>Figure 3-2: S-Video, Composite, and Component Input and Output Signal Conditioning Circuit</i> ..... | 23 |

| <i>Figure 3-3: Component Video Input</i> .....                                                          | 26 |

| <i>Figure 3-4: Connections from ADV7403 Video Decoder to XC2VP4 FGPA</i> .....                          | 27 |

| <i>Figure 3-5: Component Video Output Block Diagram</i> .....                                           | 27 |

## **Chapter 4: DVI/VGA Input Interface**

|                                                                  |    |

|------------------------------------------------------------------|----|

| <i>Figure 4-1: DVI Connectivity on VIODC Block Diagram</i> ..... | 33 |

| <i>Figure 4-2: VGA Interface</i> .....                           | 35 |

| <i>Figure 4-3: Synchronization Signaling</i> .....               | 35 |

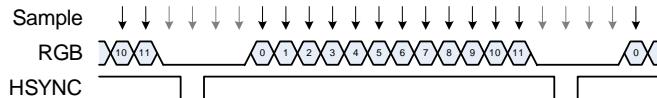

| <i>Figure 4-4: Pixel Sampling</i> .....                          | 36 |

| <i>Figure 4-5: Ideal ADC Sampling Positions</i> .....            | 37 |

## **Chapter 5: DVI/VGA Output Interface**

|                                                                       |    |

|-----------------------------------------------------------------------|----|

| <i>Figure 5-1: DVI/VGA Video Output Interface Block Diagram</i> ..... | 41 |

|-----------------------------------------------------------------------|----|

## **Chapter 6: SDI Interface**

|                                                        |    |

|--------------------------------------------------------|----|

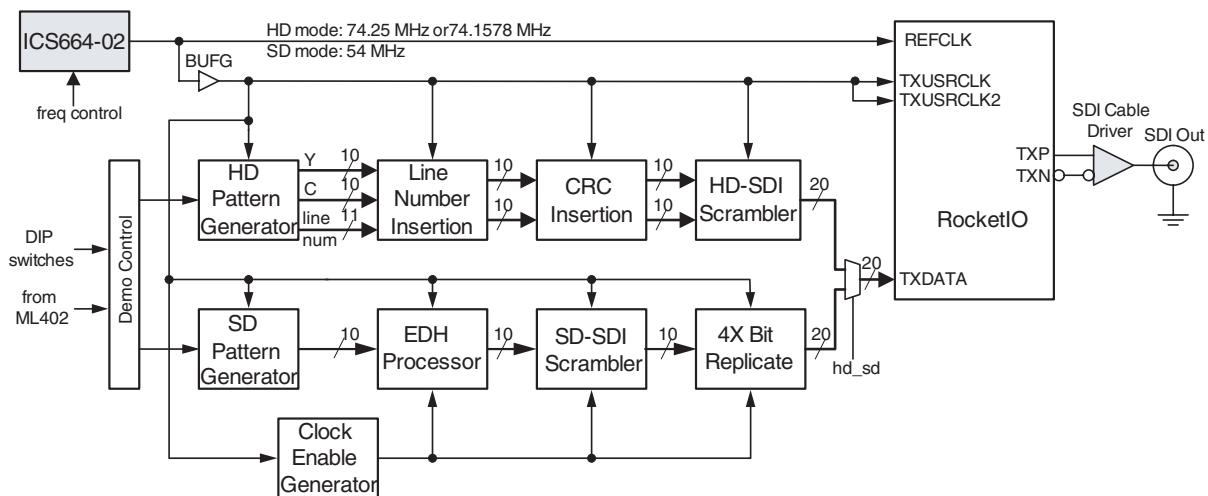

| <i>Figure 6-1: SDI Receiver Block Diagram</i> .....    | 44 |

| <i>Figure 6-2: ADV7321B Debugger</i> .....             | 46 |

| <i>Figure 6-3: SDI Transmitter Block Diagram</i> ..... | 48 |

## **Chapter 7: Image Sensor Camera Interface**

|                                                |    |

|------------------------------------------------|----|

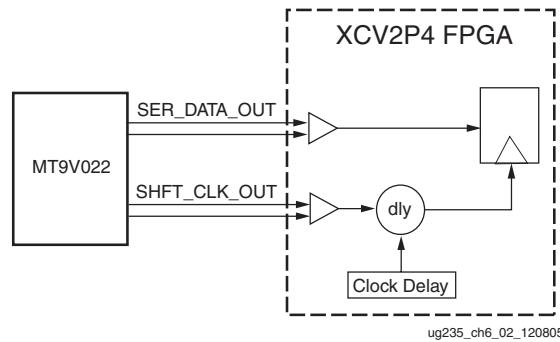

| <i>Figure 7-1: LVDS Camera Interface</i> ..... | 51 |

| <i>Figure 7-2: Camera Clock</i> .....          | 52 |

## **Chapter 8: Attaching the VIODC to the ML40x Development Board**

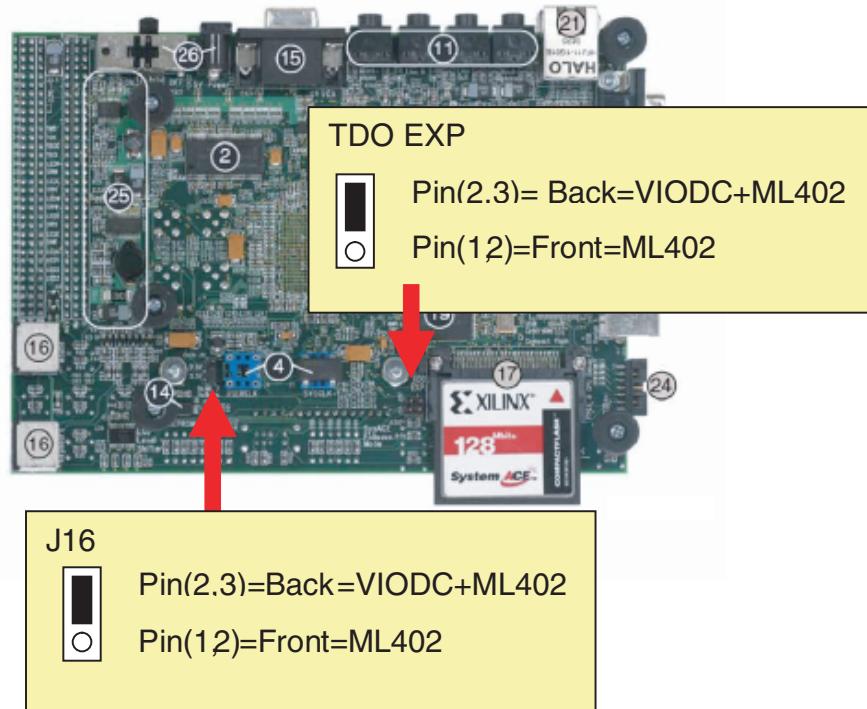

|                                                                                                                             |    |

|-----------------------------------------------------------------------------------------------------------------------------|----|

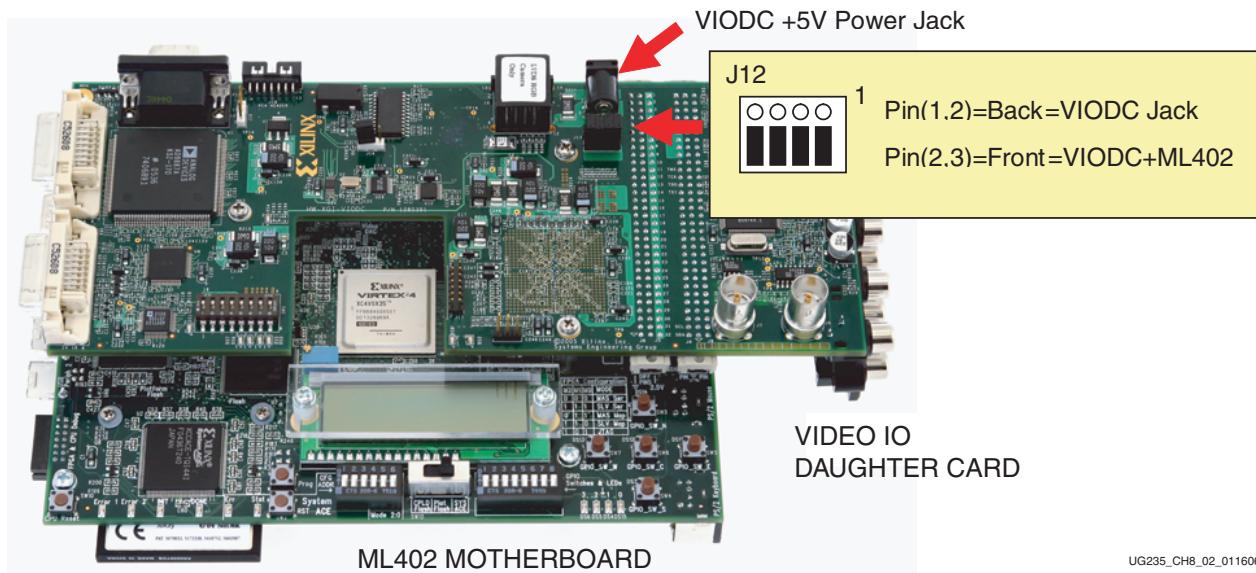

| <i>Figure 8-1: Configuration Jumper Locations on the ML40x Bottom, Configured for VIODC Mounted to an ML402 Board</i> ..... | 54 |

|-----------------------------------------------------------------------------------------------------------------------------|----|

---

|                                                                                                                              |    |

|------------------------------------------------------------------------------------------------------------------------------|----|

| <i>Figure 8-2: Configuration Jumper Locations on the VIODC Top,<br/>Configured for VIODC Mounted to an ML402 Board .....</i> | 54 |

|------------------------------------------------------------------------------------------------------------------------------|----|

## Appendix A: Reference Information

## Appendix B: VSK I/O Connector Location Pictures

|                                                   |    |

|---------------------------------------------------|----|

| <i>Figure B-1: VIODC Rear View.....</i>           | 63 |

| <i>Figure B-2: VIODC Left Side View.....</i>      | 64 |

| <i>Figure B-3: VIODC Right Side View .....</i>    | 65 |

| <i>Figure B-4: LVDS Camera.....</i>               | 66 |

| <i>Figure B-5: ML402 Board.....</i>               | 67 |

| <i>Figure B-6: ML402 Evaluation Platform.....</i> | 68 |

---

# *Schedule of Tables*

---

## **Chapter 1: VIODC Overview**

## **Chapter 2: VIODC to ML402 Card Interface**

|                                                   |    |

|---------------------------------------------------|----|

| <i>Table 2-1: VIOBUS Signal Definitions</i> ..... | 20 |

|---------------------------------------------------|----|

## **Chapter 3: Component and S-Video Interfaces**

|                                                                             |    |

|-----------------------------------------------------------------------------|----|

| <i>Table 3-1: Configuration Modes for ADV7403 Video Decoder Chip</i> .....  | 28 |

| <i>Table 3-2: Configuration Modes for ADV7321A Video Encoder Chip</i> ..... | 30 |

## **Chapter 4: DVI/VGA Input Interface**

|                                       |    |

|---------------------------------------|----|

| <i>Table 4-1: VGA Standards</i> ..... | 36 |

| <i>Table 4-2: Analog VGA60</i> .....  | 38 |

| <i>Table 4-3: Analog XGA60</i> .....  | 39 |

| <i>Table 4-4: Analog SXGA60</i> ..... | 39 |

| <i>Table 4-5: Analog UXGA60</i> ..... | 39 |

| <i>Table 4-6: DVI</i> .....           | 40 |

## **Chapter 5: DVI/VGA Output Interface**

|                                                                               |    |

|-------------------------------------------------------------------------------|----|

| <i>Table 5-1: Configuration Modes for TPF410 I2C Video Encoder Chip</i> ..... | 42 |

|-------------------------------------------------------------------------------|----|

## **Chapter 6: SDI Interface**

|                                                                                     |    |

|-------------------------------------------------------------------------------------|----|

| <i>Table 6-1: RocketIO Reference Clock Generation</i> .....                         | 44 |

| <i>Table 6-2: ADV7321B Register Settings for HD</i> .....                           | 46 |

| <i>Table 6-3: ADV7321B HD Mode Register 1 (0x10) Settings by Video Format</i> ..... | 47 |

| <i>Table 6-4: ADV7321B Register Settings for NTSC</i> .....                         | 47 |

| <i>Table 6-5: ADV7321B Register Settings for PAL</i> .....                          | 47 |

## **Chapter 7: Image Sensor Camera Interface**

|                                                  |    |

|--------------------------------------------------|----|

| <i>Table 7-1: Camera Interface Signals</i> ..... | 51 |

|--------------------------------------------------|----|

## **Chapter 8: Attaching the VIODC to the ML40x Development Board**

|                                                   |    |

|---------------------------------------------------|----|

| <i>Table 8-1: Required Jumper Positions</i> ..... | 53 |

|---------------------------------------------------|----|

## **Appendix A: Reference Information**

|                                                               |    |

|---------------------------------------------------------------|----|

| <i>Table A-1: VIODC ICs</i> .....                             | 55 |

| <i>Table A-2: VIOBUS Signals XGI Header Connections</i> ..... | 56 |

| <i>Table A-3: VIOBUS ML402 FPGA Connections</i> .....         | 58 |

| <i>Table A-4: VIOBUS VIODC FPGA Connections</i> .....         | 60 |

## Appendix B: VSK I/O Connector Location Pictures

## Preface

# About This Guide

This guide describes the Video Input and Output Daughter Card (VIODC), a standard video interface card that is compatible with the Xilinx ML401, ML402, and ML403 development platforms.

## Guide Contents

This manual contains the following chapters:

- [Chapter 1, “VIODC Overview”](#) – provides an overview of the VIODC, interfaces, and I/Os.

- [Chapter 2, “VIODC to ML402 Card Interface”](#) – describes the VIODC to ML402 card interface.

- [Chapter 3, “Component and S-Video Interfaces”](#) – describes the High Definition (HD) and Standard Definition (SD) component video and S-video interfaces.

- [Chapter 4, “DVI/VGA Input Interface”](#) – provides an overview of the VGA and DVI input interface.

- [Chapter 5, “DVI/VGA Output Interface”](#) – provides an overview of the VGA and DVI output interface.

- [Chapter 6, “SDI Interface”](#) – provides an overview of the SDI video interface.

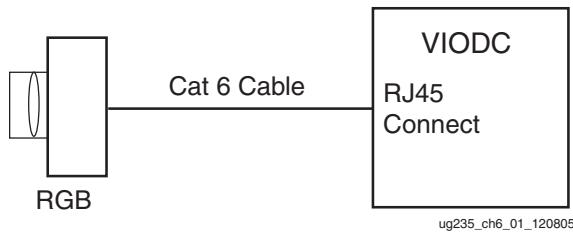

- [Chapter 7, “Image Sensor Camera Interface”](#) – describes the Irvine Sensors LVDS RGB camera interface.

- [Chapter 8, “Attaching the VIODC to the ML40x Development Board”](#) – provides information necessary for proper attachment of the VIODC to a ML40x development board.

- [Appendix A, “Reference Information”](#) – contains VIODC pinout information.

- [Appendix B, “VSK I/O Connector Location Pictures”](#) – shows I/O connection locations.

## Additional Resources

To find additional documentation, see the Xilinx website at:

<http://www.xilinx.com/literature/index.htm>.

To search the Answer Database of silicon, software, and IP questions and answers, or to create a technical support Web Case, see the Xilinx website at:

<http://www.xilinx.com/support>.

## Conventions

This document uses the following conventions. An example illustrates each convention.

### Typographical

The following typographical conventions are used in this document:

| Convention              | Meaning or Use                                                                                                  | Example                                                                                            |

|-------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Courier font            | Messages, prompts, and program files that the system displays                                                   | speed grade: - 100                                                                                 |

| <b>Courier bold</b>     | Literal commands that you enter in a syntactical statement                                                      | <b>ngdbuild design_name</b>                                                                        |

| <b>Helvetica bold</b>   | Commands that you select from a menu                                                                            | <b>File → Open</b>                                                                                 |

|                         | Keyboard shortcuts                                                                                              | <b>Ctrl+C</b>                                                                                      |

| Italic font             | Variables in a syntax statement for which you must supply values                                                | <b>ngdbuild design_name</b>                                                                        |

|                         | References to other manuals                                                                                     | See the <i>Development System Reference Guide</i> for more information.                            |

|                         | Emphasis in text                                                                                                | If a wire is drawn so that it overlaps the pin of a symbol, the two nets are <i>not</i> connected. |

| Square brackets [ ]     | An optional entry or parameter. However, in bus specifications, such as <b>bus [7 : 0]</b> , they are required. | <b>ngdbuild [option_name] design_name</b>                                                          |

| Braces { }              | A list of items from which you must choose one or more                                                          | <b>lowpwr ={on off}</b>                                                                            |

| Vertical bar            | Separates items in a list of choices                                                                            | <b>lowpwr ={on off}</b>                                                                            |

| Vertical ellipsis . . . | Repetitive material that has been omitted                                                                       | IOB #1: Name = QOUT'<br>IOB #2: Name = CLKIN'<br>. . .                                             |

| Horizontal ellipsis ... | Repetitive material that has been omitted                                                                       | <b>allow block block_name loc1 loc2 ... locn;</b>                                                  |

## Online Document

The following conventions are used in this document:

| Convention                            | Meaning or Use                                             | Example                                                                                                                                                       |

|---------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Blue text                             | Cross-reference link to a location in the current document | See the section “ <a href="#">Additional Resources</a> ” for details.<br>Refer to “ <a href="#">Title Formats</a> ” in <a href="#">Chapter 1</a> for details. |

| Red text                              | Cross-reference link to a location in another document     | See <a href="#">Figure 2-5</a> in the <i>Handbook</i> .                                                                                                       |

| <a href="#">Blue, underlined text</a> | Hyperlink to a website (URL)                               | Go to <a href="http://www.xilinx.com">http://www.xilinx.com</a> for the latest speed files.                                                                   |

## Chapter 1

# VIODC Overview

## Introduction

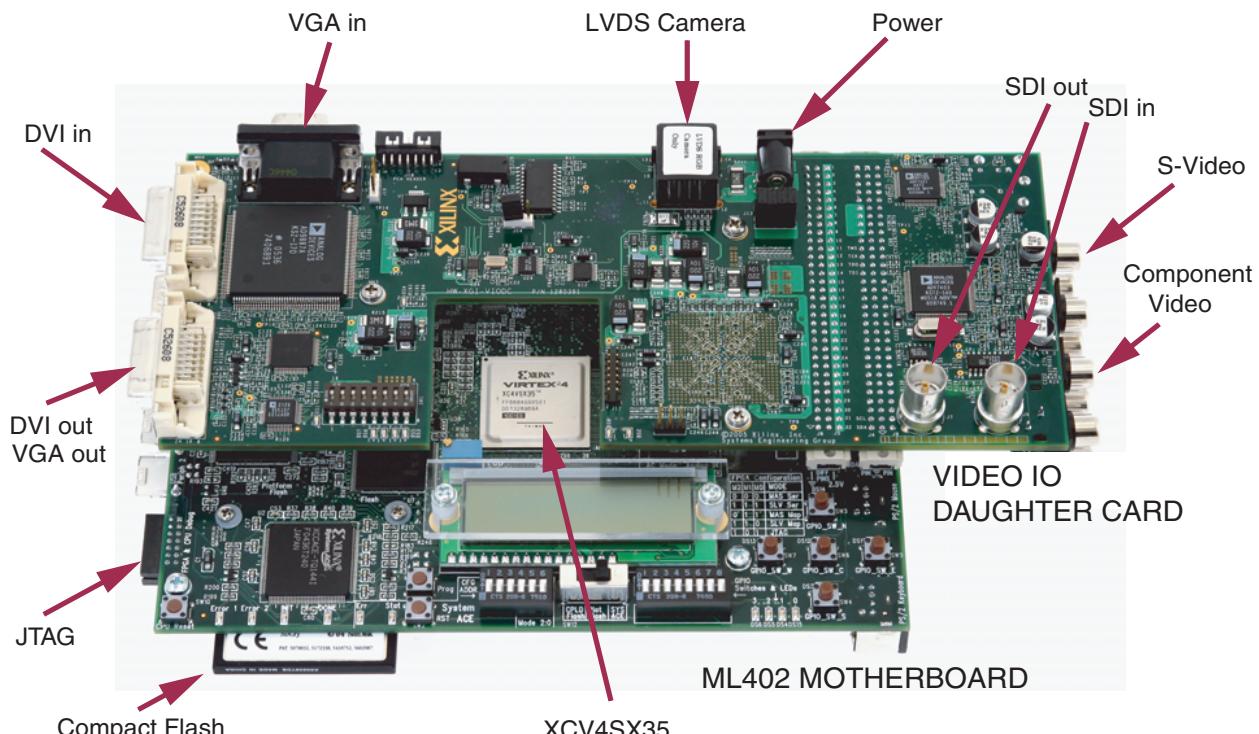

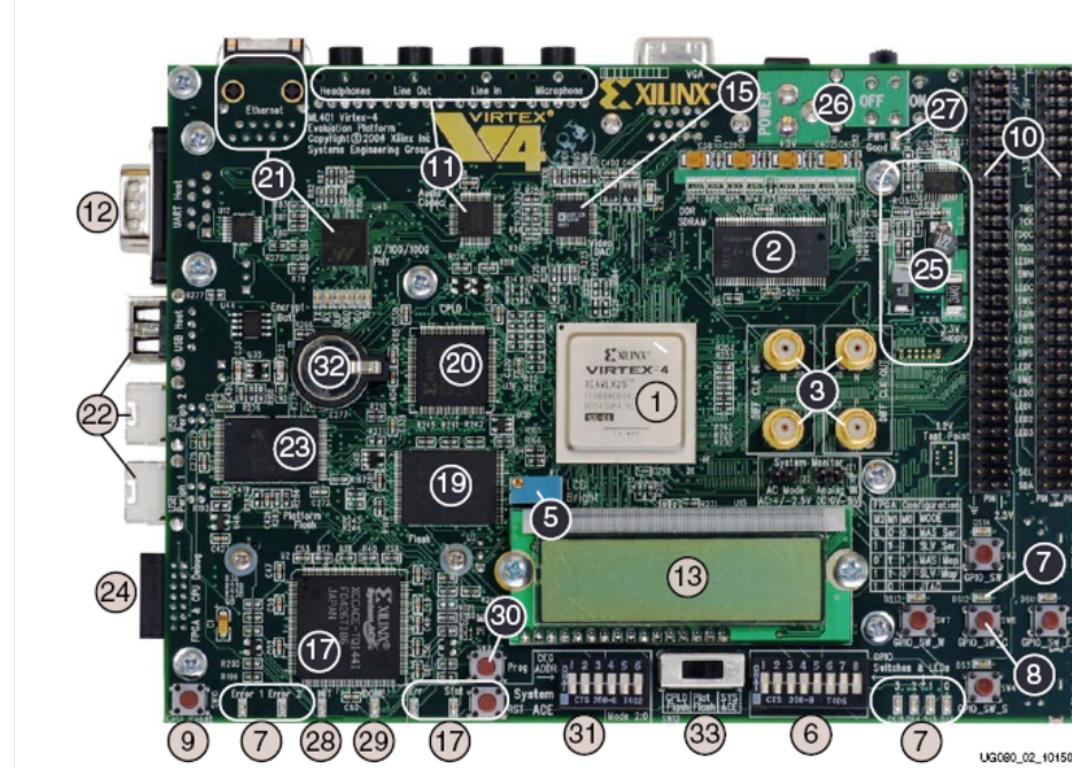

The Video Input and Output Daughter Card (VIODC) is a standard video interface card for Xilinx development platforms. It is compatible with ML401, ML402, and ML403 boards and other future Xilinx development platforms. The VIODC is shown in [Figure 1-1](#) mounted on a ML402 platform. The VIODC provides access to high definition (HD) and standard definition (SD) video streams, as well as computer graphics video interfaces, such as VGA over DVI and SDI interfaces.

UG239\_01\_122005

**Figure 1-1: VIODC Attached to an ML402 Platform**

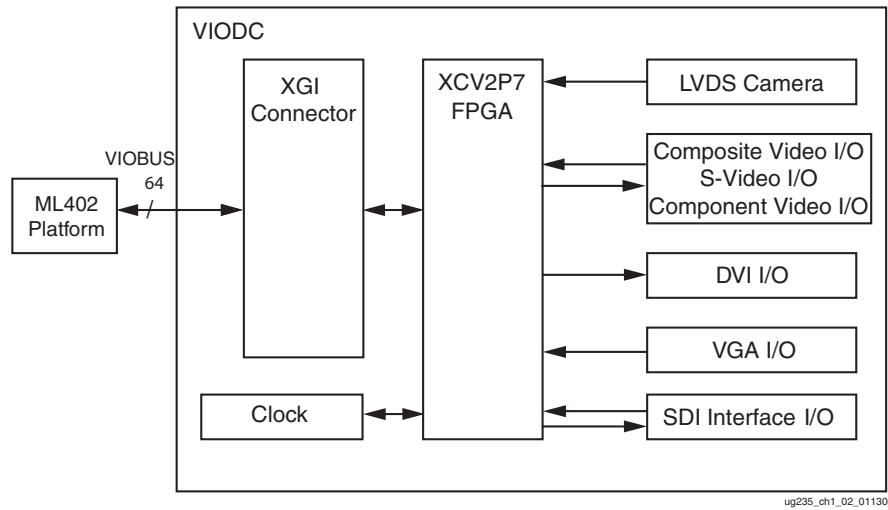

[Figure 1-2](#) shows a block diagram of the VIODC card. The VIODC consists of a number of video interface ICs connected to a Xilinx XCV2P7 FPGA. The VIODC is a daughter card which plugs onto a Xilinx ML40x FPGA platform via the XGI connector. The XGI connector provides a 64-signal bus between the ML40x and the VIODC. Collectively these signals are called the VIOBUS in this document.

Figure 1-2: VIODC Block Diagram

## Video Interface Support

The VIODC supports the following video interfaces:

- **LVDS Camera Input Port** – The LVDS camera input port supports the Irvine Sensors LVDS RGB camera with a Micron MT9V022 1/3 inch CMOS image sensor. The camera provides 752 x 480 pixels at 60 Hz progressive scan. It features low noise and very high dynamic range. The interface is implemented using LVDS signaling over standard Cat-6 Ethernet cables. Note that the LVDS camera interface is not compatible with Ethernet.

- **S-Video and Composite Video** – The VSK supports S-Video inputs and outputs. These interfaces can be configured to support NTSC, PAL, and virtually any other SD video format. The S-video input interface is supported by the ADV7403 decoder IC and output by the ADV7321 encoder IC. In addition to the encoder and decoder, analog filters are used to limit the video bandwidth.

- **Component Video I/O** – The component video I/O use standard RCA connectors to provide HD video the VSK. Component video is encoded as YPbPr video channels. The component video input on the supports 1080I, 720P, and 525P video standards. The Component video interface devices on the VSK support 10-bit digital video. Component video input is supported by the ADV7403 IC decoder IC and output by the ADV7321 encoder IC and analog filter sections.

- **DVI Digital Video I/O** – The VSK supports DVI video inputs and outputs. DVI is commonly used to interface to flat panel displays and computer graphics cards. The VSK DVI interfaces supports up to a pixel clock of up to 165 MHz. In addition to computer graphics, DVI is also used to carry HD video and is commonly found in high-end consumer video equipment, such as plasma displays, and can be found on some DVD players. The DVI ports can also be connected to HDMI interfaces by using a DVI/HDMI adapter. A TP410 IC is used to support DVI output and an AD9887 IC provides DVI input.

- **VGA Interface** – VGA input and outputs are available on the VIODC card. The VGA output is routed to the analog output pins of the DVI output connector. It is sourced by an ADV7123 10-bit DAC. VGA input is captured by the AD9887 IC.

- **SDI Video Interface** – A complete SDI video interface capable of supporting both SD and HD video rates is available on the VSK. The SDI standard is a high-speed serial interface used to carry digital video over coax cable. It is generally used in a studio environment. The SDI system includes cable equalizers and Genlock circuitry. (The VSK is a demonstration platform only. For HD-SDI verification and compliance, Xilinx recommends using the [Cook Technologies SDV board](#)).

- **Clock Generator** – The clock generator section is used to generate standard video clock frequencies. It is based on an ICS 1523 clock generator IC.

- **XCV2P7 FPGA** – The VSK also includes a Xilinx XCV2P7 FPGA, which is used to interface to the various video interfaces, as well as the ML402 main board. It features Multi-Gigabit Transceivers (MGTs), which are used to support the SDI interface. It also enables the VIODC to be used in a stand-alone fashion.

- **XGI Connector** – The XGI connector is a standard connector interface used on Xilinx ML40x FPGA development platforms. The XGI connector is used to connect to the VIODC to a standard FPGA development platform, such as the ML402. The signals consist of 32 single-ended LVCMOS25 signals and 32 signals that can be configured as either 32 LVCMOS25 signals or 16 LVDS signal pairs. The LVDS pairs are length matched and routed as pairs on the PCB. In addition, 5V power is passed up to the VIODC over the XGI connector.

- **VIOBUS** – The Video Starter Kit (VSK) uses the VIODC as a Video I/O interface. For compatibility with the VSK, the 64 XGI signals have been specified as a bus named the VIOBUS. In this use, the signals on the VIODC XGI connector have been specified as a set of buses that transmit a 27-bit digital video channel from the VIODC to the FPGA development platform and a 27-bit bus to transmit a similar digital video channel from the ML40x to the VIODC. Each video channel consists of a 24-bit digital video bus, HSYNC, VSYNC and a clock enable signal. The pinout for the VIOBUS can be found in [Appendix A, "Reference Information."](#) This implementation of the interface runs synchronous to the interface clock supplied by the ML402 board. The VIOBUS also specifies an LVDS clock, a reset signal, an I2C interface, and a 4-pin serial bus.

## Chapter 2

# VIODC to ML402 Card Interface

When the VIODC is used as part of the Video Starter Kit (VSK) from Xilinx, the 64-pin XGI connector connects the VIODC to a ML402 card to communicate with the VIODC card. When the VIODC is used with the VSK, the 64 XGI signals are allocated to a bus named the VIOBUS, which serves the following functions:

- Transfers video data between the ML402 card and the VIODC card.

- Provides a clock to the VIODC card.

- Provides reset to the VIODC card.

- Provides a low-pin count serial bus to access registers on the VIODC.

- Provides an I2C bus (an industry standard 2-pin serial data bus used to communicate and configure ICs) to access registers on the VIODC video interface FPGA.

## VIOBUS Clocking

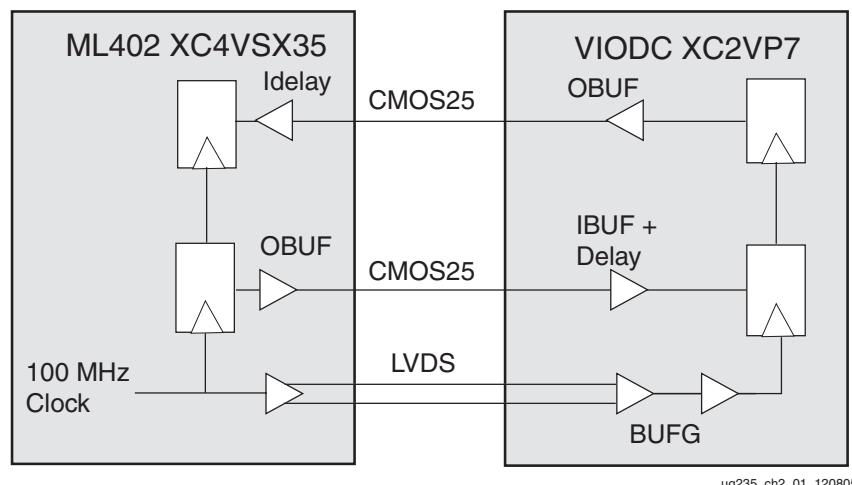

The VIOBUS uses a simple synchronous interface running at 100 MHz (Figure 2-1).

Figure 2-1: VIOBUS Clocking

A clock is passed from the ML402 FPGA to the VIODC using differential signaling. All data signals are single ended. The VIODC transmits data back to the ML402 FPGA using the received clock. Data returning back from the VIODC is clocked into the ML402 FPGA using the internal 100 MHz clock.

Future VIODC bus interfaces may implement a differential bus using the 16 differential pairs available on HDR2 and more sophisticated clocking.

## VIOBUS Signal Definitions

Table 2-1: VIOBUS Signal Definitions

| Signal                                                                   | Description                                    | nbits | Type     | Target Speed | Source FPGA | XGI Pins                    |

|--------------------------------------------------------------------------|------------------------------------------------|-------|----------|--------------|-------------|-----------------------------|

| <b>VIO Data Bus (a moderate-speed single-ended bus)</b>                  |                                                |       |          |              |             |                             |

| vio_up[25:0]                                                             | Data bus to the VIODC                          | 26    | LVCMOS25 | 100 MHz      | ML402       | hdr1[20:2],<br>hdr2[2:32]   |

| vio_up_ena                                                               | Pixel enable for vio_up[25:0]                  | 1     | LVCMOS25 | 100 MHz      | ML402       | hdr1[22]                    |

| vio_dn[25:0]                                                             | Data bus from the VIODC                        | 26    | LVCMOS25 | 100 MHz      | VIODC       | hdr1[42:24],<br>hdr2[64:34] |

| vio_dn_ena                                                               | Pixel enable for vio_dn[25:0]                  | 1     | LVCMOS25 | 100 MHz      | VIODC       | hdr1[44]                    |

| <b>Sport Serial Bus (used to configure registers in the VIODC FPGA)</b>  |                                                |       |          |              |             |                             |

| vio_sport_up                                                             | Sport write data (16-bit data, 16-bit address) | 1     | LVCMOS25 | 10 MHz       | ML402       | hdr1[54]                    |

| vio_sport_dn                                                             | Sport return data                              | 1     | LVCMOS25 | 10 MHz       | VIODC       | hdr1[52]                    |

| vio_sport_sync                                                           | Sport sync pulse                               | 1     | LVCMOS25 | 10 MHz       | ML402       | hdr1[50]                    |

| vio_sport_clk                                                            | Sport clock                                    | 1     | LVCMOS25 | 10 MHz       | ML402       | hdr1[48]                    |

| <b>I2C Serial Bus (used to configure registers in the video devices)</b> |                                                |       |          |              |             |                             |

| vio_i2c_sda_up                                                           | I2C write data                                 | 1     | LVCMOS25 | 400 kHz      | ML402       | hdr1[60]                    |

| vio_i2c_sda_dn                                                           | I2C return data                                | 1     | LVCMOS25 | 400 kHz      | VIODC       | hdr1[58]                    |

| vio_i2c_scl_up                                                           | I2C clock signal                               | 1     | LVCMOS25 | 400 kHz      | ML402       | hdr1[56]                    |

| <b>Miscellaneous</b>                                                     |                                                |       |          |              |             |                             |

| vio_reset                                                                | Active High reset to VIODC                     | 1     | LVCMOS25 | 10 MHz       | ML402       | hdr1[46]                    |

| <b>Clock</b>                                                             |                                                |       |          |              |             |                             |

| vio_up_clk_lvds_P,N                                                      |                                                | 1     | LVDS25   | 400 MHz      | ML402       | hdr1[64:62]]                |

Refer to the VIOBUS pinout in [Appendix A, "Reference Information"](#) for signal locations.

## Chapter 3

# Component and S-Video Interfaces

## Overview

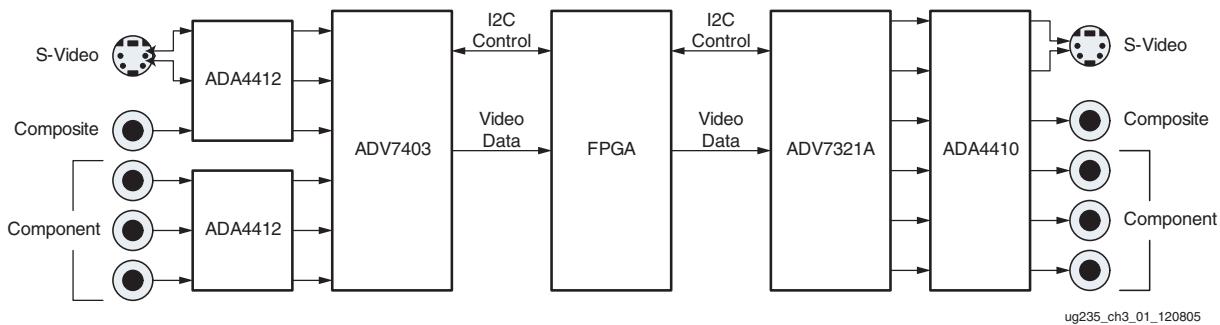

The VIODC board supports input and output for S-video, composite, and component video. **Figure 3-1** is a simplified block diagram of input and output.

**Figure 3-1: S-Video, Composite, and Component Video Input and Output Block Diagram**

Input signals are conditioned by a combination of passive components and the ADA4412 device. The conditioned input signals are converted to digital signals by the ADV7403 video decoder device. Digital video output data stream from the FPGA is converted to analog signals by the ADV7321 video encoder device. The analog output signals are conditioned by the ADA4410 device.

The video decoder, ADV7403 from Analog Devices, is responsible for converting analog video signals into a representative digital video data stream. The video encoder, ADV7321A also from Analog Devices, is responsible for the generation of S-Video, composite, and component analog video signals from a digital video data stream. Both devices offer an I<sup>2</sup>C control serial bus for control and ancillary data.

## ADV7403 Video Decoder

The ADV7403 is a high quality, single chip, multiple format video decoder and graphics digitizer. This multiple format decoder automatically supports the conversion of PAL, NTSC, and SECAM standards in the form of composite or S-video into a digital ITU-R BT.656 format. The component processor is capable of decoding/digitizing a wide selection of video formats in any color space. Component video standards supported include: 525i, 625i, 525p, 625p, 720p, 1080i and many other HD standards, as well as graphic digitization from VGA to SXGA. Converted input signals are output to the output pixel port, which is connected directly to the FPGA. Under user control, the output pixel port is configurable to conform to multiple different standards. Selection of the format is done through commands written to the device over the I<sup>2</sup>C bus and affects the pins

definitions. For complete details, refer to the Analog Devices data sheet found at [www.analog.com](http://www.analog.com)

## ADV7321 Video Encoder

The Analog Devices ADV7321 video encoder device is a single monolithic chip that performs multiple format digital-to-analog video encoder functions. Both standard and high definition input formats are supported including: SMPTE 293M (525p), BTA T-1004 EDTV2 (525p), CCIR-656, and SMPTE 274M. Multiple output standards for both SD and HD are also supported including: YPrPb HDTV (EIA 770.3), RGB, RGBHV, YPrPb progressive scan (EIA-770.1, EIA-770.2) and component YPrPb (SMPTE/EBU N10). 4:2:2 or 4:4:4 data format is supported for HDTV. For all standards, external horizontal, vertical and blanking signals or EAV/SAV timing codes control the insertion of appropriate synchronization signals into the digital data stream and, therefore, the analog output signal.

The ADV7321 provides user configuration options through an I<sup>2</sup>C bus, which enables access to a large number of configuration registers. Under user control, the device pins are reconfigured to match the operation selected. For instance, SD 8-bit mode configuration only, the data input port S7-S0 would be used to transfer in a multiplexed fashion the digital video data stream into the device. The Y and C buses would not be used. Refer to Analog Devices ADV7321 data sheet for further details.

## Video Signal Input and Output Conditioning

Each of the video input and output signals must be conditioned to ensure that the physical interfaces meet impedance and electrical specification for each individual video standard. [Figure 3-3](#) illustrates the input and output conditioning circuits used for S-video, composite and component input and output signals.

## S-Video Input and Output

### S-Video Input

Connector J20 provides input and output of S-Video compatible signals. For the input, the Y (intensity) and C (color) signals are each conditioned and input into the ADV7403 video decoder to create a digital video data stream output, which is transferred to the Xilinx XC2VP4 FPGA for handling. Generation of S-Video output starts with a digital video stream coming from the FPGA, written into the ADV7321A video encoder to produce the Y/C analog outputs, which are conditioned and output to the J20 S-Video connector.

### S-Video Input Signal Conditioning

S-Video input signals are first conditioned using two identical circuits illustrated in [Figure 3-2](#). This circuit contains both passive and active components, including the Analog Devices ADA4412 device. This conditioning circuit insures that the input signal impedance matches the S-Video (IEC 60933-5) specification and signal levels required by the ADV7403.

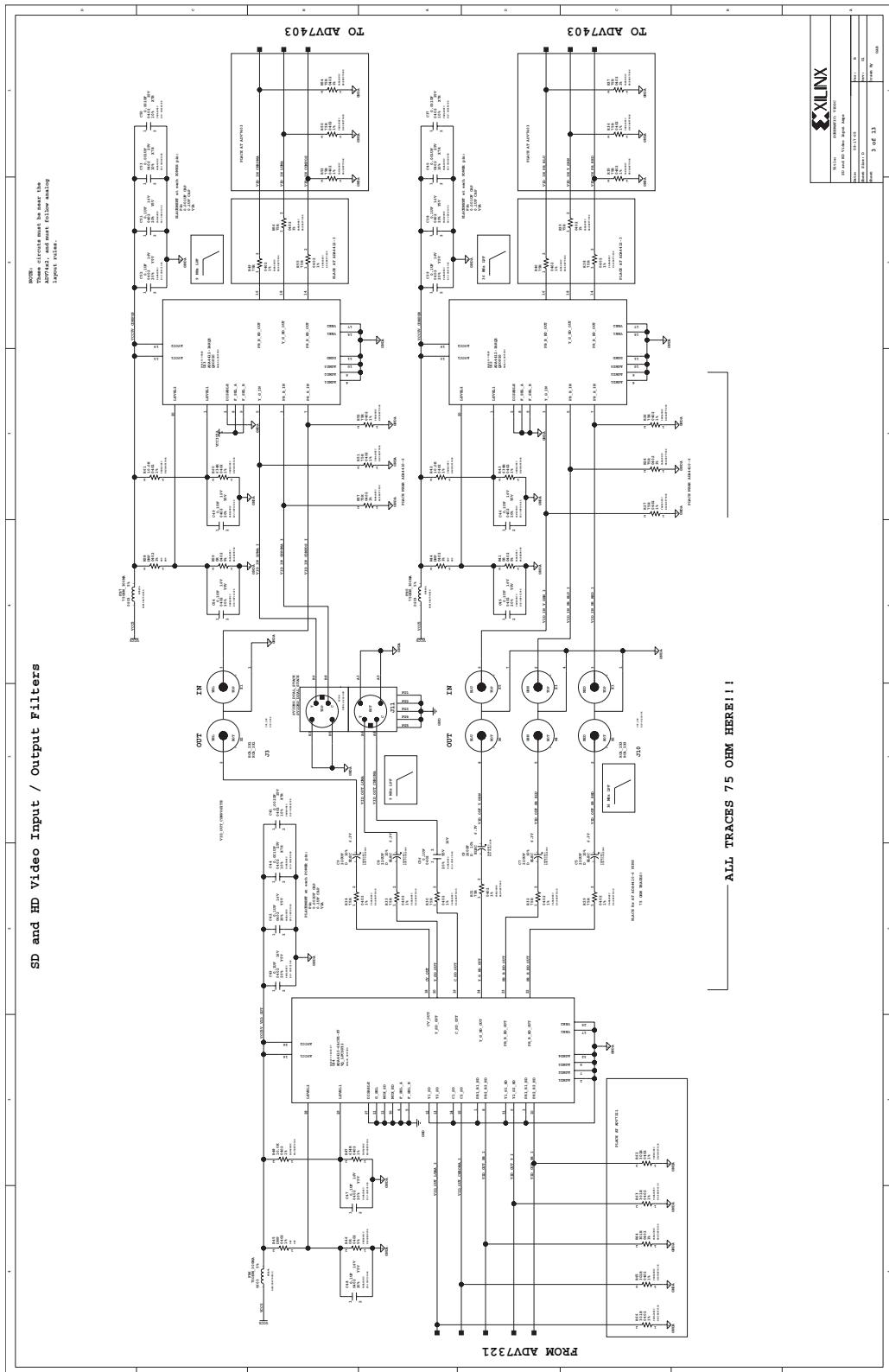

Figure 3-2: S-Video, Composite, and Component Input and Output Signal Conditioning Circuit

## ADV7403 S-Video Input

The Y (intensity) and C (color) conditioned signals are input into the A12 and A10 of the ADV7403 twelve input analog multiplexer, which routes each of the selected input signals to one of the ADCs for conversion. Fully automatic detection and selection of all worldwide standards, (PAL, NTSC and SECAM) is provided as well as vertical blanking processing for Teletext, Closed Caption and wide screen signaling. For full details regarding the ADV7403 device refer to the Analog Devices datasheet.

The digital data stream generated from the conversion of the S-Video signals is available to the FPGA through a 41-bit data bus and 5-bit control. An I2C bus available on the ADV7403 provides control, status and ancillary data and is directly connected to the FPGA. For S-Video configuration there are 6 different interface configurations that use some of the lower 30 pins. The default configuration is to output YCrCb data on the 8-bit portion of the data bus from P19 to P12.

## S-Video Output

Generation of S-Video output video from a digital video data stream is accomplished by the ADV7321 device. Video data is written from the XC2VP4 FPGA into the ADV7321 device, which converts from digital-to-analog values using DAC D and E. The analog output signals are conditioned to meet specification with the conditioned output going through connector J20.

## ADV7321 S-Video Output

Data, video timing control and operations control bus connections between the FPGA and ADV7321 video encoder provide the digital video data stream and information needed to convert to generate analog S-Video Y/C signals. The FPGA writes the digital video data stream and control into the ADV7321, which then produces the appropriate analog output with complete video timing. The format of the data written is selectable the analog output is first conditioned and then placed on the output S-Video connector J20.

## S-Video Output Signal Conditioning

Figure 3-2 details the implementation of the S-Video output conditioning circuit following the ADV7321 Y/C analog signal generation. This conditioning circuit is composed of both active and passive components, with the ADA4410 device providing active circuits and is designed to meet the specification IEC 60933-5 requirements for S-Video.

## Composite Video Input and Output

Composite video is the format of an analog television (picture only) signal before it is combined with a sound signal and modulated onto an RF carrier. It is usually in a standard format such as NTSC, PAL, or SECAM. It is a composite of three source signals called Y, U and V with sync pulses. Y represents the brightness or *luminance* of the picture and includes synchronizing pulses, so that by itself it could be displayed as a monochrome picture. U and V between them carry the color information.

Composite video input and output is supported on the VIODC card through RCA type jack J18, this dual RCA jack has the composite video input on X1 and output on X2 and are color coded yellow. Input signals are conditioned and then presented to the ADV7403 for conversion to digital video data stream. The ADV7403 device automatically detects the video standard (PAL, NTSC, SECAM) and converts to the appropriate data stream with control information. The resulting data stream and control information is transferred to the

FPGA for further processing. A digital video data stream with control is converted to a composite video stream by the ADV7321A device and associated signal conditioning circuits. The data stream and control is supplied by the FPGA.

## Composite Video Input

Composite video input on connector J18 X1 is first conditioned and then converted to the digital video data stream, which is passed to the XC2VP4 for further processing. The ADV7403 device is configurable under user control to select the format of the devices pixel output port. In SD composite video mode up to 3 10-bit data busses can be used to transfer the video data.

### Composite Video Input Conditioning Circuit

To insure compatibility with the specification an input conditioning circuit is inserted before the ADV7403 analog input. Impedance matching for the input signal and level matching for the analog input are assured. [Figure 3-2](#) details the implementation of this circuit.

### ADV7403 Composite Video Input

The conditioned composite video input signal is input on the 11<sup>th</sup> input of the 12 input analog multiplexer. When configured properly by the user the input will be routed to an analog-to-digital converter and automatic format detection logic to generate the digital video data stream. Configuration of the ADV7403 device is through the I2C control bus and appropriate writes to a number of registers. As part of the configuration process the user will select the format of the output data. For programming details please refer to the Analog Devices ADV7403 data sheet.

## Composite Video Output

Generation of composite video output starts with a digital video data stream being written from the XC2VP4 into the ADV7321A video encoder, which produces an analog output that is conditioned and presented on connector J18 X2.

### ADV7321A Composite Video Output

The XC2VP4 Xilinx FPGA provides both the digital video data stream and the configuration to the ADV7321A. Configuration of the ADV7321A defines the interface connections and active pins for the connection from the XC2VP4 and to the ADV7321A. For composite video the input format can be configured for either 8/10-bit ITU-BT.656/601 or 16/20-bit YCrCb with embedded HS, VS and FIELD codes. The input digital video data stream is then converted to an analog composite video output signal that includes all timing and control signaling.

### Composite Video Conditioning Circuit

The analog output of the ADV7321A is processed by a conditioning circuit that insures that the composite output signal meets composite video drive specifications. [Figure 3-2](#) details the composite video output circuit.

## Component Video Input and Output

### Component Video Input

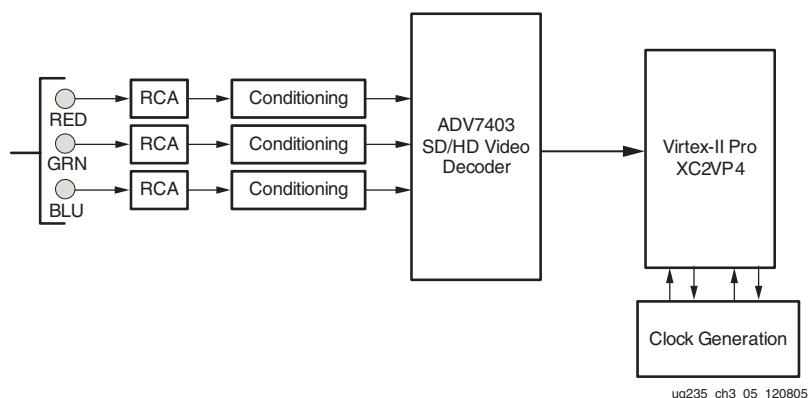

RCA style connector J19 (X1, X3 and X5) enable input of analog component video signals, which are then converted to the digital domain by the Analog Devices ADV7403 device. Either YPrPb or RGB analog input signals are accepted. The ADV7403 devices integrated 110 MHz ADCs, with 12-bit resolution, supporting HDTV for 525p, 625p, 720p and 1080i as well as RGB graphics support from VGA to SXGA at 60 frames per second. The digitized video output is connected directly to the Xilinx FPGA through a digital data, video timing control and I<sup>2</sup>C control busses. [Figure 3-3](#) illustrates the VIODC composite video input configuration, through ADV7403 video decoder to Xilinx XC2VP4 FPGA.

**Figure 3-3: Component Video Input**

### Input Signal Conditioning

The three RCA jacks X1, X3 and X5 are color coded Red, Green and Blue respectively and form the physical connectors for the component video inputs. Conditioning of the analog input signal is done using circuit detailed in [Figure 3-2](#).

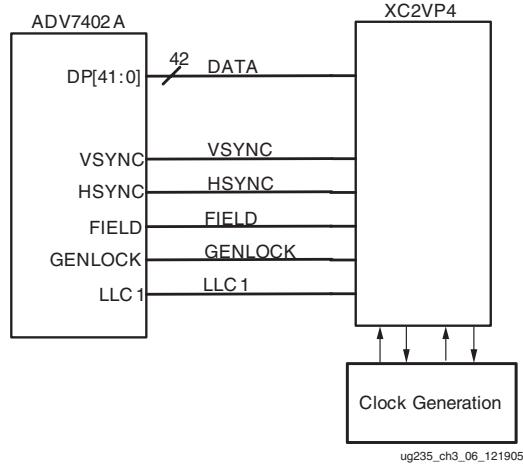

### ADV7403 Connection to FPGA

Digital connections from the ADV7403 to the Xilinx XC2VP4 FPGA consist of 42 data and 5 control signals. The data signals include three 12-bit data busses for, one for each of red, green and blue pixel values. Control signals include: horizontal and vertical frame

synchronization signals and field indicator. [Figure 3-4](#) details the connections from the ADV7403 video decoder device to the XC2VP4 Xilinx FPGA.

**Figure 3-4: Connections from ADV7403 Video Decoder to XC2VP4 FPGA**

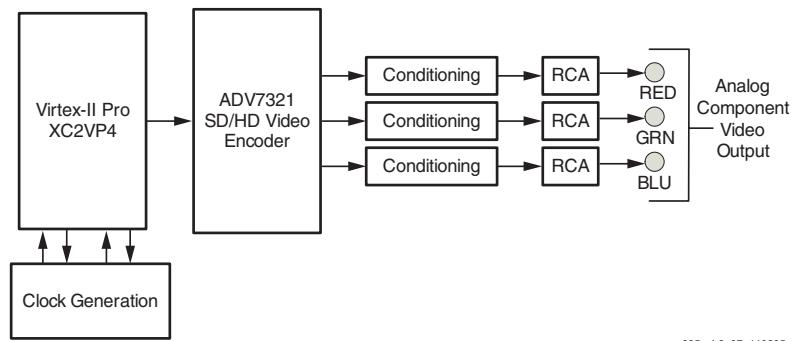

## Component Video Output

Compliant digital video streams are feed into the ADV7321 device by the Xilinx XC2VP4 FPGA, where it is converted to analog RGB or YPrPb using 12-bit DACs. The ADV7321 device, from Analog Devices, produces fully compliant SD/HD analog output signals, which are then conditioned and drive the RCA type jacks. The Analog Devices ADV7321 is used to generation all analog component RGB or YPrPb video output signals. [Figure 3-5](#) is a block diagram of the component video output system on the VIODC board.

**Figure 3-5: Component Video Output Block Diagram**

## FPGA to ADV7321 Connection

The Xilinx XC2VP4 FPGA drives digital video data streams, in either standard and/or high definition video format, onto three separate 10-bit wide digital input ports of the ADV7321. For all supported standards the ADV7321 generates all horizontal, vertical and blanking signals. Six high performance 12-bit digital to analog converters generate the analog output signals.

## Analog Output Signal Conditioning

Output analog signals are first conditioned to meet standards requirements and then connected to the red, green and blue RCA type connectors X2, X4 and X6 respectively. Analog output is conditioned by a combination of passive and active circuits, as illustrated in Figure 3-3.

## ADV7403 Configuration Modes

Refer to the ADV7403 data sheet for details configuring the ADV7403 device.

The ADV7403 is mapped to I2C address 0x40/0x41.

*Table 3-1: Configuration Modes for ADV7403 Video Decoder Chip*

| Register Name     | Register Address | Register Value | Description                         |

|-------------------|------------------|----------------|-------------------------------------|

| <b>525P</b>       |                  |                |                                     |

| Primary Mode      | 0x05             | 0x01           |                                     |

| Video Standard    | 0x06             | 0x08           | [2:0] =PRIM_MODE                    |

| Enable XTAL       | 0x1D             | 0x47           | [3:0] = VID_STD                     |

| ADC Power and PLL | 0x3a             | 0x10           | latch clock = 13-55 MHz             |

| Bias Control      | 0x3b             | 0x80           | External Bias Enable'               |

| TLLC Control      | 0x3c             | 0x5c           | PLL qpump                           |

|                   | 0x6b             | 0xC2           | [3:0]cpop_sel(1=20-bit,2=30-bit)    |

|                   | 0x85             | 0x18           | Turn off SSPD as sync is on Y       |

|                   | 0x86             | 0x0b           | ENABLE SDTI line count mode         |

|                   | 0xb3             | 0xfe           | SDTI                                |

| ADC sw1           | 0xc3             | 0x54           | [7:4]=adc1<br>[3:0]=adc0            |

| ADC sw2           | 0xc4             | 0x86           | [7]=sw_en,<br>[6]=SOG<br>[3:0]=adc2 |

|                   | 0x0e             | 0x80           | Startup sequence                    |

|                   | 0x52             | 0x46           |                                     |

|                   | 0x54             | 0x00           |                                     |

|                   | 0x0e             | 0x00           |                                     |

**Table 3-1: Configuration Modes for ADV7403 Video Decoder Chip (Continued)**

| Register Name     | Register Address | Register Value | Description                         |

|-------------------|------------------|----------------|-------------------------------------|

| <b>720P</b>       |                  |                |                                     |

| Primary Mode      | 0x05             | 0x01           |                                     |

| Video Standard    | 0x06             | 0x0a           | [2:0] =PRIM_MODE                    |

| Enable XTAL       | 0x1D             | 0x47           | [3:0] = VID_STD                     |

| ADC Power and PLL | 0x3a             | 0x20           | latch clock                         |

| Bias Control      | 0x3b             | 0x80           | External Bias Enable'               |

| TLLC Control      | 0x3c             | 0x5d           | PLL qpump                           |

|                   | 0x6b             | 0xC2           | [3:0]cpop_sel(1=20-bit,2=30-bit)    |

|                   | 0x85             | 0x18           | Turn off SSPD as sync is on Y       |

|                   | 0x86             | 0x0b           | ENABLE SDTI line count mode         |

|                   | 0xb3             | 0xfe           | SDTI                                |

| ADC sw1           | 0xc3             | 0x54           | [7:4]=adc1<br>[3:0]=adc0            |

| ADC sw2           | 0xc4             | 0x86           | [7]=sw_en,<br>[6]=SOG<br>[3:0]=adc2 |

|                   | 0x0e             | 0x80           | Startup sequence                    |

|                   | 0x52             | 0x46           |                                     |

|                   | 0x54             | 0x00           |                                     |

|                   | 0x0e             | 0x00           |                                     |

| <b>1080I</b>      |                  |                |                                     |

| Primary Mode      | 0x05             | 0x01           |                                     |

| Video Standard    | 0x06             | 0x0c           | [2:0] =PRIM_MODE                    |

| Enable XTAL       | 0x1D             | 0x47           | [3:0] = VID_STD                     |

| ADC power and PLL | 0x3a             | 0x21           | Latch clock                         |

| Bias Control      | 0x3b             | 0x80           | External Bias Enable'               |

**Table 3-1: Configuration Modes for ADV7403 Video Decoder Chip (Continued)**

| Register Name | Register Address | Register Value | Description                         |

|---------------|------------------|----------------|-------------------------------------|

| TLLC control  | 0x3c             | 0x5d           | PLL qpump                           |

|               | 0x6b             | 0xC2           | [3:0]cpop_sel(1=20-bit,2=30-bit)    |

|               | 0x85             | 0x18           | Turn off SSPD as sync is on Y       |

|               | 0x86             | 0x0b           | ENABLE SDTI line count mode         |

|               | 0xb3             | 0xfe           | SDTI                                |

| ADC sw1       | 0xc3             | 0x54           | [7:4]=adc1<br>[3:0]=adc0            |

| ADC sw2       | 0xc4             | 0x86           | [7]=sw_en,<br>[6]=SOG<br>[3:0]=adc2 |

|               | 0x0e             | 0x80           | Startup sequence                    |

|               | 0x52             | 0x46           |                                     |

|               | 0x54             | 0x00           |                                     |

|               | 0x0e             | 0x00           |                                     |

**Notes:**

1. The ADC sw1 and sw2 are unique to the VIODC input configuration.

Refer to the ADV7403 data sheet for other video configurations.

### ADV7321A Configuration Modes

**Table 3-2**, details the parameters setting for the internal registers of the ADV7321A Video Encoder device for each of the supported video standards.

The ADV7301 is mapped to I2C address 0x54/0x55.

**Table 3-2: Configuration Modes for ADV7321A Video Encoder Chip**

| Register Name | Register Address | Register Value | Description                                                                                                                                       |

|---------------|------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>525P</b>   |                  |                |                                                                                                                                                   |

| Power Mode    | 0x00             | 0xFE           | [7]=DACA_composite<br>[6]=DACP_luma<br>[5]=DACC_chroma<br>[4]=DACP_Y<br>[3]=DACE_Pr<br>[2]=DACP_Pb on<br>[1]=pll_off(1=off)<br>[0]=sleep(1=sleep) |

**Table 3-2: Configuration Modes for ADV7321A Video Encoder Chip (Continued)**

| Register Name | Register Address | Register Value | Description                                                                                                                                  |

|---------------|------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Input Mode    | 0x01             | 0x10           | [6:4]=mode<br>(7=PS54 6=SDHD 5=SDHD 4=10-bit 3=20-bit 2=hd, 1=ps, 0=sd,)<br>[3]=clock_dly<br>[2]=cb0,<br>[0]=BTA compatibility               |

| Mode          | 0x02             | 0x30           | [5]=yuv_output<br>[4]=rgb_out_sync<br>[3]=use_rgb_matrix<br>[2]=black bar'                                                                   |

| HD Mode Reg 1 | 0x10             | 0x00           | [7]=macro_vision<br>[6]=blank_low<br>[5]=720/1080i,<br>[4]=625/525p<br>[3:2]=sync_mode(0=hvsync,1=EAVcodes2<br>=async), [1:0]=output_levels( |

| HD Mode Reg 2 | 0x11             | 0x01           | [3]=tp_Field_en<br>[2]=test_pattern_on<br>[0]=data_valid_en                                                                                  |

| HD Mode Reg 4 | 0x13             | 0x04           | [7]=dbuf<br>[6]=4:2:2/4:4:4<br>[5]=SSAF<br>[3]=sync_filter<br>[2]=10-bit<br>[0]=crcb                                                         |

| HD Mode Reg 6 | 0x15             | 0x00           | [7:6]=filter<br>[5]=gamma_en<br>[4]=gamma_a/b<br>[3]=dac_swap<br>[2]=syncPrPb<br>[1]=rgb_input                                               |

| <b>525PS</b>  |                  |                |                                                                                                                                              |

| Power Mode    | 0x00             | 0xFE           |                                                                                                                                              |

| Input Mode    | 0x01             | 0x20           |                                                                                                                                              |

| Mode          | 0x02             | 0x30           |                                                                                                                                              |

| HD Mode Reg 1 | 0x10             | 0x00           |                                                                                                                                              |

| HD Mode Reg 2 | 0x11             | 0x01           |                                                                                                                                              |

| HD Mode Reg 4 | 0x13             | 0x04           |                                                                                                                                              |

**Table 3-2: Configuration Modes for ADV7321A Video Encoder Chip (Continued)**

| Register Name | Register Address | Register Value | Description |

|---------------|------------------|----------------|-------------|

| HD Mode Reg 6 | 0x15             | 0x00           |             |

| <b>720P</b>   |                  |                |             |

| Power Mode    | 0x00             | 0xFE           |             |

| Input Mode    | 0x01             | 0x20           |             |

| Mode          | 0x02             | 0x30           |             |

| HD Mode Reg 1 | 0x10             | 0x20           |             |

| HD Mode Reg 2 | 0x11             | 0x01           |             |

| HD Mode Reg 4 | 0x13             | 0x24           |             |

| HD Mode Reg 6 | 0x15             | 0x00           |             |

| <b>10801</b>  |                  |                |             |

| Power Mode    | 0x00             | 0xFE           |             |

| Input Mode    | 0x01             | 0x20           |             |

| Mode          | 0x02             | 0x30           |             |

| HD Mode Reg 1 | 0x10             | 0x68           |             |

| HD Mode Reg 2 | 0x11             | 0x01           |             |

| HD Mode Reg 4 | 0x13             | 0x04           |             |

| HD Mode Reg 6 | 0x15             | 0x00           |             |

Refer to the ADV7321A data sheet for other video configurations.

## Chapter 4

# DVI/VGA Input Interface

This chapter describes the DVI and VGA input interface theory of operation. It covers the signals and presents an overview of the internal operating modes of the AD9887. Users can refer to the [data sheet](#) for more detailed information.

## Interface Description

The VIODC DVI/VGA input interface allows standard PC video formats to be captured. This includes analog VGA formats and digital DVI up to 1600x1200 at 60 Hz.

### DVI Connectivity on VIODC

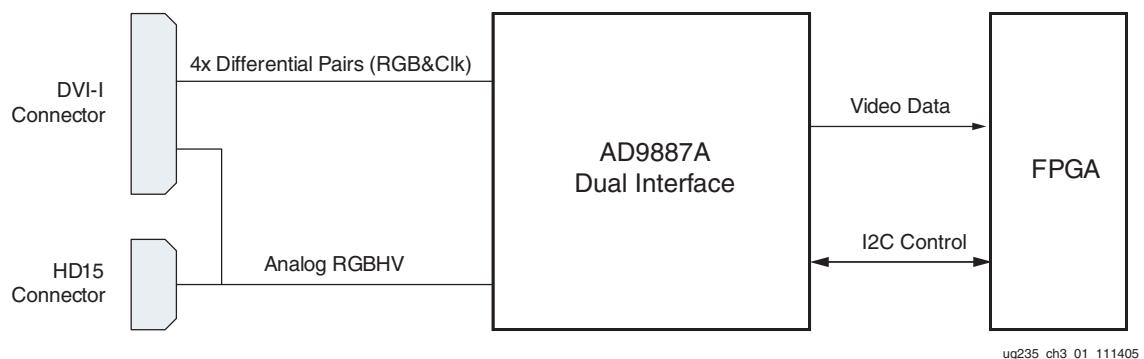

The DVI/VGA input portion of the video input and output daughter card (VIODC) has two connectors. The first is a traditional HD15 as used by all older analog video cards and monitors. The second connector is a DVI-I connector which includes pins for both the analog VGA interface and the DVI digital interface. Note that the analog pins of the two connectors are tied together, so that only one or the other can be used at any time. See [Figure 4-1](#).

VIODC uses Analog Devices [AD9887A](#) dual interface for flat panel displays. This part includes two very separate subsections: the analog (VGA) interface and the digital (DVI) interface. Via the I2C control bus, this part can be configured to receive either of the modes and output it in a parallel digital form to the FPGA.

Figure 4-1: DVI Connectivity on VIODC Block Diagram

## Signals

The AD9887A interface has a parallel digital bus interface to the FPGA for video data and an I2C control bus for configuration.

## DVI Interface

The DVI interface is through the DVI-I connector. The video data is carried by four differential pairs, three data and a clock.

## VGA interface

The analog VGA interface is through the either the HD15 connector or the analog pins of the DVI-I connector. The video data is carried by three analog signals along with up to two optional sync signals.

## Display Data Channel

Both the DVI connector and the HD15 connector include SCL and SDA pins for the Display Data Channel (DDC). This is an I2C interface used by a computer to identify a monitor's capabilities. The graphics adapter reads the monitor's extended display identification data (EDID). This structure lists monitor manufacturer and model, supported resolutions, and other capabilities. If a graphics adapter cannot retrieve this EDID structure, it runs with a default resolution, typically 640 x 480 at 60 Hz analog. To allow higher resolutions or to enable the DVI interface, the receiver must report that it is capable of these modes. To support this, VIODC includes EEPROMs on the DDC (separate for each connector) that can be programmed with this structure.

The DDC is also used in the DVI connector for negotiating encryption keys when High-bandwidth Digital Content Protection (HDCP) is required. The AD9887A interface supports this functionality and has an EEPROM for storing these keys.

## AD9887 Overview

The AD9887A dual interface includes both analog and digital interfaces. Refer to the [AD9887A](#) interface data sheet for further details.

## Analog Interface

The AD9887A is a complete 8-bit 170 mega sample per second (MSPS) monolithic analog interface optimized for capturing RGB graphics signals from personal computers and workstations. Its 170 MSPS encode rate capability and full-power analog bandwidth of 330 MHz supports resolutions up to UXGA (1600 by 1200 at 60 Hz).

The analog interface includes a 170 MHz triple ADC with internal 1.25 V reference, a phase-locked loop (PLL), and programmable gain, offset, and clamp control. The user provides only a 3.3 V power supply, analog input, and HSYNC. Three-state CMOS outputs can be powered from 2.5 V to 3.3 V.

The AD9887A's on-chip PLL generates a pixel clock from HSYNC. Pixel clock output frequencies range from 12 MHz to 170 MHz. PLL clock jitter is typically 500 ps peak-to-peak at 170 MSPS. The AD9887A also offers full sync processing for composite sync and sync-on-green (SOG) applications.

## Digital Interface

The AD9887A contains a DVI 1.0 compatible receiver and supports display resolutions up to UXGA (1600 \_ 1200 at 60 Hz). The receiver operates with true color (24-bit) panels in 1 or

2 pixel(s)/clock mode and features an intra-pair skew tolerance of up to one full clock cycle.

With the inclusion of HDCP, displays can now receive encrypted video content. The AD9887A allows for authentication of a video receiver, decryption of encoded data at the receiver, and renewability of that authentication during transmission as specified by the HDCP v1.0 protocol.

## VGA Standard Overview

The dominant video monitor interface standard for PCs has been analog VGA since its establishment in 1987. The VGA interface consists of RGB pixel levels and synchronization signaling (syncs). This interface was designed specifically for driving CRT monitors, so this interface is tailored to work with CRTs.

The video data is carried by three  $75\Omega$  transmission lines (coax), one each for red, green, and blue. When  $75\Omega$  terminated at the monitor, the voltage typically ranges from 0 mV - 700 mV. This voltage indicates 0% - 100% intensity on the associated color. In a CRT, these voltages adjust the intensity of the electron beam for each color.

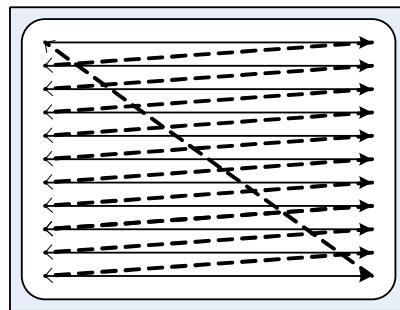

Figure 4-2: VGA Interface

Synchronization signaling is used to control the scanning of the electron beams, giving the stream of RGB video data positional significance. This signaling is a combination of two timing signals: horizontal synchronization and vertical synchronization (HSYNC and VSYNC). HSYNC resets the beam to the left edge of the screen, and when released it sweeps to the right. VSYNC resets the beam to the top of the screen, and when released it slowly sweeps downward. The monitor locks its vertical and horizontal sweep rates to the VSYNC and HSYNC frequencies, respectively.

Figure 4-3: Synchronization Signaling

The HSYNC and VSYNC signals are critical to the VGA interface, but can be encoded in several ways. The most basic is with separate sync signals for each, increasing the number of signals to 5: RGBHV. These syncs can be active high or low, and different resolutions typically have different combinations of sync polarity. A second encoding is composite HV, with HSYNC and VSYNC combined onto a single signal. This is performed through a logical XOR of the two signals. The end result looks like the original HSYNC signal, except that its polarity is inverted during VSYNC. This mode reduces the number of signals to 4. A third mode of encoding the sync signals is by combining the composite sync signal with the green data. This is referred to as "sync-on-green" (SOG). As mentioned previously, the typical signal levels are 0-700mV. SOG offsets this by 300mV to 300mV-1V. The drop from 300mV to 0 is used to indicate the composite sync.

Table 4-1: VGA Standards

|        | Pix Clock Freq (MHz) | HSync Freq (kHz) | Horizontal Timings (in clk cycles) |      |            |        | Vertical Timings (in Lines) |      |            |        |

|--------|----------------------|------------------|------------------------------------|------|------------|--------|-----------------------------|------|------------|--------|

|        |                      |                  | Front Porch                        | Sync | Back Porch | Active | Front Porch                 | Sync | Back Porch | Active |

| VGA60  | 40                   | 37.9             | 40                                 | 128  | 88         | 800    | 1                           | 4    | 23         | 600    |

| XGA60  | 65                   | 48.4             | 24                                 | 136  | 160        | 1024   | 3                           | 6    | 29         | 768    |

| SXGA60 | 108                  | 64               | 48                                 | 112  | 248        | 1280   | 1                           | 3    | 38         | 1024   |

| UXGA60 | 162                  | 75               | 64                                 | 192  | 304        | 1600   | 1                           | 3    | 46         | 1200   |

## Setting the PLL and Phase

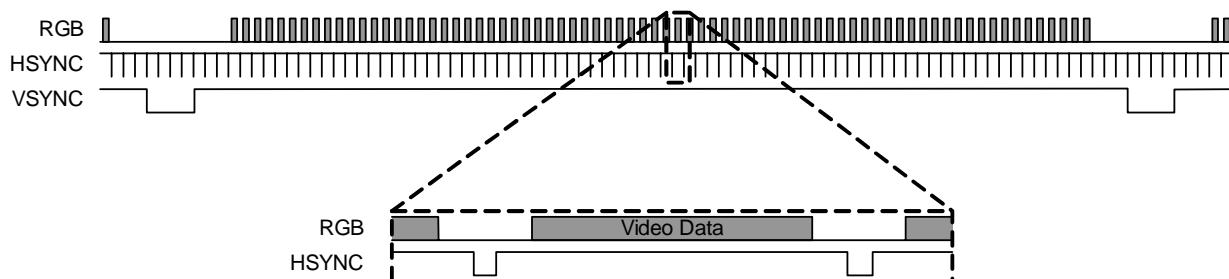

The AD9887A digitizes the analog video waveforms using three 8-bit analog-to-digital converters. For this analog-to-digital conversion to operate properly, it must sample each pixel at the appropriate time (Figure 4-4).

Figure 4-4: Pixel Sampling

To explain VGA sampling theory, it is useful to use a greatly simplified example. Figure 4-4 shows a single line from a frame with the horizontal front porch set to 1, the sync length set to 1, and the horizontal back porch set to 2. The line has 12 active pixels. In order to receive the video data, these are the only signals available.

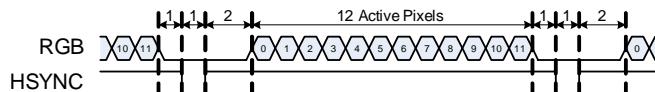

Figure 4-5 illustrates the ideal ADC sampling positions for this line. To generate these sample times, the AD9887A includes a PLL that locks to the incoming HSYNC, multiplying the HSYNC frequency by a factor set by the feedback divider. The frequency multiplication factor is set to the total number of clock cycles per HSYNC period. For the Figure 4-5 example, the multiplication value is  $1+1+2+12 = 16$ . The PLL in the AD9887A is free-running, so ADC samples occur during blanking (gray arrows) as well as active video

(black arrows). It is also important to note that the VCO frequency range and charge pump currents must be configured to match the expected frequency.

**Figure 4-5: Ideal ADC Sampling Positions**

Setting the feedback divider correctly results in the correct sample frequency, but the sample phase must also be set. Under ideal conditions, the phase delay would be  $T/2$ , to sample at the center of the pixels. This makes  $T/2$  a reasonable default value. Under actual operating conditions, there can be skew between the HSYNC signal and the video data thus requiring phase adjustment.

The process above is quite straightforward if one knows the proper settings for a given source. VESA timing standards are a good place to start for standard resolutions.

Unfortunately, graphics adapters often do not follow these exactly. In this case, the PLL divider value and phase must be adjusted to properly digitize the source. This process is beyond the scope of this document.

## Setting Black Levels

The primary mechanism for setting the black level is the input clamp. This clamps the input to ground, resulting in a DC offset in the coupling capacitor (just outside the AD9887A) equal to the difference between the current input voltage and ground. After the clamp is released, this difference is effectively subtracted from the raw input signal, resulting in an input signal reference to ground. For this circuit to function properly, this clamp should only be enabled when the input data is known to be black, such as during the horizontal back porch. The AD9887A has a clamp placement register to control the start of the clamp, in cycles after the falling edge of HSYNC. The clamp duration register controls the length of the clamp, in cycles.

The AD9887A also includes offset registers to offset the black level of each color individually. This control is typically not needed.

## Setting Gain

The AD9887A includes gain registers to adjust the input range of the ADC. Setting this too low results in a dim display, while setting it too high results in saturation and clipping of brighter colors.

## Bus Interface

The AD9887A data output is synchronous to a differential clock, DATACK. The pixel data is 8 bits per color. There are two pixel buses, A and B. There are also three key sync signals – HS, VS, and DE.

The data bus can be operated in either single pixel mode or dual pixel mode. Single pixel mode only uses port A and the clock rate is equal to the pixel rate. In dual pixel mode, port A carries even pixels and port B carries odd pixels, and the clock rate is half the pixel rate. The single pixel mode would be desirable to reduce the number of signals, but the AD9887A has a max DATACK frequency of 140 MHz, so for pixel rates greater than 140 MHz, the bus has to be operated in dual pixel mode.

The VSOUT output is an unmodified signal from the selected source. In analog mode with separate syncs, it is simply a passthrough from the VSYNC input. If the analog input is using a composite sync mode, VSOUT is the recovered vertical sync. In DVI mode, VSOUT is the decoded VSYNC from the serial digital stream.

In analog modes, the HSOUT is a reconstructed version of the HSYNC input or horizontal sync from the composite sync. Registers allow adjustment of the polarity and duration of this signal. In DVI mode, HSOUT is the decoded HSYNC from the serial digital stream.

DE is only available in DVI mode. This signal qualifies the pixel data as active pixels. In analog mode, this signal is high, and the pixels must be qualified elsewhere.

## DVI Input

The Digital Visual Interface (DVI) is a digital replacement for analog VGA. It is simply a digital version of the above described analog interface, with the same scan order and timing. Instead of analog voltages for the video data, the data is serially encoded digital values. This method for high-speed serial data is called transition minimized differential signaling (TMDS). TMDS is a combination of the electrical signal specification and the encoding scheme. The electrical signal specifications are similar to LVDS. The encoding scheme results in 10-bit symbols for each 8-bit byte, thus the encoded bit rate is 10x the byte rate. Each pixel is encoded as a 24-bit value, 8-bits for each color. Just like VGA, each color is transferred separately, so each color has its own differential pair. This means that the encoded bit rate is 10x the pixel rate. DVI also requires a separate clock reference signal, increasing the number of differential pairs to 4. The 10-bit encoding also includes some special symbols, allowing the sync signals to be included with the green signal (a digital SOG).

Other than the digital encoding, there is one significant difference in interfacing to DVI. The TMDS encoding also allows a data enable (DE) signal to be carried with the data. This signal is very useful to digital systems, as it easily qualifies the data. In the analog VGA scheme, the only way to know when the data is valid is to know specific timing relationships with respect to the sync signals.

## I2C Initialization Table (in Hex)

All I2C communications to the AD9887A is at address 0x9a/9B. See [Table 4-2](#) through [Table 4-6](#).

**Table 4-2: Analog VGA60**

| Register Name     | Register Address | Register Value | Description                                                                 |

|-------------------|------------------|----------------|-----------------------------------------------------------------------------|

| Active Interface  | 0x12             | 0x81           | Force selection of analog input                                             |

| PLL Div MSB       | 0x01             | 0x41           | PLL divider value. VGA60 has 1056 cycles per HSYNC period. 1056 - 1 = 0x41F |

| PLL Div LSB       | 0x02             | 0xF0           |                                                                             |

| VCO/CPMP          | 0x03             | 0x8C           | VCORNGE = 00, CURRENT = 011                                                 |

| Phase Adjust      | 0x04             | 0x80           | Default phase = T/2                                                         |

| Clamp Placement   | 0x05             | 0x24           | 36 cycles after HSYNC                                                       |

| Clamp Duration    | 0x06             | 0x24           | 36 cycles in duration                                                       |

| HSOUT Pulse width | 0x07             | 0x80           | 128 cycles in HSYNC                                                         |

**Table 4-3: Analog XGA60**

| Register Name     | Register Address | Register Value | Description                                                                   |

|-------------------|------------------|----------------|-------------------------------------------------------------------------------|

| Active Interface  | 0x12             | 0x81           | Force selection of analog input                                               |

| PLL Div MSB       | 0x01             | 0x53           | PLL divider value. XGA60 has 1344 cycles per HSYNC period. $1344 - 1 = 0x53F$ |

| PLL Div LSB       | 0x02             | 0xF0           |                                                                               |

| VCO/CPMP          | 0x03             | 0xB4           | VCORNGE = 01, CURRENT = 101                                                   |

| Phase Adjust      | 0x04             | 0x80           | Default phase = T/2                                                           |

| Clamp Placement   | 0x05             | 0x40           | 64 cycles after HSYNC                                                         |

| Clamp Duration    | 0x06             | 0x40           | 64 cycles in duration                                                         |

| HSOUT Pulse width | 0x07             | 0x88           | 136 cycles in HSYNC                                                           |

**Table 4-4: Analog SXGA60**

| Register Name     | Register Address | Register Value | Description                                                                    |