# **Excellent Integrated System Limited**

Stocking Distributor

Click to view price, real time Inventory, Delivery & Lifecycle Information:

Maxim Integrated DS2762AE+

For any questions, you can email us directly: <u>sales@integrated-circuit.com</u>

#### www.maxim-ic.com

#### **GENERAL DESCRIPTION**

The DS2762 high-precision Li+ battery monitor is a data-acquisition, information-storage, and safety-protection device tailored for cost-sensitive battery pack applications. This low-power device integrates precise temperature, voltage, and current measurement, nonvolatile (NV) data storage, and Li+protection into the small footprint of either a TSSOP package or flip-chip package. The DS2762 is a key component in applications including remaining capacity estimation, safety monitoring, and battery-specific data storage.

1-Wire is registered trademark of Dallas Semiconductor.

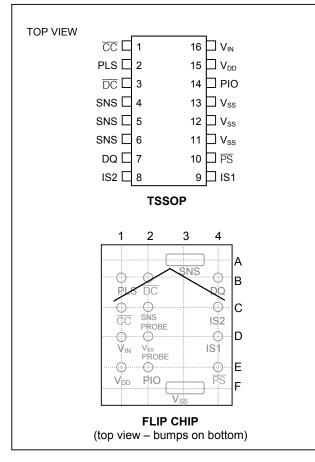

#### **PIN CONFIGURATIONS**

#### **FEATURES**

- Li+ Safety Circuit

Overvoltage Protection

Overcurrent/Short-Circuit Protection

Undervoltage Protection

- Host Alerted When Accumulated Current or Temperature Exceeds User-Selectable Limits

- 0V Battery Recovery Charge

- Available in Two Configurations: Internal 25mΩ Sense Resistor External User-Selectable Sense Resistor

- Current Accumulation: Internal Sense Resistor: 0.25mAhr LSB External Sense Resistor: 6.25µVhr LSB

- Voltage Measurement with 4.88mV Resolution

- Temperature Measurement Using Integrated Sensor with 0.125°C Resolution

- System Power Management and Control Feature Support

- 32 Bytes of Lockable EEPROM

- 16 Bytes of General-Purpose SRAM

- Dallas 1-Wire<sup>®</sup> Interface with Unique 64-Bit Device Address

- Low-Power Consumption: Active Current: 60µA typ, 90µA max Sleep Current: 1µA typ, 2µA max

# APPLICATIONS

PDAs Cell Phones/Smartphones Digital Cameras

### **ORDERING INFORMATION**

| PART      | TEMP RANGE     | PIN-PACKAGE |

|-----------|----------------|-------------|

| DS2762BE+ | -20°C to +70°C | 16 TSSOP    |

Selector Guide appears at end of data sheet, for additional options.

**Note:** Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, click here: <u>www.maxim-ic.com/errata</u>.

# ABSOLUTE MAXIMUM RATINGS

Voltage Range on PLS and  $\overline{\rm CC}$  Pin, Relative to V<sub>SS</sub> Voltage Range on PIO Pin, Relative to V<sub>SS</sub> Voltage Range on Any Other Pin, Relative to V<sub>SS</sub> Continuous Internal Sense Resistor Current Pulsed Internal Sense Resistor Current Operating Temperature Range Storage Temperature Range Soldering Temperature -0.3V to +18V -0.3V to +12V -0.3V to +6V ±2.5A ±50A for <100µs/s, <1000 pulses -40°C to +85°C -55°C to +125°C See IPC/JEDEC J-STD-020A Specification

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to the absolute maximum rating conditions for extended periods may affect device.

# **RECOMMENDED DC OPERATING CONDITIONS**

(2.5V  $\leq$  V\_{DD}  $\leq$  5.5V, T\_A = -20°C to +70°C.)

| PARAMETER      | SYMBOL          | CONDITIONS | MIN  | TYP MAX | UNITS |

|----------------|-----------------|------------|------|---------|-------|

| Supply Voltage | V <sub>DD</sub> | (Note 1)   | 2.5  | 5.5     | V     |

| Data Pin       | DQ              | (Note 1)   | -0.3 | +5.5    | V     |

# DC ELECTRICAL CHARACTERISTICS

$(2.5V \le V_{DD} \le 5.5V, T_A = -20^{\circ}C \text{ to } +70^{\circ}C.)$

| PARAMETER                         | SYMBOL             | CONDITIONS                                     | MIN                    | TYP | MAX | UNITS |

|-----------------------------------|--------------------|------------------------------------------------|------------------------|-----|-----|-------|

| Active Current                    | IACTIVE            | $DQ = V_{DD}$ , normal operation               |                        | 60  | 90  | μΑ    |

| Sleep Mode Current                | I <sub>SLEEP</sub> | DQ = 0V, no activity, $\overline{PS}$ floating |                        | 1   | 2   | μΑ    |

| Input Logic High: DQ, PIO         | VIH                | (Note 1)                                       | 1.5                    |     |     | V     |

| Input Logic High: PS              | V <sub>IH</sub>    | (Note 1)                                       | V <sub>DD</sub> - 0.2  | 2V  |     | V     |

| Input Logic Low: DQ, PIO          | VIL                | (Note 1)                                       |                        |     | 0.4 | V     |

| Input Logic Low: PS               | VIL                | (Note 1)                                       |                        |     | 0.2 | V     |

| Output Logic High: CC             | V <sub>OH</sub>    | I <sub>OH</sub> = -0.1mA (Note 1)              | V <sub>PLS</sub> - 0.4 | 4V  |     | V     |

| Output Logic High: DC             | V <sub>OH</sub>    | I <sub>OH</sub> = -0.1mA (Note 1)              | V <sub>DD</sub> - 0.4  | V   |     | V     |

| Output Logic Low: CC, DC          | V <sub>OL</sub>    | I <sub>OL</sub> = 0.1mA (Note 1)               |                        |     | 0.4 | V     |

| Output Logic Low: DQ, PIO         | V <sub>OL</sub>    | I <sub>OL</sub> = 4mA (Note 1)                 |                        |     | 0.4 | V     |

| DQ Pulldown Current               | I <sub>PD</sub>    |                                                |                        | 1   |     | μΑ    |

| Input Resistance: V <sub>IN</sub> | R <sub>IN</sub>    |                                                | 5                      |     |     | MΩ    |

| Internal Current-Sense Resistor   | R <sub>SNS</sub>   | +25°C                                          | 20                     | 25  | 30  | mΩ    |

| DQ Low to Sleep time              | t <sub>SLEEP</sub> |                                                | 2.1                    |     |     | S     |

# **ELECTRICAL CHARACTERISTICS: PROTECTION CIRCUITRY**

$(2.5V \le V_{DD} \le 5.5V, T_A = 0^{\circ}C \text{ to } +50^{\circ}C.)$

| PARAMETER                    | SYMBOL           | CONDITIONS   | MIN   | TYP   | MAX       | UNITS |

|------------------------------|------------------|--------------|-------|-------|-----------|-------|

| Ourse and the set of the set | N                |              | 4.325 | 4.350 | 4.375     |       |

| Overvoltage Detect           | Vov              | (Notes 1, 2) | 4.250 | 4.275 | 4.300     | V     |

| Charge Enable                | V <sub>CE</sub>  | (Note 1)     | 4.10  | 4.15  | 4.20      | V     |

| Undervoltage Detect          | V <sub>UV</sub>  | (Note 1)     | 2.5   | 2.6   | 2.7       | V     |

| Overcurrent Detect           | l <sub>oc</sub>  | (Note 3)     | 1.8   | 1.9   | 2.0<br>50 | А     |

| Overcurrent Detect           | V <sub>oc</sub>  | (Note 1, 4)  | 45    | 47.5  |           | mV    |

| Short-Circuit Detect         | I <sub>SC</sub>  | (Note 3)     | 5.0   | 8.0   | 11        | А     |

| Short-Circuit Detect         | V <sub>SC</sub>  | (Note 1)     | 150   | 200   | 250       | mV    |

| Overvoltage Delay            | t <sub>OVD</sub> |              | 0.8   | 1     | 1.2       | s     |

| Undervoltage Delay           | tuvo             |              | 90    | 100   | 110       | ms    |

| Overcurrent Delay            | t <sub>OCD</sub> |              | 5     | 10    | 20        | ms    |

| Short-Circuit Delay          | t <sub>SCD</sub> |              | 160   | 200   | 240       | μS    |

| Test Threshold               | V <sub>TP</sub>  |              | 0.5   | 1.0   | 1.5       | V     |

| Test Current                 | I <sub>TST</sub> |              | 10    | 20    | 40        | μA    |

| Recovery Charge Current      | I <sub>RC</sub>  | (Note 5)     | 0.5   | 1     | 2         | mA    |

# ELECTRICAL CHARACTERISTICS: TEMPERATURE, VOLTAGE, CURRENT

(2.5V  $\leq V_{\text{DD}} \leq$  5.5V,  $T_{\text{A}}$  = -20°C to +50°C.)

| PARAMETER                        | SYMBOL            | CONDITIONS        | MIN  | TYP    | MAX  | UNITS |

|----------------------------------|-------------------|-------------------|------|--------|------|-------|

| Temperature Resolution           | T <sub>LSB</sub>  |                   |      | 0.125  |      | °C    |

| Temperature Full-Scale Magnitude | T <sub>FS</sub>   |                   | 127  |        |      | °C    |

| Temperature Error                | T <sub>ERR</sub>  | (Note 6)          |      |        | ±3   | °C    |

| Voltage Resolution               | V <sub>LSB</sub>  |                   |      | 4.88   |      | mV    |

| Voltage Full-Scale Magnitude     | V <sub>FS</sub>   |                   | 4.75 |        |      | V     |

| Voltage Offset Error             | V <sub>OERR</sub> | (Note 7)          |      |        | 1    | LSB   |

| Voltage Gain Error               | V <sub>GERR</sub> |                   |      |        | 5    | %     |

| Oursent Desclution               |                   | (Note 3)          |      | 0.625  |      | mA    |

| Current Resolution               | I <sub>LSB</sub>  | (Note 4)          |      | 15.625 |      | μV    |

| Current Full Coole Megnitude     |                   | (Notes 3, 4)      | 1.9  | 2.56   |      | Α     |

| Current Full-Scale Magnitude     | I <sub>FS</sub>   | (Note 8)          |      | 64     |      | mV    |

| Current Offset Error             | I <sub>OERR</sub> | (Note 9)          |      |        | 1    | LSB   |

| Current Gain Error               |                   | (Notes 3, 10, 14) |      |        | 3    | %     |

|                                  | I <sub>GERR</sub> | (Note 4)          |      |        | 1    | 70    |

| Accumulated Current Resolution   | ~                 | (Note 3)          |      | 0.25   |      | mAhr  |

| Accumulated Current Resolution   | <b>q</b> ca       | (Note 4)          |      | 6.25   |      | μVhr  |

| Current Sampling Frequency       | f <sub>SAMP</sub> |                   |      | 1456   |      | Hz    |

| Internal Timebase Accuracy       | t <sub>ERR1</sub> | (Note 11)         |      | ±1     | ±3   | %     |

| internal fillebase Accuracy      | t <sub>ERR2</sub> | (Note 11)         |      |        | ±6.5 | %     |

# EEPROM RELIABILITY SPECIFICATION

$(2.5V \le V_{DD} \le 5.5V, T_A = -20^{\circ}C \text{ to } +70^{\circ}C.)$

| PARAMETER             | SYMBOL           | CONDITIONS | MIN    | TYP | MAX | UNITS  |

|-----------------------|------------------|------------|--------|-----|-----|--------|

| Copy to EEPROM Time   | t <sub>EEC</sub> |            |        | 2   | 10  | ms     |

| EEPROM Copy Endurance | N <sub>EEC</sub> | (Note 12)  | 25,000 |     |     | cycles |

# **ELECTRICAL CHARACTERISTICS: 1-WIRE INTERFACE**

$(2.5V \le V_{DD} \le 5.5V, T_A = -20^{\circ}C \text{ to } +70^{\circ}C.)$

| PARAMETER                                                        | SYMBOL            | CONDITIONS | MIN | TYP | MAX | UNITS |

|------------------------------------------------------------------|-------------------|------------|-----|-----|-----|-------|

| Time Slot                                                        | t <sub>SLOT</sub> |            | 60  |     | 120 | μS    |

| Recovery Time                                                    | t <sub>REC</sub>  |            | 1   |     |     | μS    |

| Write 0 Low Time                                                 | t <sub>LOW0</sub> |            | 60  |     | 120 | μS    |

| Write 1 Low Time                                                 | t <sub>LOW1</sub> |            | 1   |     | 15  | μS    |

| Read Data Valid                                                  | t <sub>RDV</sub>  |            |     |     | 15  | μS    |

| Reset Time High                                                  | t <sub>RSTH</sub> |            | 480 |     |     | μS    |

| Reset Time Low                                                   | t <sub>RSTL</sub> |            | 480 |     | 960 | μs    |

| Presence Detect High                                             | t <sub>PDH</sub>  |            | 15  |     | 60  | μs    |

| Presence Detect Low                                              | t <sub>PDL</sub>  |            | 60  |     | 240 | μs    |

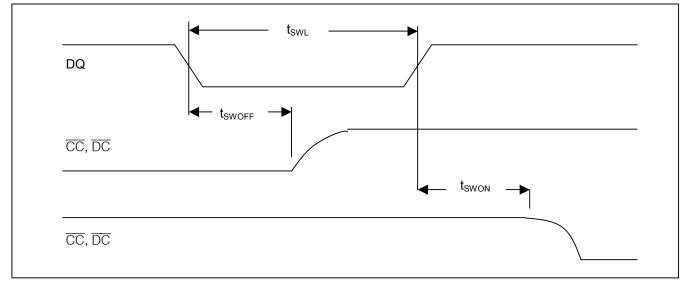

| SWAP Timing Pulse Width                                          | t <sub>SWL</sub>  |            | 0.2 |     | 120 | μS    |

| SWAP Timing Pulse Falling Edge to $\overline{\text{DC}}$ Release | tswoff            | (Note 13)  | 0   |     | 1   | μs    |

| SWAP Timing Pulse Rising Edge to $\overline{\text{DC}}$ Engage   | tswon             | (Note 13)  | 0   |     | 1   | μS    |

| DQ Capacitance                                                   | C <sub>DQ</sub>   |            |     |     | 60  | pF    |

Note 1: All voltages are referenced to V<sub>SS</sub>.

Note 2: See the Selector Guide section to determine the corresponding part number for each V<sub>OV</sub> value.

**Note 3:** Internal current-sense resistor configuration.

**Note 4:** External current-sense resistor configuration.

Note 5: Test conditions are PLS = 4.1V, V<sub>DD</sub> = 2.5V. Maximum current for conditions of PLS = 15V, V<sub>DD</sub> = 0V is 10mA.

Note 6: Self-heating due to output pin loading and sense resistor power dissipation can alter the reading from ambient conditions.

Note 7: Voltage offset measurement is with respect to V<sub>OV</sub> at +25°C.

**Note 8:** The current register supports measurement magnitudes up to 2.56A using the internal sense resistor option and 64mV with the external resistor option. Compensation of the internal sense resistor value for process and temperature variation can reduce the maximum reportable magnitude to 1.9A.

**Note 9:** Current offset error null to ±1LSB typically requires 3.5s in-system calibration by user.

**Note 10:** Current gain error specification applies to gain error in converting the voltage difference at IS1 and IS2, and excludes any error remaining after the DS2762 compensates for the internal sense resistor's temperature coefficient of 3700ppm/°C to an accuracy of ±500ppm/°C. The DS2762 does not compensate for external sense resistor characteristics, and any error terms arising from the use of an external sense resistor should be taken into account when calculating total current measurement error.

Note 11: Typical value for  $t_{ERR1}$  is specified at 3.6V and +25°C, max value is specified for 0°C to +50°C. Max value for  $t_{ERR2}$  is specified for -20°C to +70°C.

Note 12: Four-year data retention at +70°C.

**Note 13:** Typical load capacitance on  $\overline{DC}$  and  $\overline{CC}$  is 1000pF.

**Note 14:** Error at time of shipment from Dallas Semiconductor is 3% max. Board mounting processes may cause the current gain error to widen to as much as 10% for devices with the internal sense resistor option. Contact factory for on-board recalibration procedure for devices with the internal sense resistor option to improve accuracy.

# **PIN DESCRIPTION**

| PIN        |              |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|--------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSSOP      | FLIP<br>CHIP | SYMBOL                   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1          | C1           | CC                       | <b>Charge Protection Control Output.</b> Controls an external P-channel high-side charge protection FET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2          | B1           | PLS                      | <b>Battery Pack Positive Terminal Input.</b> The DS2762 monitors the pack plus terminal through PLS to detect overcurrent and overload conditions, as well as the presence of a charge source. Additionally, a charge path to recover a deeply depleted cell is provided from PLS to V <sub>DD</sub> . In sleep mode (with SWEN = 0), any capacitance or voltage source connected to PLS is discharged internally to V <sub>SS</sub> through 200µA (nominal) to assure reliable detection of a valid charge source. For details of other internal connections to PLS and associated conditions see the <i>Li</i> + <i>Protection Circuitry</i> section. |

| 3          | B2           | DC                       | <b>Discharge Protection Control Output.</b> Controls an external P-channel high-side discharge protection FET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4, 5, 6    | A3           | SNS                      | Sense Resistor Connection. Connect to the negative terminal of the battery pack. In the internal sense resistor configuration, the sense resistor is connected between $V_{SS}$ and SNS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7          | B4           | DQ                       | <b>Data Input/Out.</b> 1-Wire data line. Open-drain output driver. Connect this pin to the DATA terminal of the battery pack. Pin has an internal $1\mu$ A pulldown for sensing disconnection.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8          | C4           | IS2                      | Current-Sense Input. This pin is internally connected to SNS through a 4.7k $\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9          | D4           | IS1                      | <b>Current-Sense Input.</b> This pin is internally connected to $V_{SS}$ through a 4.7k $\Omega$ resistor.<br>Connect a 0.1µF capacitor between IS1 and IS2 to complete a lowpass input filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10         | E4           | PS                       | <b>Power Switch Sense Input.</b> The device wakes up from sleep mode when it senses the closure of a switch to $V_{SS}$ on this pin. Pin has an internal $1\mu A$ pullup to $V_{DD}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 11, 12, 13 | F3           | V <sub>SS</sub>          | <b>Device Ground.</b> Connect directly to the negative terminal of the Li+ cell. For the external sense resistor configuration, connect the sense resistor between $V_{SS}$ and SNS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 14         | E2           | PIO                      | <b>Programmable I/O Pin.</b> Can be configured to be used to control and monitor user-<br>defined external circuitry or as an interrupt output to alert the host when preset current<br>accumulator or temperature limits are exceeded. Open drain to $V_{SS}$ .                                                                                                                                                                                                                                                                                                                                                                                        |

| 15         | E1           | V <sub>DD</sub>          | <b>Power-Supply Input.</b> Connect to the positive terminal of the Li+ cell through a decoupling network.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 16         | D1           | V <sub>IN</sub>          | Voltage Sense Input. The voltage of the Li+ cell is monitored through this input pin. This pin has a weak pullup to $V_{\text{DD}}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|            | C2           | SNS<br>Probe             | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| _          | D2           | V <sub>SS</sub><br>Probe | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

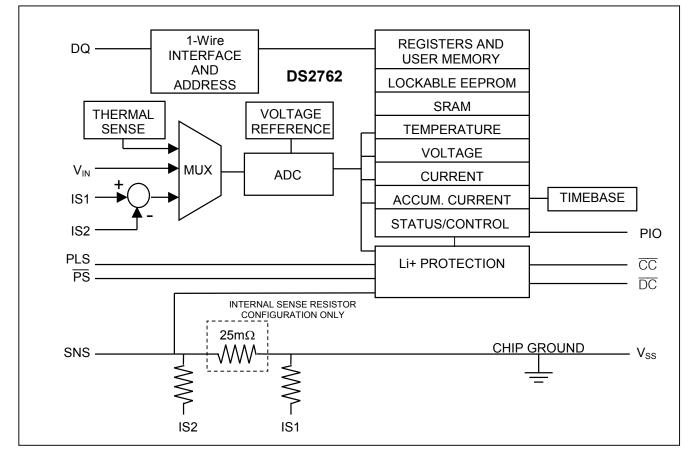

## Figure 1. Block Diagram

# DETAILED DESCRIPTION

The DS2762 high-precision Li+ battery monitor is a data-acquisition, information-storage, and safety-protection device tailored for cost-sensitive battery pack applications. This low-power device integrates precise temperature, voltage, and current measurement, nonvolatile (NV) data storage, and Li+ protection into the small footprint of either a TSSOP package or flip-chip package. The DS2762 is a key component in applications including remaining capacity estimation, safety monitoring, and battery-specific data storage.

Through its 1-Wire interface, the DS2762 gives the host system read/write access to status and control registers, instrumentation registers, and general-purpose data storage. Each device has a unique factory-programmed 64-bit net address that allows it to be individually addressed by the host system, supporting multibattery operation.

The DS2762 is capable of performing temperature, voltage, and current measurement to a resolution sufficient to support process monitoring applications such as battery charge control, remaining capacity estimation, and safety monitoring. Temperature is measured using an on-chip sensor, eliminating the need for a separate thermistor. Bidirectional current measurement and accumulation are accomplished using either an internal  $25m\Omega$  sense resistor or an external device. The DS2762 also features a programmable I/O pin that allows the host system to sense and control other electronics in the pack, including switches, vibration motors, speakers, and LEDs. This pin may also be used to alert the host when preset accumulated current or temperature limits are exceeded.

Three types of memory are provided on the DS2762 for battery information storage: EEPROM, lockable EEPROM, and SRAM. EEPROM memory saves important battery data in true NV memory that is unaffected by severe battery depletion, accidental shorts, or ESD events. Lockable EEPROM becomes ROM when locked to provide additional security for unchanging battery data. SRAM provides inexpensive storage for temporary data.

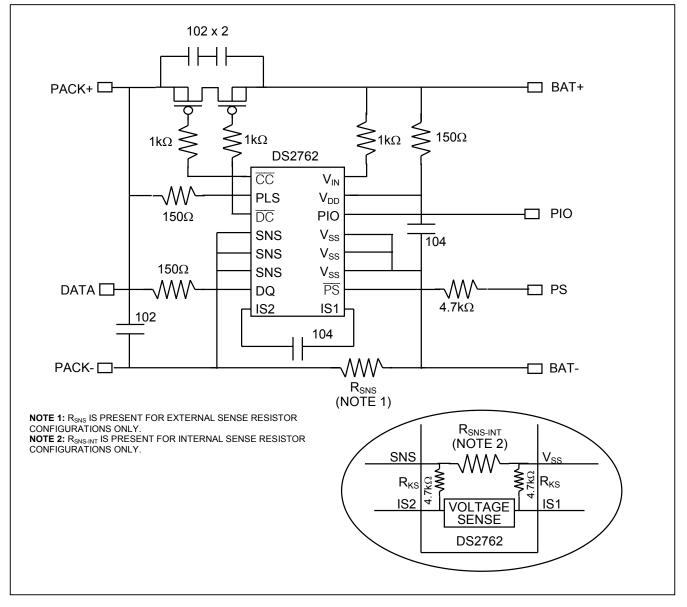

# Figure 2. Application Example

### **POWER MODES**

The DS2762 has two power modes: active and sleep. While in active mode, the DS2762 continually measures current, voltage, and temperature to provide data to the host system and to support current accumulation and Li+ safety monitoring. In sleep mode, the DS2762 ceases these activities. The DS2762 enters sleep mode when any of the following conditions occurs:

- The PMOD bit in the Status Register has been set to 1 and the DQ line is low for longer than 2s (pack disconnection).

- The voltage on V<sub>IN</sub> drops below undervoltage threshold V<sub>UV</sub> for t<sub>UVD</sub> (cell depletion).

- The pack is disabled through the issuance of a SWAP command (SWEN bit = 1).

The DS2762 returns to active mode when any of the following occurs:

- The PMOD bit has been set to 1 and the SWEN bit is set to 0 and the DQ line is pulled high (pack connection).

- The PS pin is pulled low (power switch).

- The voltage on PLS becomes greater than the voltage on V<sub>IN</sub> (charger connection) with the SWEN bit set to 0.

- The pack is enabled through the issuance of a SWAP command (SWEN bit = 1).

The DS2762 defaults to active mode when power is first applied.

# Li+ PROTECTION CIRCUITRY

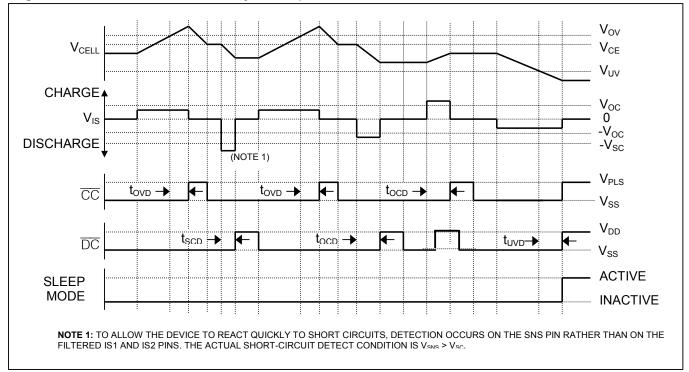

During active mode, the DS2762 constantly monitors cell voltage and current to protect the battery from overcharge (overvoltage), overdischarge (undervoltage), and excessive charge and discharge currents (overcurrent, short circuit). Conditions and DS2762 responses are described in the following sections and summarized in Table 1 and Figure 3.

|                        |                                    | ACTIVATION       |                                                      |                                                                          |

|------------------------|------------------------------------|------------------|------------------------------------------------------|--------------------------------------------------------------------------|

| CONDITION              | THRESHOLD                          | DELAY            | RESPONSE                                             | RELEASE THRESHOLD                                                        |

| Overvoltage            | V <sub>IN</sub> > V <sub>OV</sub>  | tovd             | $\overline{\text{CC}}$ high                          | $V_{IN} < V_{CE}$ , or<br>$V_{IS} \le -2mV$                              |

| Undervoltage           | $V_{IN} < V_{UV}$                  | t <sub>uvd</sub> | CC, DC high,<br>Sleep Mode                           | V <sub>PLS</sub> > V <sub>DD</sub> <sup>(1)</sup><br>(charger connected) |

| Overcurrent, Charge    | $V_{IS}$ > $V_{OC}$ <sup>(2)</sup> | t <sub>OCD</sub> | $\overline{\text{CC}}$ , $\overline{\text{DC}}$ high | $V_{PLS}$ < $V_{DD}$ - $V_{TP}$ <sup>(3)</sup>                           |

| Overcurrent, Discharge | $V_{IS} < -V_{OC}^{(2)}$           | tocp             | DC high                                              | $V_{PLS}$ > $V_{DD}$ - $V_{TP}$ <sup>(4)</sup>                           |

| Short Circuit          | $V_{SNS}$ > $V_{SC}$               | t <sub>SCD</sub> | DC high                                              | $V_{PLS}$ > $V_{DD}$ - $V_{TP}$ <sup>(4)</sup>                           |

#### Table 1. Li+ Protection Conditions and DS2762 Responses

$V_{IS} = V_{IS1} - V_{IS2}$ . Logic high =  $V_{PLS}$  for  $\overline{CC}$  and  $V_{DD}$  for  $\overline{DC}$ . All voltages are with respect to  $V_{SS}$ .  $I_{SNS}$  references current delivered from pin SNS.

Note 1: If  $V_{DD} < 2.2V$ , release is delayed until the recovery charge current ( $I_{RC}$ ) passed from PLS to  $V_{DD}$  charges the battery and allows  $V_{DD}$  to exceed 2.2V.

Note 2: For the internal sense resistor configuration, the overcurrent thresholds are expressed in terms of current: I<sub>SNS</sub> > I<sub>OC</sub> for charge direction and I<sub>SNS</sub> < -I<sub>OC</sub> for discharge direction.

- **Note 3:** With test current I<sub>TST</sub> flowing from PLS to V<sub>SS</sub> (pulldown on PLS).

- Note 4: With test current I<sub>TST</sub> flowing from V<sub>DD</sub> to PLS (pullup on PLS).

**Overvoltage.** If the cell voltage on V<sub>IN</sub> exceeds the overvoltage threshold, V<sub>OV</sub>, for a period longer than overvoltage delay, t<sub>OVD</sub>, the DS2762 shuts off the external charge FET and sets the OV flag in the protection register. When the cell voltage falls below charge enable threshold V<sub>CE</sub>, the DS2762 turns the charge FET back on (unless another protection condition prevents it). Discharging remains enabled during overvoltage, and the DS2762 re-enables the charge FET before V<sub>IN</sub> < V<sub>CE</sub> if a discharge current of -80mA (V<sub>IS</sub> ≤ -2mV) or less is detected.

**Undervoltage.** If the voltage of the cell drops below undervoltage threshold,  $V_{UV}$ , for a period longer than undervoltage delay,  $t_{UVD}$ , the DS2762 shuts off the charge and discharge FETs, sets the UV flag in the protection

register, and enters sleep mode. The DS2762 provides a current-limited ( $I_{RC}$ ) recovery charge path from PLS to  $V_{DD}$  to gently charge severely depleted cells. The recovery path is enabled when  $0 \le V_{DD} < 3V$  (typ). Once  $V_{DD}$  reaches 3V (typ), the DS2762 returns to normal operation, awaiting connection of a charger to turn on the charge FET and pull out of sleep mode.

**Overcurrent, Charge Direction.** The voltage difference between the IS1 pin and the IS2 pin ( $V_{IS} = V_{IS1} - V_{IS2}$ ) is the filtered voltage drop across the current-sense resistor. If  $V_{IS}$  exceeds overcurrent threshold  $V_{OC}$  for a period longer than overcurrent delay  $t_{OCD}$ , the DS2762 shuts off both external FETs and sets the COC flag in the protection register. The charge current path is not re-established until the voltage on the PLS pin drops below  $V_{DD} - V_{TP}$ . The DS2762 provides a test current of value  $I_{TST}$  from PLS to  $V_{SS}$  to pull PLS down to detect the removal of the offending charge current source.

**Overcurrent, Discharge Direction.** If  $V_{IS}$  is less than  $-V_{OC}$  for a period longer than  $t_{OCD}$ , the DS2762 shuts off the external discharge FET and sets the DOC flag in the protection register. The discharge current path is not reestablished until the voltage on PLS rises above  $V_{DD}$  -  $V_{TP}$ . The DS2762 provides a test current of value  $I_{TST}$  from  $V_{DD}$  to PLS to pull PLS up to detect the removal of the offending low-impedance load.

**Short Circuit.** If the voltage on the SNS pin with respect to  $V_{SS}$  exceeds short-circuit threshold  $V_{SC}$  for a period longer than short-circuit delay  $t_{SCD}$ , the DS2762 shuts off the external discharge FET and sets the DOC flag in the protection register. The discharge current path is not re-established until the voltage on PLS rises above  $V_{DD}$  -  $V_{TP}$ . The DS2762 provides a test current of value  $I_{TST}$  from  $V_{DD}$  to PLS to pull PLS up to detect the removal of the short circuit.

### Figure 3. Li+ Protection Circuitry Example Waveforms

**Summary.** All of the protection conditions described above are ORed together to affect the  $\overline{CC}$  and  $\overline{DC}$  outputs.

- DC = (Undervoltage) or (Overcurrent, Either Direction) or (Short Circuit) or (Protection Register Bit DE = 0) or (Sleep Mode)

- CC = (Overvoltage) or (Undervoltage) or (Overcurrent, Charge Direction) or (Protection Register bit CE = 0) or (Sleep Mode)

# **CURRENT MEASUREMENT**

In active mode, the DS2762 continually measures the current flow into and out of the battery by measuring the voltage drop across a current-sense resistor. The DS2762 is available in two configurations: 1) internal  $25m\Omega$  current-sense resistor and 2) external user-selectable sense resistor. In either configuration, the DS2762 considers the voltage difference between pins IS1 and IS2 ( $V_{IS} = V_{IS1} - V_{IS2}$ ) to be the filtered voltage drop across the sense resistor. A positive  $V_{IS}$  value indicates current is flowing into the battery (charging), while a negative  $V_{IS}$  value indicates current is flowing).

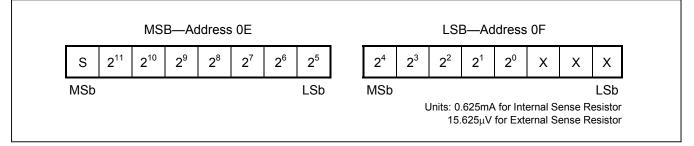

$V_{IS}$  is measured with a signed resolution of 12 bits. The current register is updated in two's-complement format every 88ms with an average of 128 readings. Currents outside the register range are reported at the range limit. Figure 4 shows the format of the current register.

For the internal sense resistor configuration, the DS2762 maintains the current register in units of amps, with a resolution of 0.625mA and full-scale range of no less than  $\pm$ 1.9A (see *Note* 7 on I<sub>FS</sub> spec for more details). The DS2762 automatically compensates for internal sense resistor process variations and temperature effects when reporting current.

For the external sense resistor configuration, the DS2762 writes the measured  $V_{IS}$  voltage to the current register, with a  $15.625\mu V$  resolution and a full-scale  $\pm 64m V$  range.

#### Figure 4. Current Register Format

# CURRENT ACCUMULATOR

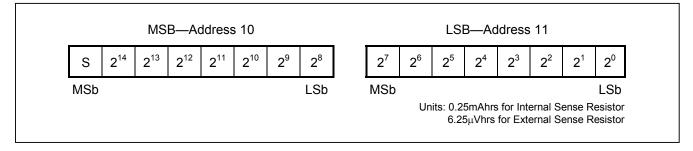

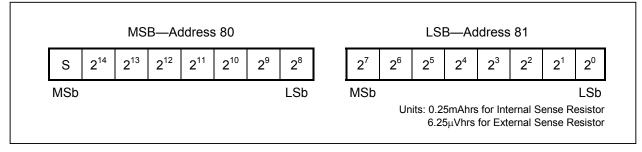

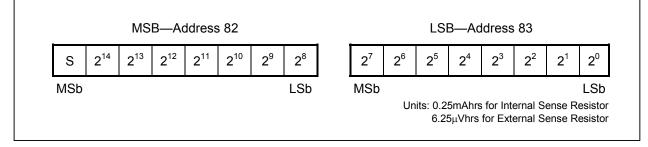

The current accumulator facilitates remaining capacity estimation by tracking the net current flow into and out of the battery. Current flow into the battery increments the current accumulator while current flow out of the battery decrements it. Data is maintained in the current accumulator in two's-complement format. Figure 5 shows the format of the current accumulator.

When the internal sense resistor is used, the DS2762 maintains the current accumulator in units of amp-hours, with a 0.25mAhrs resolution and full-scale  $\pm$ 8.2Ahrs range. When using an external sense resistor, the DS2762 maintains the current accumulator in units of volt-hours, with a 6.25µVhrs resolution and a full-scale  $\pm$ 205mVhrs range.

The current accumulator is a read/write register that can be altered by the host system as needed.

# Figure 5. Current Accumulator Format

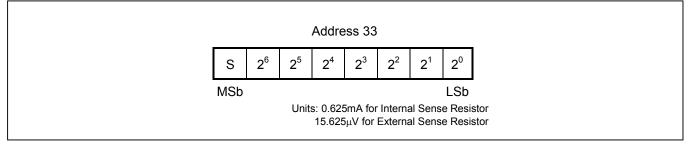

# CURRENT OFFSET COMPENSATION

Current measurement and current accumulation are internally compensated for offset on a continual basis minimizing error resulting from variations in device temperature and voltage. Additionally, a constant bias can be used to alter any other sources of offset. This bias resides in EEPROM address 33h in two's-complement format and is subtracted from each current measurement. The current offset bias is applied to the internal and external sense resistor configurations. The factory default for the current offset bias is 0.

### Figure 6. Current Offset Bias

#### **VOLTAGE MEASUREMENT**

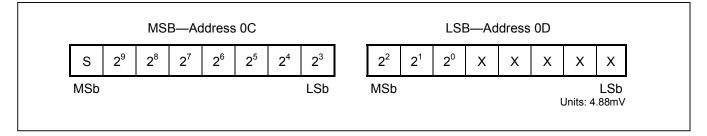

The DS2762 continually measures the voltage between pins  $V_{IN}$  and  $V_{SS}$  over a 0 to 4.75V range. The voltage register is updated in two's-complement format every 3.4ms with a 4.88mV resolution. Voltages above the maximum register value are reported as the maximum value. Figure 7 shows the voltage register format.

#### Figure 7. Voltage Register Format

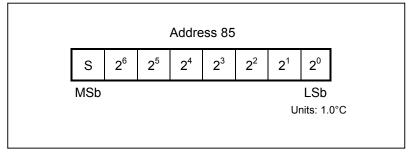

### TEMPERATURE MEASUREMENT

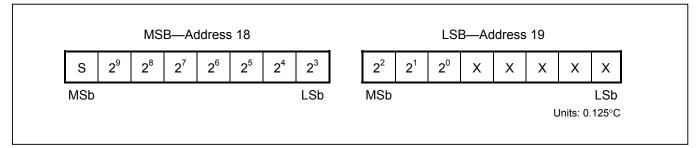

The DS2762 uses an integrated temperature sensor to continually measure battery temperature. Temperature measurements are placed in the temperature register every 220ms in two's-complement format with a  $0.125^{\circ}$ C resolution over a  $\pm 127^{\circ}$ C range. Figure 8 shows the temperature register format.

#### Figure 8. Temperature Register Format

# PROGRAMMABLE I/O

To use the PIO pin as described in this section, the IE bit (bit 2) of the Status Register must be set to 0.

To use the PIO pin as an output, write the desired output value to the PIO bit in the special feature register. Writing a 0 to the PIO bit enables the PIO output driver, pulling the PIO pin to  $V_{SS}$ . Writing a 1 to the PIO bit disables the output driver, allowing the PIO pin to be pulled high or used as an input. To sense the value on the PIO pin, read the PIO bit. The DS2762 turns off the PIO output driver and sets the PIO bit high when in sleep mode or when DQ is low for more than 2s, regardless of the state of the PMOD bit.

# ALARM COMPARATORS

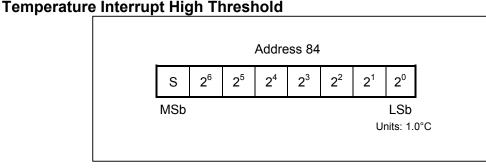

The PIO pin can be programmed as an interrupt output (active low) to alert the host system of critical events. To use the Interrupt feature, the Interrupt Enable (IE) bit (bit 2) of the Status Register must be set to a 1. Interrupt threshold values can be programmed by the user in the designated SRAM memory registers in the formats and locations found in Figure 9. Since these thresholds are located in SRAM memory, they must be reprogrammed if a loss of power to the DS2762 occurs. The PIO line will go low to interrupt the system host and indicate that one of the following events has occurred:

- Accumulated Current > Current Accumulator Interrupt High Threshold

- Accumulated Current < Current Accumulator Interrupt Low Threshold

- Temperature > Temperature Interrupt High Threshold

- Temperature < Temperature Interrupt Low Threshold

The host may then poll the DS2762 to determine which threshold has been met or exceeded.

### Figure 9. Interrupt Threshold Register Formats

#### **Current Accumulator Interrupt High Threshold**

### **Current Accumulator Interrupt Low Threshold**

### **Temperature Alarm Low Threshold**

### **POWER SWITCH INPUT**

The DS2762 provides a power control function that uses the discharge protection FET to gate battery power to the system. The  $\overline{PS}$  pin, internally pulled to V<sub>DD</sub> through a 1µA current source, is continuously monitored for a low-impedance connection to V<sub>SS</sub>. If the DS2762 is in sleep mode, the detection of a low on the  $\overline{PS}$  pin causes the device to transition into active mode, turning on the discharge FET. If the DS2762 is already in active mode, activity on  $\overline{PS}$  has no effect other than the latching of its logic low level in the  $\overline{PS}$  bit in the special feature register. The reading of a 0 in the  $\overline{PS}$  bit should be immediately followed by writing a 1 to the  $\overline{PS}$  bit to ensure that a subsequent low forced on the  $\overline{PS}$  pin is latched into the  $\overline{PS}$  bit.

### MEMORY

The DS2762 has a 256-byte linear address space with registers for instrumentation, status, and control in the lower 32 bytes, with lockable EEPROM and SRAM memory occupying portions of the remaining address space. All EEPROM memory is general purpose except addresses 30h, 31h, and 33h, which should be written with the default values for the protection register, status register, and current offset register, respectively. All SRAM memory is general purpose. When the MSB of any two-byte register is read, both the MSB and LSB are latched and held for the duration of the read data command to prevent updates during the read and ensure synchronization between the two register bytes. For consistent results, always read the MSB and the LSB of a two-byte register during the same read data command sequence.

EEPROM memory is shadowed by RAM to eliminate programming delays between writes and to allow the data to be verified by the host system before being copied to EEPROM. All reads and writes to/from EEPROM memory actually access the shadow RAM. In unlocked EEPROM blocks, the write data command updates shadow RAM. In locked EEPROM blocks, the write data command copies the contents of shadow RAM to EEPROM in an unlocked block of EEPROM but has no effect on locked blocks. The recall-data command copies the contents of a block of EEPROM to shadow RAM regardless of whether the block is locked or not.

#### Table 2. Memory Map

| ADDRESS (HEX) | DESCRIPTION                                                         | <b>READ/WRITE</b> |

|---------------|---------------------------------------------------------------------|-------------------|

| 00            | Protection Register                                                 | R/W               |

| 01            | Status Register                                                     | R                 |

| 02–06         | Reserved                                                            |                   |

| 07            | EEPROM Register                                                     | R/W               |

| 08            | Special Feature Register                                            | R/W               |

| 09–0B         | Reserved                                                            |                   |

| 0C            | Voltage Register MSB                                                | R                 |

| 0D            | Voltage Register LSB                                                | R                 |

| 0E            | Current Register MSB                                                | R                 |

| 0F            | Current Register LSB                                                | R                 |

| 10            | Accumulated Current Register MSB                                    | R/W               |

| 11            | Accumulated Current Register LSB                                    | R/W               |

| 12–17         | Reserved                                                            |                   |

| 18            | Temperature Register MSB                                            | R                 |

| 19            | Temperature Register LSB                                            | R                 |

| 1A–1F         | Reserved                                                            |                   |

| 20–2F         | EEPROM, block 0                                                     | R/W*              |

| 30–3F         | EEPROM, block 1                                                     | R/W*              |

| 40–7F         | Reserved                                                            |                   |

| 80            | SRAM (Optional Accumulated Current Interrupt<br>High Threshold MSB) | R/W               |

| 81            | SRAM (Optional Accumulated Current Interrupt<br>High Threshold LSB) | R/W               |

| 82            | SRAM (Optional Accumulated Current Interrupt<br>Low Threshold MSB)  | R/W               |

| 83            | SRAM (Optional Accumulated Current Interrupt<br>Low Threshold LSB)  | R/W               |

| 84            | SRAM (Optional Temperature Interrupt High<br>Threshold)             | R/W               |

| 85            | SRAM (Optional Temperature Interrupt Low<br>Threshold)              | R/W               |

| 86-8F         | SRAM                                                                | R/W               |

| 90–FF         | Reserved                                                            |                   |

\* Each EEPROM block is read/write until locked by the LOCK command, after which it is read-only.

# **PROTECTION REGISTER**

The protection register consists of flags that indicate protection circuit status and switches that give conditional control over the charging and discharging paths. Bits OV, UV, COC, and DOC are set when corresponding protection conditions occur and remain set until cleared by the host system. The default values of the CE and DE bits of the protection register are stored in lockable EEPROM in the corresponding bits in address 30h. A recall data command for EEPROM block 1 recalls the default values into CE and DE. Figure 10 shows the format of the protection register. The function of each bit is described in detail in the following paragraphs.

#### Figure 10. Protection Register Format

| ADDRESS 00 |       |       |       |                 |       |       |       |  |

|------------|-------|-------|-------|-----------------|-------|-------|-------|--|

| BIT 7      | BIT 6 | BIT 5 | BIT 4 | BIT 3           | BIT 2 | BIT 1 | BIT 0 |  |

| OV         | UV    | COC   | DOC   | $\overline{CC}$ | DC    | CE    | DE    |  |

**OV**—Overvoltage Flag. When set to 1, this bit indicates the battery pack has experienced an overvoltage condition. This bit must be reset by the host system.

**UV**—Undervoltage Flag. When set to 1, this bit indicates the battery pack has experienced an undervoltage condition. This bit must be reset by the host system.

**COC**—Charge Overcurrent Flag. When set to 1, this bit indicates the battery pack has experienced a chargedirection overcurrent condition. This bit must be reset by the host system.

**DOC**—Discharge Overcurrent Flag. When set to 1, this bit indicates the battery pack has experienced a dischargedirection overcurrent condition. This bit must be reset by the host system.

$\overline{CC}$ — $\overline{CC}$  Pin Mirror. This read-only bit mirrors the state of the  $\overline{CC}$  output pin.

$\overline{\text{DC}}$ — $\overline{\text{DC}}$  Pin Mirror. This read-only bit mirrors the state of the  $\overline{\text{DC}}$  output pin.

**CE**—Charge Enable. Writing a 0 to this bit disables charging ( $\overline{CC}$  output high, external charge FET off) regardless of cell or pack conditions. Writing a 1 to this bit enables charging, subject to override by the presence of any protection conditions. The DS2762 automatically sets this bit to 1 when it transitions from sleep mode to active mode.

**DE**—Discharge Enable. Writing a 0 to this bit disables discharging ( $\overline{DC}$  output high, external discharge FET off) regardless of cell or pack conditions. Writing a 1 to this bit enables discharging, subject to override by the presence of any protection conditions. The DS2762 automatically sets this bit to 1 when it transitions from sleep mode to active mode.

# STATUS REGISTER

The default values for the status register bits are stored in lockable EEPROM in the corresponding bits of address 31h. A recall data command for EEPROM block 1 recalls the default values into the status register bits. The format of the status register is shown in Figure 11. The function of each bit is described in detail in the following paragraphs.

### Figure 11. Status Register Format

| ADDRESS 01 |       |       |       |       |       |       |       |  |  |  |  |

|------------|-------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| BIT 7      | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |  |  |  |  |

| Х          | Х     | PMOD  | RNAOP | SWEN  | IE    | Х     | Х     |  |  |  |  |

X—Reserved Bits.

**PMOD**—Sleep Mode Enable. A value of 1 in this bit enables the DS2762 to enter sleep mode when the DQ line goes low for greater than 2s and to leave sleep mode when the DQ line goes high. A value of 0 disables DQ-related transitions into and out of sleep mode. This bit is read-only. The desired default value should be set in bit 5 of address 31h. The factory default is 0.

**RNAOP**—Read Net Address Opcode. A value of 0 in this bit sets the opcode for the read net address command to 33h, while a 1 sets the opcode to 39h. This bit is read-only. The desired default value should be set in bit 4 of address 31h. The factory default is 0.

**SWEN**—SWAP Command Enable. A value of 1 in this bit location enables the recognition of a SWAP command. If set to 0, SWAP commands are ignored. The desired default value should be set in bit 3 of address 31h. This bit is read-only. The factory default is 0.

**IE**—Interrupt Enable. A value of 1 in this bit location enables the PIO pin to be used as an interrupt to the host system when either the user-programmed thresholds for Accumulated Current and Temperature are met or exceeded. If set to 0, the PIO pin performs as noted in the *PIO* section. This bit is read-only. The desired default value should be set in bit 2 of address 31h. The factory default is 0.

# EEPROM REGISTER

The format of the EEPROM register is shown in Figure 12. The function of each bit is described in detail in the following paragraphs.

### Figure 12. EEPROM Register Format

|       | ADDRESS 07 |       |       |       |       |       |       |

|-------|------------|-------|-------|-------|-------|-------|-------|

| BIT 7 | BIT 6      | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

| EEC   | LOCK       | Х     | Х     | Х     | Х     | BL1   | BL0   |

**EEC**—EEPROM Copy Flag. A 1 in this read-only bit indicates that a copy data command is in progress. While this bit is high, writes to EEPROM addresses are ignored. A 0 in this bit indicates that data may be written to unlocked EEPROM blocks.

**LOCK**—EEPROM Lock Enable. When this bit is 0, the lock command is ignored. Writing a 1 to this bit enables the lock command. After the lock command is executed, the LOCK bit is reset to 0. The factory default is 0.

**BL1**—EEPROM Block 1 Lock Flag. A 1 in this read-only bit indicates that EEPROM block 1 (addresses 30 to 3F) is locked (read-only) while a 0 indicates block 1 is unlocked (read/write).

**BL0**—EEPROM Block 0 Lock Flag. A 1 in this read-only bit indicates that EEPROM block 0 (addresses 20 to 2F) is locked (read-only) while a 0 indicates block 0 is unlocked (read/write).

**X**—Reserved Bits.

#### SPECIAL FEATURE REGISTER

The format of the special feature register is shown in Figure 13. The function of each bit is described in detail in the following paragraphs.

#### Figure 13. Special Feature Register Format

| ADDRESS 08      |       |       |       |       |       |       |       |

|-----------------|-------|-------|-------|-------|-------|-------|-------|

| BIT 7           | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

| $\overline{PS}$ | PIO   | MSTR  | Х     | Х     | Х     | Х     | Х     |

$\overline{PS}$ — $\overline{PS}$  Pin Latch. This bit latches a low state on the  $\overline{PS}$  pin, and is cleared only by writing a 1 to this location. Writing this bit to a 1 immediately upon reading of a 0 value is recommended.

PIO—PIO Pin Sense and Control. See the Programmable I/O section for details on this read/write bit.

**MSTR**—SWAP Master Status Bit. This bit indicates whether a device has been selected through the SWAP command. Selection of this device through the SWAP command and the appropriate net address results in setting this bit, indicating that this device is the master. A 0 signifies that this device is not the master.

**X**—Reserved Bits.

# 1-Wire BUS SYSTEM

The 1-Wire bus is a system that has a single bus master and one or more slaves. A multidrop bus is a 1-Wire bus with multiple slaves. A single-drop bus has only one slave device. In all instances, the DS2762 is a slave device. The bus master is typically a microprocessor in the host system. The discussion of this bus system consists of four topics: 64-bit net address, hardware configuration, transaction sequence, and 1-Wire signaling.

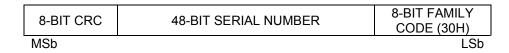

# **64-BIT NET ADDRESS**

Each DS2762 has a unique, factory-programmed 1-Wire net address that is 64 bits in length. The first eight bits are the 1-Wire family code (30h for DS2762). The next 48 bits are a unique serial number. The last eight bits are a cyclic redundancy check (CRC) of the first 56 bits (see Figure 14). The 64-bit net address and the 1-Wire I/O circuitry built into the device enable the DS2762 to communicate through the 1-Wire protocol detailed in the *1-Wire Bus System* section of this data sheet.

# Figure 14. 1-Wire Net Address Format

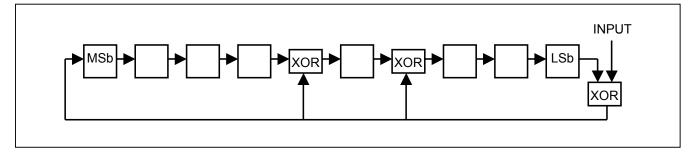

# **CRC GENERATION**

The DS2762 has an 8-bit CRC stored in the most significant byte of its 1-Wire net address. To ensure error-free transmission of the address, the host system can compute a CRC value from the first 56 bits of the address and compare it to the CRC from the DS2762. The host system is responsible for verifying the CRC value and taking action as a result. The DS2762 does not compare CRC values and does not prevent a command sequence from proceeding as a result of a CRC mismatch. Proper use of the CRC can result in a communication channel with a very high level of integrity.

The CRC can be generated by the host using a circuit consisting of a shift register and XOR gates as shown in Figure 15, or it can be generated in software. Additional information about the Dallas 1-Wire CRC is available in *Application Note 27: Understanding and Using Cyclic Redundancy Checks with Dallas Semiconductor Touch Memory Products* (www.maxim-ic.com/appnoteindex).

In the circuit in Figure 15, the shift register bits are initialized to 0. Then, starting with the least significant bit of the family code, one bit at a time is shifted in. After the 8th bit of the family code has been entered, then the serial number is entered. After the 48th bit of the serial number has been entered, the shift register contains the CRC value.

### Figure 15. 1-Wire CRC Generation Block Diagram

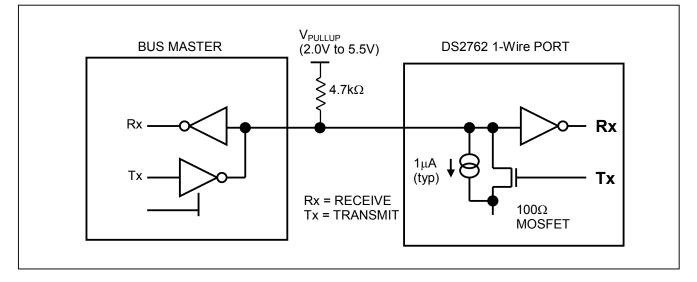

## HARDWARE CONFIGURATION

Because the 1-Wire bus has only a single line, it is important that each device on the bus be able to drive it at the appropriate time. To facilitate this, each device attached to the 1-Wire bus must connect to the bus with open-drain or tri-state output drivers. The DS2762 used an open-drain output driver as part of the bidirectional interface circuitry shown in Figure 16. If a bidirectional pin is not available on the bus master, separate output and input pins can be connected together.

The 1-Wire bus must have a pullup resistor at the bus-master end of the bus. For short line lengths, the value of this resistor should be approximately  $5k\Omega$ . The idle state for the 1-Wire bus is high. If, for any reason, a bus transaction must be suspended, the bus must be left in the idle state to properly resume the transaction later. If the bus is left low for more than  $120\mu s$ , slave devices on the bus begin to interpret the low period as a reset pulse, effectively terminating the transaction.

# TRANSACTION SEQUENCE

The protocol for accessing the DS2762 through the 1-Wire port is as follows:

- Initialization

- Net Address Command

- Function Command

- Transaction/Data

The sections that follow describe each of these steps in detail.

All transactions of the 1-Wire bus begin with an initialization sequence consisting of a reset pulse transmitted by the bus master, followed by a presence pulse simultaneously transmitted by the DS2762 and any other slaves on the bus. The presence pulse tells the bus master that one or more devices are on the bus and ready to operate. For more details, see the *1-Wire Signaling* section.

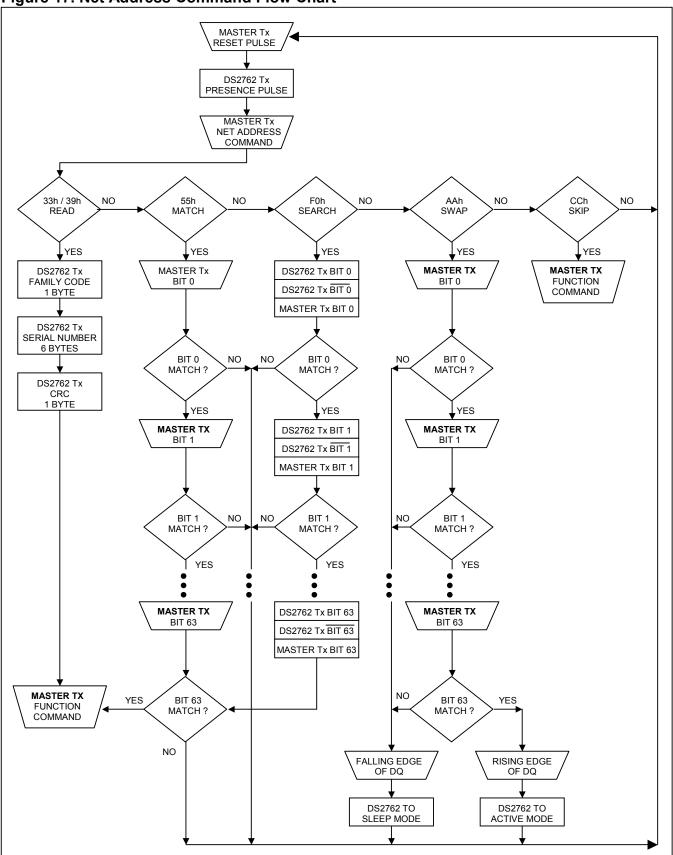

#### NET ADDRESS COMMANDS

Once the bus master has detected the presence of one or more slaves, it can issue one of the net address commands described in the following paragraphs. The name of each ROM command is followed by the 8-bit opcode for that command in square brackets. Figure 17 presents a transaction flowchart of the net address commands.

**Read Net Address [33h or 39h].** This command allows the bus master to read the DS2762's 1-Wire net address. This command can only be used if there is a single slave on the bus. If more than one slave is present, a data collision occurs when all slaves try to transmit at the same time (open drain produces a wired-AND result). The RNAOP bit in the status register selects the opcode for this command, with RNAOP = 0 indicating 33h, and RNAOP = 1 indicating 39h.

**Match Net Address [55h].** This command allows the bus master to specifically address one DS2762 on the 1-Wire bus. Only the addressed DS2762 responds to any subsequent function command. All other slave devices ignore the function command and wait for a reset pulse. This command can be used with one or more slave devices on the bus.

**Skip Net Address [CCh].** This command saves time when there is only one DS2762 on the bus by allowing the bus master to issue a function command without specifying the address of the slave. If more than one slave device is present on the bus, a subsequent function command can cause a data collision when all slaves transmit data at the same time.

**Search Net Address [F0h].** This command allows the bus master to use a process of elimination to identify the 1-Wire net addresses of all slave devices on the bus. The search process involves the repetition of a simple threestep routine: read a bit, read the complement of the bit, then write the desired value of that bit. The bus master performs this simple three-step routine on each bit location of the net address. After one complete pass through all 64 bits, the bus master knows the address of one device. The remaining devices can then be identified on additional iterations of the process. See Chapter 5 of the *Book of DS19xx <u>i</u>Button<sup>®</sup> Standards* for a comprehensive discussion of a net address search, including an actual example (<u>www.maxim-ic.com/iButtonBook</u>).

**SWAP [AAh].** SWAP is a ROM level command specifically intended to aid in distributed multiplexing applications and is described specifically with regards to power control using the 27xx series of products. The term power control refers to the ability of the DS2762 to control the flow of power into or out the battery pack using control pins  $\overline{DC}$  and  $\overline{CC}$ . The SWAP command is issued followed by the net address. The effect is to cause the addressed device to enable power to or from the system while simultaneously (break-before-make) deselecting and powering down (SLEEP) all other packs. This switching sequence is controlled by a timing pulse issued on the DQ line following the net address. The falling edge of the pulse is used to disable power with the rising edge enabling power flow by the selected device. The DS2762 recognizes a SWAP command, device address, and timing pulse only if the SWEN bit is set.

#### **FUNCTION COMMANDS**

After successfully completing one of the net address commands, the bus master can access the features of the DS2762 with any of the function commands described in the following paragraphs and summarized in Table 3. The name of each function is followed by the 8-bit opcode for that command in square brackets.

**Read Data [69h, XX].** This command reads data from the DS2762 starting at memory address XX. The LSb of the data in address XX is available to be read immediately after the MSb of the address has been entered. Because the address is automatically incremented after the MSb of each byte is received, the LSb of the data at address XX + 1 is available to be read immediately after the MSb of the data at address XX. If the bus master continues to read beyond address FFh, the DS2762 outputs logic 1 until a reset pulse occurs. Addresses labeled "Reserved" in the memory map contain undefined data. The read data command can be terminated by the bus master with a reset pulse at any bit boundary.

iButton is a registered trademark of Dallas Semiconductor.

Write Data [6Ch, XX]. This command writes data to the DS2762 starting at memory address XX. The LSb of the data to be stored at address XX can be written immediately after the MSb of address has been entered. Because the address is automatically incremented after the MSb of each byte is written, the LSb to be stored at address XX + 1 can be written immediately after the MSb to be stored at address XX. If the bus master continues to write beyond address FFh, the DS2762 ignores the data. Writes to read-only addresses, reserved addresses and locked EEPROM blocks are ignored. Incomplete bytes are not written. Writes to unlocked EEPROM blocks are to shadow RAM rather than EEPROM. See the *Memory* section for more details.

**Copy Data [48h, XX].** This command copies the contents of shadow RAM to EEPROM for the 16-byte EEPROM block containing address XX. Copy data commands that address locked blocks are ignored. While the copy data command is executing, the EEC bit in the EEPROM register is set to 1 and writes to EEPROM addresses are ignored. Reads and writes to non-EEPROM addresses can still occur while the copy is in progress. The copy data command execution time,  $t_{EEC}$ , is 2ms typical and starts after the last address bit is transmitted.

**Recall Data [B8h, XX].** This command recalls the contents of the 16-byte EEPROM block containing address XX to shadow RAM.

**Lock [6Ah, XX].** This command locks (write-protects) the 16-byte block of EEPROM memory containing memory address XX. The LOCK bit in the EEPROM register must be set to I before the lock command is executed. If the LOCK bit is 0, the lock command has no effect. The lock command is permanent; a locked block can never be written again.

| COMMAND     | FUNCTION                                                           | COMMAND<br>PROTOCOL | BUS STATE AFTER<br>COMMAND PROTOCOL | BUS DATA                |

|-------------|--------------------------------------------------------------------|---------------------|-------------------------------------|-------------------------|

| Read Data   | Reads data from memory<br>starting at address XX                   | 69h, XX             | Master Rx                           | Up to 256 bytes of data |

| Write Data  | Writes data to memory starting at address XX                       | 6Ch, XX             | Master Tx                           | Up to 256 bytes of data |

| Copy Data   | Copies shadow RAM data to<br>EEPROM block containing<br>address XX | 48h, XX             | Bus idle                            | None                    |

| Recall Data | Recalls EEPROM block<br>containing address XX to<br>shadow RAM     | B8h, XX             | Bus idle                            | None                    |

| Lock        | Permanently locks the block<br>of EEPROM<br>containing address XX  | 6Ah, XX             | Bus idle                            | None                    |

#### **Table 3. Function Commands**

### Figure 17. Net Address Command Flow Chart

PACK+

PACK-

# I/O SIGNALING

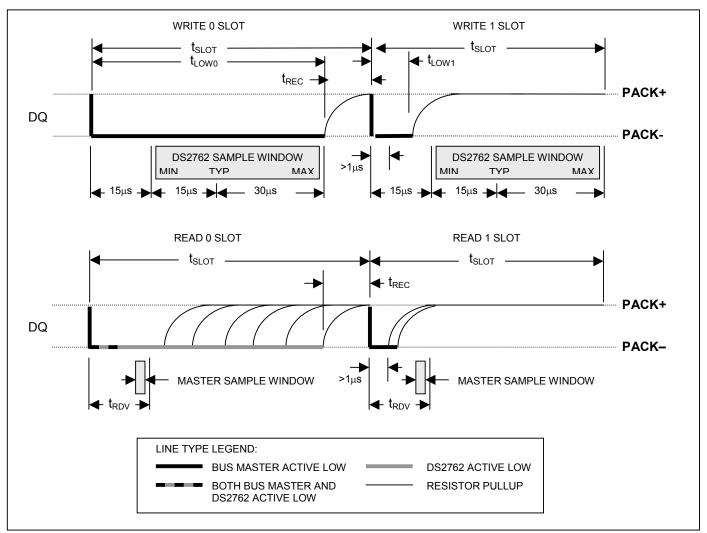

The 1-Wire bus requires strict signaling protocols to ensure data integrity. The four protocols used by the DS2762 are as follows: the initialization sequence (reset pulse followed by presence pulse), write 0, write 1, and read data. The bus master initiates all these types of signaling except the presence pulse.

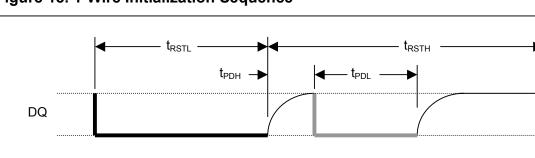

The initialization sequence required to begin any communication with the DS2762 is shown in Figure 18. A presence pulse following a reset pulse indicates that the DS2762 is ready to accept a net address command. The bus master transmits (Tx) a reset pulse for  $t_{RSTL}$ . The bus master then releases the line and goes into receive mode (Rx). The 1-Wire bus line is then pulled high by the pullup resistor. After detecting the rising edge on the DQ pin, the DS2762 waits for  $t_{PDH}$  and then transmits the presence pulse for  $t_{PDL}$ .

BUS MASTER ACTIVE LOW

BOTH BUS MASTER AND

DS2762 ACTIVE LOW

#### Figure 18. 1-Wire Initialization Sequence

LINE TYPE LEGEND:

# WRITE-TIME SLOTS

A write-time slot is initiated when the bus master pulls the 1-Wire bus from a logic-high (inactive) level to a logic-low level. There are two types of write-time slots: write 1 and write 0. All write-time slots must be  $t_{SLOT}$  (60µs to 120µs) in duration with a 1µs minimum recovery time,  $t_{REC}$ , between cycles. The DS2762 samples the 1-Wire bus line between 15µs and 60µs after the line falls. If the line is high when sampled, a write 1 occurs. If the line is low when sampled, a write 0 occurs (Figure 19). For the bus master to generate a write 1 time slot, the bus line must be pulled low and then released, allowing the line to be pulled high within 15µs after the start of the write time slot. For the host to generate a write 0 time slot, the bus line must be pulled low and held low for the duration of the write-time slot.

DS2762 ACTIVE LOW

**RESISTOR PULLUP**

# **READ-TIME SLOTS**

A read-time slot is initiated when the bus master pulls the 1-Wire bus line from a logic-high level to a logic-low level. The bus master must keep the bus line low for at least 1 $\mu$ s and then release it to allow the DS2762 to present valid data. The bus master can then sample the data  $t_{RDV}$  (15 $\mu$ s) from the start of the read-time slot. By the end of the read-time slot, the DS2762 releases the bus line and allows it to be pulled high by the external pullup resistor. All read-time slots must be  $t_{SLOT}$  (60 $\mu$ s to 120 $\mu$ s) in duration with a 1 $\mu$ s minimum recovery time,  $t_{REC}$ , between cycles. See Figure 19 for more information.

## Figure 19. 1-Wire Write- and Read-Time Slots

Figure 20. Swap Command Timing

| PART MARKING     |          | DESCRIPTION                                                                   |  |  |

|------------------|----------|-------------------------------------------------------------------------------|--|--|

| DS2762AE+        | DS2762A  | TSSOP, External Sense Resistor, 4.275V V <sub>OV</sub> , Lead-Free            |  |  |

| DS2762BE+        | DS2762B  | TSSOP, External Sense Resistor, 4.35V V <sub>OV</sub> , Lead-Free             |  |  |

| DS2762AE+T&R     | DS2762A  | DS2762AE+ on Tape-and-Reel, Lead-Free                                         |  |  |

| DS2762BE+T&R     | DS2762B  | DS2762BE+ on Tape-and-Reel, Lead-Free                                         |  |  |

| DS2762AE+025     | 2762A25  | TSSOP, 25m $\Omega$ Sense Resistor, 4.275V V <sub>OV</sub> , Lead-Free        |  |  |

| DS2762BE+025     | 2762B25  | TSSOP, 25m $\Omega$ Sense Resistor, 4.35V V <sub>OV</sub> , Lead-Free         |  |  |

| DS2762AE+025/T&R | 2762A25  | DS2762AE+025 in Tape-and-Reel, Lead-Free                                      |  |  |

| DS2762BE+025/T&R | 2762B25  | DS2762BE+025 in Tape-and-Reel, Lead-Free                                      |  |  |

| DS2762AX-025/T&R | DS2762AR | Flip-Chip, 25m $\Omega$ Sense Resistor, Tape-and-Reel, 4.275V $V_{\text{OV}}$ |  |  |

| DS2762BX-025/T&R | DS2762BR | Flip-Chip, 25m $\Omega$ Sense Resistor, Tape-and-Reel, 4.35V $V_{\text{OV}}$  |  |  |

| DS2762AX/T&R     | DS2762A  | Flip-Chip, External Sense Resistor, Tape-and-Reel, 4.275V $V_{\text{OV}}$     |  |  |

| DS2762BX/T&R     | DS2762B  | Flip-Chip, External Sense Resistor, Tape-and-Reel, 4.35V Vov                  |  |  |

| DS2762AE         | DS2762A  | TSSOP, External Sense Resistor, 4.275V V <sub>OV</sub>                        |  |  |

| DS2762BE         | DS2762B  | TSSOP, External Sense Resistor, 4.35V V <sub>OV</sub>                         |  |  |

| DS2762AE/T&R     | DS2762A  | DS2762AE on Tape-and-Reel                                                     |  |  |

| DS2762BE/T&R     | DS2762B  | DS2762BE on Tape-and-Reel                                                     |  |  |

| DS2762AE-025     | 2762A25  | TSSOP, 25m $\Omega$ Sense Resistor, 4.275V V <sub>ov</sub>                    |  |  |

| DS2762BE-025     | 2762B25  | TSSOP, 25m $\Omega$ Sense Resistor, 4.35V V <sub>OV</sub>                     |  |  |

| DS2762AE-025/T&R | 2762A25  | DS2762AE-025 in Tape-and-Reel                                                 |  |  |

| DS2762BE-025/T&R | 2762B25  | DS2762BE-025 in Tape-and-Reel                                                 |  |  |

# SELECTOR GUIDE

**Note:** Additional V<sub>OV</sub> options are available, contact Maxim/Dallas Semiconductor sales.

### PACKAGE INFORMATION

(For the latest package outline information, go to www.maxim-ic.com/DallasPackInfo.)

Maxim/Dallas Semiconductor cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim/Dallas Semiconductor product. No circuit patent licenses are implied. Maxim/Dallas Semiconductor reserves the right to change the circuitry and specifications without notice at any time. Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 © 2003 Maxim Integrated Products • Printed USA