## **Excellent Integrated System Limited**

Stocking Distributor

Click to view price, real time Inventory, Delivery & Lifecycle Information:

Bourns Inc.

TISP6NTP2CDR-S

For any questions, you can email us directly: sales@integrated-circuit.com

### Distributor of Bourns Inc.: Excellent Integrated System Limited

Datasheet of TISP6NTP2CDR-S - SURGE PROT THYRIST 155VDUAL SLIC

Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

#### TISP6NTP2C

#### QUAD FORWARD-CONDUCTING P-GATE THYRISTORS PROGRAMMABLE OVERVOLTAGE PROTECTORS

## TISP6NTP2C High Voltage Ringing SLIC Protector

**Independent Tracking Overvoltage Protection for Two SLICs:**

- Dual Voltage-Programmable Protectors

- Supports Battery Voltages Down to -155 V

- Low 5 mA max. Gate Triggering Current

- High 150 mA min. (70 °C) Holding Current

- Specified 2/10 Limiting Voltage

- Small Outline Surface Mount Package

- Full 0 °C to 70 °C Temperature Range

#### **Rated for Common Impulse Waveforms**

| Voltage Impulse<br>Wave Shape | Current Impulse<br>Wave Shape | I <sub>PPSM</sub> |

|-------------------------------|-------------------------------|-------------------|

| maro onapo                    | maro onapo                    | Α                 |

| 10/1000                       | 10/1000                       | 25                |

| 10/700                        | 5/310                         | 40                |

| 2/10                          | 2/10                          | 90                |

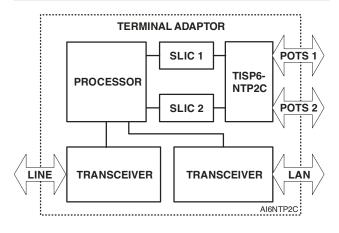

#### **Typical TISP6NTP2C Router Application**

## D Package (Top View) G3.G4 r 3 K3 MDRXAN

#### **Device Symbol**

...... UL Recognized Components

The TISP6NTP2C has been designed for short loop systems such as:

- WILL (Wireless In the Local Loop)

- FITL (Fibre In The Loop)

- SOHO (Small Office Home Office)

ISDN-TA (Integrated Services Digital Network Terminal Adaptors)

- DAML (Digital Added Main Line, Pair Gain)

#### **How to Order**

| Device     | Package                 | Order As                 |                |

|------------|-------------------------|--------------------------|----------------|

| TISP6NTP2C | D (8-pin Small-Outline) | R (Embossed Tape Reeled) | TISP6NTP2CDR-S |

\*RoHS Directive 2002/95/EC Jan 27 2003 including Annex MARCH 2002 - REVISED JULY 2008

Specifications are subject to change without notice.

Customers should verify actual device performance in their specific applications.

# **Distributor of Bourns Inc.: Excellent Integrated System Limited**Datasheet of TISP6NTP2CDR-S - SURGE PROT THYRIST 155VDUAL SLIC Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

## TISP6NTP2C High Voltage Ringing SLIC Protector **BOURNS**®

#### **Description (Continued)**

The systems described often have the need to source two POTS (Plain Old Telephone Service) lines, one for a telephone and the other for a facsimile machine. In a single surface mount package, the TISP6NTP2C protects the two POTS line SLICs (Subscriber Line Interface Circuits) against overvoltages caused by lightning, a.c. power contact and induction.

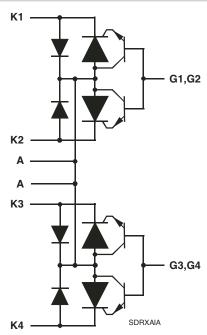

The TISP6NTP2C has an array of four buffered P-gate forward conducting thyristors with twin commoned gates and a common anode connection. Each thyristor cathode has a separate terminal connection. An antiparallel anode-cathode diode is connected across each thyristor. The buffer transistors reduce the gate supply current.

In use, the cathodes of an TISP6NTP2C thyristors are connected to the four conductors of two POTS lines (see applications information). Each gate is connected to the appropriate negative voltage battery feed of the SLIC driving that line pair. By having separate gates, each SLIC can be protected at a voltage level related to the negative supply voltage of that individual SLIC. The anode of the TISP6NTP2C is connected to the SLIC common. The TISP6NTP2C voltage and current ratings also make it suitable for the protection of ISDN d.c. feeds of down to -115 V (ETSI Technical Report ETR 080:1993, ranges 1 to 5).

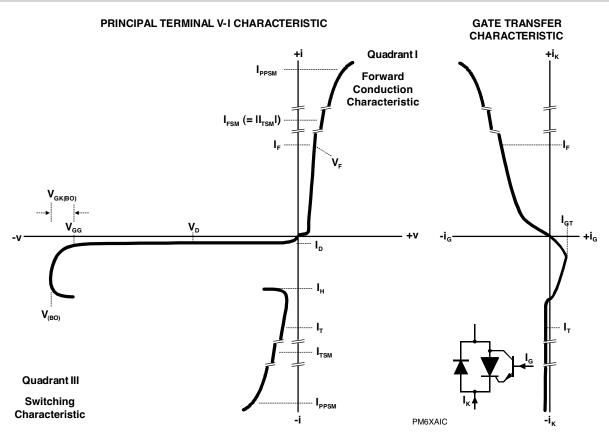

Positive overvoltages are clipped to common by forward conduction of the TISP6NTP2C antiparallel diode. Negative overvoltages are initially clipped close to the SLIC negative supply by emitter follower action of the TISP6NTP2C buffer transistor. If sufficient clipping current flows, the TISP6NTP2C thyristor will regenerate and switch into a low voltage on-state condition. As the overvoltage subsides, the high holding current of the TISP6NTP2C helps prevent d.c. latchup.

#### Absolute Maximum Ratings, 0 $^{\circ}$ C $\leq$ T $_{J}$ $\leq$ 70 $^{\circ}$ C (Unless Otherwise Noted)

| Rating                                                                         | Symbol            | Value       | Unit |

|--------------------------------------------------------------------------------|-------------------|-------------|------|

| Repetitive peak off-state voltage, V <sub>GK</sub> = 0                         | V <sub>DRM</sub>  | -170        | V    |

| Repetitive peak gate-cathode voltage, V <sub>KA</sub> = 0                      | V <sub>GKRM</sub> | -167        | V    |

| Non-repetitive peak on-state pulse current (see Notes 1 and 2)                 |                   |             |      |

| 10/1000 (Telcordia (Bellcore) GR-1089-CORE, Issue 2, February 1999, Section 4) | l                 | 25          | Α    |

| 5/320 (ITU-T K.20, K.21& K.45, K.44 open-circuit voltage wave shape 10/700)    | I <sub>PPSM</sub> | 40          | ^    |

| 2/10 (Telcordia (Bellcore) GR-1089-CORE, Issue 2, February 1999, Section 4)    |                   | 90          |      |

| Non-repetitive peak on-state current, 50 Hz/60 Hz (see Notes 1 and 2)          |                   |             |      |

| 0.1 s                                                                          | I <sub>TSM</sub>  | 7           | А    |

| 1 s                                                                            |                   | 2.7         |      |

| 5 s                                                                            |                   | 1.5         |      |

| 300 s                                                                          |                   | 0.45        |      |

| 900 s                                                                          |                   | 0.43        |      |

| Non-repetitive peak gate current, 1/2 µs pulse, cathodes commoned (see Note 1) | I <sub>GSM</sub>  | +25         | Α    |

| Operating free-air temperature range                                           | T <sub>A</sub>    | -40 to +85  | °C   |

| Junction temperature                                                           | T <sub>J</sub>    | -40 to +150 | °C   |

| Storage temperature range                                                      | T <sub>stg</sub>  | -40 to +150 | °C   |

- NOTES: 1. Initially, the protector must be in thermal equilibrium. The surge may be repeated after the device returns to its initial conditions. Gate voltage range is -20 V to -155 V.

- These non-repetitive rated currents are peak values for either polarity. The rated current values may be applied to any cathodeanode terminal pair. Additionally, all cathode-anode terminal pairs may have their rated current values applied simultaneously (in this case the anode terminal current will be four times the rated current value of an individual terminal pair).

#### **Recommended Operating Conditions**

|                | Component                                                                                    | Min | Тур | Max | Unit |

|----------------|----------------------------------------------------------------------------------------------|-----|-----|-----|------|

| C <sub>G</sub> | Gate decoupling capacitor                                                                    | 100 | 220 |     | nF   |

| R.             | Series resistor for GR-1089-CORE intra-building surge survival, section 4.5.9, tests 1 and 2 | 5   | 50  |     | Ω    |

| $R_S$          | Series resistor for K.20, K.21 and K.45 coordination with a 400 V primary protector          | 10  | 50  |     | Ω    |

## TISP6NTP2C High Voltage Ringing SLIC Protector **BOURNS**®

#### Electrical Characteristics, 0 $^{\circ}$ C $\leq$ T $_{J}$ $\leq$ 70 $^{\circ}$ C (Unless Otherwise Noted)

|                     | Parameter                               | Test Conditions                                                                                                       | Min  | Тур | Max       | Unit     |

|---------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|-----|-----------|----------|

| I <sub>D</sub>      | Off-state current                       | $V_D = V_{DRM}$ , $V_{GK} = 0$                                                                                        |      |     | -5        | μΑ       |

|                     |                                         |                                                                                                                       |      |     | -50       | μΑ       |

| V <sub>(BO)</sub>   | Ramp breakover voltage                  | UL 497B, dv/dt $\leq$ ±100 V/ $\mu$ s, di/dt = ±10 A/ $\mu$ s, $V_{GG}$ = -100 V, Maximum ramp value = ±10 A          |      |     | -112      | V        |

| V <sub>(BO)</sub>   | Impulse breakover voltage               | 2/10 μs, $I_{TM}$ = -27 A, di/dt = -27 A/μs, $R_S$ = 50 Ω, $V_{GG}$ = -100 V, (see Note 3)                            |      |     | -115      | V        |

| V <sub>GK(BO)</sub> | Gate-cathode impulse breakover voltage  | 2/10 μs, $I_{TM}$ = -27 A, di/dt = -27 A/μs, $R_S$ = 50 Ω, $V_{GG}$ = -100 V, (see Note 3)                            |      |     | 15        | ٧        |

| V <sub>F</sub>      | Forward voltage                         | $I_F = 5 \text{ A}, t_w = 200 \ \mu \text{s}$                                                                         |      |     | 3         | V        |

| V <sub>FRM</sub>    | Ramp peak forward recovery voltage      | UL 497B, dv/dt $\leq$ ±100 V/ $\mu$ s, di/dt = ±10 A/ $\mu$ s, Maximum ramp value = ±10 A $T_J = 25~^{\circ}\text{C}$ |      |     | 5         | V        |

| V <sub>FRM</sub>    | Impulse peak forward recovery voltage   | 2/10 μs, $I_{TM}$ = -27 A, di/dt = -27 A/μs, $R_S$ = 50 $\Omega$ , (see Note 3)                                       |      |     | 12        | V        |

| I <sub>H</sub>      | Holding current                         | $I_T = -1 \text{ A, di/dt} = 1 \text{A/ms, V}_{GG} = -100 \text{ V}$                                                  | -150 |     |           | mA       |

| I <sub>GKS</sub>    | Gate reverse current                    | $V_{GG} = V_{GK} = V_{GKRM}, V_{KA} = 0$ $T_{J} = 25  ^{\circ}C$                                                      |      |     | -5<br>-50 | μA<br>μA |

|                     |                                         | T <sub>.1</sub> = 25 °C                                                                                               |      |     | 5         | mΑ       |

| I <sub>GT</sub>     | Gate trigger current                    | $I_T = -3 \text{ A}, t_{p(g)} \ge 20  \mu\text{s}, V_{GG} = -100 \text{ V}$                                           |      |     | 6         | mA       |

| V <sub>GT</sub>     | Gate-cathode trigger voltage            | $I_T = -3 \text{ A}, t_{p(g)} \ge 20  \mu\text{s}, V_{GG} = -100 \text{ V}$                                           |      |     | 2.5       | V        |

| C <sub>KA</sub>     | Cathode-anode off-<br>state capacitance | $f = 1 \text{ MHz}, V_d = 1 \text{ V}, I_G = 0, \text{ (see Note 4)}$ $V_D = -3 \text{ V}$ $V_D = -48 \text{ V}$      |      |     | 100<br>50 | pF<br>pF |

|                     | otato capacitante                       | V <sub>D</sub> = -46 V                                                                                                |      |     | 50        | þΓ       |

NOTES: 3. GR-1089-CORE intra-building 2/10, 1.5 kV conditions with 20 MHz bandwidth. The diode forward recovery and the thyristor gate impulse breakover (overshoot) are not strongly dependent of the SLIC supply voltage value (V<sub>GG</sub>).

#### **Thermal Characteristics**

|                   | Parameter                               | Test Conditions                                     | Min | Тур | Max | Unit |

|-------------------|-----------------------------------------|-----------------------------------------------------|-----|-----|-----|------|

| р                 | Junction to free air thermal resistance | T <sub>A</sub> = 70 °C, EIA/JESD51-3 PCB,           |     |     | 160 | °C/W |

| H <sub>θ</sub> JA | Junction to nee an thermal resistance   | EIA/JESD51-2 environment, P <sub>tot</sub> = 0.52 W |     |     | 100 | C/VV |

<sup>4.</sup> These capacitance measurements employ a three terminal capacitance bridge incorporating a guard circuit. The unmeasured device terminals are a.c. connected to the guard terminal of the bridge.

## TISP6NTP2C High Voltage Ringing SLIC Protector **BOURNS**®

#### **Parameter Measurement Information**

Figure 1. Principal Terminal and Gate Transfer Characteristics

# Distributor of Bourns Inc.: Excellent Integrated System Limited Datasheet of TISP6NTP2CDR-S - SURGE PROT THYRIST 155VDUAL SLIC Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

## TISP6NTP2C High Voltage Ringing SLIC Protector **BOURNS®**

#### **APPLICATIONS INFORMATION**

#### **SLIC Protection**

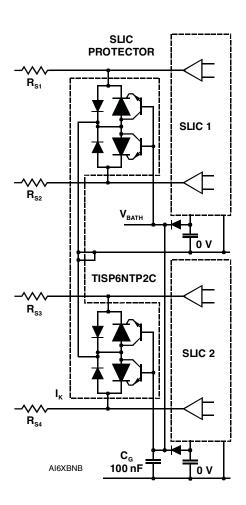

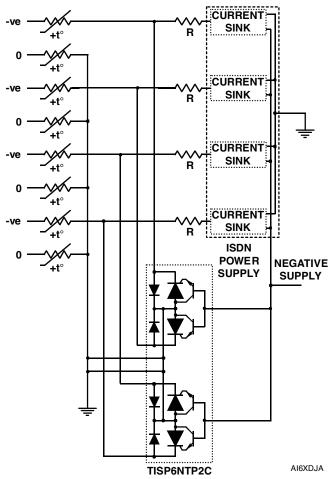

The generation of POTS lines at the customer premise normally uses a ringing SLIC. Although the lines are short, a central office ringing voltage level is often required for fax machine operation. High voltage SLICs are now available that can produce adequate ringing voltage (see table). The TISP6NTP2C has been designed to work with these SLICs which use battery voltages, V<sub>BATH</sub>, down to -150 V. Figure 2 shows a typical example with one TISP6NTP2C protecting two SLICs.

The table below shows some details of HV SLICs using multiple negative supply rails.

| Manufacturer              | INFINE   | ON‡   |              |         | LEGERI            | TY™‡ |                   |      | l l min |       |

|---------------------------|----------|-------|--------------|---------|-------------------|------|-------------------|------|---------|-------|

| SLIC Series               | SLIC     | -P‡   | ISLIC        | ISLIC™‡ |                   |      |                   |      | Unit    |       |

| SLIC#                     | PEB 4266 |       | 79F          | 79R241  |                   | R101 | 79F               | R100 |         |       |

| Data Sheet Issue          | 14/02    | /2001 | 01 -/08/2000 |         | -/07/2            | 2000 | -/07/2            | 000  |         |       |

| Short Circuit Current     | 11       | 0     | 15           | 50      | 15                | 50   | 15                | 50   | mA      |       |

| V <sub>BATH</sub> max.    | -15      | 55    | -104         |         | -104              |      | -104              |      | V       |       |

| V <sub>BATL</sub> max.    | -15      | 50    | -104         |         | V <sub>BATH</sub> |      | V <sub>BATH</sub> |      | V       |       |

| AC Ringing for:           | 8        | 5     | 45†          |         | 45† 50†           |      | 50† 55†           |      | 5†      | V rms |

| Crest Factor              | 1.       | 4     | 1.           | 1.4     |                   | 1.4  |                   | 1.25 |         |       |

| V <sub>BATH</sub>         | -7       | -70   |              | -90     |                   | 9    | -9                | 9    | V       |       |

| V <sub>BATR</sub>         | -15      | 50    | -36          |         | -2                | 4    | -2                | 4    | V       |       |

| R or T Overshoot < 250 ns |          |       | -15          | 15      | -20               | 12   | -20               | 12   | V       |       |

| Line Feed Resistance      | 20 +     | + 30  | 50           |         | 5                 | 0    | 5                 | 0    | Ω       |       |

<sup>†</sup> Assumes -20 V battery voltage during ringing.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

#### **ISDN Protection**

For voltage feed protection, the cathodes of an TISP6NTP2C thyristors are connected to the four conductors to be protected (see Figure 3). Each gate is connected to the appropriate negative voltage feed. The anode of the TISP6NTP2C is connected to the system common. Positive overvoltages are clipped to common by forward conduction of the TISP6NTP2C antiparallel diode. Negative overvoltages are initially clipped close to the negative supply by emitter follower action of the TISP6NTP2C buffer transistor. If sufficient clipping current flows, the TISP6NTP2C thyristor will regenerate and switch into a low voltage on-state condition. As the negative overvoltage subsides, the high holding current of the TISP6NTP2C prevents d.c. latchup.

#### **Voltage Stress Levels**

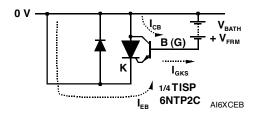

Figure 4 shows the protector electrodes. The package terminal designated gate, G, is the transistor base, B, electrode connection and so is marked as B (G). The following junctions are subject to voltage stress: Transistor EB and CB, SCR AK (off state) and the antiparallel diode (reverse blocking). This clause covers the necessary testing to ensure the junctions are good.

Testing transistor CB and EB: The maximum voltage stress level for the TISP6NTP2C is  $V_{BATH}$  with the addition of the short term antiparallel diode voltage overshoot,  $V_{FRM}$ . The current flowing out of the G terminal is measured at  $V_{BATH}$  plus  $V_{FRM}$ . The SCR K terminal is shorted to the common (0 V) for this test (see Figure 4). The measured current,  $I_{GKS}$ , is the sum of the junction currents  $I_{CB}$  and  $I_{EB}$ .

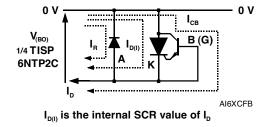

Testing transistor CB, SCR AK off state and diode reverse blocking: The highest AK voltage occurs during the overshoot period of the protector. To make sure that the SCR and diode blocking junctions do not break down during this period, a d.c. test for off-state current,  $I_D$ , can be applied at the overshoot voltage value. To avoid transistor CB current amplification by the transistor gain, the transistor base-emitter is shorted during this test (see Figure 5).

Summary: Two tests are need to verify the protector junctions. Maximum current values for  $I_{GKS}$  and  $I_D$  are required at the specified applied voltage conditions.

MARCH 2002 - REVISED JULY 2008

Specifications are subject to change without notice.

Customers should verify actual device performance in their specific applications.

<sup>‡</sup> Legerity, the Legerity logo and ISLIC are the trademarks of Legerity, Inc.

## TISP6NTP2C High Voltage Ringing SLIC Protector **BOURNS®**

#### **APPLICATIONS INFORMATION**

Figure 2. SLIC Protection

Figure 4. Transistor CB and EB Verification

Resistor "R" may be needed if sink has internal clamp diode

Figure 3. Protection of Four ISDN Power Feeds

Figure 5. Off-State Current Verification

## **Distributor of Bourns Inc.: Excellent Integrated System Limited**

Datasheet of TISP6NTP2CDR-S - SURGE PROT THYRIST 155VDUAL SLIC Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

## TISP6NTP2C High Voltage Ringing SLIC Protector

#### **MECHANICAL DATA**

**Device Symbolization Code**

Devices will be coded as below.

| Device         | Symbolization Code |

|----------------|--------------------|

| TISP6NTP2CDR-S | 6NTP2C             |

<sup>&</sup>quot;TISP" is a trademark of Bourns, Ltd., a Bourns Company, and is Registered in U.S. Patent and Trademark Office. "Bourns" is a registered trademark of Bourns, Inc. in the U.S. and other countries.