## Excellent Integrated System Limited

Stocking Distributor

Click to view price, real time Inventory, Delivery & Lifecycle Information:

[Maxim Integrated](#)

[MAX12557ETK+D](#)

For any questions, you can email us directly:

[sales@integrated-circuit.com](mailto:sales@integrated-circuit.com)

19-3544; Rev 0; 2/05

EVALUATION KIT

AVAILABLE

## Dual, 65Msp, 14-Bit, IF/Baseband ADC

### General Description

The MAX12557 is a dual 3.3V, 14-bit analog-to-digital converter (ADC) featuring fully differential wideband track-and-hold (T/H) inputs, driving internal quantizers. The MAX12557 is optimized for low power, small size, and high dynamic performance in intermediate frequency (IF) and baseband sampling applications. This dual ADC operates from a single 3.3V supply, consuming only 610mW while delivering a typical 72.5dB signal-to-noise ratio (SNR) performance at a 175MHz input frequency. The T/H input stages accept single-ended or differential inputs up to 400MHz. In addition to low operating power, the MAX12557 features a 166µW power-down mode to conserve power during idle periods.

A flexible reference structure allows the MAX12557 to use the internal 2.048V bandgap reference or accept an externally applied reference and allows the reference to be shared between the two ADCs. The reference structure allows the full-scale analog input range to be adjusted from  $\pm 0.35V$  to  $\pm 1.15V$ . The MAX12557 provides a common-mode reference to simplify design and reduce external component count in differential analog input circuits.

The MAX12557 supports either a single-ended or differential input clock. User-selectable divide-by-two (DIV2) and divide-by-four (DIV4) modes allow for design flexibility and help eliminate the negative effects of clock jitter. Wide variations in the clock duty cycle are compensated with the ADC's internal duty-cycle equalizer (DCE).

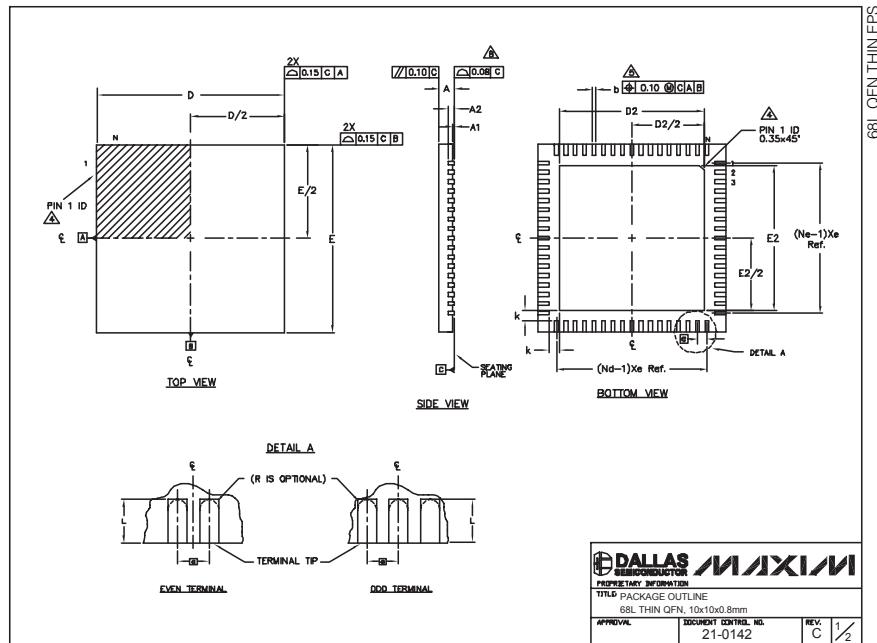

The MAX12557 features two parallel, 14-bit-wide, CMOS-compatible outputs. The digital output format is pin-selectable to be either two's complement or Gray code. A separate power-supply input for the digital outputs accepts a 1.7V to 3.6V voltage for flexible interfacing with various logic levels. The MAX12557 is available in a 10mm x 10mm x 0.8mm, 68-pin thin QFN package with exposed paddle (EP), and is specified for the extended (-40°C to +85°C) temperature range.

For a 12-bit, pin-compatible version of this ADC, refer to the MAX12527 data sheet.

### Applications

IF and Baseband Communication Receivers

Cellular, LMDS, Point-to-Point Microwave,

MMDS, HFC, WLAN

I/Q Receivers

Ultrasound and Medical Imaging

Portable Instrumentation

Digital Set-Top Boxes

Low-Power Data Acquisition

### Features

- ◆ Direct IF Sampling Up to 400MHz

- ◆ Excellent Dynamic Performance

- 74.1dB/72.5dB SNR at  $f_{IN} = 70\text{MHz}/175\text{MHz}$

- 83.4dBc/79.5dBc SFDR at  $f_{IN} = 70\text{MHz}/175\text{MHz}$

- ◆ 3.3V Low-Power Operation

- 637mW (Differential Clock Mode)

- 610mW (Single-Ended Clock Mode)

- ◆ Fully Differential or Single-Ended Analog Input

- ◆ Adjustable Differential Analog Input Voltage

- ◆ 750MHz Input Bandwidth

- ◆ Adjustable, Internal or External, Shared Reference

- ◆ Differential or Single-Ended Clock

- ◆ Accepts 25% to 75% Clock Duty Cycle

- ◆ User-Selectable DIV2 and DIV4 Clock Modes

- ◆ Power-Down Mode

- ◆ CMOS Outputs in Two's Complement or Gray Code

- ◆ Out-of-Range and Data-Valid Indicators

- ◆ Small, 68-Pin Thin QFN Package

- ◆ 12-Bit Compatible Version Available (MAX12527)

- ◆ Evaluation Kit Available (Order MAX12557 EV Kit)

MAX12557

### Ordering Information

| PART        | TEMP RANGE     | PIN-PACKAGE                              |

|-------------|----------------|------------------------------------------|

| MAX12557ETK | -40°C to +85°C | 68 Thin QFN-EP*<br>(10mm x 10mm x 0.8mm) |

\*EP = Exposed paddle.

### Selector Guide

| PART     | SAMPLING RATE (MspS) | RESOLUTION (Bits) |

|----------|----------------------|-------------------|

| MAX12557 | 65                   | 14                |

| MAX12527 | 65                   | 12                |

*Pin Configuration appears at end of data sheet.*

## **Dual, 65MspS, 14-Bit, IF/Baseband ADC**

### **ABSOLUTE MAXIMUM RATINGS**

$V_{DD}$  to GND ..... -0.3V to +3.6V

$OV_{DD}$  to GND ..... -0.3V to the lower of ( $V_{DD}$  + 0.3V) and +3.6V

INAP, INAN to GND ..... -0.3V to the lower of ( $V_{DD}$  + 0.3V) and +3.6V

INBP, INBN to GND ..... -0.3V to the lower of ( $V_{DD}$  + 0.3V) and +3.6V

CLKP, CLKN to GND ..... -0.3V to the lower of ( $V_{DD}$  + 0.3V) and +3.6V

REFIN, REfout to GND ..... -0.3V to the lower of ( $V_{DD}$  + 0.3V) and +3.6V

REFAP, REFAN, COMA to GND ..... -0.3V to the lower of ( $V_{DD}$  + 0.3V) and +3.6V

REFBP, REFBN, COMB to GND ..... -0.3V to the lower of ( $V_{DD}$  + 0.3V) and +3.6V

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

( $V_{DD}$  = 3.3V,  $OV_{DD}$  = 2.0V, GND = 0, REFIN = REfout (internal reference),  $C_L \approx 10pF$  at digital outputs,  $V_{IN} = -0.5dBFS$  (differential), DIFFCLK/SECLK =  $OV_{DD}$ , PD = GND, SHREF = GND, DIV2 = GND, DIV4 = GND,  $G/\bar{T} = GND$ ,  $f_{CLK} = 65MHz$ ,  $T_A = -40^\circ C$  to  $+85^\circ C$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .) (Note 1)

| PARAMETER                                            | SYMBOL       | CONDITIONS                                                   | MIN  | TYP          | MAX       | UNITS        |

|------------------------------------------------------|--------------|--------------------------------------------------------------|------|--------------|-----------|--------------|

| <b>DC ACCURACY</b>                                   |              |                                                              |      |              |           |              |

| Resolution                                           |              |                                                              | 14   |              |           | Bits         |

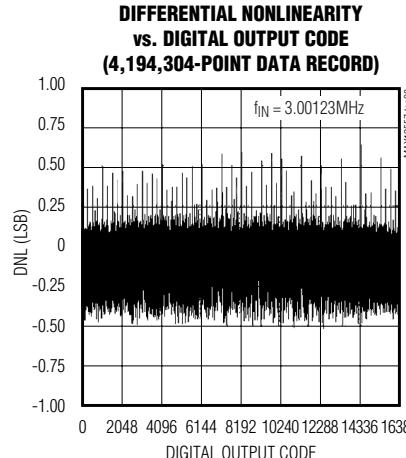

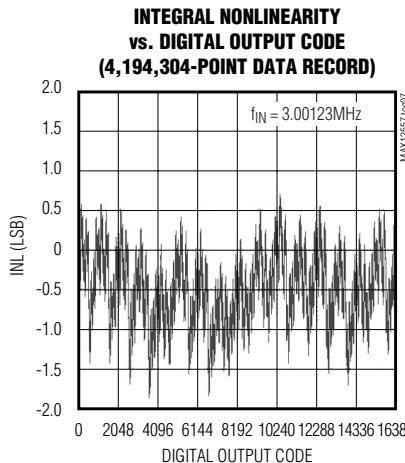

| Integral Nonlinearity                                | INL          | $f_{IN} = 3MHz$                                              |      | $\pm 2.1$    |           | LSB          |

| Differential Nonlinearity                            | DNL          | $f_{IN} = 3MHz$ , no missing codes over temperature (Note 2) | -1.0 | $\pm 0.6$    | +1.3      | LSB          |

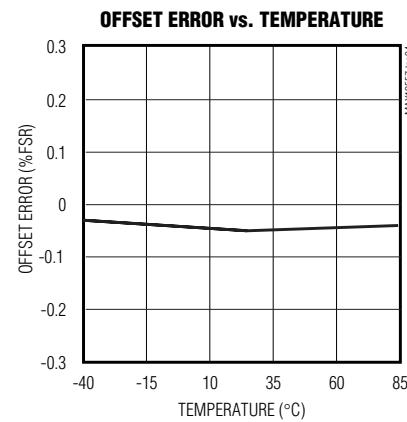

| Offset Error                                         |              |                                                              |      | $\pm 0.1$    | $\pm 0.9$ | %FSR         |

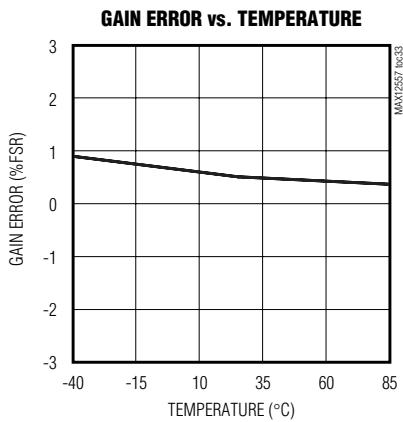

| Gain Error                                           |              |                                                              |      | $\pm 0.5$    | $\pm 5.0$ | %FSR         |

| <b>ANALOG INPUT (INAP, INAN, INBP, INBN)</b>         |              |                                                              |      |              |           |              |

| Differential Input Voltage Range                     | $V_{DIFF}$   | Differential or single-ended inputs                          |      | $\pm 1.024$  |           | V            |

| Common-Mode Input Voltage                            |              |                                                              |      | $V_{DD} / 2$ |           | V            |

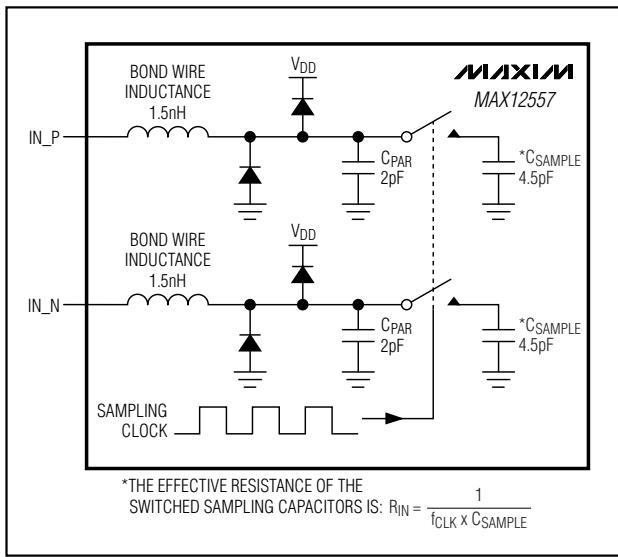

| Analog Input Resistance                              | $R_{IN}$     | Each input, Figure 3                                         | 3.4  |              |           | $k\Omega$    |

| Analog Input Capacitance                             | $C_{PAR}$    | Fixed capacitance to ground, each input, Figure 3            |      | 2            |           | $pF$         |

|                                                      | $C_{SAMPLE}$ | Switched capacitance, each input, Figure 3                   |      | 4.5          |           |              |

| <b>CONVERSION RATE</b>                               |              |                                                              |      |              |           |              |

| Maximum Clock Frequency                              | $f_{CLK}$    |                                                              | 65   |              |           | MHz          |

| Minimum Clock Frequency                              |              |                                                              |      | 5            |           | MHz          |

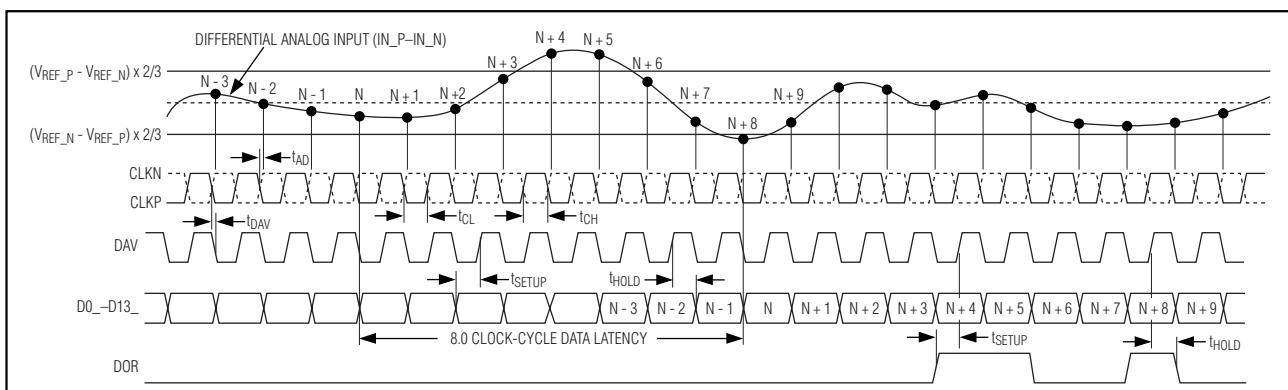

| Data Latency                                         |              | Figure 5                                                     |      | 8            |           | Clock Cycles |

| <b>DYNAMIC CHARACTERISTICS (differential inputs)</b> |              |                                                              |      |              |           |              |

| Small-Signal Noise Floor                             | SSNF         | Input at -35dBFS                                             | 74.5 | 76           |           | dBFS         |

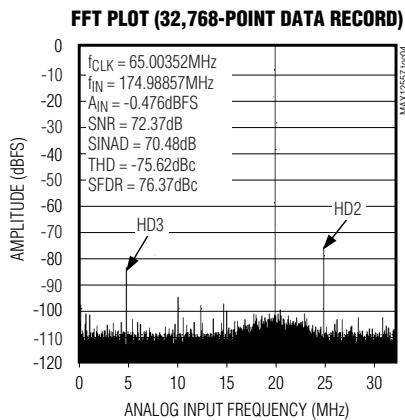

| Signal-to-Noise Ratio                                | SNR          | $f_{IN} = 3MHz$ at -0.5dBFS                                  | 72.5 | 75           |           | dB           |

|                                                      |              | $f_{IN} = 32.5MHz$ at -0.5dBFS                               |      | 74.5         |           |              |

|                                                      |              | $f_{IN} = 70MHz$ at -0.5dBFS                                 |      | 74.1         |           |              |

|                                                      |              | $f_{IN} = 175MHz$ at -0.5dBFS                                | 70.4 | 72.5         |           |              |

## **Dual, 65MspS, 14-Bit, IF/Baseband ADC**

### **ELECTRICAL CHARACTERISTICS (continued)**

( $V_{DD} = 3.3V$ ,  $OV_{DD} = 2.0V$ ,  $GND = 0$ ,  $REFIN = REfout$  (internal reference),  $C_L \approx 10pF$  at digital outputs,  $V_{IN} = -0.5dBFS$  (differential),  $DIFFCLK/SECLK = OV_{DD}$ ,  $PD = GND$ ,  $SHREF = GND$ ,  $DIV2 = GND$ ,  $DIV4 = GND$ ,  $G/\bar{T} = GND$ ,  $f_{CLK} = 65MHz$ ,  $T_A = -40^\circ C$  to  $+85^\circ C$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .) (Note 1)

| PARAMETER                                    | SYMBOL             | CONDITIONS                                                           | MIN  | TYP   | MAX   | UNITS  |

|----------------------------------------------|--------------------|----------------------------------------------------------------------|------|-------|-------|--------|

| Signal-to-Noise Plus Distortion              | SINAD              | $f_{IN} = 3MHz$ at $-0.5dBFS$ (Note 3)                               | 71.8 | 74.4  |       | dB     |

|                                              |                    | $f_{IN} = 32.5MHz$ at $-0.5dBFS$                                     |      | 73.10 |       |        |

|                                              |                    | $f_{IN} = 70MHz$ at $-0.5dBFS$                                       |      | 73.4  |       |        |

|                                              |                    | $f_{IN} = 175MHz$ at $-0.5dBFS$                                      |      | 71.5  |       |        |

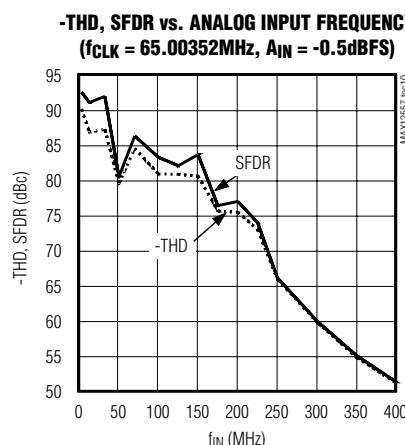

| Spurious-Free Dynamic Range                  | SFDR               | $f_{IN} = 3MHz$ at $-0.5dBFS$ (Note 3)                               | 75.5 | 86.6  |       | dBc    |

|                                              |                    | $f_{IN} = 32.5MHz$ at $-0.5dBFS$                                     |      | 82.8  |       |        |

|                                              |                    | $f_{IN} = 70MHz$ at $-0.5dBFS$                                       |      | 83.4  |       |        |

|                                              |                    | $f_{IN} = 175MHz$ at $-0.5dBFS$                                      |      | 79.5  |       |        |

| Total Harmonic Distortion                    | THD                | $f_{IN} = 3MHz$ at $-0.5dBFS$ (Note 3)                               |      | -84.5 | -74.5 | dBc    |

|                                              |                    | $f_{IN} = 32.5MHz$ at $-0.5dBFS$                                     |      | -80.7 |       |        |

|                                              |                    | $f_{IN} = 70MHz$ at $-0.5dBFS$                                       |      | -81.7 |       |        |

|                                              |                    | $f_{IN} = 175MHz$ at $-0.5dBFS$                                      |      | -78.3 |       |        |

| Second Harmonic                              | HD2                | $f_{IN} = 3MHz$ at $-0.5dBFS$                                        |      | -89.5 |       | dBc    |

|                                              |                    | $f_{IN} = 32.5MHz$ at $-0.5dBFS$                                     |      | -84.2 |       |        |

|                                              |                    | $f_{IN} = 70MHz$ at $-0.5dBFS$                                       |      | -84.7 |       |        |

|                                              |                    | $f_{IN} = 175MHz$ at $-0.5dBFS$                                      |      | -79.5 |       |        |

| Third Harmonic                               | HD3                | $f_{IN} = 3MHz$ at $-0.5dBFS$                                        |      | -93   |       | dBc    |

|                                              |                    | $f_{IN} = 32.5MHz$ at $-0.5dBFS$                                     |      | -85.5 |       |        |

|                                              |                    | $f_{IN} = 70MHz$ at $-0.5dBFS$                                       |      | -86.5 |       |        |

|                                              |                    | $f_{IN} = 175MHz$ at $-0.5dBFS$                                      |      | -87.2 |       |        |

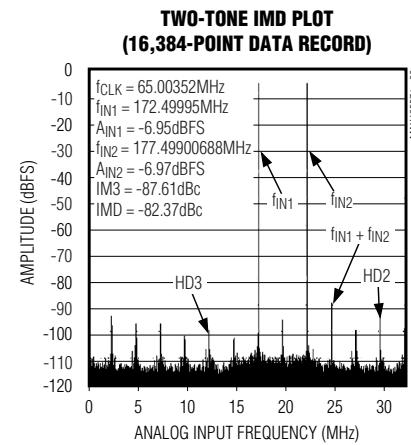

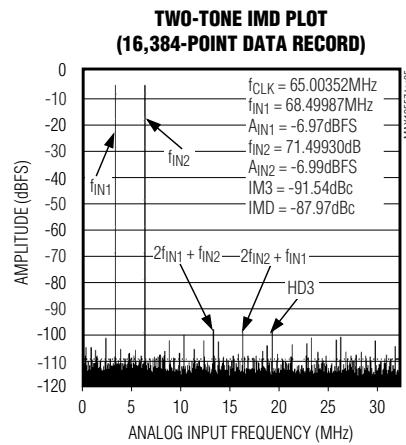

| Two-Tone Intermodulation Distortion (Note 2) | TTIMD              | $f_{IN1} = 68.5MHz$ at $-7dBFS$<br>$f_{IN2} = 71.5MHz$ at $-7dBFS$   |      | -88   |       | dBc    |

|                                              |                    | $f_{IN1} = 172.5MHz$ at $-7dBFS$<br>$f_{IN2} = 177.5MHz$ at $-7dBFS$ |      | -82.4 |       |        |

|                                              |                    | $f_{IN1} = 68.5MHz$ at $-7dBFS$<br>$f_{IN2} = 71.5MHz$ at $-7dBFS$   |      | -91.5 |       |        |

|                                              |                    | $f_{IN1} = 172.5MHz$ at $-7dBFS$<br>$f_{IN2} = 177.5MHz$ at $-7dBFS$ |      | -87.6 |       |        |

| Two-Tone Spurious-Free Dynamic Range         | SFDR <sub>TT</sub> | $f_{IN1} = 68.5MHz$ at $-7dBFS$<br>$f_{IN2} = 71.5MHz$ at $-7dBFS$   |      | 89    |       | dBc    |

|                                              |                    | $f_{IN1} = 172.5MHz$ at $-7dBFS$<br>$f_{IN2} = 177.5MHz$ at $-7dBFS$ |      | 82.4  |       |        |

| Full-Power Bandwidth                         | FPBW               | Input at $-0.2dBFS$ , $-3dB$ rolloff                                 | 750  |       |       | MHz    |

| Aperture Delay                               | t <sub>AD</sub>    | Figure 5                                                             | 1.2  |       |       | ns     |

| Aperture Jitter                              | t <sub>AJ</sub>    |                                                                      |      | <0.15 |       | psRMS  |

| Output Noise                                 | n <sub>OUT</sub>   | INAP = INAN = COMA<br>INBP = INBN = COMB                             |      | 1.02  |       | LSBRMS |

## **Dual, 65Msps, 14-Bit, IF/Baseband ADC**

### **ELECTRICAL CHARACTERISTICS (continued)**

( $V_{DD} = 3.3V$ ,  $OV_{DD} = 2.0V$ ,  $GND = 0$ ,  $REFIN = REfout$  (internal reference),  $C_L \approx 10pF$  at digital outputs,  $V_{IN} = -0.5dBFS$  (differential),  $DIFFCLK/\overline{SECLK} = OV_{DD}$ ,  $PD = GND$ ,  $SHREF = GND$ ,  $DIV2 = GND$ ,  $DIV4 = GND$ ,  $G/\overline{T} = GND$ ,  $f_{CLK} = 65MHz$ ,  $T_A = -40^\circ C$  to  $+85^\circ C$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .) (Note 1)

| PARAMETER                                                                                                                                                                                                                        | SYMBOL                     | CONDITIONS                                                               | MIN   | TYP        | MAX       | UNITS           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------|-------|------------|-----------|-----------------|

| Overdrive Recovery Time                                                                                                                                                                                                          |                            | $\pm 10\%$ beyond full scale                                             |       | 1          |           | Clock Cycle     |

| <b>INTERCHANNEL CHARACTERISTICS</b>                                                                                                                                                                                              |                            |                                                                          |       |            |           |                 |

| Crosstalk Rejection                                                                                                                                                                                                              |                            | $f_{INA} \text{ or } f_{INB} = 70MHz$ at $-0.5dBFS$                      | 90    |            |           | dB              |

|                                                                                                                                                                                                                                  |                            | $f_{INA} \text{ or } f_{INB} = 175MHz$ at $-0.5dBFS$                     | 85    |            |           |                 |

| Gain Matching                                                                                                                                                                                                                    |                            |                                                                          |       | $\pm 0.01$ | $\pm 0.1$ | dB              |

| Offset Matching                                                                                                                                                                                                                  |                            |                                                                          |       | $\pm 0.01$ |           | %FSR            |

| <b>INTERNAL REFERENCE (REFOUT)</b>                                                                                                                                                                                               |                            |                                                                          |       |            |           |                 |

| REFOUT Output Voltage                                                                                                                                                                                                            | $V_{REFOUT}$               |                                                                          | 2.000 | 2.048      | 2.080     | V               |

| REFOUT Load Regulation                                                                                                                                                                                                           |                            | $-1mA < I_{REFOUT} < +1mA$                                               | 35    |            |           | mV/mA           |

| REFOUT Temperature Coefficient                                                                                                                                                                                                   | $TC_{REF}$                 |                                                                          |       | $\pm 50$   |           | ppm/ $^\circ C$ |

| REFOUT Short-Circuit Current                                                                                                                                                                                                     |                            | Short to $V_{DD}$ —sinking                                               | 0.24  |            |           | mA              |

|                                                                                                                                                                                                                                  |                            | Short to $GND$ —sourcing                                                 | 2.1   |            |           |                 |

| <b>BUFFERED REFERENCE MODE (REFIN is driven by REFOUT or an external 2.048V single-ended reference source; <math>V_{REFAP}/V_{REFAN}/V_{COMA}</math> and <math>V_{REFBP}/V_{REFBN}/V_{COMB}</math> are generated internally)</b> |                            |                                                                          |       |            |           |                 |

| REFIN Input Voltage                                                                                                                                                                                                              | $V_{REFIN}$                |                                                                          | 2.048 |            |           | V               |

| REFIN Input Resistance                                                                                                                                                                                                           | $R_{REFIN}$                |                                                                          |       | $>50$      |           | $M\Omega$       |

| COM_ Output Voltage                                                                                                                                                                                                              | $V_{COMA}$<br>$V_{COMB}$   | $V_{DD} / 2$                                                             | 1.60  | 1.65       | 1.70      | V               |

| REF_P Output Voltage                                                                                                                                                                                                             | $V_{REFAP}$<br>$V_{REFBP}$ | $V_{DD} / 2 + (V_{REFIN} \times 3/8)$                                    |       | 2.418      |           | V               |

| REF_N Output Voltage                                                                                                                                                                                                             | $V_{REFAN}$<br>$V_{REFBN}$ | $V_{DD} / 2 - (V_{REFIN} \times 3/8)$                                    |       | 0.882      |           | V               |

| Differential Reference Voltage                                                                                                                                                                                                   | $V_{REFA}$<br>$V_{REFB}$   | $V_{REFA} = V_{REFAP} - V_{REFAN}$<br>$V_{REFB} = V_{REFBP} - V_{REFBN}$ | 1.460 | 1.536      | 1.580     | V               |

| Differential Reference Temperature Coefficient                                                                                                                                                                                   | $TC_{REF}$                 |                                                                          |       | $\pm 25$   |           | ppm/ $^\circ C$ |

| <b>UNBUFFERED EXTERNAL REFERENCE (REFIN = GND, <math>V_{REFAP}/V_{REFAN}/V_{COMA}</math> and <math>V_{REFBP}/V_{REFBN}/V_{COMB}</math> are applied externally, <math>V_{COMA} = V_{COMB} = V_{DD} / 2</math>)</b>                |                            |                                                                          |       |            |           |                 |

| REF_P Input Voltage                                                                                                                                                                                                              | $V_{REFAP}$<br>$V_{REFBP}$ | $V_{REF\_P} - V_{COM}$                                                   |       | +0.768     |           | V               |

| REF_N Input Voltage                                                                                                                                                                                                              | $V_{REFAN}$<br>$V_{REFBN}$ | $V_{REF\_N} - V_{COM}$                                                   |       | -0.768     |           | V               |

| COM_ Input Voltage                                                                                                                                                                                                               | $V_{COM}$                  | $V_{DD} / 2$                                                             |       | 1.65       |           | V               |

| Differential Reference Voltage                                                                                                                                                                                                   | $V_{REFA}$<br>$V_{REFB}$   | $V_{REF\_} = V_{REF\_P} - V_{REF\_N} = V_{REFIN} \times 3/4$             |       | 1.536      |           | V               |

## **Dual, 65MspS, 14-Bit, IF/Baseband ADC**

### **ELECTRICAL CHARACTERISTICS (continued)**

( $V_{DD} = 3.3V$ ,  $OV_{DD} = 2.0V$ ,  $GND = 0$ ,  $REFIN = REfout$  (internal reference),  $C_L \approx 10pF$  at digital outputs,  $V_{IN} = -0.5dBFS$  (differential),  $DIFFCLK/SECLK = OV_{DD}$ ,  $PD = GND$ ,  $SHREF = GND$ ,  $DIV2 = GND$ ,  $DIV4 = GND$ ,  $G/T = GND$ ,  $f_{CLK} = 65MHz$ ,  $T_A = -40^\circ C$  to  $+85^\circ C$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .) (Note 1)

| PARAMETER                                                    | SYMBOL                         | CONDITIONS                                                 | MIN                  | TYP                  | MAX     | UNITS            |

|--------------------------------------------------------------|--------------------------------|------------------------------------------------------------|----------------------|----------------------|---------|------------------|

| REF_P Sink Current                                           | $I_{REFAP}$<br>$I_{REFBP}$     | $V_{REF\_P} = 2.418V$                                      |                      | 1.2                  |         | mA               |

| REF_N Source Current                                         | $I_{REFAN}$<br>$I_{REFBN}$     | $V_{REF\_N} = 0.882V$                                      |                      | 0.85                 |         | mA               |

| COM_ Sink Current                                            | $I_{COMA}$<br>$I_{COMB}$       | $V_{COM\_} = 1.65V$                                        |                      | 0.85                 |         | mA               |

| REF_P, REF_N Capacitance                                     | $C_{REF\_P}$ ,<br>$C_{REF\_N}$ |                                                            |                      | 13                   |         | pF               |

| COM_ Capacitance                                             | $C_{COM\_}$                    |                                                            |                      | 6                    |         | pF               |

| <b>CLOCK INPUTS (CLKP, CLKN)</b>                             |                                |                                                            |                      |                      |         |                  |

| Single-Ended Input High Threshold                            | $V_{IH}$                       | $DIFFCLK/SECLK = GND$ , $CLKN = GND$                       | $0.8 \times V_{DD}$  |                      |         | V                |

| Single-Ended Input Low Threshold                             | $V_{IL}$                       | $DIFFCLK/SECLK = GND$ , $CLKN = GND$                       |                      | $0.2 \times V_{DD}$  |         | V                |

| Minimum Differential Clock Input Voltage Swing               |                                | $DIFFCLK/SECLK = OV_{DD}$                                  |                      | 0.2                  |         | V <sub>P-P</sub> |

| Differential Input Common-Mode Voltage                       |                                | $DIFFCLK/SECLK = OV_{DD}$                                  |                      | $V_{DD} / 2$         |         | V                |

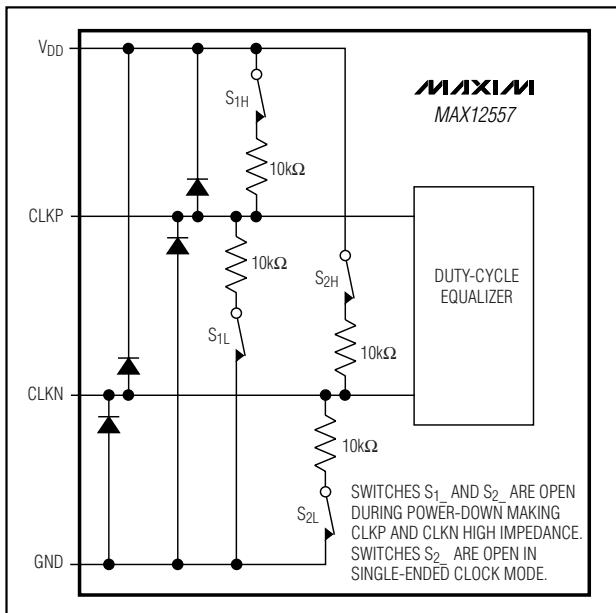

| CLK_ Input Resistance                                        | $R_{CLK}$                      | Each input, Figure 4                                       |                      | 5                    |         | k $\Omega$       |

| CLK_ Input Capacitance                                       | $C_{CLK}$                      |                                                            |                      | 2                    |         | pF               |

| <b>DIGITAL INPUTS (DIFFCLK/SECLK, G/T, PD, DIV2, DIV4)</b>   |                                |                                                            |                      |                      |         |                  |

| Input High Threshold                                         | $V_{IH}$                       |                                                            | $0.8 \times OV_{DD}$ |                      |         | V                |

| Input Low Threshold                                          | $V_{IL}$                       |                                                            |                      | $0.2 \times OV_{DD}$ |         | V                |

| Input Leakage Current                                        |                                | $OV_{DD}$ applied to input                                 |                      | $\pm 5$              | $\mu A$ |                  |

|                                                              |                                | Input connected to ground                                  |                      | $\pm 5$              |         |                  |

| Digital Input Capacitance                                    | $C_{DIN}$                      |                                                            |                      | 5                    |         | pF               |

| <b>DIGITAL OUTPUTS (D0A–D13A, D0B–D13B, DORA, DORB, DAV)</b> |                                |                                                            |                      |                      |         |                  |

| Output-Voltage Low                                           | $V_{OL}$                       | D0A–D13A, D0B–D13B, DORA, DORB:<br>$I_{SINK} = 200\mu A$   |                      | 0.2                  |         | V                |

|                                                              |                                | DAV: $I_{SINK} = 600\mu A$                                 |                      | 0.2                  |         |                  |

| Output-Voltage High                                          | $V_{OH}$                       | D0A–D13A, D0B–D13B, DORA, DORB:<br>$I_{SOURCE} = 200\mu A$ | $OV_{DD} - 0.2$      |                      |         | V                |

|                                                              |                                | DAV: $I_{SOURCE} = 600\mu A$                               | $OV_{DD} - 0.2$      |                      |         |                  |

| Tri-State Leakage Current<br>(Note 3)                        | $I_{LEAK}$                     | $OV_{DD}$ applied to input                                 |                      | $\pm 5$              | $\mu A$ |                  |

|                                                              |                                | Input connected to ground                                  |                      | $\pm 5$              |         |                  |

## **Dual, 65MspS, 14-Bit, IF/Baseband ADC**

### **ELECTRICAL CHARACTERISTICS (continued)**

( $V_{DD} = 3.3V$ ,  $OV_{DD} = 2.0V$ ,  $GND = 0$ ,  $REFIN = REfout$  (internal reference),  $C_L \approx 10pF$  at digital outputs,  $V_{IN} = -0.5dBFS$  (differential),  $DIFFCLK/\overline{SECLK} = OV_{DD}$ ,  $PD = GND$ ,  $SHREF = GND$ ,  $DIV2 = GND$ ,  $DIV4 = GND$ ,  $G/\overline{T} = GND$ ,  $f_{CLK} = 65MHz$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                                             | SYMBOL     | CONDITIONS                                                                                                         | MIN  | TYP   | MAX      | UNITS |

|-----------------------------------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------|------|-------|----------|-------|

| D0A-D13A, D0B-D13B and D0B-D13B Tri-State Output Capacitance (Note 3) | $C_{OUT}$  |                                                                                                                    |      | 3     |          | pF    |

| DAV Tri-State Output Capacitance (Note 3)                             | $C_{DAV}$  |                                                                                                                    |      | 6     |          | pF    |

| <b>POWER REQUIREMENTS</b>                                             |            |                                                                                                                    |      |       |          |       |

| Analog Supply Voltage                                                 | $V_{DD}$   |                                                                                                                    | 3.15 | 3.30  | 3.60     | V     |

| Digital Output Supply Voltage                                         | $OV_{DD}$  |                                                                                                                    | 1.70 | 2.0   | $V_{DD}$ | V     |

| Analog Supply Current                                                 | $I_{VDD}$  | Normal operating mode<br>$f_{IN} = 175MHz$ at -0.5dBFS, single-ended clock ( $DIFFCLK/\overline{SECLK} = GND$ )    |      | 185   |          | mA    |

|                                                                       |            | Normal operating mode<br>$f_{IN} = 175MHz$ at -0.5dBFS differential clock ( $DIFFCLK/\overline{SECLK} = OV_{DD}$ ) |      | 193   | 210      |       |

|                                                                       |            | Power-down mode ( $PD = OV_{DD}$ ) clock idle                                                                      |      | 0.05  |          |       |

| Analog Power Dissipation                                              | $P_{VDD}$  | Normal operating mode<br>$f_{IN} = 175MHz$ at -0.5dBFS single-ended clock ( $DIFFCLK/\overline{SECLK} = GND$ )     |      | 610   |          | mW    |

|                                                                       |            | Normal operating mode<br>$f_{IN} = 175MHz$ at -0.5dBFS differential clock ( $DIFFCLK/\overline{SECLK} = OV_{DD}$ ) |      | 637   | 693      |       |

|                                                                       |            | Power-down mode ( $PD = OV_{DD}$ ) clock idle                                                                      |      | 0.165 |          |       |

| Digital Output Supply Current                                         | $I_{OVDD}$ | Normal operating mode<br>$f_{IN} = 175MHz$ at -0.5dBFS                                                             |      | 21.3  |          | mA    |

|                                                                       |            | Power-down mode ( $PD = OV_{DD}$ ) clock idle                                                                      |      | 0.001 |          |       |

## **Dual, 65MspS, 14-Bit, IF/Baseband ADC**

### **ELECTRICAL CHARACTERISTICS (continued)**

( $V_{DD} = 3.3V$ ,  $OV_{DD} = 2.0V$ ,  $GND = 0$ ,  $REFIN = REfout$  (internal reference),  $C_L \approx 10pF$  at digital outputs,  $V_{IN} = -0.5dBFS$  (differential),  $DIFFCLK/SECLK = OV_{DD}$ ,  $PD = GND$ ,  $SHREF = GND$ ,  $DIV2 = GND$ ,  $DIV4 = GND$ ,  $G/T = GND$ ,  $f_{CLK} = 65MHz$ ,  $T_A = -40^\circ C$  to  $+85^\circ C$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .) (Note 1)

| PARAMETER                                 | SYMBOL      | CONDITIONS           | MIN | TYP | MAX | UNITS |

|-------------------------------------------|-------------|----------------------|-----|-----|-----|-------|

| <b>TIMING CHARACTERISTICS (Figure 5)</b>  |             |                      |     |     |     |       |

| Clock Pulse-Width High                    | $t_{CH}$    |                      |     | 7.7 |     | ns    |

| Clock Pulse-Width Low                     | $t_{CL}$    |                      |     | 7.7 |     | ns    |

| Data-Valid Delay                          | $t_{DAV}$   |                      |     | 5.4 |     | ns    |

| Data Setup Time Before Rising Edge of DAV | $t_{SETUP}$ | (Note 6)             |     | 7.0 |     | ns    |

| Data Hold Time After Rising Edge of DAV   | $t_{HOLD}$  | (Note 6)             |     | 7.0 |     | ns    |

| Wake-Up Time from Power-Down              | $t_{WAKE}$  | $V_{REFIN} = 2.048V$ |     | 10  |     | ms    |

**Note 1:** Specifications  $\geq +25^\circ C$  guaranteed by production test,  $< +25^\circ C$  guaranteed by design and characterization.

**Note 2:** Guaranteed by design and characterization. Device tested for performance during product test.

**Note 3:** Specification guaranteed by production test for  $\geq +25^\circ C$ .

**Note 4:** Two-tone intermodulation distortion measured with respect to a single-carrier amplitude, and not the peak-to-average input power of both input tones.

**Note 5:** During power-down, D0A–D13A, D0B–D13B, DORA, DORB, and DAV are high impedance.

**Note 6:** Guaranteed by design and characterization.

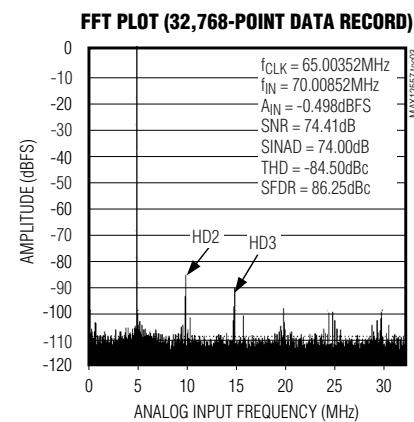

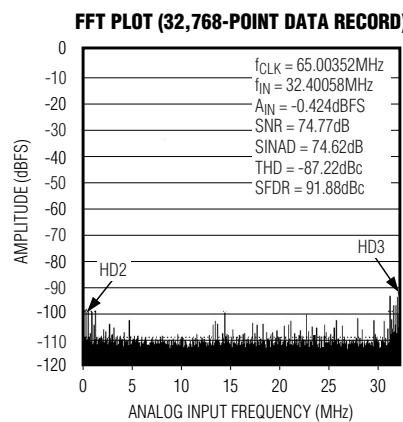

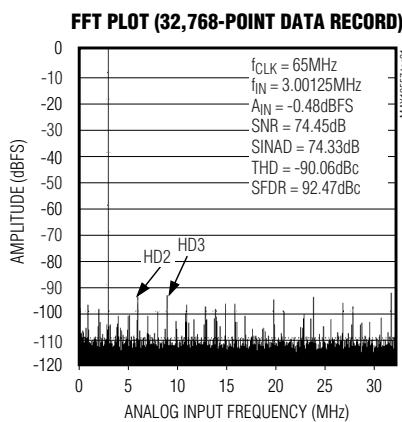

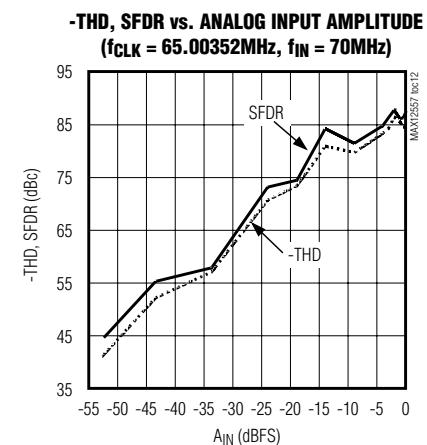

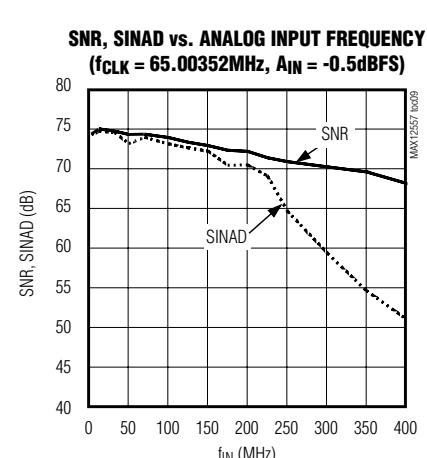

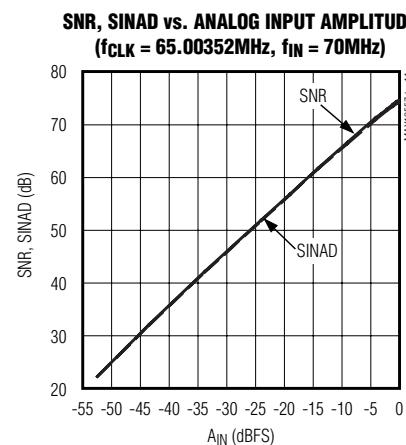

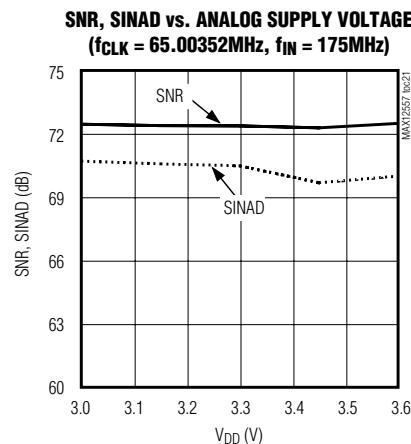

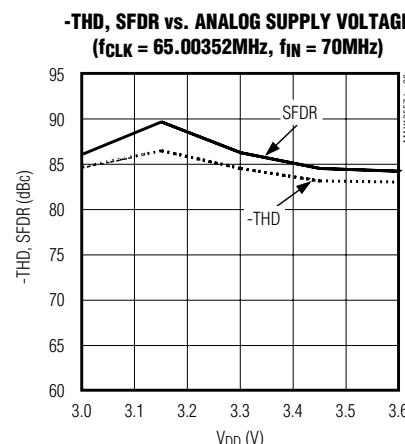

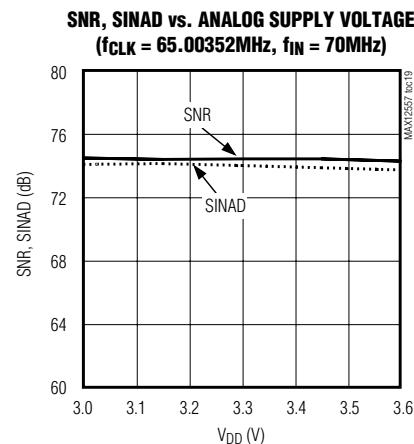

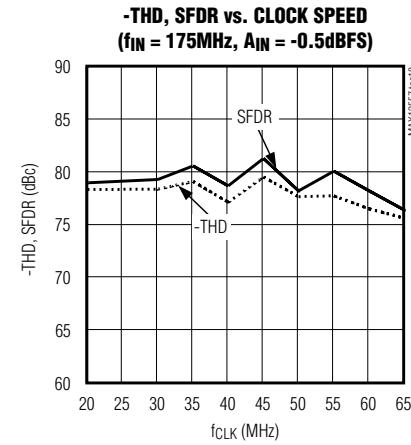

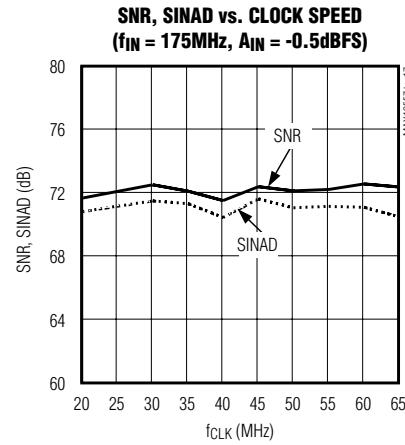

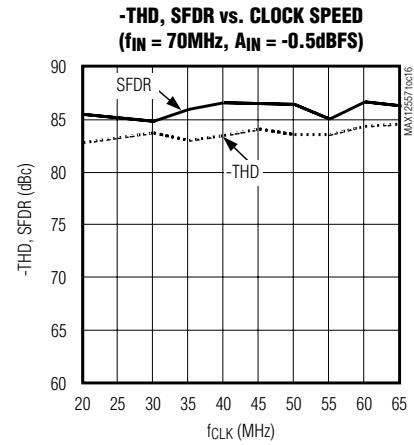

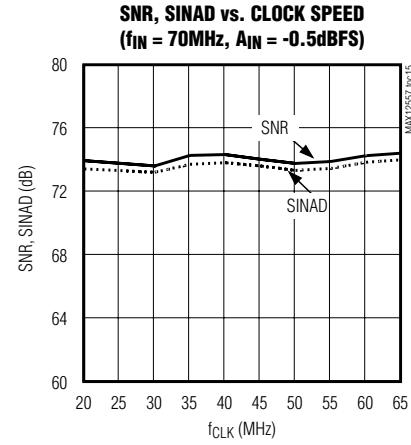

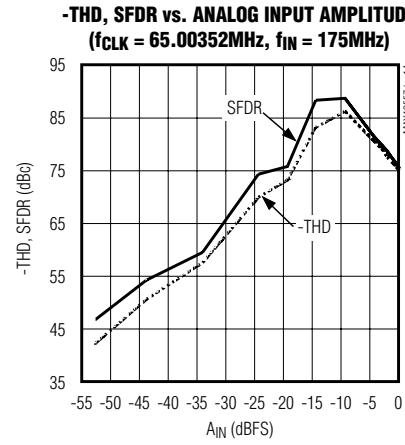

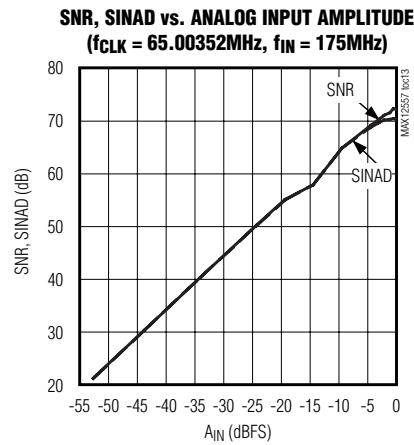

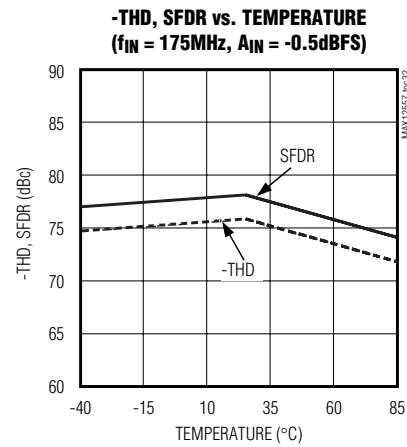

### **Typical Operating Characteristics**

( $V_{DD} = 3.3V$ ,  $OV_{DD} = 2.0V$ ,  $GND = 0$ ,  $REFIN = REfout$  (internal reference mode),  $C_L \approx 5pF$  at digital outputs,  $V_{IN} = -0.5dBFS$ ,  $DIFFCLK/SECLK = OV_{DD}$ ,  $PD = GND$ ,  $G/T = GND$ ,  $f_{CLK} = 65MHz$  (50% duty cycle),  $T_A = +25^\circ C$ , unless otherwise noted.)

## Dual, 65Msps, 14-Bit, IF/Baseband ADC

### Typical Operating Characteristics (continued)

( $V_{DD} = 3.3V$ ,  $OV_{DD} = 2.0V$ ,  $GND = 0$ ,  $REFIN = REFOUT$  (internal reference mode),  $C_L \approx 5pF$  at digital outputs,  $V_{IN} = -0.5dBFS$ ,  $DIFFCLK/SECLK = OV_{DD}$ ,  $PD = GND$ ,  $G/\bar{T} = GND$ ,  $f_{CLK} = 65MHz$  (50% duty cycle),  $T_A = +25^\circ C$ , unless otherwise noted.)

## Dual, 65Mps, 14-Bit, IF/Baseband ADC

**MAX12557**

### Typical Operating Characteristics (continued)

( $V_{DD} = 3.3V$ ,  $OV_{DD} = 2.0V$ ,  $GND = 0$ ,  $REFIN = REFOUT$  (internal reference mode),  $C_L \approx 5pF$  at digital outputs,  $V_{IN} = -0.5dBFS$ ,  $DIFFCLK/SECLK = OV_{DD}$ ,  $PD = GND$ ,  $G/\bar{T} = GND$ ,  $f_{CLK} = 65MHz$  (50% duty cycle),  $T_A = +25^\circ C$ , unless otherwise noted.)

## Dual, 65Msps, 14-Bit, IF/Baseband ADC

### Typical Operating Characteristics (continued)

( $V_{DD} = 3.3V$ ,  $OV_{DD} = 2.0V$ ,  $GND = 0$ ,  $REFIN = REFOUT$  (internal reference mode),  $C_L \approx 5pF$  at digital outputs,  $V_{IN} = -0.5dBFS$ ,  $DIFFCLK/SECLK = OV_{DD}$ ,  $PD = GND$ ,  $G/\bar{T} = GND$ ,  $f_{CLK} = 65MHz$  (50% duty cycle),  $T_A = +25^\circ C$ , unless otherwise noted.)

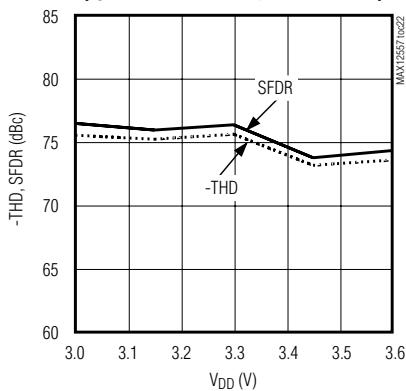

**-THD, SFDR vs. ANALOG SUPPLY VOLTAGE**

( $f_{CLK} = 65.00352MHz$ ,  $f_{IN} = 175MHz$ )

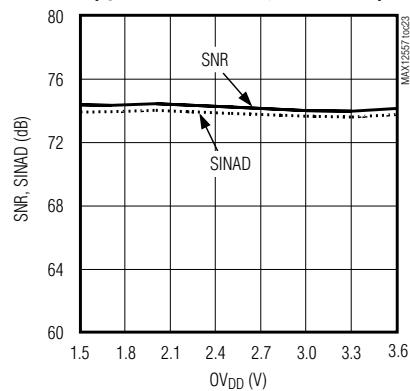

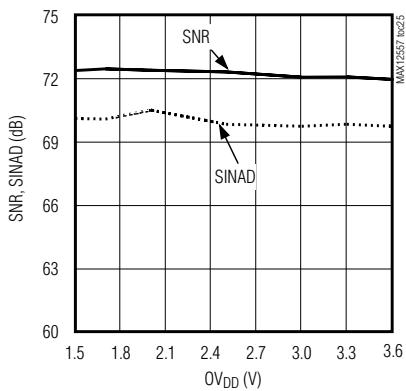

**SNR, SINAD vs. DIGITAL SUPPLY VOLTAGE**

( $f_{CLK} = 65.00352MHz$ ,  $f_{IN} = 70MHz$ )

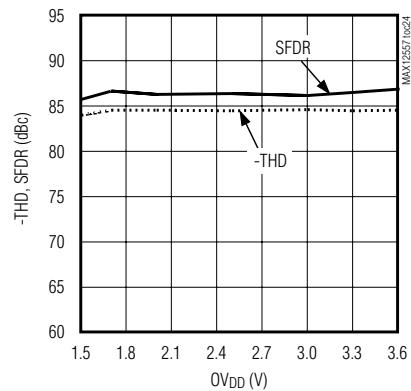

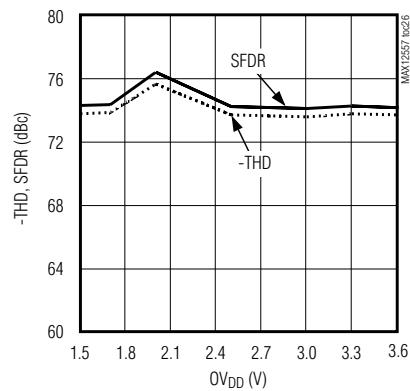

**-THD, SFDR vs. DIGITAL SUPPLY VOLTAGE**

( $f_{CLK} = 65.00352MHz$ ,  $f_{IN} = 70MHz$ )

**SNR, SINAD vs. DIGITAL SUPPLY VOLTAGE**

( $f_{CLK} = 65.00352MHz$ ,  $f_{IN} = 175MHz$ )

**-THD, SFDR vs. DIGITAL SUPPLY VOLTAGE**

( $f_{CLK} = 65.00352MHz$ ,  $f_{IN} = 175MHz$ )

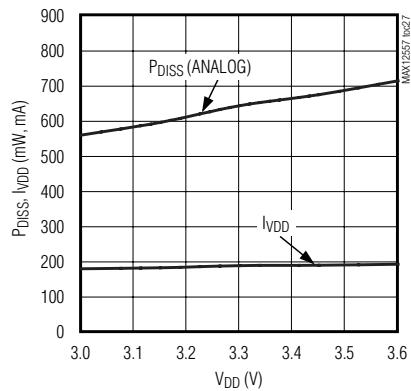

**$P_{DISS}$ ,  $I_{VDD}$  (DIGITAL) vs. ANALOG SUPPLY VOLTAGE**

( $f_{CLK} = 65.00352MHz$ ,  $f_{IN} = 175MHz$ )

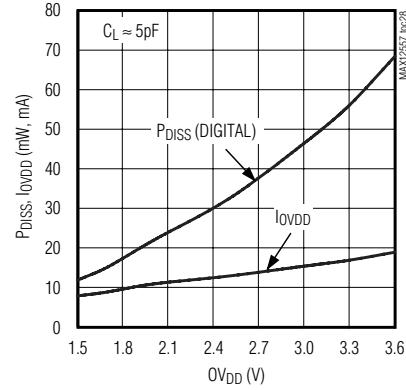

**$P_{DISS}$ ,  $I_{VDD}$  (DIGITAL)**

vs. DIGITAL SUPPLY VOLTAGE

( $f_{CLK} = 65.00352MHz$ ,  $f_{IN} = 175MHz$ )

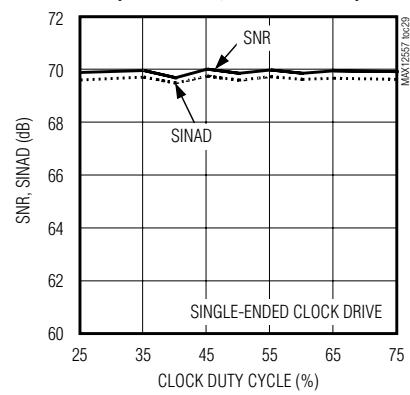

**SNR, SINAD vs. CLOCK DUTY CYCLE**

( $f_{IN} = 70MHz$ ,  $A_{IN} = -0.5dBFS$ )

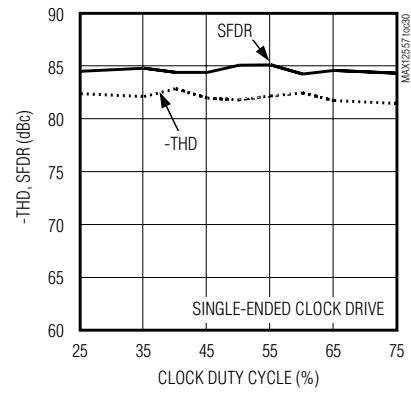

**-THD, SFDR vs. CLOCK DUTY CYCLE**

( $f_{IN} = 70MHz$ ,  $A_{IN} = -0.5dBFS$ )

## **Dual, 65Mps, 14-Bit, IF/Baseband ADC**

**MAX12557**

### **Typical Operating Characteristics (continued)**

( $V_{DD} = 3.3V$ ,  $OV_{DD} = 2.0V$ ,  $GND = 0$ ,  $REFIN = REFOUT$  (internal reference mode),  $C_L \approx 5pF$  at digital outputs,  $V_{IN} = -0.5dBFS$ ,  $DIFFCLK/SECLK = OV_{DD}$ ,  $PD = GND$ ,  $G/\bar{T} = GND$ ,  $f_{CLK} = 65MHz$  (50% duty cycle),  $T_A = +25^\circ C$ , unless otherwise noted.)

## **Dual, 65Msp, 14-Bit, IF/Baseband ADC**

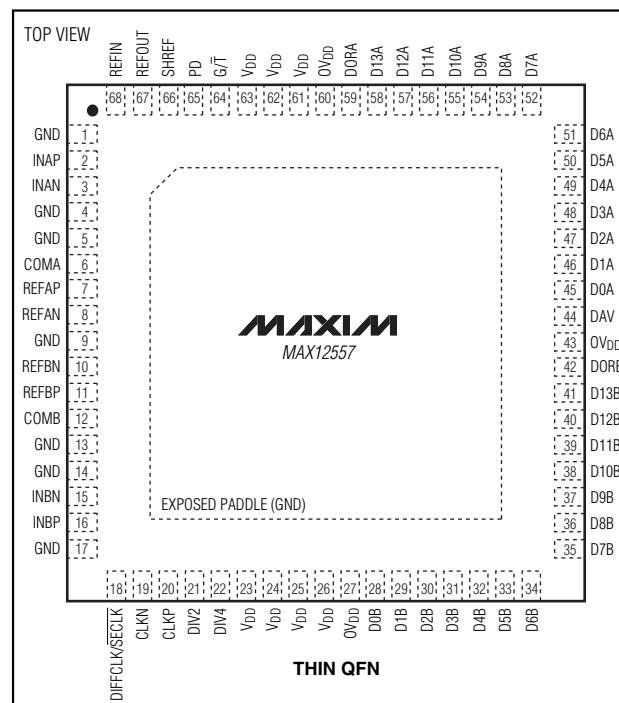

### **Pin Description**

| PIN                       | NAME              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 4, 5, 9,<br>13, 14, 17 | GND               | Converter Ground. Connect all ground pins and the exposed paddle (EP) together.                                                                                                                                                                                                                                                                                               |

| 2                         | INAP              | Channel A Positive Analog Input                                                                                                                                                                                                                                                                                                                                               |

| 3                         | INAN              | Channel A Negative Analog Input                                                                                                                                                                                                                                                                                                                                               |

| 6                         | COMA              | Channel A Common-Mode Voltage I/O. Bypass COMA to GND with a 0.1 $\mu$ F capacitor.                                                                                                                                                                                                                                                                                           |

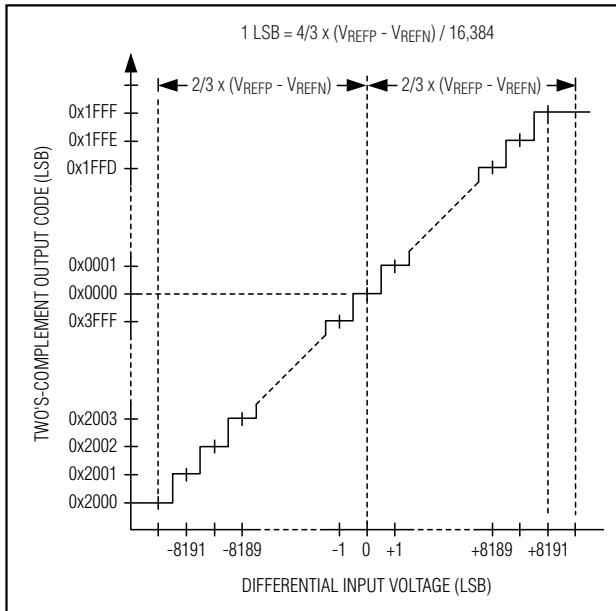

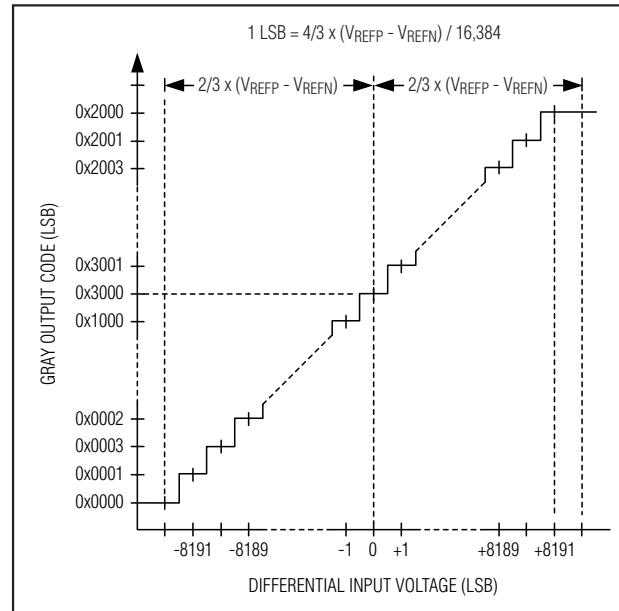

| 7                         | REFAP             | Channel A Positive Reference I/O. Channel A conversion range is $\pm 2/3 \times (V_{REFAP} - V_{REFAN})$ . Bypass REFAP with a 0.1 $\mu$ F capacitor to GND. Connect a 10 $\mu$ F and a 1 $\mu$ F bypass capacitor between REFAP and REFAN. <b>Place the 1<math>\mu</math>F REFAP-to-REFAN capacitor as close to the device as possible on the same side of the PC board.</b> |

| 8                         | REFAN             | Channel A Negative Reference I/O. Channel A conversion range is $\pm 2/3 \times (V_{REFAP} - V_{REFAN})$ . Bypass REFAN with a 0.1 $\mu$ F capacitor to GND. Connect a 10 $\mu$ F and a 1 $\mu$ F bypass capacitor between REFAP and REFAN. <b>Place the 1<math>\mu</math>F REFAP-to-REFAN capacitor as close to the device as possible on the same side of the PC board.</b> |

| 10                        | REFBN             | Channel B Negative Reference I/O. Channel B conversion range is $\pm 2/3 \times (V_{REFBP} - V_{REFBN})$ . Bypass REFBN with a 0.1 $\mu$ F capacitor to GND. Connect a 10 $\mu$ F and a 1 $\mu$ F bypass capacitor between REFBP and REFBN. <b>Place the 1<math>\mu</math>F REFBP-to-REFBN capacitor as close to the device as possible on the same side of the PC board.</b> |

| 11                        | REFBP             | Channel B Positive Reference I/O. Channel B conversion range is $\pm 2/3 \times (V_{REFBP} - V_{REFBN})$ . Bypass REFBP with a 0.1 $\mu$ F capacitor to GND. Connect a 10 $\mu$ F and a 1 $\mu$ F bypass capacitor between REFBP and REFBN. <b>Place the 1<math>\mu</math>F REFBP-to-REFBN capacitor as close to the device as possible on the same side of the PC board.</b> |

| 12                        | COMB              | Channel A Common-Mode Voltage I/O. Bypass COMB to GND with a 0.1 $\mu$ F capacitor.                                                                                                                                                                                                                                                                                           |

| 15                        | INBN              | Channel B Negative Analog Input                                                                                                                                                                                                                                                                                                                                               |

| 16                        | INBP              | Channel B Positive Analog Input                                                                                                                                                                                                                                                                                                                                               |

| 18                        | DIFFCLK/<br>SECLK | Differential/Single-Ended Input Clock Drive. This input selects between single-ended or differential clock input drives.<br>DIFFCLK/SECLK = GND: Selects single-ended clock input drive.<br>DIFFCLK/SECLK = OV <sub>DD</sub> : Selects differential clock input drive.                                                                                                        |

| 19                        | CLKN              | Negative Clock Input. In differential clock input mode (DIFFCLK/SECLK = OV <sub>DD</sub> ), connect a differential clock signal between CLKP and CLKN. In single-ended clock mode (DIFFCLK/SECLK = GND), apply the clock signal to CLKP and connect CLKN to GND.                                                                                                              |

| 20                        | CLKP              | Positive Clock Input. In differential clock input mode (DIFFCLK/SECLK = OV <sub>DD</sub> ), connect a differential clock signal between CLKP and CLKN. In single-ended clock mode (DIFFCLK/SECLK = GND), apply the single-ended clock signal to CLKP and connect CLKN to GND.                                                                                                 |

| 21                        | DIV2              | Divide-by-Two Clock-Divider Digital Control Input. See Table 2 for details.                                                                                                                                                                                                                                                                                                   |

| 22                        | DIV4              | Divide-by-Four Clock-Divider Digital Control Input. See Table 2 for details.                                                                                                                                                                                                                                                                                                  |

| 23–26, 61,<br>62, 63      | V <sub>DD</sub>   | Analog Power Input. Connect V <sub>DD</sub> to a 3.15V to 3.60V power supply. Bypass V <sub>DD</sub> to GND with a parallel capacitor combination of $\geq 10\mu$ F and 0.1 $\mu$ F. Connect all V <sub>DD</sub> pins to the same potential.                                                                                                                                  |

| 27, 43, 60                | OV <sub>DD</sub>  | Output-Driver Power Input. Connect OV <sub>DD</sub> to a 1.7V to V <sub>DD</sub> power supply. Bypass OV <sub>DD</sub> to GND with a parallel capacitor combination of $\geq 10\mu$ F and 0.1 $\mu$ F.                                                                                                                                                                        |

## **Dual, 65MspS, 14-Bit, IF/Baseband ADC**

### **Pin Description (continued)**

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                          |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28  | D0B  | Channel B CMOS Digital Output, Bit 0 (LSB)                                                                                                                                                                                                        |

| 29  | D1B  | Channel B CMOS Digital Output, Bit 1                                                                                                                                                                                                              |

| 30  | D2B  | Channel B CMOS Digital Output, Bit 2                                                                                                                                                                                                              |

| 31  | D3B  | Channel B CMOS Digital Output, Bit 3                                                                                                                                                                                                              |

| 32  | D4B  | Channel B CMOS Digital Output, Bit 4                                                                                                                                                                                                              |

| 33  | D5B  | Channel B CMOS Digital Output, Bit 5                                                                                                                                                                                                              |

| 34  | D6B  | Channel B CMOS Digital Output, Bit 6                                                                                                                                                                                                              |

| 35  | D7B  | Channel B CMOS Digital Output, Bit 7                                                                                                                                                                                                              |

| 36  | D8B  | Channel B CMOS Digital Output, Bit 8                                                                                                                                                                                                              |

| 37  | D9B  | Channel B CMOS Digital Output, Bit 9                                                                                                                                                                                                              |

| 38  | D10B | Channel B CMOS Digital Output, Bit 10                                                                                                                                                                                                             |

| 39  | D11B | Channel B CMOS Digital Output, Bit 11                                                                                                                                                                                                             |

| 40  | D12B | Channel B CMOS Digital Output, Bit 12                                                                                                                                                                                                             |

| 41  | D13B | Channel B CMOS Digital Output, Bit 13 (MSB)                                                                                                                                                                                                       |

| 42  | DORB | Channel B Data Out-of-Range Indicator. The DORB digital output indicates when the channel B analog input voltage is out of range.<br>DORB = 1: Digital outputs exceed full-scale range.<br>DORB = 0: Digital outputs are within full-scale range. |

| 44  | DAV  | Data-Valid Digital Output. The rising edge of DAV indicates that data is present on the digital outputs. The MAX12557 evaluation kit utilizes DAV to latch data into any external back-end digital logic.                                         |

| 45  | D0A  | Channel A CMOS Digital Output, Bit 0 (LSB)                                                                                                                                                                                                        |

| 46  | D1A  | Channel A CMOS Digital Output, Bit 1                                                                                                                                                                                                              |

| 47  | D2A  | Channel A CMOS Digital Output, Bit 2                                                                                                                                                                                                              |

| 48  | D3A  | Channel A CMOS Digital Output, Bit 3                                                                                                                                                                                                              |

| 49  | D4A  | Channel A CMOS Digital Output, Bit 4                                                                                                                                                                                                              |

| 50  | D5A  | Channel A CMOS Digital Output, Bit 5                                                                                                                                                                                                              |

| 51  | D6A  | Channel A CMOS Digital Output, Bit 6                                                                                                                                                                                                              |

| 52  | D7A  | Channel A CMOS Digital Output, Bit 7                                                                                                                                                                                                              |

| 53  | D8A  | Channel A CMOS Digital Output, Bit 8                                                                                                                                                                                                              |

| 54  | D9A  | Channel A CMOS Digital Output, Bit 9                                                                                                                                                                                                              |

| 55  | D10A | Channel A CMOS Digital Output, Bit 10                                                                                                                                                                                                             |

| 56  | D11A | Channel A CMOS Digital Output, Bit 11                                                                                                                                                                                                             |

| 57  | D12A | Channel A CMOS Digital Output, Bit 12                                                                                                                                                                                                             |

| 58  | D13A | Channel A CMOS Digital Output, Bit 13 (MSB)                                                                                                                                                                                                       |

| 59  | DORA | Channel A Data Out-of-Range Indicator. The DORA digital output indicates when the channel A analog input voltage is out of range.<br>DORA = 1: Digital outputs exceed full-scale range.<br>DORA = 0: Digital outputs are within full-scale range. |

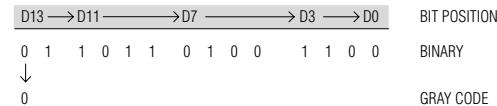

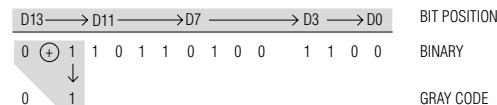

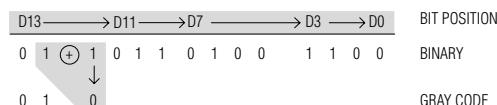

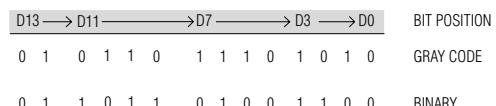

| 64  | G/T  | Output Format Select Digital Input.<br>G/T = GND: Two's-complement output format selected.<br>G/T = OVDD: Gray-code output format selected.                                                                                                       |

**MAX12557**

## Dual, 65Msps, 14-Bit, IF/Baseband ADC

### Pin Description (continued)

| PIN | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 65  | PD     | Power-Down Digital Input.<br>PD = GND: ADCs are fully operational.<br>PD = OV <sub>DD</sub> : ADCs are powered down.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 66  | SHREF  | Shared Reference Digital Input.<br>SHREF = V <sub>DD</sub> : Shared reference enabled.<br>SHREF = GND: Shared reference disabled.<br>When sharing the reference, externally connect REFP and REFBP together to ensure that V <sub>REFAP</sub> = V <sub>REFBP</sub> . Similarly, when sharing the reference, externally connect REFPN to REFBN together to ensure that V <sub>REFAN</sub> = V <sub>REFBN</sub> .                                                                                                                                                                                                         |

| 67  | REFOUT | Internal Reference Voltage Output. The REFOUT output voltage is 2.048V and REFOUT can deliver 1mA.<br>For internal reference operation, connect REFOUT directly to REFIN or use a resistive divider from REFOUT to set the voltage at REFIN. <b>Bypass REFOUT to GND with a <math>\geq 0.1\mu\text{F}</math> capacitor.</b><br>For external reference operation, REFOUT is not required and must be bypassed to GND with a $\geq 0.1\mu\text{F}$ capacitor.                                                                                                                                                             |

| 68  | REFIN  | Single-Ended Reference Analog Input.<br>For internal reference and buffered external reference operation, apply a 0.7V to 2.3V DC reference voltage to REFIN. <b>Bypass REFIN to GND with a <math>4.7\mu\text{F}</math> capacitor.</b> Within its specified operating voltage, REFIN has a $>50\text{M}\Omega$ input impedance, and the differential reference voltage (V <sub>REF_P</sub> - V <sub>REF_N</sub> ) is generated from REFIN. For unbuffered external reference operation, connect REFIN to GND. In this mode, REFP, REFN, and COM_ are high-impedance inputs that accept the external reference voltages. |

| —   | EP     | Exposed Paddle. EP is internally connected to GND. Externally connect EP to GND to achieve specified dynamic performance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

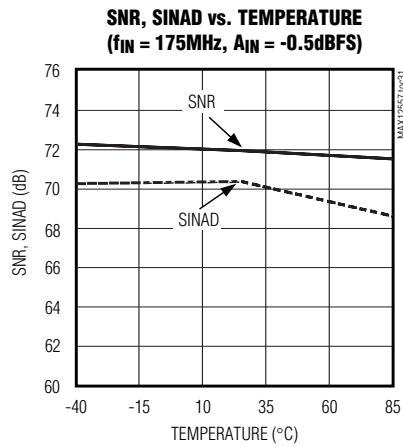

Figure 1. Pipeline Architecture—Stage Blocks

### Detailed Description

The MAX12557 uses a 10-stage, fully differential, pipelined architecture (Figure 1) that allows for high-speed conversion while minimizing power consumption. Samples taken at the inputs move progressively through the pipeline stages every half clock cycle. From input to output the total latency is 8 clock cycles.

Each pipeline converter stage converts its input voltage to a digital output code. At every stage, except the last, the error between the input voltage and the digital output code is multiplied and passed along to the next pipeline stage. Digital error correction compensates for ADC comparator offsets in each pipeline stage and ensures no missing codes. Figure 2 shows the MAX12557 functional diagram.

## **Dual, 65MspS, 14-Bit, IF/Baseband ADC**

**MAX12557**

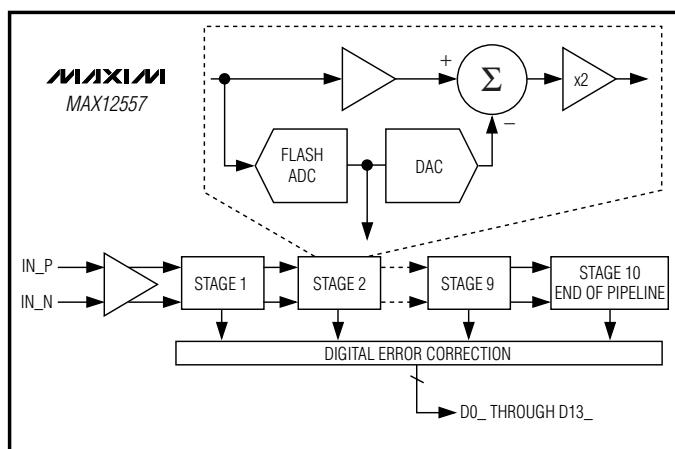

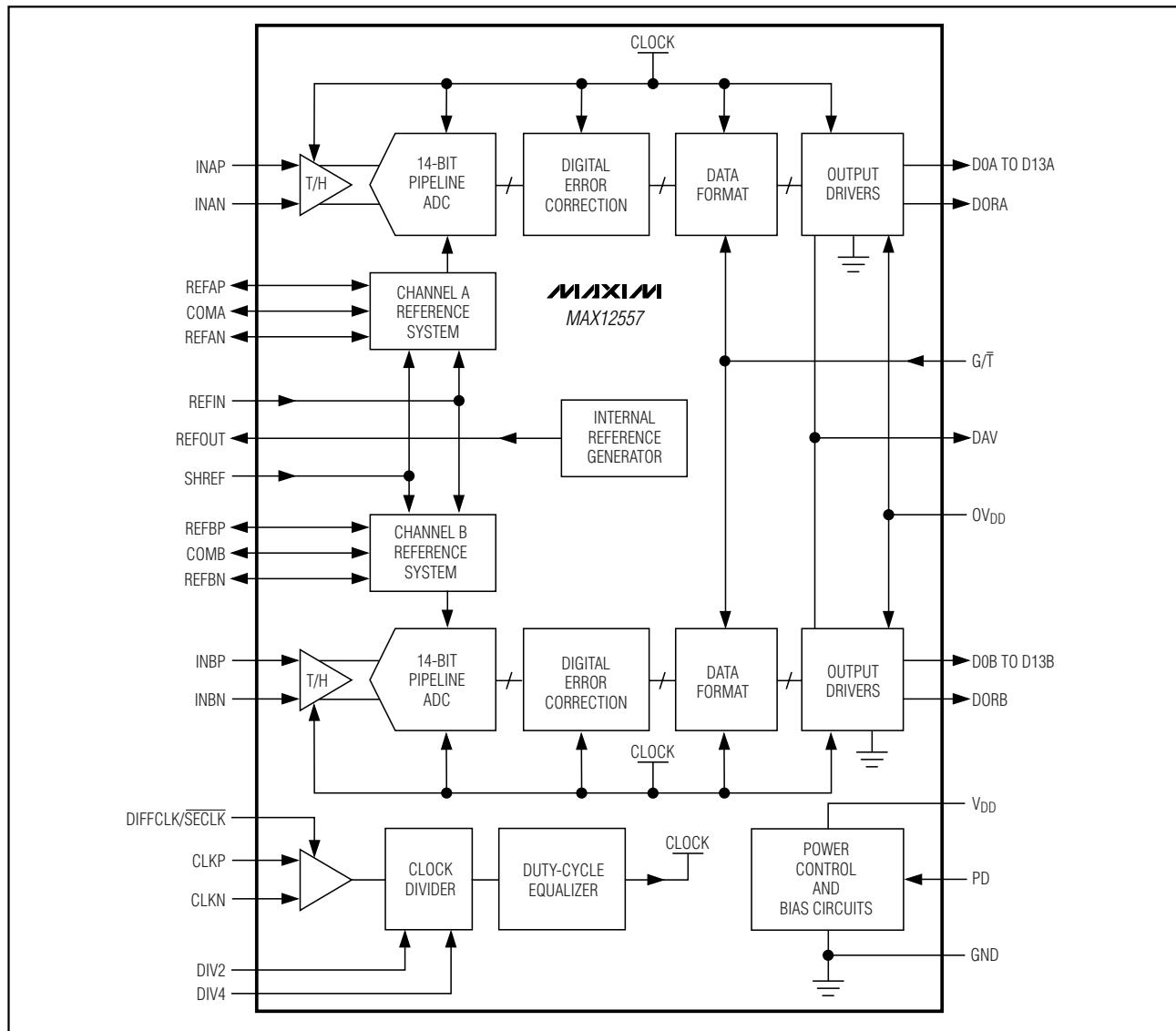

Figure 2. Functional Diagram

## Dual, 65MspS, 14-Bit, IF/Baseband ADC

Figure 3. Internal T/H Circuit

### Analog Inputs and Input Track-and-Hold (T/H) Amplifier

Figure 3 displays a simplified functional diagram of the input T/H circuit. This input T/H circuit allows for high analog input frequencies of 175MHz and beyond and supports a  $V_{DD} / 2$  common-mode input voltage.

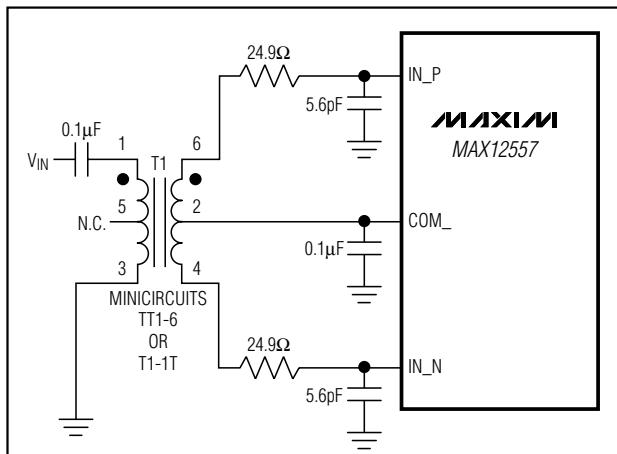

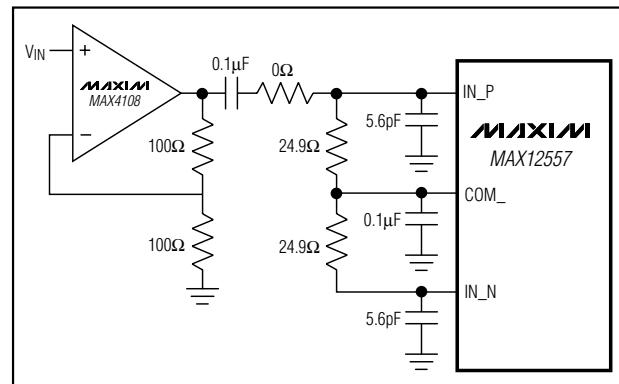

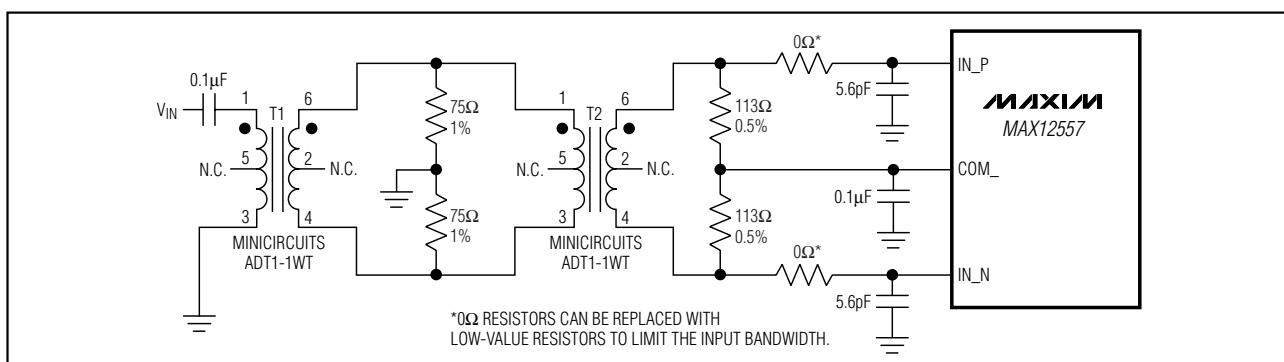

The MAX12557 sampling clock controls the switched-capacitor input T/H architecture (Figure 3) allowing the analog input signals to be stored as charge on the sampling capacitors. These switches are closed (track mode) when the sampling clock is high and open (hold mode) when the sampling clock is low (Figure 4). The analog input signal source must be able to provide the dynamic currents necessary to charge and discharge the sampling capacitors. To avoid signal degradation, these capacitors must be charged to one-half LSB accuracy within one-half of a clock cycle. The analog input of the MAX12557 supports differential or single-ended input drive. For optimum performance with differential inputs, balance the input impedance of IN\_P and IN\_N and set the common-mode voltage to mid-supply ( $V_{DD} / 2$ ). The MAX12557 provides the optimum common-mode voltage of  $V_{DD} / 2$  through the COM output when operating in internal reference mode and buffered external reference mode. This COM output voltage can be used to bias the input network as shown in Figures 9, 10, and 11.

### Reference Output

An internal bandgap reference is the basis for all the internal voltages and bias currents used in the

**Table 1. Reference Modes**

| V <sub>REFIN</sub>                                  | REFERENCE MODE                                                                                                                                                                                                                                |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35% V <sub>REFOUT</sub> to 100% V <sub>REFOUT</sub> | Internal Reference Mode.<br>REFIN is driven by REFOUT either through a direct short or a resistive divider.<br>$V_{COM} = V_{DD} / 2$<br>$V_{REF\_P} = V_{DD} / 2 + 3/8 \times V_{REFIN}$<br>$V_{REF\_N} = V_{DD} / 2 - 3/8 \times V_{REFIN}$ |

| 0.7V to 2.3V                                        | Buffered External Reference Mode.<br>An external 0.7V to 2.3V reference voltage is applied to REFIN.<br>$V_{COM} = V_{DD} / 2$<br>$V_{REF\_P} = V_{DD} / 2 + 3/8 \times V_{REFIN}$<br>$V_{REF\_N} = V_{DD} / 2 - 3/8 \times V_{REFIN}$        |

| <0.5V                                               | Unbuffered External Reference Mode.<br>REF_P, REF_N, and COM_ are driven by external reference sources. The full-scale analog input range is $\pm(V_{REF\_P} - V_{REF\_N}) \times 2/3$ .                                                      |

MAX12557. The power-down logic input (PD) enables and disables the reference circuit. REFOUT has approximately  $17\text{k}\Omega$  to GND when the MAX12557 is powered down. The reference circuit requires 10ms to power up and settle to its final value when power is applied to the MAX12557 or when PD transitions from high to low.

The internal bandgap reference produces a buffered reference voltage of  $2.048V \pm 1\%$  at the REFOUT pin with a  $\pm 50\text{ppm}/^{\circ}\text{C}$  temperature coefficient. Connect an external  $\geq 0.1\mu\text{F}$  bypass capacitor from REFOUT to GND for stability. REFOUT sources up to  $1\text{mA}$  and sinks up to  $0.1\text{mA}$  for external circuits with a  $35\text{mV}/\text{mA}$  load regulation. Short-circuit protection limits IREFOUT to a  $2.1\text{mA}$  source current when shorted to GND and a  $0.24\text{mA}$  sink current when shorted to  $V_{DD}$ . Similar to REFOUT, REFIN should be bypassed with a  $4.7\mu\text{F}$  capacitor to GND.

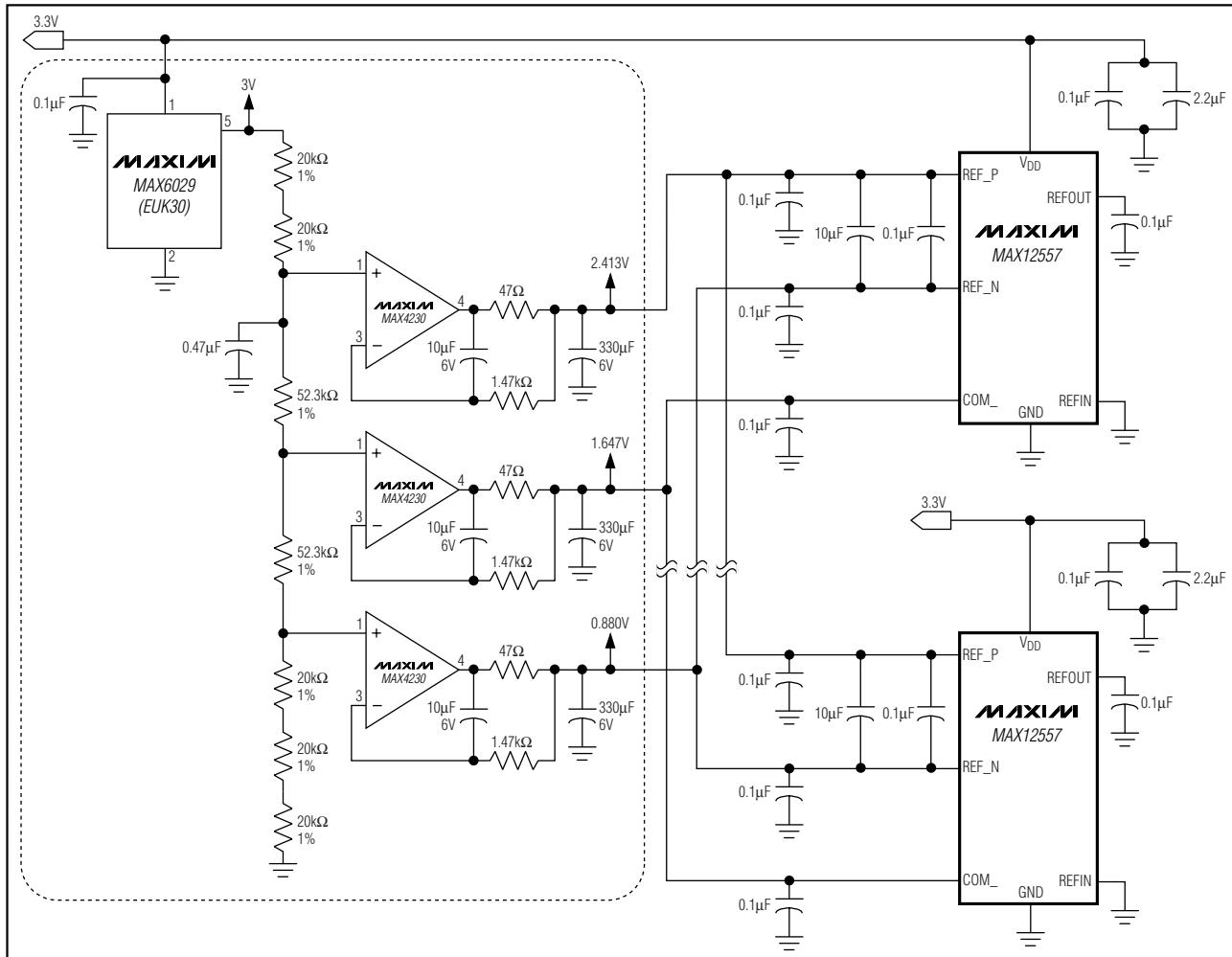

### Reference Configurations

The MAX12557 full-scale analog input range is  $\pm 2/3 \times V_{REF}$  with a  $V_{DD} / 2 \pm 0.5\text{V}$  common-mode input range. V<sub>REF</sub> is the voltage difference between REFAP (REFBP) and REFAN (REFBN). The MAX12557 provides three modes of reference operation. The voltage at REFIN ( $V_{REFIN}$ ) selects the reference operation mode (Table 1).

Connect REFOUT to REFIN either with a direct short or through a resistive divider to enter internal reference mode. COM\_, REF\_P, and REF\_N are low-impedance outputs with  $V_{COM} = V_{DD} / 2$ ,  $V_{REFP} = V_{DD} / 2 + 3/8 \times V_{REFIN}$ , and  $V_{REFN} = V_{DD} / 2 - 3/8 \times V_{REFIN}$ . Bypass REF\_P, REF\_N, and COM\_ each with a  $0.1\mu\text{F}$  capacitor

## Dual, 65MspS, 14-Bit, IF/Baseband ADC

**MAX12557**

to GND. Bypass REF\_P to REF\_N with a 10 $\mu$ F capacitor. Bypass REFIN and REfout to GND with a 0.1 $\mu$ F capacitor. The REFIN input impedance is very large (>50M $\Omega$ ). When driving REFIN through a resistive divider, use resistances  $\geq$ 10k $\Omega$  to avoid loading REfout.

Buffered external reference mode is virtually identical to the internal reference mode except that the reference source is derived from an external reference and not the MAX12557's internal bandgap reference. In buffered external reference mode, apply a stable reference voltage source between 0.7V to 2.3V at REFIN. Pins COM\_, REF\_P, and REF\_N are low-impedance outputs with  $V_{COM\_} = V_{DD} / 2$ ,  $V_{REF\_P} = V_{DD} / 2 + 3/8 \times V_{REFIN}$ , and  $V_{REF\_N} = V_{DD} / 2 - 3/8 \times V_{REFIN}$ . Bypass REF\_P, REF\_N, and COM\_ each with a 0.1 $\mu$ F capacitor to GND. Bypass REF\_P to REF\_N with a 10 $\mu$ F capacitor.

Connect REFIN to GND to enter unbuffered external reference mode. Connecting REFIN to GND deactivates the on-chip reference buffers for COM\_, REF\_P, and REF\_N. With their buffers deactivated, COM\_, REF\_P, and REF\_N become high-impedance inputs and must be driven with separate, external reference sources. Drive  $V_{COM\_}$  to  $V_{DD} / 2 \pm 5\%$ , and drive REF\_P and REF\_N so  $V_{COM\_} = (V_{REF\_P} + V_{REF\_N}) / 2$ . The analog input range is  $\pm(V_{REF\_P} - V_{REF\_N}) \times 2/3$ . Bypass REF\_P, REF\_N, and COM\_ each with a 0.1 $\mu$ F capacitor to GND. Bypass REF\_P to REF\_N with a 10 $\mu$ F capacitor.

For all reference modes, bypass REfout with a 0.1 $\mu$ F and REFIN with a 4.7 $\mu$ F capacitor to GND.

The MAX12557 also features a shared reference mode, in which the user can achieve better channel-to-channel matching. When sharing the reference (SHREF = VDD), externally connect REFAP and REFBP together to ensure that VREFAP = VREFBP. Similarly, when sharing the reference, externally connect REFAN to REFBN together to ensure that VREFAN = VREFBN.

Connect SHREF to GND to disable the shared reference mode of the MAX12557. In this independent reference mode, a better channel-to-channel isolation is achieved.

For detailed circuit suggestions and how to drive the ADC in buffered/unbuffered external reference mode, see the *Applications Information* section.

### Clock Duty-Cycle Equalizer

The MAX12557 has an internal clock duty-cycle equalizer, which makes the converter insensitive to the duty cycle of the signal applied to CLKP and CLKN. The converters allow clock duty-cycle variations from 25% to 75% without negatively impacting the dynamic performance.

The clock duty-cycle equalizer uses a delay-locked loop (DLL) to create internal timing signals that are duty-cycle independent. Due to this DLL, the MAX12557 requires approximately 100 clock cycles to acquire and lock to new clock frequencies.

### Clock Input and Clock Control Lines

The MAX12557 accepts both differential and single-ended clock inputs with a wide 25% to 75% input clock duty cycle. For single-ended clock input operation, connect DIFFCLK/SECLK and CLKN to GND. Apply an external single-ended clock signal to CLKP. To reduce clock jitter, the external single-ended clock must have sharp falling edges. For differential clock input operation, connect DIFFCLK/SECLK to OVDD. Apply an external differential clock signal to CLKP and CLKN. Consider the clock input as an analog input and route it away from any other analog inputs and digital signal lines. CLKP and CLKN enter high impedance when the MAX12557 is powered down (Figure 4).

Low clock jitter is required for the specified SNR performance of the MAX12557. The analog inputs are sampled on the falling (rising) edge of CLKP (CLKN), requiring this edge to have the lowest possible jitter. Jitter limits the maximum SNR performance of any ADC according to the following relationship:

$$SNR = 20 \times \log \left( \frac{1}{2 \times \pi \times f_N \times t_J} \right)$$

where  $f_N$  represents the analog input frequency and  $t_J$  is the total system clock jitter. Clock jitter is especially critical for undersampling applications. For instance, assuming that clock jitter is the only noise source, to obtain the specified 72.5dB of SNR with an input frequency of 175MHz the system must have less than 0.21ps of clock jitter. However, in reality there are other noise sources such as thermal noise and quantization noise that contribute to the system noise requiring the clock jitter to be less than 0.14ps to obtain the specified 72.5dBc of SNR at 175MHz.

### Clock-Divider Control Inputs (DIV2, DIV4)

The MAX12557 features three different modes of sampling/clock operation (see Table 2). Pulling both control lines low, the clock-divider function is disabled and the converters sample at full clock speed. Pulling DIV4 low and DIV2 high enables the divide-by-two feature, which sets the sampling speed to one-half the selected clock frequency. In divide-by-four mode, the converter sampling speed is set to one-fourth the clock speed of the MAX12557. Divide-by-four mode is achieved by applying a high level to DIV4 and a low level to DIV2. The option to

Figure 4. Simplified Clock Input Circuit

select either one-half or one-fourth of the clock speed for sampling provides design flexibility, relaxes clock requirements, and can minimize clock jitter.

### System Timing Requirements

Figure 5 shows the timing relationship between the clock, analog inputs, DAV indicator, DOR\_ indicators, and the resulting output data. The analog input is sampled on the falling (rising) edge of CLKN (CLKP) and the resulting data appears at the digital outputs 8 clock cycles later.

The DAV indicator is synchronized with the digital output and optimized for use in latching data into digital back-end circuitry. Alternatively, digital back-end cir-

**Table 2. Clock-Divider Control Inputs**

| DIV4 | DIV2 | FUNCTION                                                   |

|------|------|------------------------------------------------------------|

| 0    | 0    | Clock Divider Disabled<br>$f_{SAMPLE} = f_{CLK}$           |

| 0    | 1    | Divide-by-Two Clock Divider<br>$f_{SAMPLE} = f_{CLK} / 2$  |

| 1    | 0    | Divide-by-Four Clock Divider<br>$f_{SAMPLE} = f_{CLK} / 4$ |

| 1    | 1    | Not Allowed                                                |

cuiry can be latched with the rising edge of the conversion clock (CLKP - CLKN).

### Data-Valid Output

DAV is a single-ended version of the input clock that is compensated to correct for any input clock duty-cycle variations. The MAX12557 output data changes on the falling edge of DAV, and DAV rises once the output data is valid. The falling edge of DAV is synchronized to have a 5.4ns delay from the falling edge of the input clock. Output data at D0A/B-D13A/B and D0RA/B are valid from 7ns before the rising edge of DAV to 7ns after the rising edge of DAV.

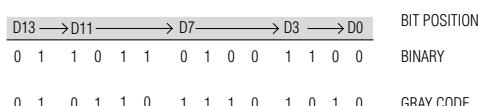

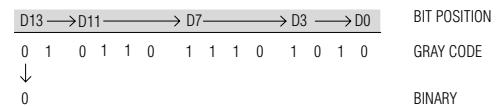

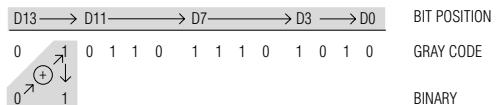

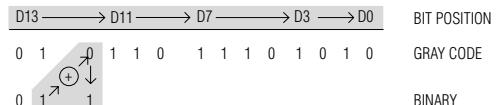

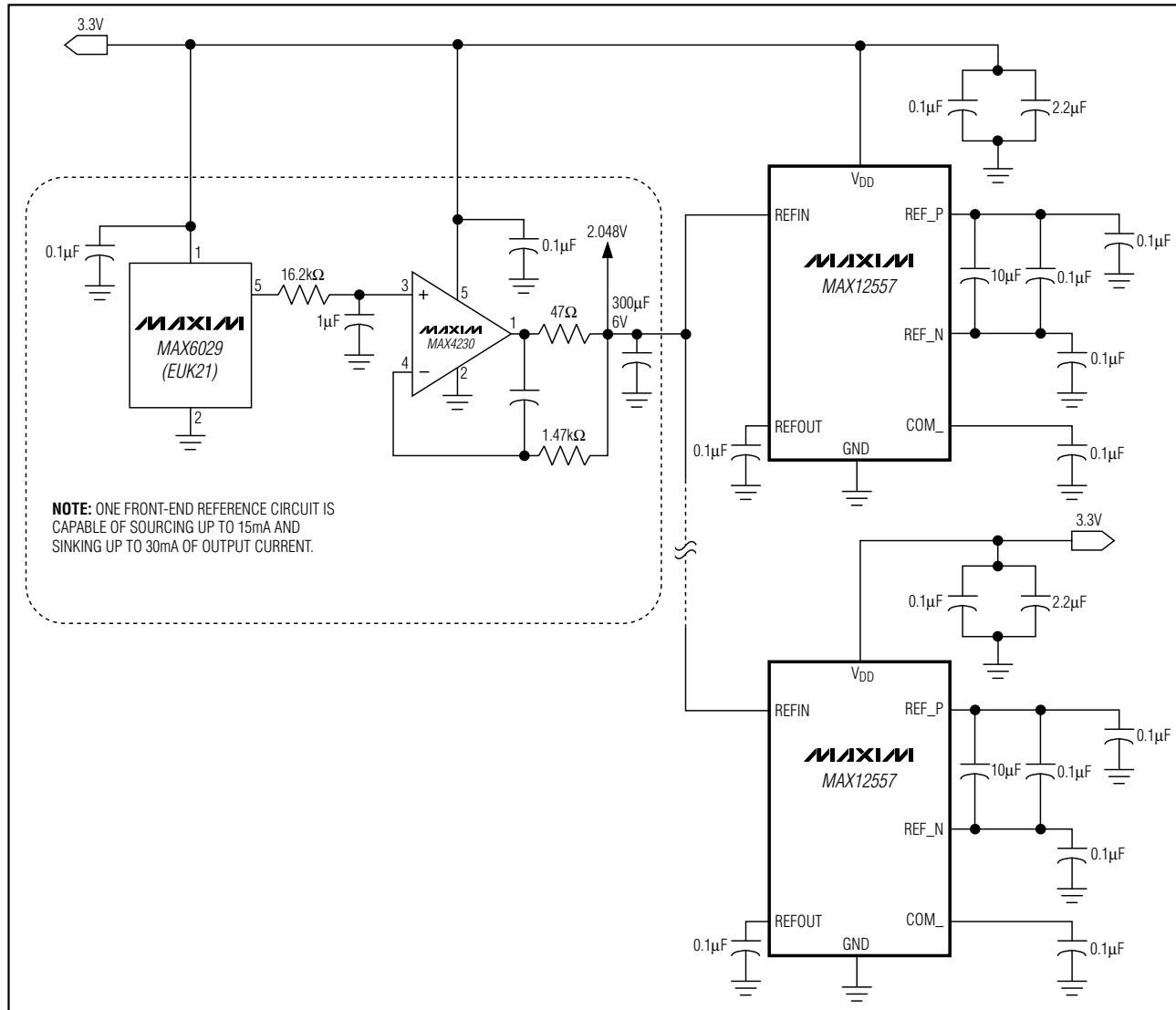

DAV enters high impedance when the MAX12557 is powered down ( $PD = OVDD$ ). DAV enters its high-impedance state 10ns after the rising edge of PD and becomes active again 10ns after PD transitions low.