### **Excellent Integrated System Limited**

Stocking Distributor

Click to view price, real time Inventory, Delivery & Lifecycle Information:

Maxim Integrated MAX4358ECE+

For any questions, you can email us directly: sales@integrated-circuit.com

###

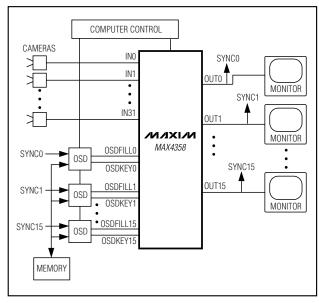

# 32 x 16 Nonblocking Video Crosspoint Switch with On-Screen Display Insertion and I/O Buffers

### **General Description**

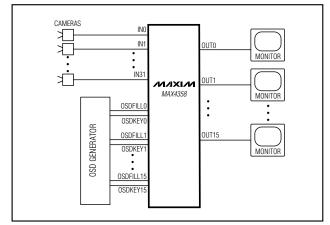

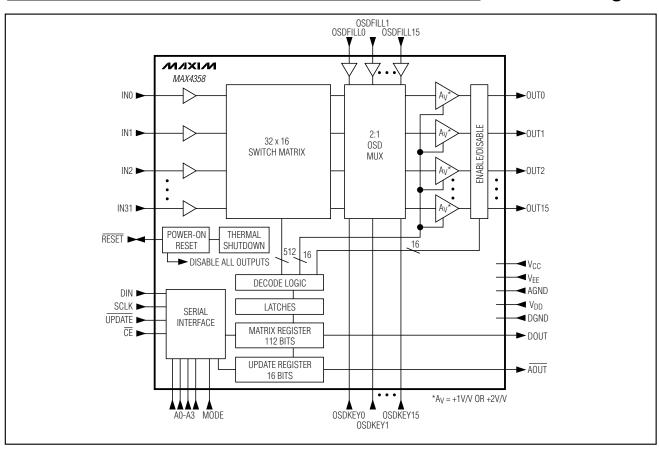

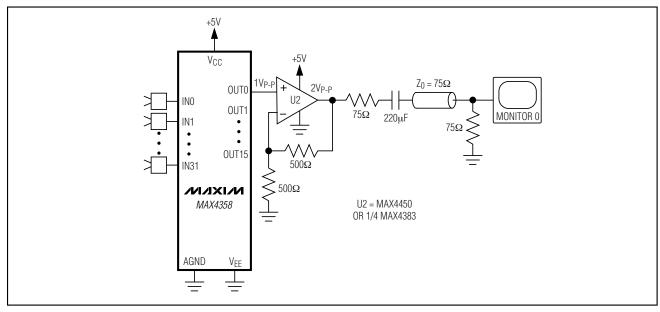

The MAX4358 is a 32  $\times$  16 highly integrated video crosspoint switch matrix with input and output buffers and On-Screen Display (OSD) Insertion. This device operates from dual  $\pm 3V$  to  $\pm 5V$  supplies or from a single +5V supply. Digital logic is supplied from an independent single  $\pm 2.7V$  to  $\pm 5.5V$  supply. Individual outputs can be switched between an input video signal source and OSD information through an internal, dedicated fast 2:1 mux (40ns switching times) located before the output buffer. All inputs and outputs are buffered, with all outputs able to drive standard  $75\Omega$  reverse-terminated video loads.

The switch matrix configuration and output buffer gain are programmed through an SPI/QSPI<sup>TM</sup>-compatible, three-wire serial interface and initialized with a single update signal. The unique serial interface operates in two modes facilitating both fast updates and initialization. On power-up, all outputs are initialized in the disabled state to avoid output conflicts in large-array configurations.

Superior flexibility, high integration, and space-saving packaging make this nonblocking switch matrix ideal for routing video signals in security and video-on-demand systems.

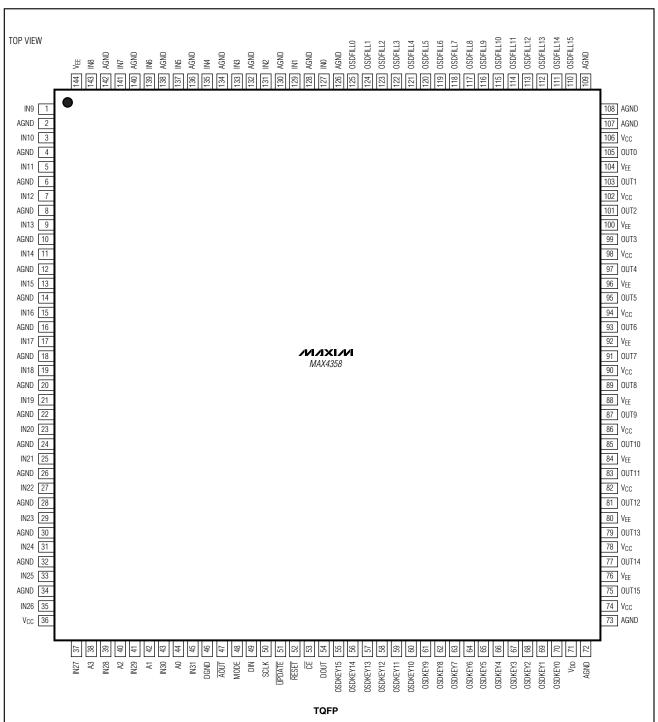

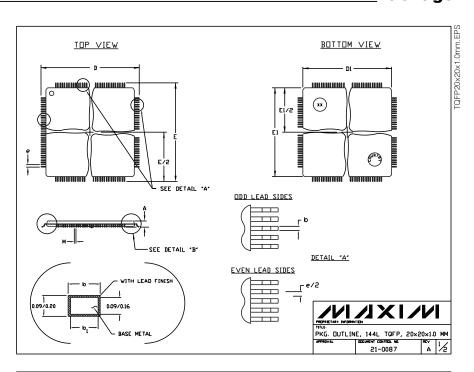

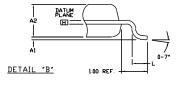

The MAX4358 is available in a 144-pin TQFP package and specified over an extended -40°C to +85°C temperature range. The MAX4358 evaluation kit is available to speed designs.

#### **Applications**

Security Systems

Video Routing

Video-On-Demand Systems

### \_Typical Operating Circuit

SPI/QSPI are trademarks of Motorola, Inc.

#### **Features**

- ♦ 32 × 16 Nonblocking Matrix with Buffered Inputs and Outputs

- ♦ Operates from a ±3V, ±5V, or +5V Supply

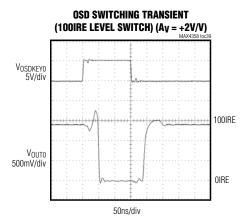

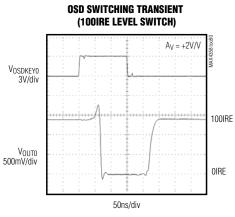

- ♦ Fast Switching (40ns) 2:1 OSD Insertion Mux

- ♦ Each Output Individually Addressable

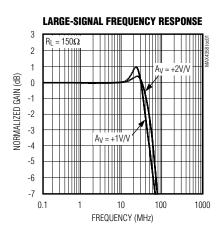

- ♦ Individually Programmable Output Buffer Gain (Ay = +1V/V or +2V/V)

- High-Impedance Output Disable for Wired-OR Connections

- ♦ 0.1dB Gain Flatness to 12MHz

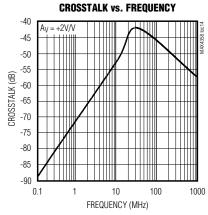

- ♦ Minimum -62dB Crosstalk, -110dB Isolation at 6MHz

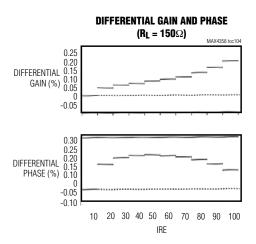

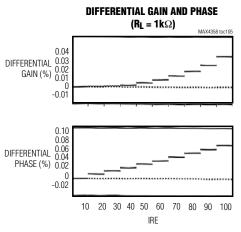

- ♦ 0.05%/0.1° Differential Gain/Differential Phase Error

- Low 195mW Power Consumption (0.38mW per point)

### **Ordering Information**

| PART       | TEMP RANGE     | PIN PACKAGE |

|------------|----------------|-------------|

| MAX4358ECE | -40°C to +85°C | 144 TQFP    |

Pin Configuration appears at end of data sheet.

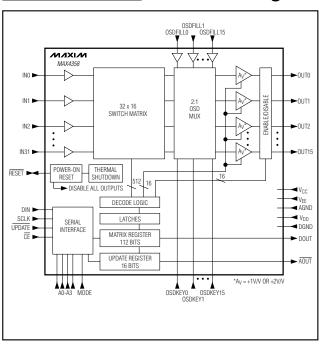

#### Functional Diagram

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| Analog Supply Voltage (VCC - VEE)+                     | -11V  |

|--------------------------------------------------------|-------|

| Digital Supply Voltage (VDD - DGND)                    |       |

| Analog Supplies to Analog Ground                       |       |

| (V <sub>CC</sub> - AGND) and (AGND - V <sub>EE</sub> ) | +6V   |

| Analog Ground to Digital Ground0.3V to +               |       |

| IN, OSDFILL Voltage Range (VCC + 0.3V) to (VEE - C     | .3V)  |

| OUT Short-Circuit Duration to AGND, VCC, or VEEIndef   | inite |

| SCLK, CE, UPDATE, MODE, A_, DIN, DOUT,                 |       |

| RESET, AOUT, OSDKEY(VDD + 0.3V) to (DGND - 0           | (V8.i |

| Current Into Any Analog Input Pin (IN_, OSDFILL_<br>Current Into Any Analog Output Pin (OUT_) |               |

|-----------------------------------------------------------------------------------------------|---------------|

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                                         |               |

| 144-Pin TQFP (derate 28.6mW/°C above +70°                                                     | C)2.23W       |

| Operating Temperature Range                                                                   | 40°C to +85°C |

| Junction Temperature                                                                          | +150°C        |

| Storage Temperature Range69                                                                   |               |

| Lead Temperature (soldering, 10s)                                                             | +300°C        |

|                                                                                               |               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS—DUAL SUPPLIES ±5V

$(V_{CC} = +5V, V_{EE} = -5V, V_{DD} = +5V, AGND = DGND = 0, V_{IN} = 0, V_{OSDFILL} = 0, R_L = 150\Omega$  to AGND, and  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                         | SYMBOL                       | CONDITIONS                                                                             |                                                                                   | MIN                    | TYP   | MAX                       | UNITS  |  |

|-----------------------------------|------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------|-------|---------------------------|--------|--|

| Operating Supply Voltage<br>Range | V <sub>CC</sub> -            | Guaranteed by PS                                                                       | Guaranteed by PSRR test                                                           |                        |       | 10.5                      | V      |  |

| Logic Supply Voltage Range        | V <sub>DD</sub> to<br>DGND   |                                                                                        |                                                                                   | 2.7                    |       | 5.5                       | V      |  |

|                                   |                              | (VEE + 2.5V) < V <sub>II</sub><br>A <sub>V</sub> = +1V/V, R <sub>L</sub> =             |                                                                                   | 0.97                   | 0.995 | 1                         |        |  |

| Gain (Note 1)                     | $A_{V} = +1V$ $(V_{EE} + 3)$ | (V <sub>EE</sub> + 2.5V) < V <sub>II</sub><br>A <sub>V</sub> = +1V/V, R <sub>L</sub> = |                                                                                   | 0.99                   | 0.999 | 1                         |        |  |

|                                   |                              |                                                                                        | $(V_{EE} + 3.75V) < V_{IN} < (V_{CC} - 3.75V),$<br>$A_V = +2V/V, R_L = 150\Omega$ |                        | 1.996 | 2.08                      | V/V    |  |

|                                   |                              | $(V_{EE} + 3.75V) < V_{IN} < (V_{CC} - 3.75V)$<br>$A_V = +2V/V, R_L = 10k\Omega$       |                                                                                   | 1.94                   | 2.008 | 2.06                      |        |  |

|                                   |                              | $(V_{EE} + 1V) < V_{IN} < (V_{CC} - 1.2V),$<br>$A_{V} = +1V/V, R_{L} = 10k\Omega$      |                                                                                   | 0.95                   | 0.994 | 1                         |        |  |

| Gain Matching                     |                              | $R_L = 10k\Omega$                                                                      |                                                                                   |                        | 0.5   | 1.5                       | %      |  |

| (Channel to Channel)              |                              | $R_L = 150\Omega$                                                                      |                                                                                   |                        | 0.5   | 2                         | 70     |  |

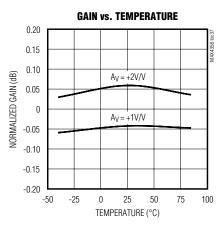

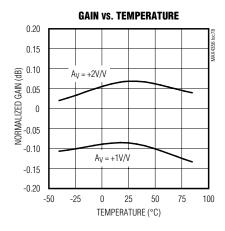

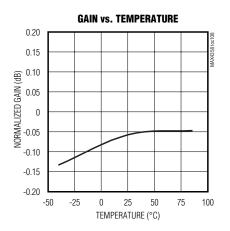

| Temperature Coefficient of Gain   | TCAV                         |                                                                                        |                                                                                   |                        | 10    |                           | ppm/°C |  |

|                                   |                              | 4)/0/                                                                                  | $R_L = 10k\Omega$                                                                 | V <sub>EE</sub> + 1    |       | V <sub>CC</sub> - 1.2     |        |  |

| January Walter and Danner         |                              | $A_V = +1V/V$                                                                          | $R_L = 150\Omega$                                                                 | V <sub>EE</sub> + 2.5  |       | V <sub>CC</sub> - 2.5     |        |  |

| Input Voltage Range               | V <sub>IN</sub> _            |                                                                                        | $R_L = 10k\Omega$                                                                 | V <sub>EE</sub> + 3    |       | V <sub>CC</sub> - 3.1     | - V    |  |

|                                   |                              | $A_V = +2V/V$                                                                          | $R_L = 150\Omega$                                                                 | V <sub>EE</sub> + 3.75 |       | V <sub>CC</sub> -<br>3.75 |        |  |

N/XL/N

### DC ELECTRICAL CHARACTERISTICS—DUAL SUPPLIES ±5V (continued)

$(V_{CC} = +5V, V_{EE} = -5V, V_{DD} = +5V, AGND = DGND = 0, V_{IN} = 0, V_{OSDFILL} = 0, R_L = 150\Omega$  to AGND, and  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25$ °C.)

| PARAMETER                               | SYMBOL            | CON                                       | IDITIONS                                   | MIN                   | TYP       | MAX                   | UNITS |

|-----------------------------------------|-------------------|-------------------------------------------|--------------------------------------------|-----------------------|-----------|-----------------------|-------|

| Output                                  | Vout              | $R_L = 10k\Omega$                         | $R_L = 10k\Omega$                          |                       |           | V <sub>CC</sub> - 1.2 | V     |

| Voltage Range                           | V001              | $R_L = 150\Omega$                         |                                            | V <sub>EE</sub> + 2.5 |           | V <sub>CC</sub> - 2.5 | V     |

| Input Bias Current                      | IB                |                                           |                                            |                       | 4         | 11                    | μΑ    |

| Input Resistance                        | R <sub>IN</sub> _ | $(V_{EE} + 1V) < V_{IN_{}}$               | < (V <sub>CC</sub> - 1.2V)                 |                       | 10        |                       | МΩ    |

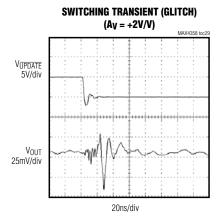

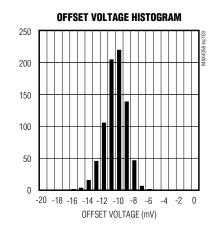

| Output Offset Voltage                   | VOFFSET           | $A_V = +1V/V$ $A_V = +2V/V$               |                                            |                       | ±5<br>±10 | ±20<br>±40            | mV    |

| Output Short-Circuit Current            | I <sub>SC</sub>   | Sinking or sourcir                        | ng, $R_L = 1\Omega$                        |                       | ±40       |                       | mA    |

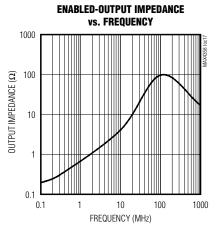

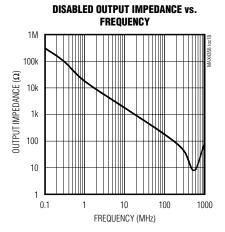

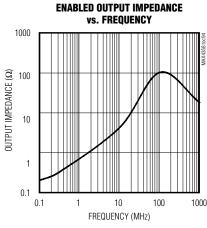

| Enabled Output Impedance                | Z <sub>OUT</sub>  | $(V_{EE} + 1V) < V_{IN}$                  | < (V <sub>CC</sub> - 1.2V)                 |                       | 0.2       |                       | Ω     |

| Output Leakage Current,<br>Disable Mode | lod               | (V <sub>EE</sub> + 1V) < V <sub>OU</sub>  | <sub>IT_</sub> < (V <sub>CC</sub> - 1.2V)  |                       | 0.004     | 1                     | μА    |

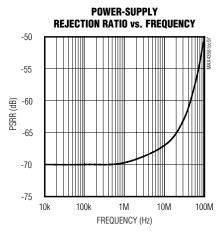

| DC Power-Supply Rejection<br>Ratio      | PSRR              | 4.5V < (V <sub>CC</sub> - V <sub>EE</sub> | e) < 10.5V                                 | 60                    | 70        |                       | dB    |

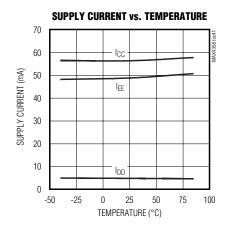

|                                         | 1                 | D.                                        | Outputs enabled,<br>T <sub>A</sub> = +25°C |                       | 110       | 160                   |       |

|                                         | Icc               | R <sub>L</sub> = ∞                        | Outputs enabled                            |                       |           | 185                   |       |

|                                         |                   |                                           | Outputs disabled                           |                       | 60        | 80                    | mA    |

| Quiescent<br>Supply Current             |                   | D.                                        | Outputs enabled,<br>$T_A = +25^{\circ}C$   |                       | 105       | 160                   |       |

|                                         | IEE               | R <sub>L</sub> = ∞                        | Outputs enabled                            |                       |           | 185                   |       |

|                                         |                   |                                           | Outputs disabled                           |                       | 55        | 80                    |       |

|                                         | I <sub>DD</sub>   |                                           |                                            |                       | 4         | 8                     |       |

### DC ELECTRICAL CHARACTERISTICS—DUAL SUPPLIES ±3V

$(V_{CC}=+3V, V_{EE}=-3V, V_{DD}=+3V, AGND=DGND=0, V_{IN}=0, V_{OSDFILL}=0, R_L=150\Omega$  to AGND, and  $T_A=T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A=+25^{\circ}C$ .)

| PARAMETER                         | SYMBOL                            | CON                                                                          | NDITIONS                   | MIN                 | TYP   | MAX                      | UNITS                   |

|-----------------------------------|-----------------------------------|------------------------------------------------------------------------------|----------------------------|---------------------|-------|--------------------------|-------------------------|

| Operating Supply Voltage<br>Range | V <sub>CC</sub> - V <sub>EE</sub> | Guaranteed by PS                                                             | SRR test                   | 4.5                 |       | 10.5                     | V                       |

| Logic Supply Voltage Range        | V <sub>DD</sub> to<br>DGND        |                                                                              |                            | 2.7                 |       | 5.5                      | V                       |

|                                   |                                   | (VEE + 1V) < V <sub>IN</sub> _<br>A <sub>V</sub> = +1V/V, R <sub>L</sub> =   |                            | 0.94                | 0.983 | 1                        |                         |

| Coin (Note 1)                     | A                                 | (VEE + 1V) < V <sub>IN_</sub><br>A <sub>V</sub> = +1V/V, R <sub>L</sub> =    |                            | 0.96                | 0.993 | 1                        | - V/V                   |

| Gain (Note 1)                     | Av                                | (VEE + 2V) < V <sub>IN_</sub><br>A <sub>V</sub> = +2V/V, R <sub>L</sub> =    |                            | 1.92                | 1.985 | 2.08                     | V/V                     |

| Gain Matching                     |                                   | $(V_{EE} + 2V) < V_{IN} < (V_{CC} - 2.1V)$<br>$A_V = +2V/V, R_L = 10k\Omega$ |                            | 1.94                | 2.00  | 2.06                     |                         |

| Gain Matching                     |                                   | $R_L = 10k\Omega$                                                            |                            |                     | 0.5   | 1.5                      | %                       |

| (Channel to Channel)              |                                   | $R_L = 150\Omega$                                                            |                            |                     | 0.5   | 2                        | /0                      |

| Temperature Coefficient of Gain   | TC <sub>AV</sub>                  |                                                                              |                            |                     | 10    |                          | ppm/°C                  |

|                                   |                                   | A <sub>V</sub> = +1V/V                                                       | $R_L = 10k\Omega$          | V <sub>EE</sub> + 1 |       | V <sub>CC</sub> -<br>1.2 | 1.2<br>00 -<br>1.2<br>V |

| Input Voltage Range               | V <sub>IN</sub> _                 |                                                                              | $R_L = 150\Omega$          | V <sub>EE</sub> + 1 |       | V <sub>CC</sub> -<br>1.2 |                         |

| input voltage hange               | VIN_                              | A 0)/A/                                                                      | $R_L = 10k\Omega$          | V <sub>EE</sub> + 2 |       | V <sub>CC</sub> - 2.1    |                         |

|                                   |                                   | A <sub>V</sub> = +2V/V                                                       | $R_L = 150\Omega$          | V <sub>EE</sub> + 2 |       | V <sub>CC</sub> - 2.1    |                         |

| Output Voltage Range              | Vour                              | $R_L = 10k\Omega$                                                            |                            | V <sub>EE</sub> + 1 |       | V <sub>CC</sub> -<br>1.2 | - v                     |

| Output Voltage Hange              | Vout                              | $R_L = 150\Omega$                                                            |                            | V <sub>EE</sub> + 1 |       | V <sub>CC</sub> - 1.2    | V                       |

| Input Bias Current                | ΙΒ                                |                                                                              |                            |                     | 4     | 11                       | μΑ                      |

| Input Resistance                  | RiN                               | $(V_{EE} + 1V) < V_{IN}$                                                     | < (V <sub>CC</sub> - 1.2V) |                     | 10    |                          | MΩ                      |

| Output Offset                     | VOFFSET                           | $A_V = +1V/V$                                                                |                            |                     | ±5    | ±20                      | mV                      |

| Voltage                           | VOFFSEI                           | $A_V = +2V/V$                                                                |                            |                     | ±10   | ±40                      | ''''                    |

#### DC ELECTRICAL CHARACTERISTICS—DUAL SUPPLIES ±3V (continued)

$(V_{CC} = +3V, V_{EE} = -3V, V_{DD} = +3V, AGND = DGND = 0, V_{IN} = 0, V_{OSDFILL} = 0, R_L = 150\Omega$  to AGND, and  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                               | SYMBOL           | CONDITIONS                                                            |                  | MIN | TYP   | MAX | UNITS |

|-----------------------------------------|------------------|-----------------------------------------------------------------------|------------------|-----|-------|-----|-------|

| Output Short-Circuit Current            | Isc              | Sinking or sourcing, $R_L = 1\Omega$                                  |                  |     | ±40   |     | mA    |

| Enabled Output Impedance                | Z <sub>OUT</sub> | (V <sub>EE</sub> + 1V) < V <sub>IN</sub> _ < (V <sub>CC</sub> - 1.2V) |                  |     | 0.2   |     | Ω     |

| Output Leakage Current,<br>Disable Mode | I <sub>OD</sub>  | (V <sub>EE</sub> + 1V) < V <sub>OUT</sub> _< (V <sub>CC</sub> - 1.2V) |                  |     | 0.004 | 1   | μΑ    |

| DC Power-Supply Rejection<br>Ratio      | PSRR             | 4.5V < (V <sub>CC</sub> - V <sub>EE</sub> ) < 10.5V                   |                  | 60  | 75    |     | dB    |

|                                         | Icc              | R <sub>L</sub> = ∞                                                    | Outputs enabled  |     | 95    |     |       |

| Quiescent                               |                  | 11 <u>L</u> = ∞                                                       | Outputs disabled |     | 50    |     |       |

| Supply                                  | IEE              | Rı = ∞                                                                | Outputs enabled  |     | 90    |     | mA    |

| Current                                 |                  | NL = ∞                                                                | Outputs disabled |     | 45    |     |       |

|                                         | I <sub>DD</sub>  |                                                                       |                  |     | 3     |     |       |

#### DC ELECTRICAL CHARACTERISTICS—SINGLE SUPPLY +5V

$(V_{CC} = +5V, V_{EE} = 0, V_{DD} = +5V, AGND = DGND = 0, V_{IN} = V_{OSDFILL} = +1.75V, A_V = +1V/V, R_L = 150\Omega$  to AGND, and  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                         | SYMBOL                     | со                                                                                | NDITIONS                | MIN               | TYP   | MAX                   | UNITS |

|-----------------------------------|----------------------------|-----------------------------------------------------------------------------------|-------------------------|-------------------|-------|-----------------------|-------|

| Operating Supply Voltage<br>Range | Vcc                        | Guaranteed by PS                                                                  | Guaranteed by PSRR test |                   |       | 5.5                   | V     |

| Logic-Supply Voltage Range        | V <sub>DD</sub> to<br>DGND |                                                                                   | 2.7                     |                   | 5.5   | V                     |       |

| Caia (Nata 1)                     | Δ                          | $(V_{EE} + 1V) < V_{IN}$<br>$A_V = +1V/V, R_L =$                                  | , ,                     | 0.94              | 0.995 | 1                     | V     |

| Gain (Note 1)                     | Av                         | $(V_{EE} + 1V) < V_{IN} < (V_{CC} - 1.2V),$<br>$A_{V} = +1V/V, R_{L} = 10k\Omega$ |                         | 0.94              | 0.995 | 1                     | V     |

| Gain Matching (Channel to         |                            | $R_L = 10k\Omega$                                                                 |                         |                   | 0.5   | 3                     | %     |

| Channel)                          |                            | $R_L = 150\Omega$                                                                 |                         |                   | 0.5   | 3                     | 3     |

| Temperature Coefficient of Gain   | TC <sub>AV</sub>           |                                                                                   |                         |                   | 10    |                       | ppm/° |

| _                                 |                            | A <sub>V</sub> = +1V/V                                                            | $R_L = 10k\Omega$       | V <sub>EE</sub> + |       | V <sub>CC</sub> - 1.2 |       |

| Input Voltage Range               | VIN                        |                                                                                   | $R_L = 150\Omega$       | V <sub>EE</sub> + |       | Vcc -<br>2.5          | V     |

| Output Voltage<br>Range           |                            | $A_V = +1V/V,$<br>$R_L = 10k\Omega$                                               | ·                       | V <sub>EE</sub> + |       | V <sub>CC</sub> - 1.2 |       |

|                                   | Vout                       | $A_V = +1V/V,$ $R_L = 150\Omega$                                                  |                         | V <sub>EE</sub> + |       | V <sub>CC</sub> - 2.5 | V     |

### DC ELECTRICAL CHARACTERISTICS—SINGLE SUPPLY +5V (continued)

$(V_{CC} = +5V, V_{EE} = 0, V_{DD} = +5V, AGND = DGND = 0, V_{IN} = V_{OSDFILL} = +1.75V, A_{V} = +1V/V, R_{L} = 150\Omega \text{ to AGND, and } T_{A} = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_{A} = +25^{\circ}C.)$

| PARAMETER                               | SYMBOL           |                        | CONDITIONS                                       |    | TYP   | MAX | UNITS |

|-----------------------------------------|------------------|------------------------|--------------------------------------------------|----|-------|-----|-------|

| Input Bias Current                      | ΙB               |                        |                                                  |    | 4     | 11  | μΑ    |

| Input Resistance                        | R <sub>IN</sub>  | V <sub>EE</sub> + 1V   | $< V_{IN_{-}} < V_{CC} - 1.2V$                   |    | 10    |     | МΩ    |

| Output Offset<br>Voltage                | Voffset          | A <sub>V</sub> = +1V/V |                                                  |    | ±10   | ±40 | mV    |

| Output Short-Circuit Current            | Isc              | Sinking o              | r sourcing, $R_L = 1\Omega$                      |    | ±35   |     | mA    |

| Enabled Output Impedance                | Z <sub>OUT</sub> | (V <sub>EE</sub> + 1\  | /) < V <sub>IN_</sub> < (V <sub>CC</sub> - 1.2V) |    | 0.2   |     | Ω     |

| Output Leakage Current,<br>Disable Mode | IOD              | (V <sub>EE</sub> + 1\  | /) < V <sub>OUT</sub> < (V <sub>CC</sub> - 1.2V) |    | 0.004 | 1   | μΑ    |

| DC Power-Supply Rejection<br>Ratio      | PSRR             | 4.5V < V(              | CC - V <sub>EE</sub> < 5.5V                      | 50 | 65    |     | dB    |

|                                         | 1                | D.                     | Outputs enabled, T <sub>A</sub> = +25°C          |    | 85    |     |       |

|                                         | Icc              | R <sub>L</sub> = ∞     | Outputs disabled                                 |    | 35    |     |       |

| Quiescent Supply                        | 1                | D.                     | Outputs enabled, T <sub>A</sub> = +25°C          |    | 80    |     | mA    |

| Current                                 | lEE              | nL = ∞                 | R <sub>L</sub> = ∞ Outputs disabled              |    | 30    |     |       |

|                                         | I <sub>DD</sub>  |                        |                                                  |    | 4     | •   |       |

6 \_\_\_\_\_\_ /N/XI/N

#### **LOGIC-LEVEL CHARACTERISTICS**

$(V_{CC} - V_{EE}) = +4.5V$  to +10.5V,  $V_{DD} = +2.7V$  to +5.5V, AGND = DGND = 0,  $V_{IN} = V_{OSDFILL} = 0$ ,  $R_L = 150\Omega$  to AGND, and  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                | SYMBOL           |                               | CONDITIONS                     | MIN  | TYP  | MAX | UNITS |

|--------------------------|------------------|-------------------------------|--------------------------------|------|------|-----|-------|

| Input Voltage High Lovel | V                | $V_{DD} = +5.0V$              |                                | 3    |      |     |       |

| Input Voltage High Level | V <sub>IH</sub>  | $V_{DD} = +3V$                |                                | 2    |      |     | V     |

| Input Voltage            | VII              | $V_{DD} = +5.0V$              |                                |      |      | 0.8 |       |

| Low Level                | V IL             | $V_{DD} = +3V$                |                                |      |      | 0.6 | V     |

| Input Current            | luu              | V <sub>I</sub> > 2V           | Excluding RESET                | -1   | 0.01 | 1   |       |

| High Level               | lін              | V  > 2V                       | RESET                          | -30  | -20  |     | μΑ    |

| Input Current            | l.,              | V <sub>I</sub> < 1V           | Excluding RESET                | -1   | 0.01 | 1   |       |

| Low Level                | I <sub>Ι</sub> Γ |                               | RESET                          | -300 | -235 |     | μΑ    |

| Output Voltage High      | Voh              | ISOURCE = 1mA                 | $v_{N}$ , $V_{DD} = +5V$       | 4.7  | 4.9  |     | V     |

| Level                    | VOH              | ISOURCE = 1mA                 | $v_{N}$ , $V_{DD} = +3V$       | 2.7  | 2.9  |     | V     |

| Output Voltage Low       | VOL              | ISINK = 1mA, V                | OD = +5V                       |      | 0.1  | 0.3 | V     |

| Level                    | VOL              | ISINK = 1mA, V                | $I_{SINK} = 1mA, V_{DD} = +3V$ |      | 0.1  | 0.3 | V     |

| Output Current High      | lou              | $V_{DD} = +5V, V_{O}$         | = +4.9V                        | 1    | 4    |     | mA    |

| Level                    | Іон              | $V_{DD} = +3V, V_{OI}$        | JT = +2.7V                     | 1    | 8    |     | MA    |

| Output Current           | lou              | $V_{DD} = +5V, V_{O} = +0.1V$ |                                | 1    | 4    |     | m /   |

| Low Level                | loL              | $V_{DD} = +3V, V_{O}$         | = +0.3V                        | 1    | 8    | •   | mA    |

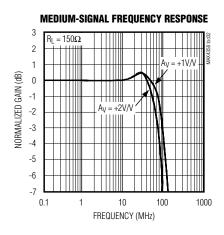

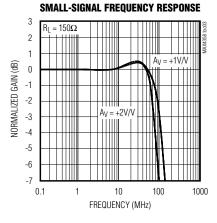

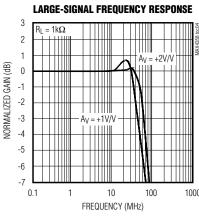

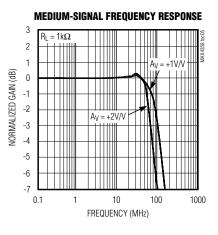

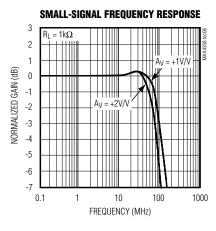

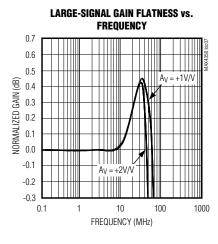

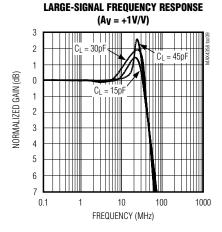

#### AC ELECTRICAL CHARACTERISTICS—DUAL SUPPLIES ±5V

$(V_{CC} = +5V, V_{EE} = -5V, V_{DD} = +5V, AGND = DGND = 0, V_{IN} = V_{OSDFILL} = 0, R_L = 150\Omega$  to AGND, and  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER          | SYMBOL                 | COND                                          | ITIONS        | MIN | TYP | MAX | UNITS                |

|--------------------|------------------------|-----------------------------------------------|---------------|-----|-----|-----|----------------------|

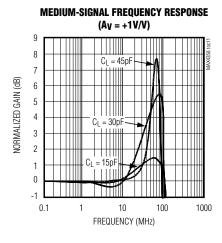

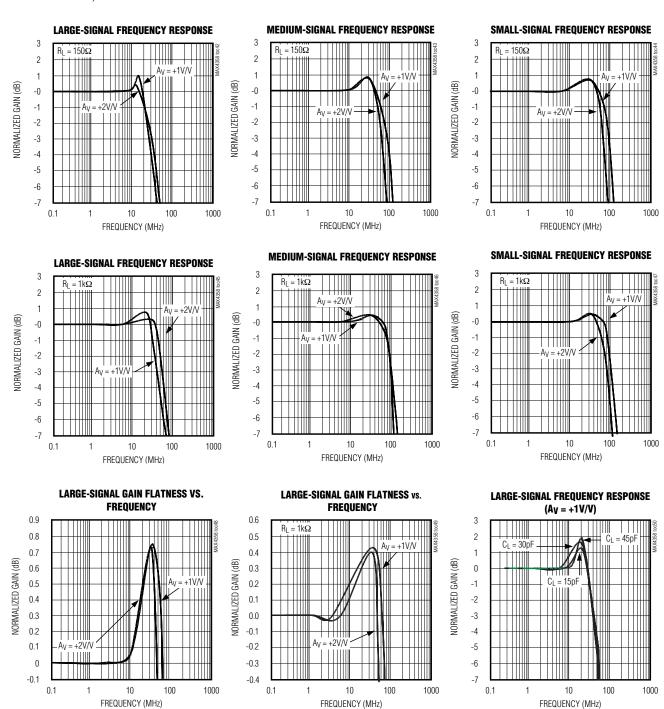

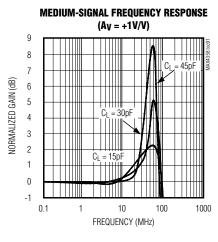

| Small-Signal -3dB  | BWss                   | V <sub>OUT</sub> = 20mVp-p                    | $A_V = +1V/V$ |     | 95  |     | MHz                  |

| Bandwidth          |                        | 001_ 11                                       | $A_V = +2V/V$ |     | 70  |     |                      |

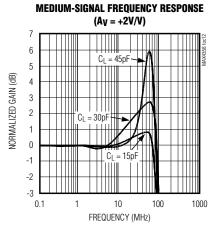

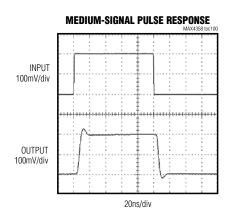

| Medium-Signal -3dB | BW <sub>MS</sub>       | V <sub>OUT</sub> _=                           | $A_V = +1V/V$ |     | 90  |     | MHz                  |

| Bandwidth          | DAMIN2                 | 200mVp-p                                      | $A_V = +2V/V$ |     | 70  |     | IVII IZ              |

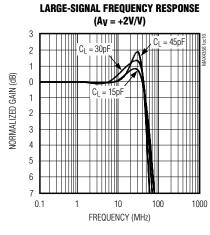

| Large-Signal -3dB  | BWLS                   | V <sub>OUT</sub> = 2Vp-p                      | $A_V = +1V/V$ |     | 40  |     | MHz                  |

| Bandwidth          | DWES                   | νΟΟΙ_= Σνρ-ρ                                  | $A_V = +2V/V$ |     | 50  |     | IVI□∠                |

| Small-Signal 0.1dB | BW <sub>0.1dB-SS</sub> | Vour - 20m\/n n                               | $A_V = +1V/V$ |     | 15  |     | MHz                  |

| Bandwidth          |                        | V <sub>OUT</sub> _= 20mVp-p                   | $A_V = +2V/V$ |     | 15  |     | IVIIIZ               |

| Medium-Signal      | BW <sub>0.1dB-MS</sub> | V <sub>OUT</sub> _=                           | $A_V = +1V/V$ |     | 15  |     | MHz                  |

| 0.1dB Bandwidth    | DVV0.10B-MS            | 200mVp-p                                      | $A_V = +2V/V$ |     | 15  |     | IVIITZ               |

| Large-Signal 0.1dB | DW                     | \/a. = 0\/a a                                 | $A_V = +1V/V$ |     | 12  |     | MHz                  |

| Bandwidth          | BW <sub>0.1dB-LS</sub> | V <sub>OUT</sub> _= 2Vp-p                     | $A_V = +2V/V$ |     | 12  |     | IVI□∠                |

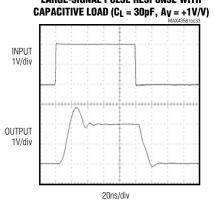

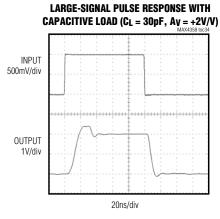

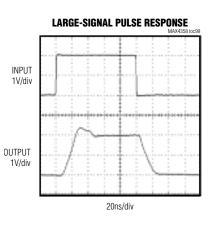

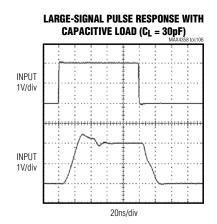

| Slew Rate          | CD                     | $V_{OUT} = 2V$ step,<br>$A_V = +1V/V$         |               |     | 150 |     | \// <sub>1</sub> , a |

|                    | SR                     | $V_{OUT} = 2V \text{ step},$<br>$A_V = +2V/V$ |               |     | 160 |     | V/μs                 |

### AC ELECTRICAL CHARACTERISTICS—DUAL SUPPLIES ±5V (continued)

$(V_{CC} = +5V, V_{EE} = -5V, V_{DD} = +5V, AGND = DGND = 0, V_{IN} = V_{OSDFILL} = 0, R_L = 150\Omega$  to AGND, and  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                | SYMBOL              | CO                  | NDITIONS        | MIN TY | P MAX    | UNITS             |  |  |

|------------------------------------------|---------------------|---------------------|-----------------|--------|----------|-------------------|--|--|

| Cottling Times                           | 4                   | Vout = 0 to 2V      | $A_V = +1V/V$   | 6      | 0        |                   |  |  |

| Settling Time                            | <sup>t</sup> S 0.1% | step                | $A_V = +2V/V$   | 6      | 0        | ns                |  |  |

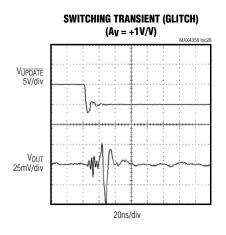

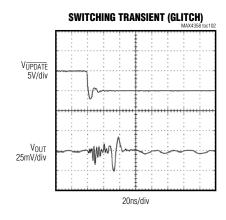

| Switching Transient                      |                     | $A_V = +1V/V$       |                 | 5      | 0        | mV                |  |  |

| (Glitch) (Note 3)                        |                     | $A_V = +2V/V$       |                 | 5      | 0        | IIIV              |  |  |

| AC Power-Supply                          |                     | f = 100kHz          |                 | 7      | 0        | dB                |  |  |

| Rejection Ratio                          |                     | f = 1MHz            | f = 1MHz        |        | 8        | l ub              |  |  |

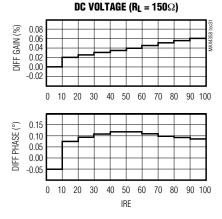

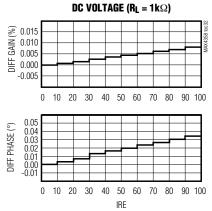

| Differential Gain                        |                     | $R_L = 1k\Omega$    |                 | 0.0    | 01       | - %               |  |  |

| Error (Note 4)                           |                     | $R_L = 150\Omega$   |                 | 0.0    | 05       | 70                |  |  |

| Differential Phase                       |                     | $R_L = 1k\Omega$    |                 | 0.0    | 03       | degrees           |  |  |

| Error (Note 4)                           |                     | $R_L = 150\Omega$   |                 | 0.     | 1        | degrees           |  |  |

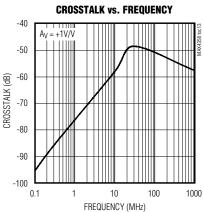

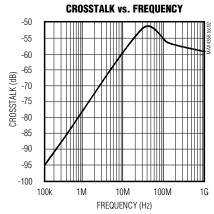

| Crosstalk, All Hostile                   |                     | f = 6MHz            |                 | -6     | 2        | dB                |  |  |

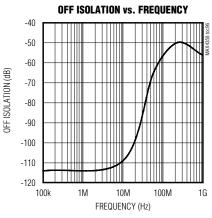

| Off-Isolation, Input-to-Output           |                     | f = 6MHz            |                 | -1     | 10       | dB                |  |  |

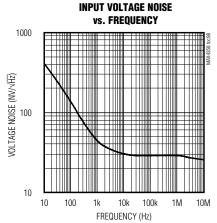

| Input Noise Voltage Density              | e <sub>n</sub>      | BW = 6MHz           |                 | 7      | 3        | μV <sub>RMS</sub> |  |  |

| Input Capacitance                        | CIN                 |                     |                 | 5      | <u> </u> | pF                |  |  |

| Disabled Output Capacitance              |                     | Amplifier in disabl | e mode          | 3      | 3        | рF                |  |  |

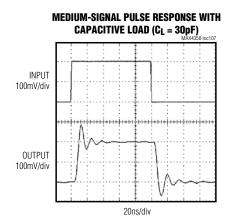

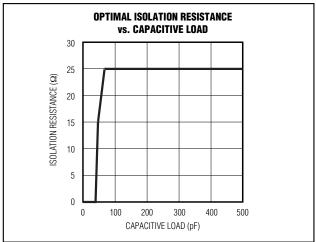

| Capacitive Load at 3dB<br>Output Peaking |                     |                     |                 | 3      | 0        | рF                |  |  |

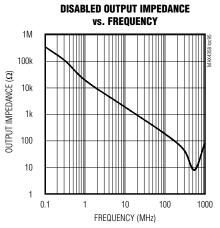

| Output Impadance                         | 70117               | f = 6MHz            | Output enabled  | 3      | 3        |                   |  |  |

| Output Impedance                         | Zout                | I = OIVIMZ          | Output disabled | 4      | k        | Ω                 |  |  |

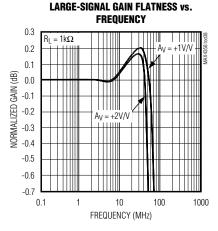

#### AC ELECTRICAL CHARACTERISTICS—DUAL SUPPLIES ±3V

$(V_{CC} = +3V, V_{EE} = -3V, V_{DD} = +3V, AGND = DGND = 0, V_{IN} = V_{OSDFILL} = 0, R_L = 150\Omega$  to AGND,  $A_V = +1V/V$ , and  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER          | SYMBOL                  | COI                      | CONDITIONS    |  | TYP | MAX | UNITS   |  |

|--------------------|-------------------------|--------------------------|---------------|--|-----|-----|---------|--|

| Small-Signal       | BWss                    | V <sub>OUT_</sub> =      | $A_V = +1V/V$ |  | 90  |     | MHz     |  |

| -3dB Bandwidth     | DW55                    | 20mVp-p                  | $A_V = +2V/V$ |  | 65  |     | IVII IZ |  |

| Medium-Signal      | D\\\.                   | V <sub>OUT</sub> =       | $A_V = +1V/V$ |  | 90  |     | MHz     |  |

| -3dB Bandwidth     | BW <sub>MS</sub>        | 200mVp-p                 | $A_V = +2V/V$ |  | 65  |     | IVIHZ   |  |

| Large-Signal -3dB  | BWLs                    | Vour - 2\/p p            | $A_V = +1V/V$ |  | 30  |     | MHz     |  |

| Bandwidth          | DVVLS                   | $V_{OUT_{-}} = 2V_{p-p}$ | $A_V = +2V/V$ |  | 35  |     | IVIIIZ  |  |

| Small-Signal       | D\\\/                   | V <sub>OUT</sub> _ =     | $A_V = +1V/V$ |  | 15  |     | MHz     |  |

| 0.1dB Bandwidth    | BW <sub>0.1dB</sub> -SS | 20mVp-p                  | $A_V = +2V/V$ |  | 15  |     | IVI□Z   |  |

| Medium-Signal      | DW                      | V <sub>OUT</sub> =       | $A_V = +1V/V$ |  | 15  |     | MHz     |  |

| 0.1dB Bandwidth    | BW <sub>0.1dB-MS</sub>  | 200mVp-p                 | $A_V = +2V/V$ |  | 15  |     | IVI□Z   |  |

| Large-Signal 0.1dB | arge-Signal 0.1dB       |                          | $A_V = +1V/V$ |  | 12  |     | MHz     |  |

| Bandwidth          | BW <sub>0.1dB-LS</sub>  | $V_{OUT_{-}} = 2V_{p-p}$ | $A_V = +2V/V$ |  | 12  |     | IVI⊟Z   |  |

N/XI/N/

#### AC ELECTRICAL CHARACTERISTICS—DUAL SUPPLIES ±3V (continued)

$(V_{CC} = +3V, V_{EE} = -3V, V_{DD} = +3V, AGND = DGND = 0, V_{IN} = V_{OSDFILL} = 0, R_L = 150\Omega$  to AGND, Av = +1V/V, and T<sub>A</sub> = +25°C, unless otherwise noted.)

| PARAMETER                             | SYMBOL   | C                                                   | CONDITIONS    |     | TYP     | MAX | UNITS             |  |

|---------------------------------------|----------|-----------------------------------------------------|---------------|-----|---------|-----|-------------------|--|

| Slew Rate                             | SR       | $V_{OUT_{-}} = 2V \text{ ste}$<br>$A_{V} = +1V/V$   | р             |     | 120     |     | - V/ue            |  |

| Siew Hate                             | SH       | V <sub>OUT</sub> = 2V ste<br>A <sub>V</sub> = +2V/V | р             |     | 120     |     | V/μs              |  |

| Cattling Time                         | to 0.404 | \\\ \( \) = 0 to 2\\\ \( \) oto                     | $A_V = +1V/V$ |     | 60      |     | 200               |  |

| Settling Time                         | ts 0.1%  | $V_0 = 0$ to 2V ste                                 | $A_V = +2V/V$ |     | 60      |     | ns                |  |

| Switching Transient                   |          |                                                     | $A_V = +1V/V$ |     | 15      |     | mV                |  |

| (Glitch) (Note 3)                     |          |                                                     | $A_V = +2V/V$ |     | 20      |     | mv                |  |

| AC Power-Supply                       |          | f = 100kHz                                          |               |     | 60      |     | ٩D                |  |

| Rejection Ratio                       |          | f = 1MHz                                            | = 1MHz 40     |     |         | dB  |                   |  |

| Differential Gain Error               |          | $R_L = 1k\Omega$                                    |               |     | 0.03    |     | %                 |  |

| (Note 4)                              |          | $R_L = 150\Omega$                                   |               | 0.2 |         |     |                   |  |

| Differential Phase                    |          | $R_L = 1k\Omega$                                    |               |     | 0.08    |     | -1                |  |

| Error (Note 4)                        |          | $R_{L} = 150\Omega \qquad 0.2$                      |               |     | degrees |     |                   |  |

| Crosstalk, All Hostile                |          | f = 6MHz                                            |               |     | -63     |     | dB                |  |

| Off-Isolation, Input to Output        |          | f = 6MHz                                            |               |     | -112    |     | dB                |  |

| Input Noise Voltage Density           | en       | BW = 6MHz                                           |               |     | 73      |     | μV <sub>RMS</sub> |  |

| Input Capacitance                     | CIN      |                                                     |               |     | 5       |     | рF                |  |

| Disabled Output Capacitance           |          | Amplifier in disa                                   | able mode     |     | 3       |     | рF                |  |

| Capacitive Load at 3dB Output Peaking |          |                                                     |               |     | 30      |     | pF                |  |

| Outrout loop a day as                 | 7        | f = Outp                                            | put enabled   |     | 3       |     |                   |  |

| Output Impedance                      | Zout     | 6MHz Out                                            | out disabled  |     | 4k      |     | Ω                 |  |

### **AC ELECTRICAL CHARACTERISTICS—SINGLE SUPPLY +5V**

$(V_{CC} = +5V, V_{EE} = 0, V_{DD} = +5V, AGND = DGND = 0, V_{IN} = V_{OSDFILL} = 1.75V, R_L = 150\Omega$  to AGND,  $A_V = +1V/V$ , and  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                             | SYMBOL                  |                           | CONDITIONS                  | MIN | TYP  | MAX | UNITS             |

|---------------------------------------|-------------------------|---------------------------|-----------------------------|-----|------|-----|-------------------|

| Small-Signal<br>-3dB Bandwidth        | BW <sub>SS</sub>        | V <sub>OUT</sub> _ = 20r  | V <sub>OUT</sub> _= 20mVp-p |     |      |     | MHz               |

| Medium-Signal -3dB<br>Bandwidth       | BW <sub>MS</sub>        | V <sub>OUT</sub> = 200r   | nVp-p                       |     | 90   |     | MHz               |

| Large-Signal<br>-3dB Bandwidth        | BW <sub>LS</sub>        | V <sub>OUT</sub> = 1.5\   | /p-p                        |     | 38   |     | MHz               |

| Small-Signal<br>0.1dB Bandwidth       | BW <sub>0.1dB</sub> -SS | V <sub>OUT</sub> = 20m    | Vp-p                        |     | 12   |     | MHz               |

| Medium-Signal<br>0.1dB Bandwidth      | BW <sub>0.1dB-MS</sub>  | V <sub>OUT</sub> _ = 200  | mVp-p                       |     | 12   |     | MHz               |

| Large-Signal<br>0.1dB Bandwidth       | BW <sub>0.1dB-LS</sub>  | V <sub>OUT</sub> _ = 1.5\ | √p-p                        |     | 12   |     | MHz               |

| Slew Rate                             | SR                      | V <sub>OUT</sub> = 2V s   | step, $A_V = +1V/V$         |     | 100  |     | V/µs              |

| Settling Time                         | ts 0.1%                 | V <sub>OUT</sub> _ = 0 to | o 2V step                   |     | 60   |     | ns                |

| Switching Transient (Glitch)          |                         |                           |                             |     | 25   |     | mV                |

| AC Power-Supply                       |                         | f = 100kHz                |                             |     | 70   |     | dB                |

| Rejection Ratio                       |                         | f = 1MHz                  |                             |     | 69   |     | ив                |

| Differential Gain Error               |                         | $R_L = 1k\Omega$          |                             |     | 0.03 |     | %                 |

| (Note 4)                              |                         | $R_L = 150\Omega$         |                             |     | 0.15 |     | ,0                |

| Differential Phase                    |                         | $R_L = 1k\Omega$          |                             |     | 0.06 |     | degrees           |

| Error (Note 4)                        |                         | $R_L = 150\Omega$         |                             |     | 0.2  |     | Ŭ                 |

| Crosstalk, All Hostile                |                         | f = 6MHz                  |                             |     | -63  |     | dB                |

| Off-Isolation, Input-to-<br>Output    |                         | f = 6MHz                  |                             |     | -110 |     | dB                |

| Input Noise Voltage                   | en                      | BW = 6MHz                 |                             |     | 73   |     | μV <sub>RMS</sub> |

| Input Capacitance                     | C <sub>IN</sub> _       |                           |                             |     | 5    |     | рF                |

| Disabled Output<br>Capacitance        |                         | Amplifier in disable mode |                             |     | 3    |     | рF                |

| Capacitive Load at 3dB Output Peaking |                         |                           |                             |     | 30   |     | рF                |

| Output                                | 70.17                   | f = 6MHz                  | f Output enabled            |     |      | 3   |                   |

| Impedance                             | Zout                    | i = bivimZ                |                             | 4k  |      |     |                   |

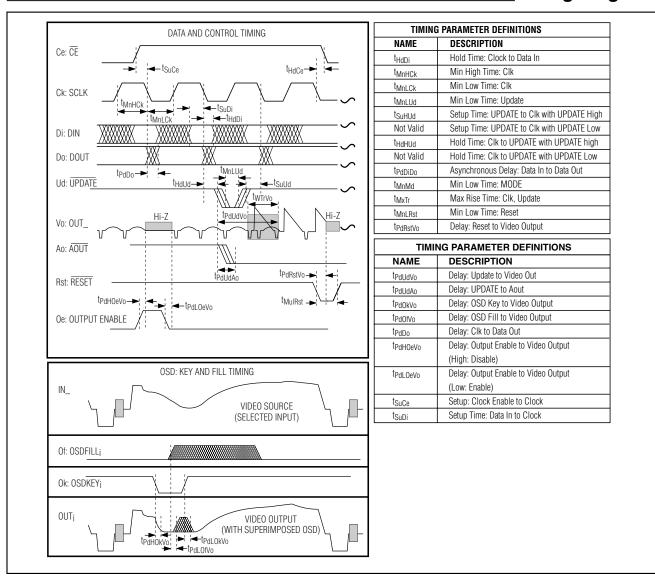

#### **SWITCHING CHARACTERISTICS**

$((V_{CC} - V_{EE}) = +4.5V \text{ to } +10.5V, V_{DD} = +2.7V \text{ to } +5.5V, DGND = AGND = 0, V_{IN} = V_{OSDFILL} = 0 \text{ for dual supplies, } V_{IN} = V_{OSDFILL} = +1.75V \text{ for single supply, } R_L = 150\Omega \text{ to } AGND, C_L = 100pF, A_V = +1V/V, and T_A = T_{MIN} - T_{MAX}, unless otherwise noted. Typical values are at <math>T_A = +25^{\circ}C$ .

| PARAMETER                  | SYMBOL               | COND                                                                                                   | ITIONS                | MIN | TYP | MAX | UNITS |

|----------------------------|----------------------|--------------------------------------------------------------------------------------------------------|-----------------------|-----|-----|-----|-------|

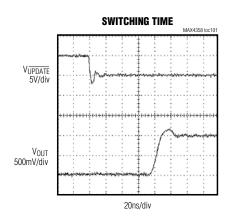

| Delay: UPDATE to Video Out | tPdUdVo              | V <sub>IN</sub> = 0.5V step                                                                            |                       |     | 200 | 450 | ns    |

| Delay: UPDATE to AOUT      | tPdUdAo              | $\frac{\text{MODE} = 0, \text{ time to } \overline{\text{A0}}}{\overline{\text{UPDATE}} = \text{low}}$ | OUT = low after       |     | 30  | 200 | ns    |

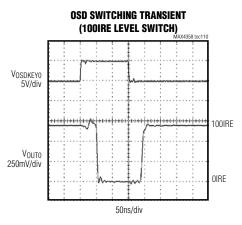

| Delay: OSDKEY to Output    | tPdOkVo/             | V <sub>OUT</sub> = 0.5V step                                                                           | $V_{DD} = +5V$        |     | 40  |     | ne    |

| Delay: OSDRET_ to Output   | tPdOfVo              | VOUT = 0.5V Step                                                                                       | $V_{DD} = +3V$        |     | 60  |     | ns    |

| Delay: SCLK to DOUT Valid  | tPdDo                | Logic state change in SCLK edge                                                                        | n DOUT on active      |     | 30  | 200 | ns    |

| Delay: Output Disable      | t <sub>PdHOeVo</sub> | $V_{OUT} = 0.5V$ , $1k\Omega$ pu                                                                       | ılldown to AGND       |     | 300 | 800 | ns    |

| Delay: Output Enable       | tPdLOeVo             | Output disabled, $1k\Omega$ pulldown to AGND, $V_{IN} = 0.5V$                                          |                       |     | 200 | 800 | ns    |

| Setup: CE to SCLK          | tSuCe                |                                                                                                        |                       |     |     | 100 | ns    |

| Setup: DIN to SCLK         | tSuDi                |                                                                                                        |                       | 100 |     |     | ns    |

| Hold Time: SCLK to DIN     | tHdDi                |                                                                                                        |                       | 100 |     |     | ns    |

| Minimum High Time: SCLK    | tMnHCk               |                                                                                                        |                       | 100 |     |     | ns    |

| Minimum Low Time: SCLK     | tMnLCk               |                                                                                                        |                       | 100 |     |     | ns    |

| Minimum Low Time: UPDATE   | tMnLUd               |                                                                                                        |                       | 100 |     |     | ns    |

| Setup Time: UPDATE to SCLK | tSuHUd               | Rising edge of UPDA SCLK                                                                               | TE to falling edge of | 100 |     |     | ns    |

| Hold Time: SCLK to UPDATE  | tHdHUd               | Falling edge of SCLK to falling edge of UPDATE                                                         |                       | 100 |     |     | ns    |

| Setup Time: MODE to SCLK   | tSuMd                | Minimum time from clock edge to MODE with valid data clocking                                          |                       | 100 |     |     | ns    |

| Hold Time: MODE to SCLK    | tHdMd                | Minimum time from clock edge to MODE with valid data clocking                                          |                       | 100 |     |     | ns    |

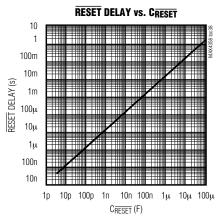

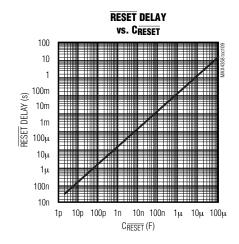

| Minimum Low Time: RESET    | t <sub>MnLRst</sub>  |                                                                                                        |                       |     |     | 300 | ns    |

| Delay: RESET               | t <sub>PdRst</sub>   | 10kΩ pulldown to AGND                                                                                  |                       |     |     | 600 | ns    |

- Note 1: Associated output voltage may be determined by multiplying the input voltage by the specified gain (Av) and adding output offset voltage. Gain is specified for IN\_ and OSDFILL\_ signal paths.

- Note 2: Logic level characteristics apply to the following pins: DIN, DOUT, SCLK,  $\overline{\text{CE}}$ ,  $\overline{\text{UPDATE}}$ ,  $\overline{\text{RESET}}$ , A3–A0, MODE,  $\overline{\text{AOUT}}$ , and OSDKEY\_.

- **Note 3:** Switching transient settling time is guaranteed by the settling time (ts) specification. Switching transient is a result of updating the switch matrix.

- Note 4: Input test signal: 3.58MHz sine wave of amplitude 40IRE superimposed on a linear ramp (0 to 100IRE). IRE is a unit of video-signal amplitude developed by the International Radio Engineers: 140IRE = 1.0V.

- Note 5: All devices are 100% production tested at +25°C. Specifications over temperature limits are guaranteed by design.

### Symbol Definitions

| SYMBOL | TYPE     | DESCRIPTION                             |

|--------|----------|-----------------------------------------|

| Ao     | Signal   | Address Valid Flag (AOUT)               |

| Ce     | Signal   | Clock Enable ( $\overline{\text{CE}}$ ) |

| Ck     | Signal   | Clock (SCLK)                            |

| Di     | Signal   | Serial Data In (DIN)                    |

| Do     | Signal   | Serial Data Output (DOUT)               |

| Md     | Signal   | MODE                                    |

| Oe     | Signal   | Output enable                           |

| Rst    | Signal   | Reset Input (RESET)                     |

| Ud     | Signal   | UPDATE                                  |

| Vo     | Signal   | Video Out (OUT)                         |

| н      | Property | High- or Low-to-High transition         |

| Hd     | Property | Hold                                    |

| L      | Property | Low- or High-to-Low transition          |

| Mn     | Property | Minimum                                 |

| Mx     | Property | Maximum                                 |

| Pd     | Property | Propagation delay                       |

| Su     | Property | Setup                                   |

| Tr     | Property | Transition                              |

| W      | Property | Width                                   |

#### **Naming Conventions:**

- All parameters with time units are given "t" designation, with appropriate subscript modifiers.

- Propagation delays for clocked signals are from active edge of clock.

- Propagation delay for level sensitive signals is from input to output at 50% point of a transition.

- Setup and Hold times are measured from 50% point of signal transition to 50% point of clocking signal transition.

- Setup time refers to any signal that must be stable before active clock edge, even if signal is not latched or clocked itself

- Hold time refers to any signal that must be stable during and after active clock edge, even if signal is not latched or clocked

- Propagation delays to unobservable internal signals are modified to setup and hold designations applied to observable IO signals.

MIXIM

### **Timing Diagram**

Figure 1. Timing Diagram

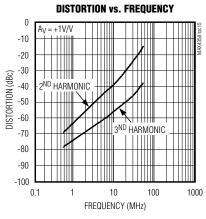

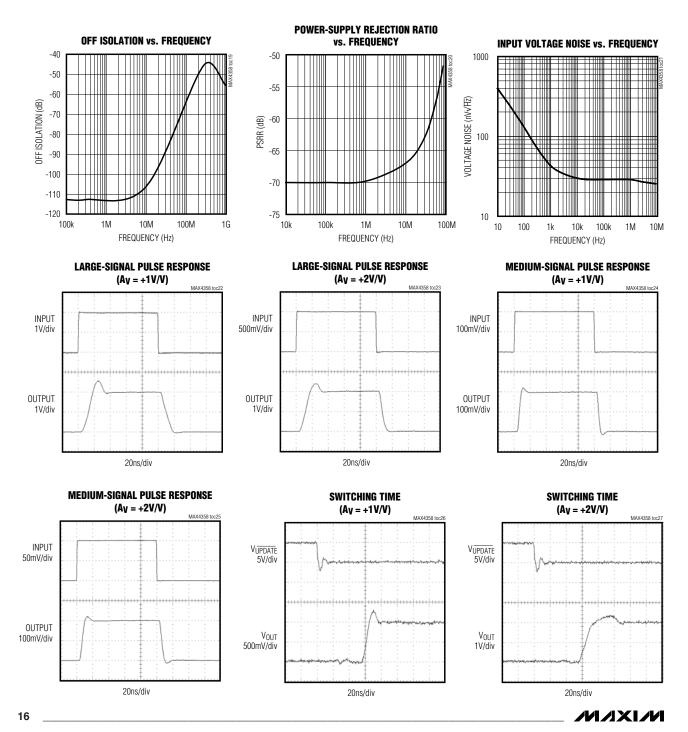

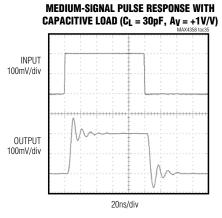

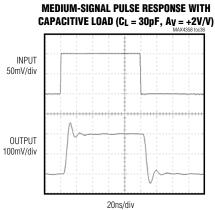

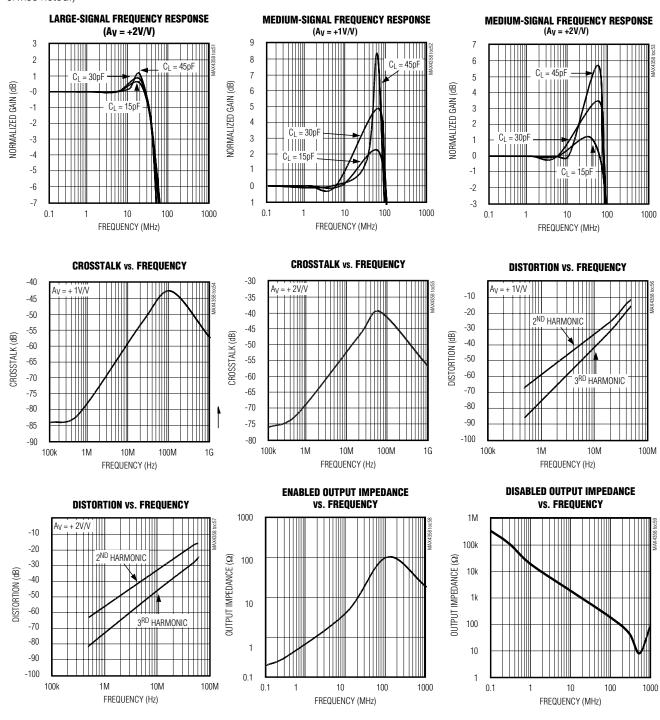

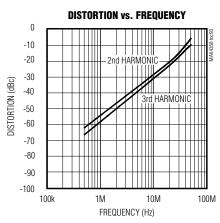

### Typical Operating Characteristics—Dual Supplies ±5V

$(V_{CC} = +5V \text{ and } V_{EE} = -5V, V_{DD} = +5V, AGND = DGND = 0, V_{IN} = 0, R_L = 150\Omega \text{ to AGND, } A_V = +1V/V, \text{ and } T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

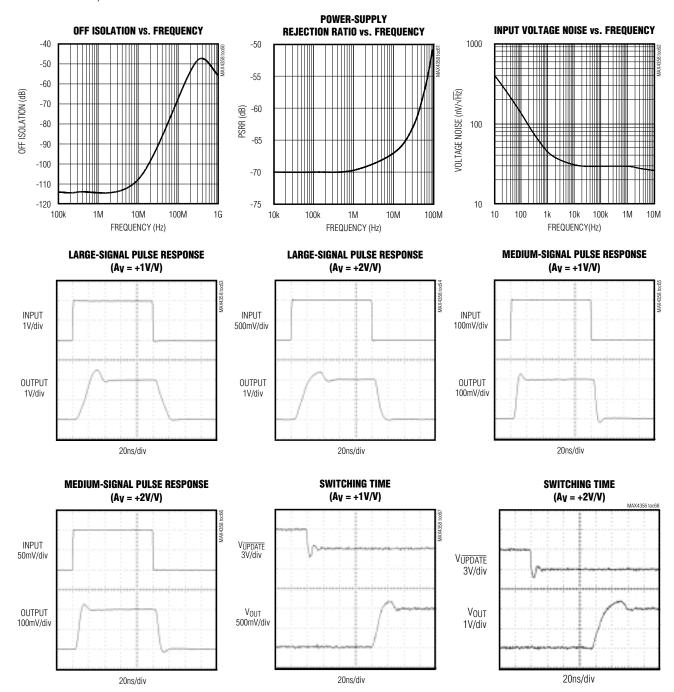

### Typical Operating Characteristics—Dual Supplies ±5V (continued)

$(V_{CC} = +5V \text{ and } V_{EE} = -5V, V_{DD} = +5V, AGND = DGND = 0, V_{IN} = 0, R_L = 150\Omega \text{ to AGND, } A_V = +1V/V, \text{ and } T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

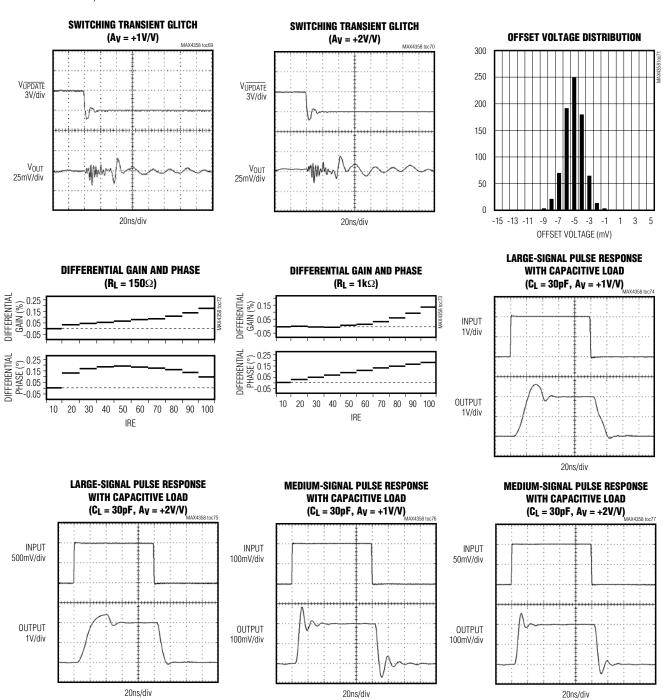

### \_Typical Operating Characteristics—Dual Supplies ±5V (continued)

$(V_{CC} = +5V \text{ and } V_{EE} = -5V, V_{DD} = +5V, AGND = DGND = 0, V_{IN} = 0, R_L = 150\Omega$  to AGND,  $A_V = +1V/V$ , and  $T_A = +25^{\circ}C$ , unless otherwise noted.)

### \_Typical Operating Characteristics—Dual Supplies ±5V (continued)

$(V_{CC} = +5V \text{ and } V_{EE} = -5V, V_{DD} = +5V, AGND = DGND = 0, V_{IN} = 0, R_L = 150\Omega \text{ to AGND, } A_V = +1V/V, \text{ and } T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

DIFFERENTIAL GAIN AND PHASE vs.

DIFFERENTIAL GAIN AND PHASE vs.

/VI/IXI/VI

### \_Typical Operating Characteristics—Dual Supplies ±5V (continued)

$(V_{CC} = +5V \text{ and } V_{EE} = -5V, V_{DD} = +5V, AGND = DGND = 0, V_{IN} = 0, R_L = 150\Omega \text{ to AGND, } A_V = +1V/V, \text{ and } T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

18 \_\_\_\_\_\_ **//**|**/**|**/**|

### \_Typical Operating Characteristics—Dual Supplies ±3V

$(V_{CC} = +3V \text{ and } V_{EE} = -3V, V_{DD} = +3V, AGND = DGND = 0, V_{IN} = 0, R_L = 150\Omega \text{ to AGND, } A_V = +1V/V, \text{ and } T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

### Typical Operating Characteristics—Dual Supplies ±3V (continued)

$(V_{CC} = +3V \text{ and } V_{EE} = -3V, V_{DD} = +3V, AGND = DGND = 0, V_{IN} = 0, R_L = 150\Omega \text{ to AGND, } A_V = +1V/V, \text{ and } T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

### \_Typical Operating Characteristics—Dual Supplies ±3V (continued)

$(V_{CC} = +3V \text{ and } V_{EE} = -3V, V_{DD} = +3V, AGND = DGND = 0, V_{IN} = 0, R_L = 150\Omega \text{ to AGND, } A_V = +1V/V, \text{ and } T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

22

# 32 x 16 Nonblocking Video Crosspoint Switch with On-Screen Display Insertion and I/O Buffers

### \_Typical Operating Characteristics—Dual Supplies ±3V (continued)

$(V_{CC} = +3V \text{ and } V_{EE} = -3V, V_{DD} = +3V, AGND = DGND = 0, V_{IN} = 0, R_L = 150\Omega \text{ to AGND, } A_V = +1V/V, \text{ and } T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

### \_Typical Operating Characteristics—Dual Supplies ±3V (continued)

$(V_{CC} = +3V \text{ and } V_{EE} = -3V, V_{DD} = +3V, AGND = DGND = 0, V_{IN} = 0, R_L = 150\Omega \text{ to AGND, } A_V = +1V/V, \text{ and } T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

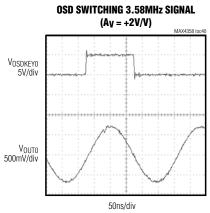

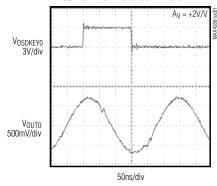

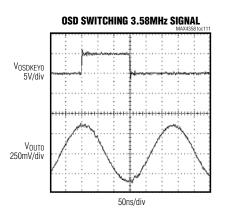

#### **OSD SWITCHING 3.58MHz SIGNAL**

### Typical Operating Characteristics—Single Supply +5V

$(V_{CC} = +5V \text{ and } V_{EE} = 0, V_{DD} = +5V, AGND = DGND = 0, V_{IN} = 0, R_L = 150\Omega \text{ to AGND, } A_V = +1V/V, \text{ and } T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

### Typical Operating Characteristics—Single Supply +5V (continued)

$(V_{CC} = +5V \text{ and } V_{EE} = 0, V_{DD} = +5V, AGND = DGND = 0, V_{IN} = 0, R_L = 150\Omega \text{ to AGND, } A_V = +1V/V, \text{ and } T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

### \_Typical Operating Characteristics—Single Supply +5V (continued)

$(V_{CC} = +5V \text{ and } V_{EE} = 0, V_{DD} = +5V, AGND = DGND = 0, V_{IN} = 0, R_L = 150\Omega \text{ to AGND, } A_V = +1V/V, \text{ and } T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

MIXIM

### \_Typical Operating Characteristics—Single Supply +5V (continued)

$(V_{CC} = +5V \text{ and } V_{EE} = 0, V_{DD} = +5V, AGND = DGND = 0, V_{IN} = 0, R_L = 150\Omega \text{ to AGND, } A_V = +1V/V, \text{ and } T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

### **Pin Description**

| PIN                                                                                                                                         | NAME                   | FUNCTION                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3, 5, 7, 9, 11, 13, 15, 17, 19,<br>21, 23, 25, 27, 29, 31, 33, 35, 37,<br>39, 41, 43, 45, 127, 129, 131,<br>133, 135, 137, 139, 141, 143 | INO-IN31               | Buffered Analog Inputs                                                                                                                                                                                                                                               |

| 2, 4, 6, 8, 10, 12, 14, 16, 18, 20, 22, 24, 26, 28, 30, 32, 34, 72, 73, 107, 108, 109, 126, 128, 130, 132, 134, 136, 138, 140, 142          | AGND                   | Analog Ground                                                                                                                                                                                                                                                        |

| 36, 74, 78, 82, 86, 90, 94, 98,<br>102, 106                                                                                                 | Vcc                    | Positive Analog Supply. Bypass each pin with a 0.1µF capacitor to AGND. Connect a single 10µF capacitor from one V <sub>CC</sub> pin to AGND.                                                                                                                        |

| 38, 40, 42, 44                                                                                                                              | A3-A0                  | Address Programming Inputs. Connect to DGND or $V_{DD}$ to select the address for individual output address mode. See Table 4.                                                                                                                                       |

| 46                                                                                                                                          | DGND                   | Digital Ground                                                                                                                                                                                                                                                       |

| 47                                                                                                                                          | AOUT                   | Address Recognition Output. AOUT drives low after successful chip address recognition.                                                                                                                                                                               |

| 48                                                                                                                                          | MODE                   | Serial Interface Mode Select Input. Drive high for Complete Matrix Mode (Mode 1), or drive low for Individual Output Address Mode (Mode 0).                                                                                                                          |

| 49                                                                                                                                          | DIN                    | Serial Data Input. Data is clocked-in on the falling edge of SCLK.                                                                                                                                                                                                   |

| 50                                                                                                                                          | SCLK                   | Serial Clock Input                                                                                                                                                                                                                                                   |

| 51                                                                                                                                          | UPDATE                 | Update Input. Drive UPDATE low to transfer data from Mode Registers to the switch matrix.                                                                                                                                                                            |

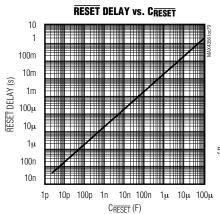

| 52                                                                                                                                          | RESET                  | Asynchronous Reset Input/Output. Drive RESET low to initiate hardware reset. All analog outputs are disabled. Additional power-on reset delay may be set by connecting a small capacitor from RESET to DGND.                                                         |

| 53                                                                                                                                          | CE                     | Clock Enable Input. Drive low to enable the serial data interface.                                                                                                                                                                                                   |

| 54                                                                                                                                          | DOUT                   | Serial Data Output. In Complete Matrix Mode, data is clocked through the 112-bit Matrix Control shift register. In Individual Output Address Mode, data at DIN passes directly to DOUT.                                                                              |

| 55–70                                                                                                                                       | OSDKEY0-<br>OSDKEY15   | Digital Control Input. Control for the fast 2:1 OSD Insertion multiplexer routing signal to output buffers. A logic high routes programmed IN_ analog input signal to output buffer. A logic low routes the dedicated OSDFILL_ input to corresponding output buffer. |

| 71                                                                                                                                          | $V_{\mathrm{DD}}$      | Digital Logic Supply. Bypass V <sub>DD</sub> with a 0.1µF capacitor to DGND.                                                                                                                                                                                         |

| 75, 77, 79, 81, 83, 85, 87, 89, 91, 93, 95, 97, 99, 101, 103, 105                                                                           | OUT0-<br>OUT15         | Buffered Analog Outputs. Gain is individually programmable for $A_V = +1V/V$ or $A_V = +2V/V$ via the serial interface. Outputs may be individually disabled (high impedance). On power-up, or assertion of $\overline{\text{RESET}}$ , all outputs are disabled.    |

| 76, 80, 84, 88, 92, 96, 100, 104,<br>144                                                                                                    | V <sub>EE</sub>        | Negative Analog Supply. Bypass each pin with a 0.1µF capacitor to AGND. Connect a single 10µF capacitor from one VEE pin to AGND.                                                                                                                                    |

| 110, 111, 112, 113, 114, 115,<br>116, 117, 118, 119, 120, 121,<br>122, 123, 124, 125                                                        | OSDFILL15<br>-OSDFILL0 | Dedicated OSD Analog Signal Buffered Inputs. For each output buffer amplifier. $OSDFILL_i$ input signal is routed to output buffer amplifier $OUT_i$ when the corresponding $OSDKEY_i$ is low.                                                                       |

MIXIM

#### **Functional Diagram**

#### **Detailed Description**

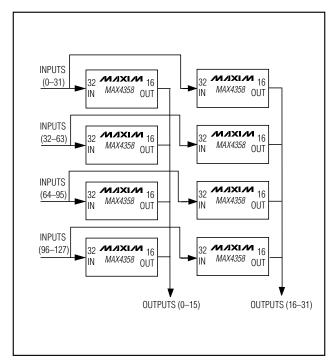

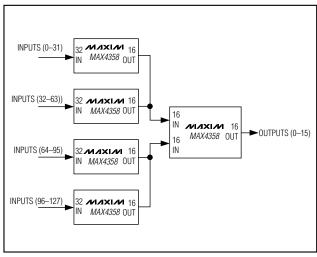

The MAX4358 is a highly integrated 32  $\times$  16 nonblocking video crosspoint switch matrix . All inputs and outputs are buffered, with all outputs able to drive standard 75 $\Omega$  reverse-terminated video loads.

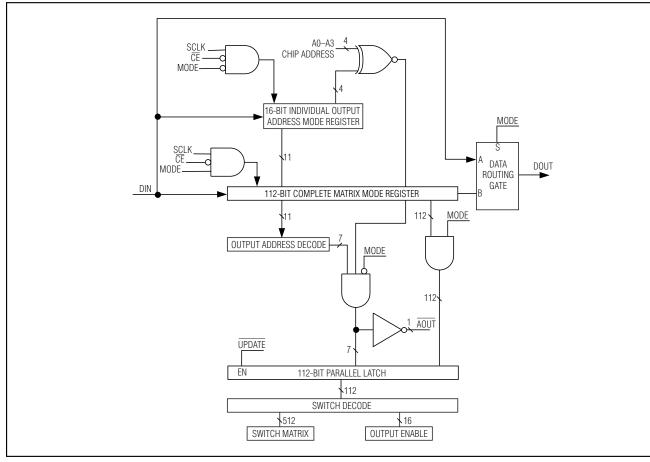

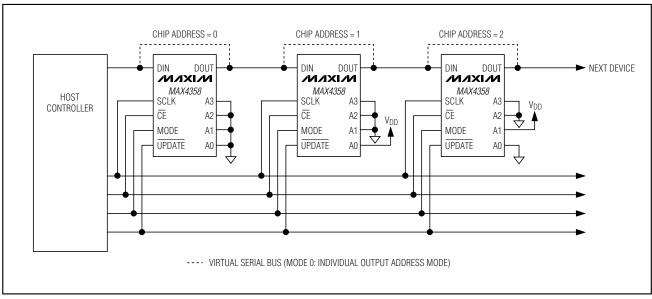

A three-wire interface programs the switch matrix and initializes with a single update signal. The unique serial interface operates in one of two modes, Complete Matrix Mode (Mode 1) or Individual Output Address Mode (Mode 0).

The signal path of the MAX4358 is from the buffered inputs (IN0-IN31), through the switching matrix, buffered by the output amplifiers, and presented at the outputs (OUT0-OUT15) (Functional Diagram). The other functional blocks are the serial interface and control logic. Each of the functional blocks is described in detail below.

#### **Analog Outputs**

The MAX4358 outputs are high-speed amplifiers capable of driving  $150\Omega$  ( $75\Omega$  back-terminated) loads. The gain,  $A_V = +1V/V$  or +2V/V, is selectable via programming bit 5 of the serial control word. Amplifier compensation is automatically optimized to maximize the bandwidth for each gain selection. Each output can be individually enabled and disabled via bit 6 of the serial control word. When disabled, the output is high impedance presenting typically  $4k\Omega$  load, and 3pF output capacitance, allowing multiple outputs to be connected together for building large arrays. On power-up (or asynchronous RESET) all outputs are initialized in the disabled state to avoid output conflicts in large array configurations. The programming and operation of the MAX4358 is output referred. Outputs are configured individually to connect to any one of the 32 analog inputs, programmed to the desired gain ( $A_V = +1V/V$  or +2V/V), and enabled or disabled in a high-impedance

#### **Table 1. Operation Truth Table**

| CE | UPDATE | SCLK     | DIN | DOUT   | MODE | AOUT | RESET | OPERATION/COMMENTS                                                                                                                                                                                                                 |

|----|--------|----------|-----|--------|------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | Х      | Х        | Χ   | Х      | Х    | Х    | 1     | No change in logic                                                                                                                                                                                                                 |

| 0  | 1      | <b>\</b> | Di  | Di-112 | 1    | 1    | 1     | Data at DIN is clocked on<br>negative edge of SCLK into 112-<br>bit Complete Matrix Mode<br>register. DOUT supplies original<br>data in 112 SCLK pulses later.                                                                     |

| 0  | 0      | X        | X   | X      | 1    | 1    | 1     | Data in serial 112-bit Complete<br>Matrix Mode register is<br>transferred into parallel latches<br>which control the switching<br>matrix.                                                                                          |

| 0  | 1      | ↓        | Di  | Di     | 0    | 1    | 1     | Data at DIN is routed to Individual Output Address Mode shift register. DIN is also connected directly to DOUT so that all devices on the serial bus may be addressed in parallel.                                                 |

| 0  | 0      | X        | Di  | Di     | 0    | 0    | 1     | 4-bit chip address A3–A0 is compared to D14–D11. If equal, remaining 11 bits in Individual Output Address Mode Register are decoded, allowing reprogramming for a single output. AOUT signals successful individual matrix update. |

| Х  | Х      | Х        | Х   | Х      | Х    | Х    | 0     | Asynchronous reset. All outputs are disabled. Other logic remains unchanged.                                                                                                                                                       |

Note: "X" = Don't Care

#### **Analog Inputs**

The MAX4358 offers 32 analog input channels. Each input is buffered before the crosspoint matrix switch, allowing one input to cross-connect up to 16 outputs. The input buffers are voltage feedback amplifiers with high-input impedance and low input bias current. This allows the use of very simple input clamp circuits.

#### **OSDFILL and OSDKEY Inputs**

Intended for on-screen display insertion, the 16 OSD-FILL inputs are buffered analog signal inputs that are routed to a dedicated output buffer through a fast 2:1 MUX. The signal presented to the output buffer is selected from the programmed analog input signal (IN\_) and the dedicated OSDFILL input signal.

#### **Switch Matrix**

The MAX4358 has 512 individual T-switches making a  $32 \times 16$  switch matrix. The switching matrix is 100% nonblocking, which means that any input may be routed to any output. The switch matrix programming is output-referred. Each output may be connected to any one of the 32 analog inputs. Any one input can be routed to all 16 outputs with no signal degradation.

#### Digital Interface

The digital interface consists of the following pins: DIN, DOUT, SCLK, AOUT, UPDATE, CE, A3–A0, MODE, and RESET. DIN is the serial-data input, DOUT is the serial-data output.

Figure 2. Serial Interface Block Diagram

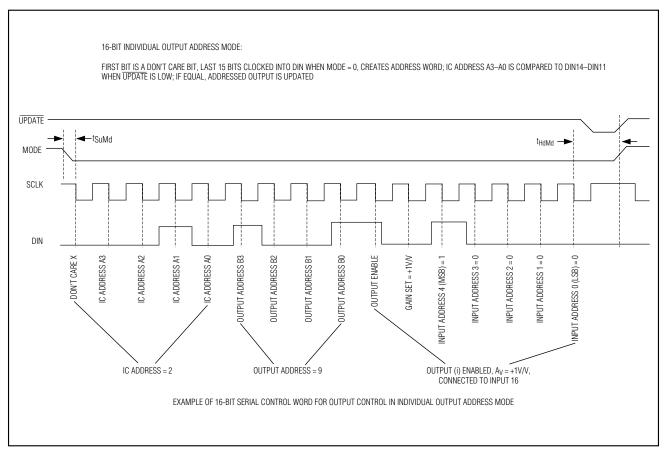

SCLK is the serial-data clock which clocks data into the data input registers (Figure 3). Data at DIN is loaded in at each falling edge of SCLK. DOUT is the data shifted out of the 112-bit Complete Matrix Mode register (Mode = 1). DIN passes directly to DOUT when in Individual Output Address Mode (Mode = 0).

The falling edge of UPDATE latches the data and programs the matrix. When using Individual Output Address Mode, the address recognition output AOUT drives low when control-word bits D14 to D11 match the address programming inputs (A3–A0) and UPDATE is low (Table 1). Table 1 is the operation truth table.

#### **Programming the Matrix**

The MAX4358 offers two programming modes: Individual Output Address Mode and Complete Matrix

Mode. These two distinct programming modes are selected by toggling a single MODE pin high or low. Both modes operate with the same physical board layout. This flexibility allows initial programming of the IC by daisy-chaining and sending one long data word while still being able to immediately address and update individual outputs in the matrix.

#### Individual Output Address Mode (MODE = 0)

Drive MODE to logic low to select Mode 0. Individual outputs are programmed via the serial interface with a single 16-bit control word. The control word consists of a don't care MSB, the chip address bits, output address bits, an output enable/disable bit, an output gain-set bit, and input address bits (Table 2 through Table 6, and Figure 2).

### Table 2. 16-Bit Serial Control Word Bit Assignments (Mode 0: Individual Output Address Mode)

| BIT      | NAME              | FUNCTION                                                             |

|----------|-------------------|----------------------------------------------------------------------|

| 15 (MSB) | X                 | Don't Care                                                           |

| 14       | IC Address A3     | MSB of selected chip address                                         |

| 13       | IC Address A2     |                                                                      |

| 12       | IC Address A1     |                                                                      |

| 11       | IC Address A0     | LSB of selected chip address                                         |

| 10       | Output Address B3 | MSB of output buffer address                                         |

| 9        | Output Address B2 |                                                                      |

| 8        | Output Address B1 |                                                                      |

| 7        | Output Address B0 | LSB of output buffer address                                         |

| 6        | Output Enable     | Enable bit for output, 0 = disable, 1 = enable.                      |

| 5        | Gain Set          | Gain Select for output buffer, 0 = gain of +1V/V, 1 = gain of +2V/V. |

| 4        | Input Address 4   | MSB of input channel select address                                  |

| 3        | Input Address 3   |                                                                      |

| 2        | Input Address 2   |                                                                      |

| 1        | Input Address 1   |                                                                      |

| 0 (LSB)  | Input Address 0   | LSB of input channel select address                                  |