# **Excellent Integrated System Limited**

Stocking Distributor

Click to view price, real time Inventory, Delivery & Lifecycle Information:

Peregrine Semiconductor EK43602-01

For any questions, you can email us directly: <u>sales@integrated-circuit.com</u>

**Product Description**

lead QFN footprint.

**Distributor of Peregrine Semiconductor: Excellent Integrated System Limited** Datasheet of EK43602-01 - KIT EVAL FOR PE43602 RF DSA Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

The PE43602 is a HaRP<sup>™</sup>-enhanced, high linearity, 6-bit RF Digital Step Attenuator (DSA) covering a 31.5 dB

attenuation range in 0.5 dB steps. This Peregrine 50  $\Omega$  RF

frequency and temperature and exhibits very low insertion

loss and low power consumption. Performance does not

UltraCMOS<sup>™</sup> process, a patented variation of silicon-on-

offering the performance of GaAs with the economy and

insulator (SOI) technology on a sapphire substrate,

change with  $V_{DD}$  due to on-board regulator. This next generation Peregrine DSA is available in a 4x4 mm 24

The PE43602 is manufactured on Peregrine's

integration of conventional CMOS.

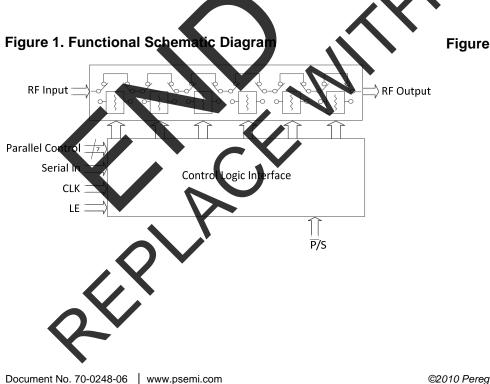

DSA provides both a serial and parallel CMOS control interface. It maintains high attenuation accuracy over

# Product Specification PE43602

#### 50 Ω RF Digital Attenuator 6-bit, 31.5 dB, 9 kHz - 5.0 GHz

#### Features

- HaRP<sup>™</sup>-enhanced UltraCMOS<sup>™</sup> device

- Attenuation: 0.5 dB steps to 31.5 dB

- High Linearity: Typical +58 dBm IIP3

- Excellent low-frequency performance

- 3.3 V or 5.0 V Power Supply Voltage

- Fast switch settling time

- Programming Modes:

- Direct Parallel

- Latched Parallel

- Serial

- High-attenuation state @ power-up (PUP)

- CMOS Compatible

- No DC hlocking capacitors required

- Cackaged in a 24-lead 4x4x0.85 mm QFN

Figure 2. Package Type 24-lead 4x4x0.85 mm QFN

PE43602 Product Specification

#### Table 1. Electrical Specifications @ +25°C, V<sub>DD</sub> = 3.3 V or 5.0 V

| Parameter              | Test Conditions                                                                                                   | Frequency                                       | Min   | Typical   | Max                                   | Units          |

|------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------|-----------|---------------------------------------|----------------|

| Frequency Range        |                                                                                                                   |                                                 | 9 kHz |           | 5 GHz                                 |                |

| Attenuation Range      | 0.5 dB Step                                                                                                       |                                                 |       | 0 – 31.5  |                                       | dB             |

| Insertion Loss         |                                                                                                                   | 9 kHz $\leq$ 5 GHz                              |       | 2.2       | 2.7                                   | dB             |

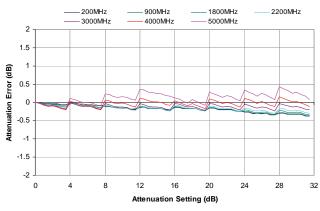

| Attenuation Error      | 0 dB - 31.5 dB Attenuation settings<br>0 dB - 31.5 dB Attenuation settings<br>0 dB - 31.5 dB Attenuation settings | 9 kHz < 4 GHz<br>4 GHz ≤ 5 GHz<br>4 GHz ≤ 5 GHz |       |           | ±(0.3 + 3)%<br>+0.4 + 5%<br>-0.3 - 3% | dB<br>dB<br>dB |

| Return Loss            |                                                                                                                   | 9 kHz - 5 GHz                                   |       | 18        |                                       | dB             |

| Relative Phase         | All States                                                                                                        | 9 kHz - 5 GHz                                   |       | 55        |                                       | deg            |

| P1dB (note 1)          | Input                                                                                                             | 20 MHz - 5 GHz                                  | 30    | <u>32</u> |                                       | dBm            |

| IIP3                   | Two tones at +18 dBm, 20 MHz spacing                                                                              | 20 MHz - 5 GHz                                  |       | 58        |                                       | dBm            |

| Typical Spurious Value |                                                                                                                   | 1 MHz                                           |       | -110      |                                       | dBm            |

| Video Feed Through     |                                                                                                                   |                                                 |       | 10        |                                       | mVpp           |

| Switching Time         | 50% DC CTRL to 10% / 90% RF                                                                                       |                                                 |       | 650       |                                       | ns             |

| RF Trise/Tfall         | 10% / 90% RF                                                                                                      |                                                 |       | 400       |                                       | ns             |

| Settling Time          | RF settled to within 0.05 dB of final value<br>RBW = 5 MHz, Averaging ON                                          |                                                 |       | 4         |                                       | μs             |

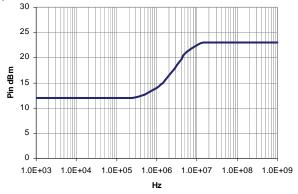

Note 1. Please note Maximum Operating Pin (50 Ω) of +23 dBm as shown in

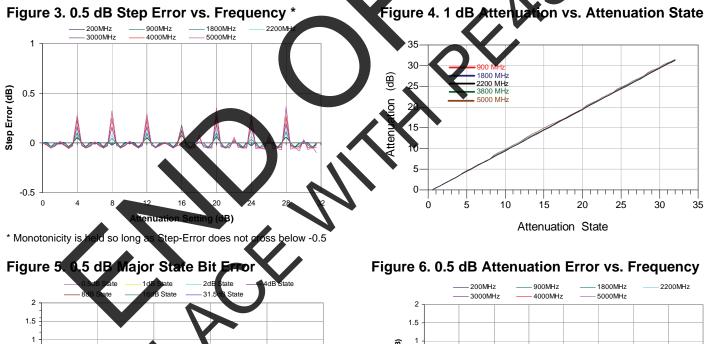

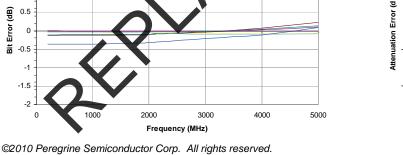

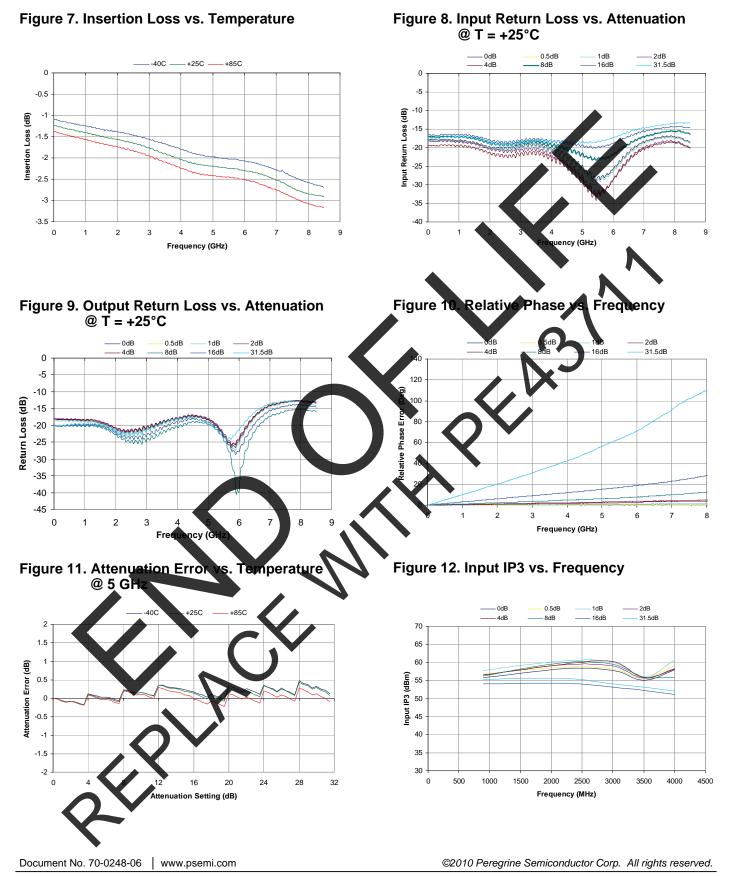

#### **Performance Plots**

Document No. 70-0248-06 UltraCMOS™ REIC Solutions

Bit Error (dB)

Logo updated under non-rev change. Peregrine products are protected under one or more of the following U.S. Patents: http://patents.psemi.com

PE43602 Product Specification

### PE43602

Product Specification

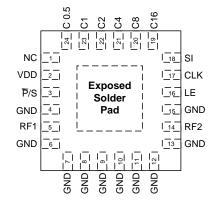

#### Figure 13. Pin Configuration (Top View)

#### **Table 2. Pin Descriptions**

| Pin No. | Pin Name        | Description                         |  |

|---------|-----------------|-------------------------------------|--|

| 1       | GND             | Ground                              |  |

| 2       | V <sub>DD</sub> | Power supply pin                    |  |

| 3       | ₽/S             | Serial/Parallel mode select         |  |

| 4       | GND             | Ground                              |  |

| 5       | RF1             | RF1 port                            |  |

| 6 - 13  | GND             | Ground                              |  |

| 14      | RF2             | RF2 port                            |  |

| 15      | GND             | Ground                              |  |

| 16      | LE              | Serial interface Latch Enable input |  |

| 17      | CLK             | Serial interface Clock input        |  |

| 18      | SI              | Serial interface Data input         |  |

| 19      | C16 (D6)        | Parallel control bit, 16 dB         |  |

| 20      | C8 (D5)         | Parallel control bit, 8 dB          |  |

| 21      | C4 (D4)         | Parallel control bit, 4 dB          |  |

| 22      | C2 (D3)         | Parallel control bit, 2 dB          |  |

| 23      | C1 (D2)         | Parallel control bit, 1 dB          |  |

| 24      | C0.5 (D1)       | Parallel control bit, 0.5 dB        |  |

| Paddle  | GND             | Ground for proper operation         |  |

Note: Ground C0.5, C1, C2, C4, C8, if no

#### Exposed Solder P ad Con

The exposed solder pad on the bottom of the package must be grounded for prope device operat

#### Moisture Sensitivity

The Moisture Ser Level rating fo the PE43602 in sitiv the 24-lead 4x4 QFN package is M.

#### Switching Frequency

The PE43602 has a max num 25 kHz switching rate. to be the speed at which the Switching rate is define DSA can be toggled across attenuation states.

#### Latch-Up A oidance

Unlike co entional CMOS devices, UltraCMOS™ devices are mmune to latch-up.

©2010 Peregrine Semiconductor Corp. All rights reserved.

Page 4 of 11

Logo updated under non-rev change. Peregrine products are protected under one or more of the following U.S. Patents: http://patents.psemi.com

#### **Table 3. Operating Ranges**

| Parameter                                                                             | Min | Тур | Max            | Units      |

|---------------------------------------------------------------------------------------|-----|-----|----------------|------------|

| V <sub>DD</sub> Power Supply Voltage                                                  | 3.0 | 3.3 |                | V          |

| V <sub>DD</sub> Power Supply Voltage                                                  |     | 5.0 | 5.5            | V          |

| I <sub>DD</sub> Power Supply Current                                                  |     | 70  | 350            | μA         |

| Digital Input High                                                                    | 2.6 |     | 5.5            | V          |

| P <sub>IN</sub> Input power (50 Ω):<br>9 kHz <i>≤</i> 20 MHz<br>20 MHz <i>≤</i> 5 GHz |     |     | Fig. 14<br>+23 | dBm<br>dBm |

| T <sub>OP</sub> Operating temperature range                                           | -40 | 25  | 85             | °C         |

| Digital Input Low                                                                     | 0   |     | 1              | V          |

| Digital Input Leakage <sup>1</sup>                                                    |     |     | 15             | μA         |

Note 1. Input leakage current c Control pin

#### Table 4. Absolute Maximum Ratings

| -                |                                                       | 9    |                |            |

|------------------|-------------------------------------------------------|------|----------------|------------|

| Symbol           | Parameter/Conditions                                  | Min  | Max            | Units      |

| V <sub>DD</sub>  | Power supply voltage                                  | -0.3 | 6.0            | V          |

| VI               | Voltage on any Digital input                          | -0.3 | 5.8            | V          |

| T <sub>ST</sub>  | Storage temperature range                             | -65  | 150            | °C         |

| Pin              | Input power (50 Ω)<br>SkHz ≤ 20 NHz<br>20 MHz ≤ 9 GHz |      | Fig. 14<br>+23 | dBm<br>dBm |

| V <sub>ESD</sub> | ESD voltage (HBN)/<br>ESD voltage (Machine Model)     |      | 500<br>100     | V<br>V     |

dy Model (HBM, MIL\_STD 883 Method 3015.7) 1. Huma

solute maximum ratings may cause Exceeding permanent damage. Operation should be restricted to its in the Operating Ranges table. Operation the lin etween operating range maximum and absolute imum for extended periods may reduce reliability. ma

#### igure 14. Maximum Power Handling Capability

#### **Electrostatic Discharge (ESD) Precautions**

When handling this UltraCMOS<sup>™</sup> device, observe the same precautions that you would use with other ESDsensitive devices. Although this device contains circuitry to protect it from damage due to ESD, precautions should be taken to avoid exceeding the specified rating.

Document No. 70-0248-06

UltraCMOS<sup>™</sup> RFIC Solutions

#### PE43602

**Product Specification**

**Table 5. Control Voltage**

#### **Table 8. Serial Attenuation Word Truth Table**

| Low<br>High<br>able 6. Latch and Cloc<br>Latch Enable Shift Clock<br>X î<br>X X | F                      | at 10 μA (typ)                                             | <b>D7</b> | D6     |            |          |        |          |        |             |

|---------------------------------------------------------------------------------|------------------------|------------------------------------------------------------|-----------|--------|------------|----------|--------|----------|--------|-------------|

| ble 6. Latch and Cloc<br>atch Enable Shift Clock                                | ck Specific            |                                                            |           |        | D5         | D4       | D3     | D2       | D1     | D0<br>(LSB) |

| atch Enable Shift Clock<br>X ↑                                                  | F                      | ations                                                     |           | L      | L          | L        | L      | L        | L      | L           |

| Atch Enable Shift Clock                                                         | F                      | ations                                                     | L         | L      | L          | L        | L      | L        |        | L           |

| X ↑                                                                             |                        |                                                            | L         | L      | L          | L        | L      | Н        | L      |             |

|                                                                                 |                        | Function                                                   | L         | L      | L          | L        | Н      |          | Ŀ      | L           |

| ↑ X                                                                             | Shift R                | egister Clocked                                            | L         | L      | L          | Н        |        | L        | K      | L           |

|                                                                                 | Content<br>transferred | s of shift register<br>I to attenuator core                | L         | L      | н          |          | L      |          | L      |             |

|                                                                                 |                        |                                                            | L         | H<br>H | L<br>H     | L        | H      | L<br>H   | L<br>H | L           |

| able 7. Parallel Truth                                                          | Table                  |                                                            |           | •      |            |          |        |          |        |             |

| Parallel Control Sett                                                           | ing                    | Attenuation                                                |           |        |            |          |        |          |        |             |

| D6 D5 D4 D3                                                                     | D2 D1                  | Setting<br>RF1-RF2                                         |           |        |            |          |        |          | 1      |             |

| L L L L                                                                         | L L                    | Reference I.L.                                             |           |        |            |          |        | <b>?</b> | ``     |             |

| L L L L                                                                         | L H                    | 0.5 dB                                                     |           | •      |            |          | N      |          |        |             |

| L L L L                                                                         | H L                    | 1 dB                                                       |           |        |            |          | V      | K.       |        |             |

| L L L H                                                                         | L L                    | 2 dB                                                       |           |        |            |          |        |          |        |             |

| L L H L                                                                         | LL                     | 4 dB                                                       |           |        | $\bigcirc$ |          |        |          |        |             |

| L H L L                                                                         | LL                     | 8 dB                                                       |           |        | V          |          |        |          |        |             |

| H L L L                                                                         | LL                     | 16 dB                                                      |           |        |            |          |        |          |        |             |

| н н н н                                                                         | НН                     | 31.5 dB                                                    |           |        |            |          |        |          |        |             |

| Able 9. Serial Register   ISB (last in)   Q7 Q6   Q7 Q6   D7 D6                 | <b>Q3</b>              | <b>COR</b> (first in<br><b>Q2 Q1 Q0</b><br><b>D2 D1 D0</b> |           | Bits   | must b     | e set to | ologic | low      |        |             |

Document No. 70-0248-06 | www.psemi.com

PE43602 Product Specification

#### **Programming Options**

#### Parallel/Serial Selection

Either a parallel or serial interface can be used to control the PE43602. The  $\overline{P}/S$  bit provides this selection, with  $\overline{P}/S=LOW$  selecting the parallel interface and  $\overline{P}/S=HIGH$  selecting the serial interface.

#### **Parallel Mode Interface**

The parallel interface consists of six CMOScompatible control lines that select the desired attenuation state, as shown in *Table 7*.

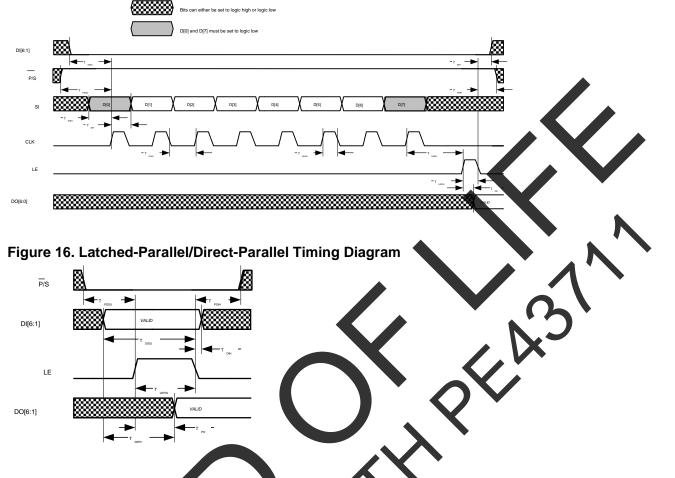

The parallel interface timing requirements are defined by *Fig. 16* (Parallel Interface Timing Diagram), *Table 11* (Parallel Interface AC Characteristics), and switching speed (*Table 1*).

For *latched*-parallel programming the Latch Enable (LE) should be held LOW while changing attenuation state control values, then pulse LE HIGH to LOW (*per Fig. 16*) to latch new attenuation state into device.

For *direct* parallel programming, the Latch Enable (LE) line should be pulled HIGH. Changing attenuation state control values will change device state to new attenuation. Direct Mode is ideal for manual control of the device (using hardwire, switches, or jumpers).

#### **Serial Interface**

The serial interface is a 8-bit serial-in, parallel-out shift register buffered by a transparent later. The set bits make up the Attenuation Word that controls the DSA. *Fig. 15* illustrates a example timing diagram for programming a state.

The serial-interface is controlled using three CMOScompatible signals: Serial-In (SI), Clock (CLK), and Latch Enable (LE). The SI and CLK inputs allow data to be serially entered into the shift register. Serial data is clocked in LSB first

The shift register must be loaded while LE is held LOW to prevent the attenuator value from changing as data is entered. The LE input should then be toggled HIGH and brought LOW again, latching the new data into the DSA. Attenuation Word truth table is listed in *Table 8*. A programming example of the serial register is illustrated in *Table 9*. The serial timing diagram is illustrated in *Fig. 15*. It is required that all parallel pins be grounded when the DSA is used in serial mode.

#### Power-up Control Settings

The PE43602 will always initialize to the maximum attenuation setting (31.5 dB) on power-up for both the serial and latched-parallel modes of operation and will remain in this setting until the user latches in the next programming word. In direct-parallel mode, the DSA can be preset to any state within the 31.5 dB range by pre-setting the parallel control pins prior to power up. In this mode, there is a 400-µs delay between the time the DSA is powered-up to e time the desired state is set. During this powerup delay, the device attenuates to the maximum attenuation setting (31.5 dB) before defaulting to the r defined state. If the control pins are left floating ùs in this mode during power-up, the device will default to the minimum attenuation setting (insertion loss state

Dynamic operation between serial and parallel programming modes is possible.

If the DSA powers up in serial mode ( $\overline{P}/S = HIGH$ ), all the parallel control inputs DI[6:1] must be set to logic low. Prior to toggling to parallel mode, the DSA *must* be programmed serially to ensure D[7] is set to logic low.

If the DSA powers up in either latched or directparallel mode, all parallel pins DI[6:1] must be set to logic low prior to toggling to serial mode ( $\overline{P}/S$ = HIGH), and *held* low until the DSA has been programmed serially to ensure bit D[7] is set to logic low.

The sequencing is only required once on powerup. Once completed, the DSA may be toggled between serial and parallel programming modes at will.

©2010 Peregrine Semiconductor Corp. All rights reserved.

Document No. 70-0248-06 | UltraCMOS™ RFIC Solutions

PE43602

Product Specification

#### Figure 15. Serial Timing Diagram

#### Table 10. Serial Interface AC Characteristics $V_{DD} = 3.3 \text{ or } 5.0 \text{ V}, -40^{\circ}\text{C} < T_A < 85^{\circ}\text{C}$ , unless otherwise specified

| Symbol            | Parameter                                                                  | Min. | Max. | Unit |

|-------------------|----------------------------------------------------------------------------|------|------|------|

| F <sub>CLK</sub>  | Serial clock frequency                                                     | ·    | 10   | MHż  |

| T <sub>CLKH</sub> | Serial clock HIGH time                                                     | 30   | -    | ns   |

| T <sub>CLKL</sub> | Serial clock LOW time                                                      | 30   | -    | ns   |

| T <sub>LESU</sub> | Last serial clock rising edge<br>setup time to Latch Enable<br>rising edge | 10   | Ņ    | ns   |

| $T_{LEPW}$        | Latch Enable minimum pulse width                                           | 30   |      | ns   |

| T <sub>SISU</sub> | Serial data setup time                                                     | 10   |      | ns   |

| T <sub>SIH</sub>  | Serial data hold time                                                      | 10   | -    | ns   |

| $T_{DISU}$        | Parallel data setup time                                                   | 100  | -    | ns   |

| T <sub>DIH</sub>  | Parallel data hold time                                                    | 100  | -    | ns   |

| T <sub>ASU</sub>  | Address setup time                                                         | 100  | -    | ns   |

| T <sub>AH</sub>   | Address hold time                                                          | 100  | -    | ns   |

| T <sub>PSSU</sub> | Parallel/Serial setup time                                                 | 100  | -    | ns   |

| T <sub>PSH</sub>  | Parallel/Serial hold time                                                  | 100  | -    | ns   |

| T <sub>PD</sub>   | Digital register delay (internal)                                          | -    | 10   | ns   |

#### ble 11. Parallel and Direct Interface AC Characteristics

$V_{DD}$  = 3.3 or 5.0 V, -40°C < T<sub>A</sub> < 85°C, unless otherwise specified

| Symbol            | Parameter                                           | Min | Max | Unit |

|-------------------|-----------------------------------------------------|-----|-----|------|

| T <sub>LEPW</sub> | Latch Enable minimum pulse width                    | 30  | -   | ns   |

| T <sub>DISU</sub> | Parallel data setup time                            | 100 | -   | ns   |

| T <sub>DIH</sub>  | Parallel data hold time                             | 100 | -   | ns   |

| T <sub>PSSU</sub> | Parallel/Serial setup time                          | 100 | -   | ns   |

| T <sub>PSIH</sub> | Parallel/Serial hold time                           | 100 | -   | ns   |

| T <sub>PD</sub>   | Digital register delay (internal)                   | -   | 10  | ns   |

| T <sub>DIPD</sub> | Digital register delay (internal, direct mode only) | -   | 5   | ns   |

Document No. 70-0248-06 | www.psemi.com

PE43602 Product Specification

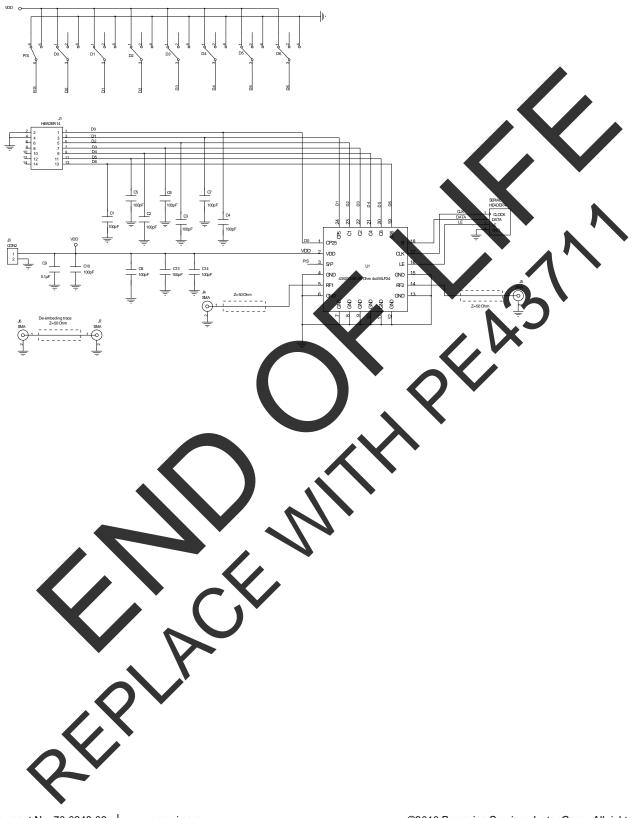

#### **Evaluation Kit**

The Digital Attenuator Evaluation Kit board was designed to ease customer evaluation of the PE43602 Digital Step Attenuator.

Direct-Parallel Programming Procedure For automated direct-parallel programming, connect the test harness provided with the EVK from the parallel port of the PC to the J1 & Serial header pin and set the D0-D6 SP3T switches to the 'MIDDLE' toggle position. Position the Parallel/Serial ( $\overline{P}$ /S) select switch to the Parallel (or left) position. The evaluation software is written to operate the DSA in either Parallel or Serial-Addressable Mode. Ensure that the software is set to program in *Direct-Parallel* mode. Using the software, enable or disable each setting to the desired attenuation state. The software automatically programs the DSA each time an attenuation state is enabled or disabled.

For manual direct-parallel programming, disconnect the test harness provided with the from the J1 and Serial header pins. Position the Parallel/Serial ( $\overline{P}/S$ ) select switch to the Parallel (or left) position. The LE pin on the Serial header must be tied to  $V_{DD}$ . Switches D0-D6 are SP3 switches which enable the user to manually program the parallel bits. When any input D0-D6 is toggled 'UP', logic high is presented to the parallel input. When toggled DQWN', logic low is presented to the parallel input. Setting D0-D6 to the 'MIDDLE' toggle position present an OPEN Table 9 denic which forces an on-chip logic lov the parallel programming truth table and illustrates the parallel programming timi diagram,

#### Latched-Parallel Programming Procedure

For automated latched-parallel programming, the procedure is identical to the direct parallel method. The user only must ensure that *Latched-Parallel* is selected in the software.

For manual latched parallel programming, the procedure is identical to direct-parallel except now the LE pin on the Setial header must be logic low Figure 17. Evaluation Board Layout

Peregrine Specification 101-0310

Reference Figure 18 for Evaluation Board Schematic

as the parallel bits are applied. The user must then pulse LE from 0V to  $V_{DD}$  and back to 0V to latch the programming word into the DSA. LE must be logic low prior to programming the next word.

#### Serial Programming Procedure

Position the Parallel/Serial ( $\overline{P}$ /S) select switch to the Serial (or right) position. The evaluation software is written to operate the DSA in either Parallel or Serial Mode. Ensure that the software is set to program in Serial mode. Using the software, enable or disable each setting to the desired attenuation state. The software automatically programs the DSA each time an attenuation state is enabled or disabled.

©2010 Peregrine Semiconductor Corp. All rights reserved.

Document No. 70-0248-06 | UltraCMOS™ RFIC Solutions

PE43602 Product Specification

#### Figure 18. Evaluation Board Schematic

Peregrine Specification 102-0379

Document No. 70-0248-06 | www.psemi.com

PE43602 Product Specification

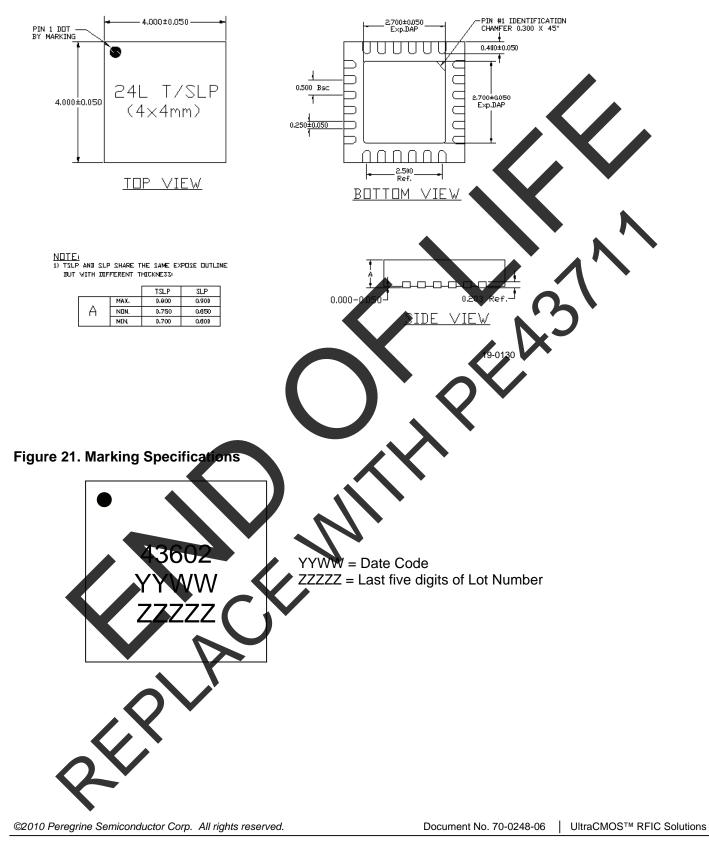

#### Figure 19. Package Drawing

## PE43602

Product Specification

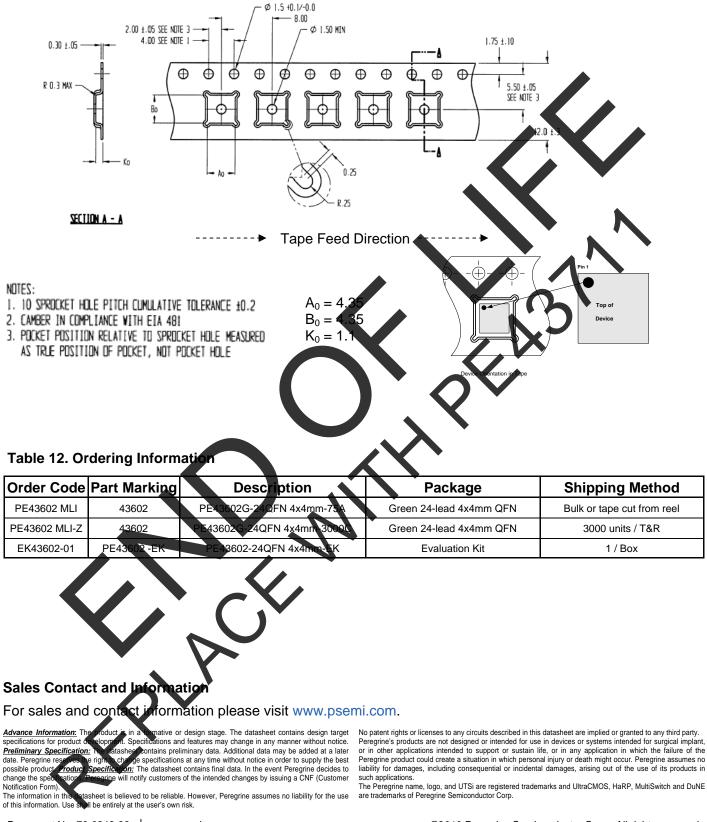

#### Figure 20. Tape and Reel Drawing

Document No. 70-0248-06 www.psemi.com

©2010 Peregrine Semiconductor Corp. All rights reserved.

Logo updated under non-rev change. Peregrine products are protected under one or more of the following U.S. Patents: http://patents.psemi.com