## Excellent Integrated System Limited

Stocking Distributor

Click to view price, real time Inventory, Delivery & Lifecycle Information:

[Texas Instruments](#)

[AFE7070IRGZR](#)

For any questions, you can email us directly:

[sales@integrated-circuit.com](mailto:sales@integrated-circuit.com)

## Dual 14-Bit 65-MSPS Digital-to-Analog Converter With Integrated Analog Quadrature Modulator

Check for Samples: [AFE7070](#)

### FEATURES

- Maximum Sample Rate: 65 MSPS

- Low Power:

- 325 mW LVDS Output Mode

- 334 mW Analog Output Mode

- Interleaved CMOS Input, 1.8–3.3 V IOVDD

- Input FIFO for Independent Data and DAC Clocks

- 3- or 4-pin SPI Interface for Register Programming

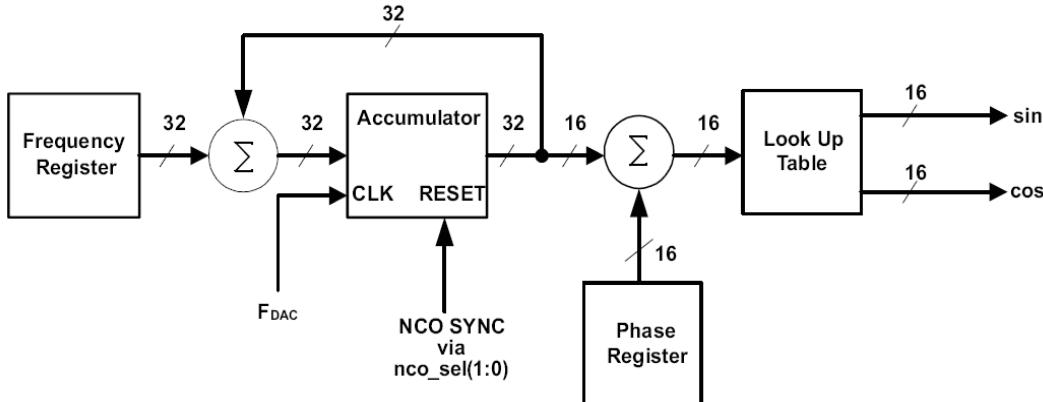

- Complex NCO (DDS): 32-Bit Frequency, 16-Bit Phase

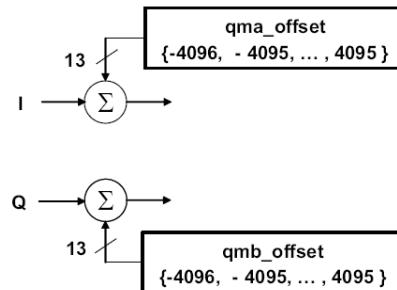

- Quadrature Modulator Correction: Gain, Phase, Offset for Sideband and LO Suppression

- Analog Baseband Filter With Programmable Bandwidth: 20-MHz Maximum RF Bandwidth

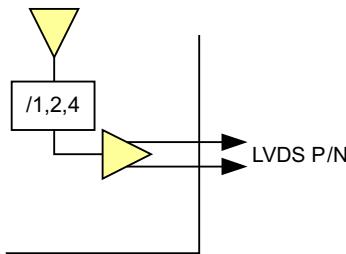

- RF Ouput: Analog (linear) or LVDS (Clock)

- RF Frequency Range: 100 MHz to 2.7 GHz

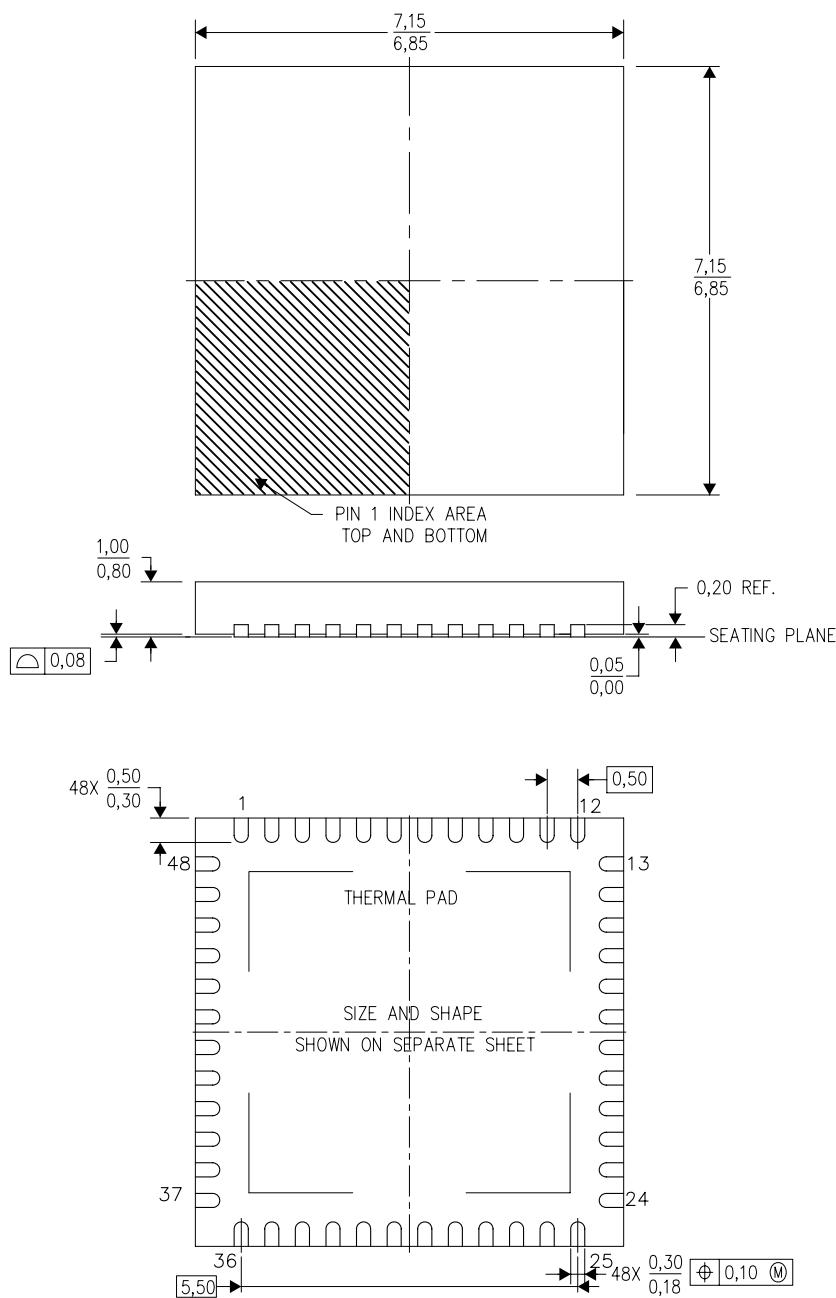

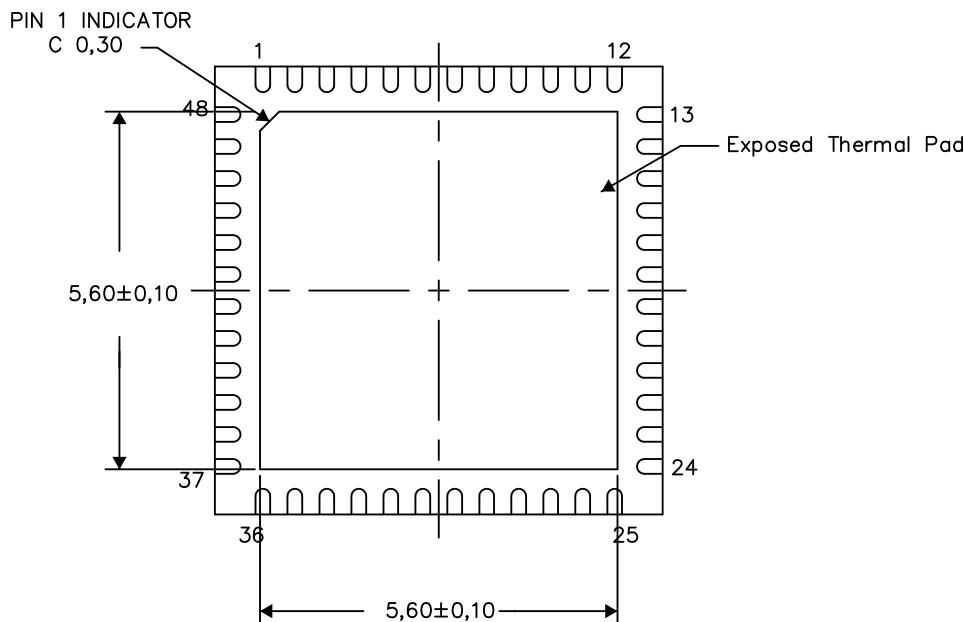

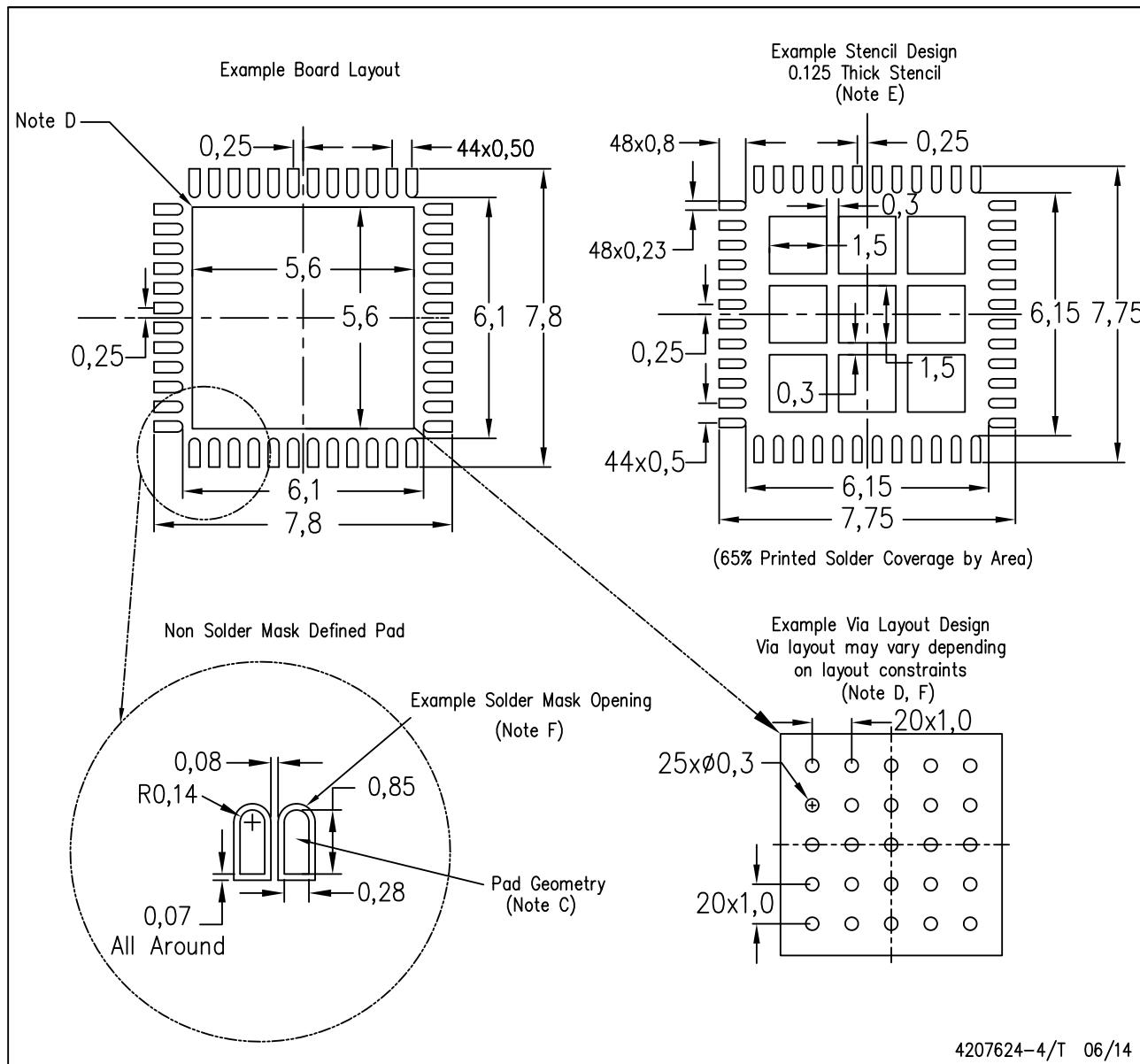

- Package: 48-Pin QFN (7-mm × 7-mm)

### APPLICATIONS

- Low-Power, Compact Software-Defined Radios

- Femto- and Pico-Cell BTS

- Clock Frequency Translation

### DESCRIPTION

The AFE7070 is a dual 14-bit 65-MSPS digital-to-analog converter (DAC) with integrated, programmable fourth-order baseband filter and analog quadrature modulator. The AFE7070 includes additional digital signal-processing features such as a numerically controlled oscillator for frequency generation/translation, and a quadrature modulator correction circuit, providing LO and sideband suppression capability. The AFE7070 has an interleaved 14-bit 1.8-V to 3.3-V CMOS input. The AFE7070 provides 20 MHz of RF signal bandwidth with an RF output frequency range of 100 MHz to 2.7 GHz. An optional LVDS output can be used to convert the quadrature modulator output to a clock signal up to 800 MHz. Total power consumption is less than 350 mW with the LVDS output and 334 mW with the analog RF output.

The AFE7070 package is a 7-mm × 7mm 48-pin QFN package. The AFE7070 is specified over the full industrial temperature range (–40°C to 85°C).

### AVAILABLE OPTIONS

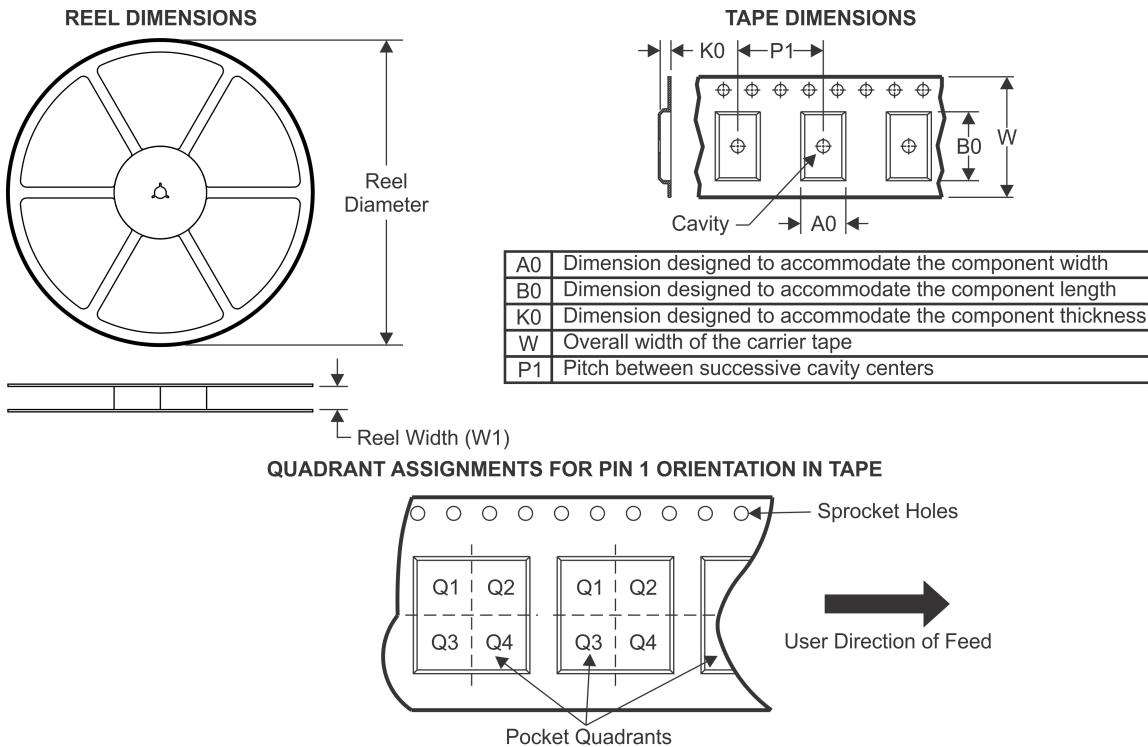

| T <sub>A</sub> | ORDER CODE    | PACKAGE DRAWING/TYPE              | TRANSPORT MEDIA | QUANTITY |

|----------------|---------------|-----------------------------------|-----------------|----------|

| –40°C to 85°C  | AFE7070IRGZ25 | RGZ / 48QFN quad flatpack no-lead | Tape and reel   | 25       |

|                | AFE7070IRGZT  |                                   |                 | 250      |

|                | AFE7070IRGZR  |                                   |                 | 2500     |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

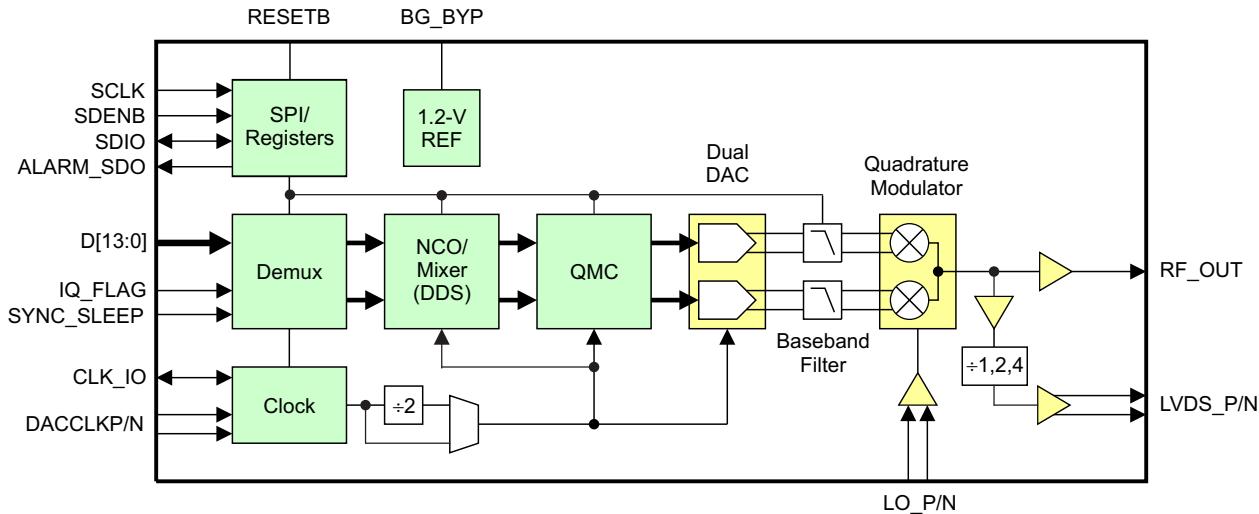

## BLOCK DIAGRAM

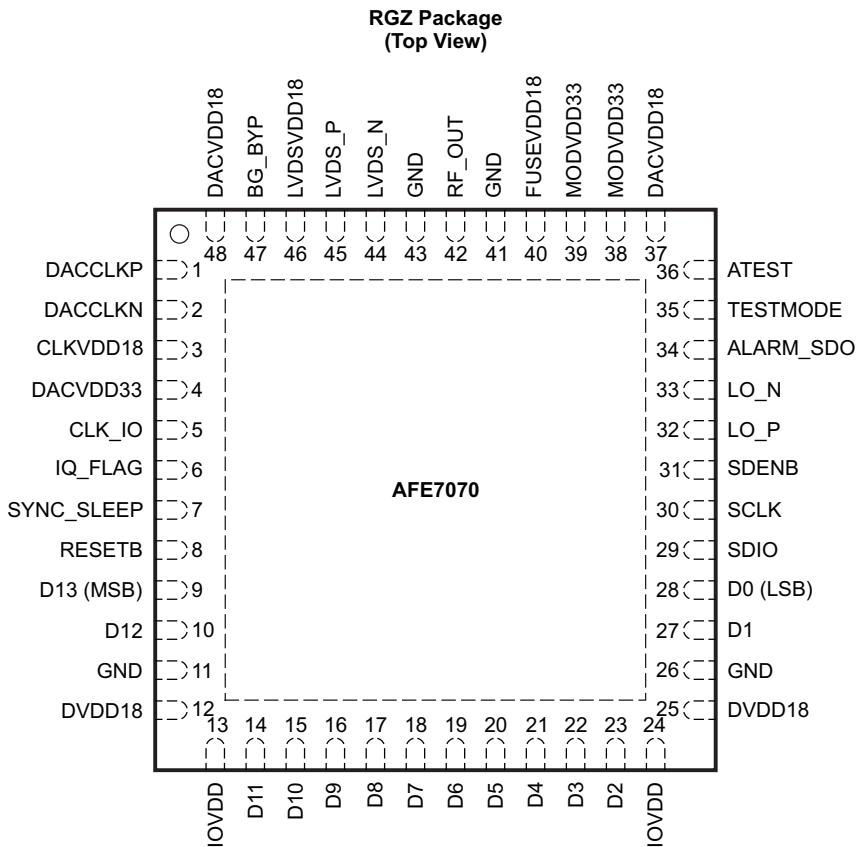

## PIN CONFIGURATION

P0023-25

**PIN FUNCTIONS**

| PIN                         |                            | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                   |

|-----------------------------|----------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                        | NO.                        |     |                                                                                                                                                                                                                                                                                                               |

| <b>MISC/SERIAL</b>          |                            |     |                                                                                                                                                                                                                                                                                                               |

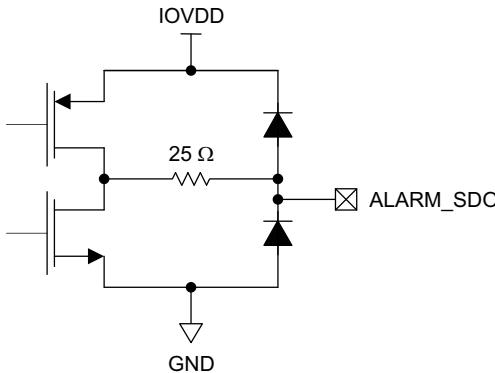

| ALARM_SDO                   | 34                         | O   | CMOS output for ALARM condition, active-low. The ALARM output functionality is defined through the CONFIG7 registers.<br>Optionally, it can be used as the unidirectional data output in 4-pin serial interface mode (CONFIG3 sif_4pin = 1). 1.8-V to 3.3-V CMOS, set by IOVDD.                               |

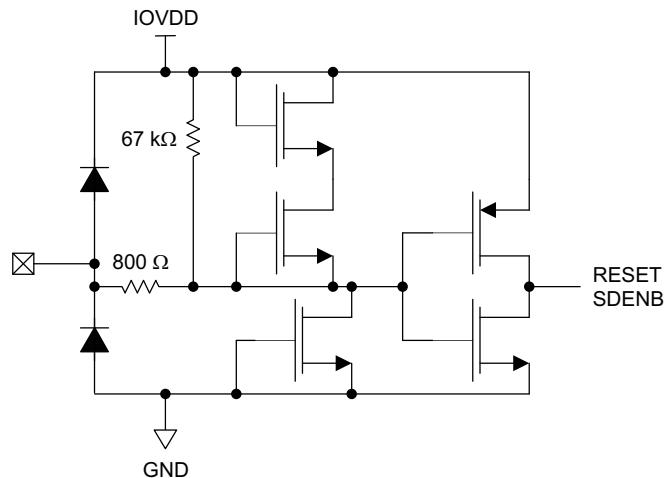

| RESETB                      | 8                          | I   | Resets the chip when low. 1.8-V to 3.3-V CMOS, set by IOVDD. Internal pullup                                                                                                                                                                                                                                  |

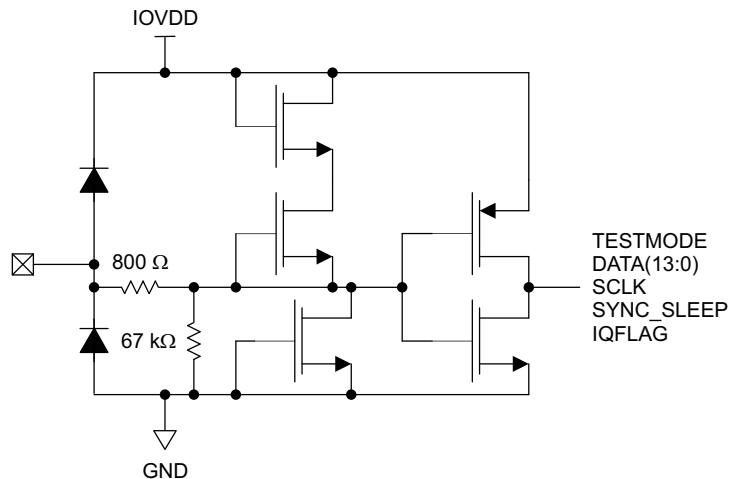

| SCLK                        | 30                         | I   | Serial interface clock. 1.8-V to 3.3-V CMOS, set by IOVDD. Internal pulldown                                                                                                                                                                                                                                  |

| SDENB                       | 31                         | I   | Active-low serial data enable, always an input. 1.8-V to 3.3-V CMOS, set by IOVDD. Internal pullup                                                                                                                                                                                                            |

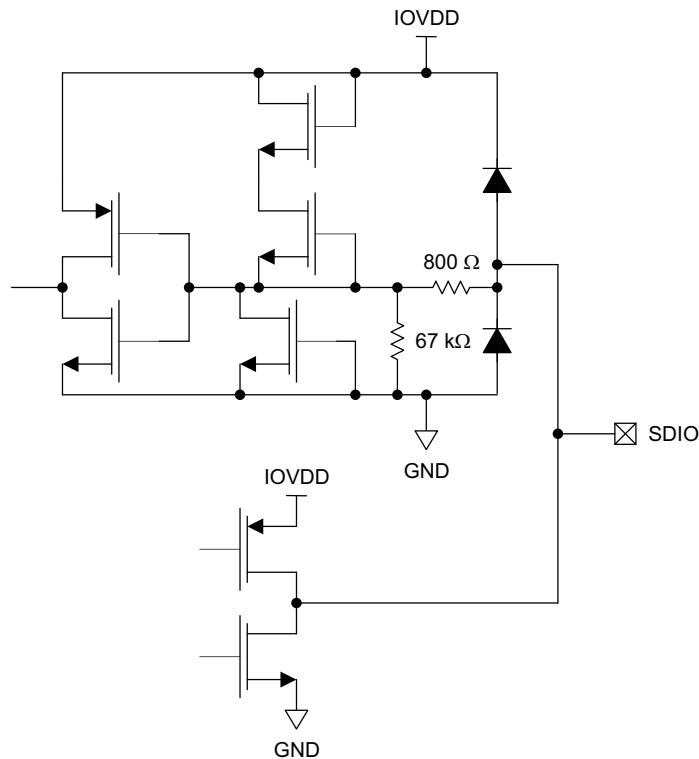

| SDIO                        | 29                         | I/O | Bidirectional serial data in 3-pin mode (default). In 4-pin interface mode (CONFIG3 sif_4pin), the SDIO pin is an input only. 1.8-V to 3.3-V CMOS, set by IOVDD. Internal pulldown                                                                                                                            |

| <b>DATA/CLOCK INTERFACE</b> |                            |     |                                                                                                                                                                                                                                                                                                               |

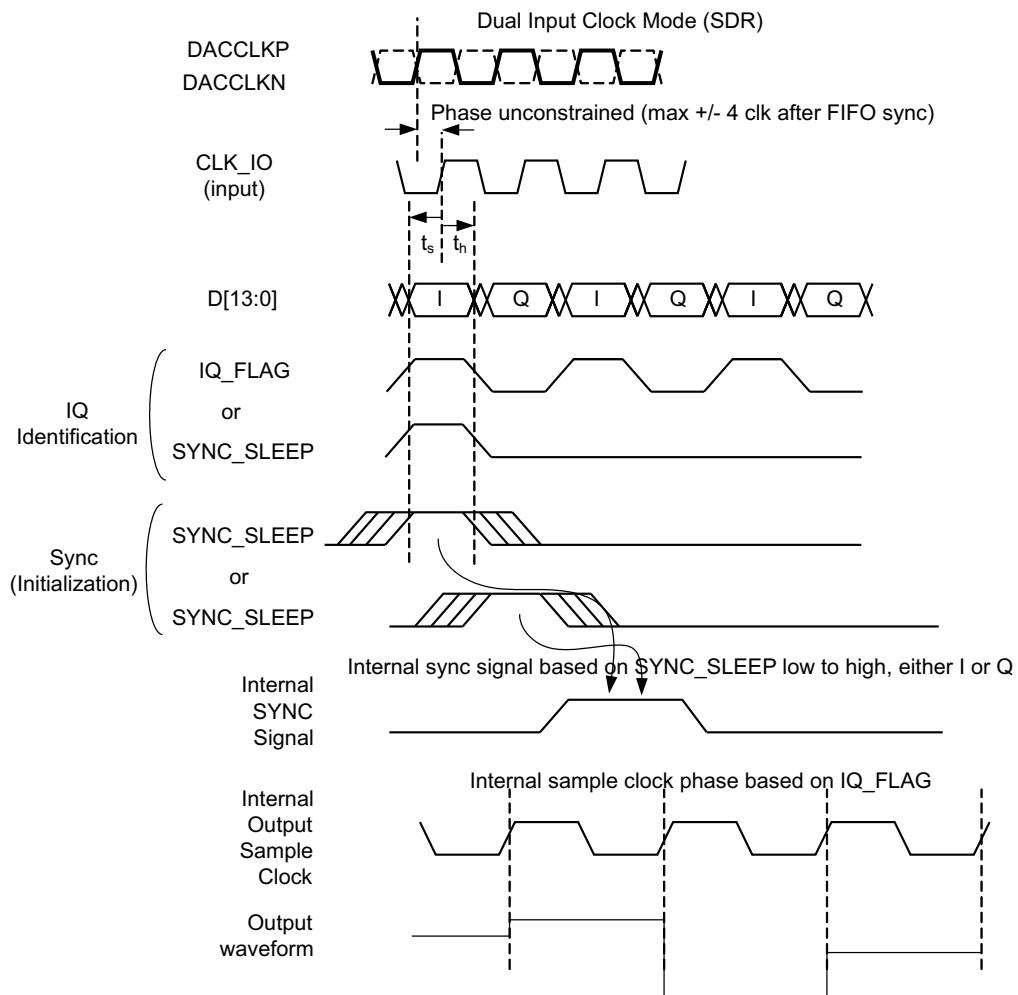

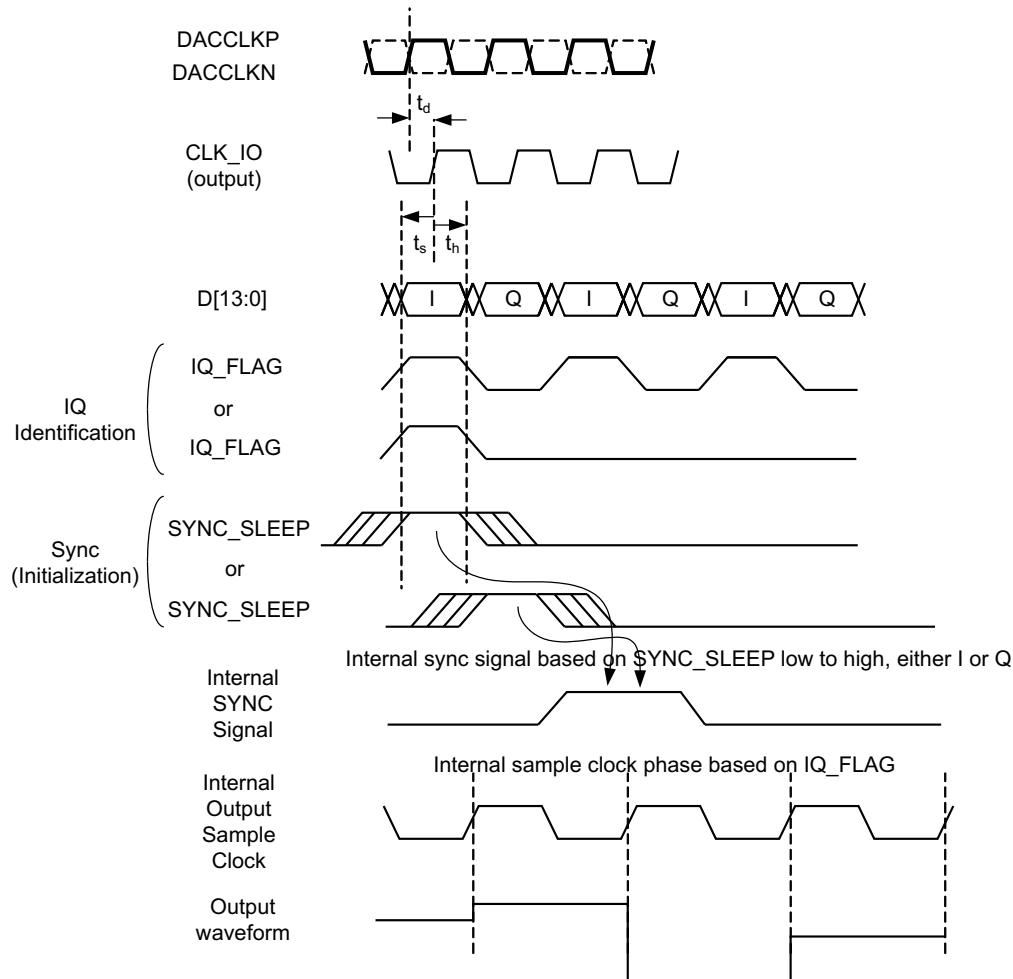

| CLK_IO                      | 5                          | I/O | Single-ended input or output CMOS level clock for latching input data. 1.8-V to 3.3-V CMOS, set by IOVDD.                                                                                                                                                                                                     |

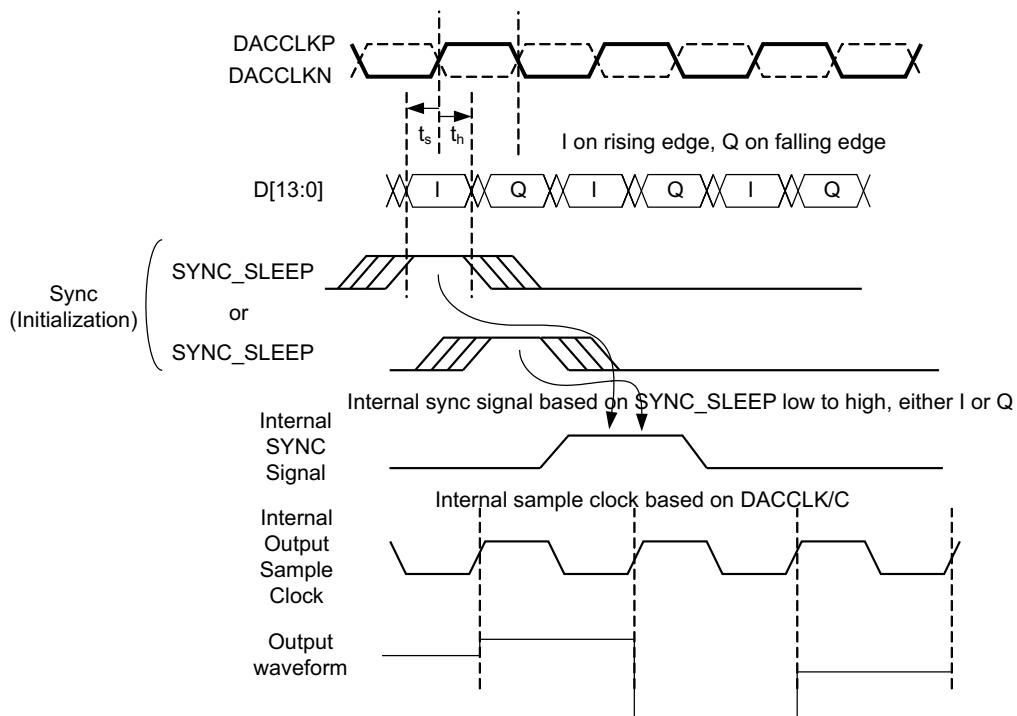

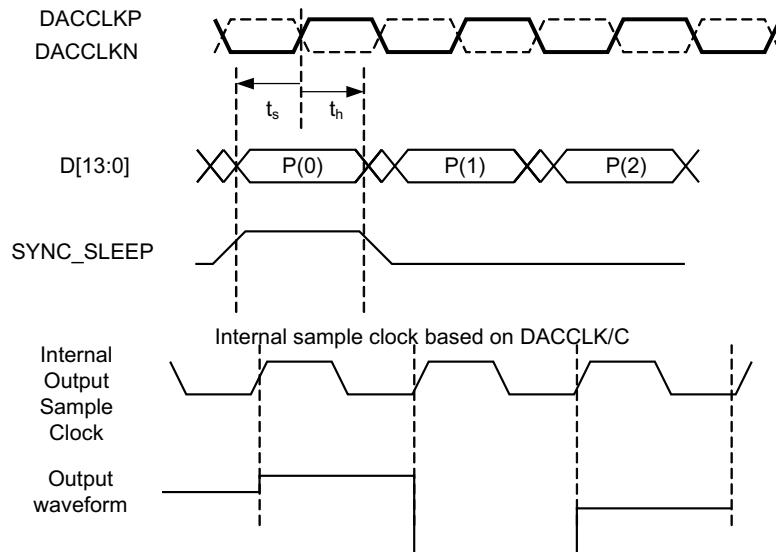

| D[13:0]                     | 9, 10,<br>14–23,<br>27, 28 | I   | Data bits 0 through 13. D13 is the MSB, D0 is the LSB. For complex data, channel I and channel Q are multiplexed. For NCO phase data, either 14 bits are transferred at the internal sample clock rate, or 8 MSBs and 8 LSBs are interleaved on D[13:6]. 1.8-V to 3.3-V CMOS, set by IOVDD. Internal pulldown |

| DACCLKP,<br>DACCLKN         | 1, 2                       | I   | Differential input clock for DACs.                                                                                                                                                                                                                                                                            |

| IQ_FLAG                     | 6                          | I   | When register CONFIG1 iqswap is 0, IQ-FLAG high identifies the DACA sample in dual-input or dual-output clock modes. 1.8-V or 3.3-V CMOS, set by IOVDD. Internal pulldown                                                                                                                                     |

| SYNC_SLEEP                  | 7                          | I   | Multi-function. Sync signal for signal processing blocks, TX ENABLE or SLEEP function. Selectable via SPI. 1.8-V to 3.3-V CMOS, set by IOVDD.                                                                                                                                                                 |

| <b>RF</b>                   |                            |     |                                                                                                                                                                                                                                                                                                               |

| LO_P, LO_N                  | 32, 33                     | I   | Local oscillator input. Can be used differentially or single-ended by terminating the unused input through a capacitor and 50- $\Omega$ resistor to GND.                                                                                                                                                      |

| LVDS_P,<br>LVDS_N           | 45, 44                     | O   | Differential LVDS output                                                                                                                                                                                                                                                                                      |

| RF_OUT                      | 42                         | O   | Analog RF output                                                                                                                                                                                                                                                                                              |

| <b>REFERENCE</b>            |                            |     |                                                                                                                                                                                                                                                                                                               |

| ATEST                       | 36                         | O   | Factory use only. Do not connect.                                                                                                                                                                                                                                                                             |

| BG_BYP                      | 47                         | I   | Reference voltage decoupling – connect 0.1 $\mu$ F to GND.                                                                                                                                                                                                                                                    |

| TESTMODE                    | 35                         | I   | Factory use only. Connect to GND.                                                                                                                                                                                                                                                                             |

| <b>POWER</b>                |                            |     |                                                                                                                                                                                                                                                                                                               |

| IOVDD                       | 13, 24                     | I   | 1.8-V to 3.3-V supply for CMOS I/Os                                                                                                                                                                                                                                                                           |

| CLKVDD18                    | 3                          | I   | 1.8 V                                                                                                                                                                                                                                                                                                         |

| DVDD18                      | 12, 25                     | I   | 1.8 V                                                                                                                                                                                                                                                                                                         |

| LVDSVDD18                   | 46                         | I   | 1.8 V                                                                                                                                                                                                                                                                                                         |

| DACVDD18                    | 37, 48                     | I   | 1.8 V                                                                                                                                                                                                                                                                                                         |

| DACVDD33                    | 4                          | I   | 3.3 V                                                                                                                                                                                                                                                                                                         |

| MODVDD33                    | 38, 39                     | I   | 3.3 V                                                                                                                                                                                                                                                                                                         |

| FUSEVDD18                   | 40                         | I   | Connect to 1.8 V to 3.3 V supply (1.8 V is preferred to lower power dissipation).                                                                                                                                                                                                                             |

| GND                         | 11, 26,<br>41, 43          | I   | Ground                                                                                                                                                                                                                                                                                                        |

## ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                      |                                                                                       | VALUE                       |

|------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------|

| Supply voltage range                                 | DACVDD33, MODVDD33, FUSEVDD18, IOVDD <sup>(2)</sup>                                   | –0.5 V to 4 V               |

|                                                      | DVDD18, CLKVDD18, DACVDD18 <sup>(2)</sup>                                             | –0.5 V to 2.3 V             |

|                                                      |                                                                                       | –0.5 V to 4 V               |

| Supply voltage range <sup>(2)</sup>                  | D[13..0], IQ FLAG, SYNC_SLEEP, SCLK, SDENB, SDIO, ALARM_SDO, RESETB, CLK_IO, TESTMODE | –0.5 V to IOVDD + 0.5 V     |

|                                                      | DACCLKP, DACCLKN                                                                      | –0.5 V to CLKVDD18 + 0.5 V  |

|                                                      | LVDS_P, LVDS_N                                                                        | –0.5 V to LVDSVDD18 + 0.5 V |

|                                                      | BG_BYP, ATTEST                                                                        | –0.5 V to DACVDD33 + 0.5 V  |

|                                                      | RFOUT, LO_P, LO_N                                                                     | –0.5 V to MODVDD33 + 0.5 V  |

| Operating free-air temperature range, T <sub>A</sub> |                                                                                       | –40°C to 85°C               |

| Storage temperature range                            |                                                                                       | –65°C to 150°C              |

(1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Measured with respect to GND

## DC ELECTRICAL CHARACTERISTICS

Typical values at T<sub>A</sub> = 25°C, full temperature range is T<sub>MIN</sub> = –40°C to T<sub>MAX</sub> = 85°C, DAC sampling rate = 65 MSPS, DVDD18 = 1.8 V, CLKVDD18 = 1.8 V, DACVDD18 = 1.8 V, IOVDD = 3.3 V, DACVDD33 = 3.3 V, MODVDD33 = 3.3 V, analog output (unless otherwise noted)

| PARAMETER                                                         | TEST CONDITIONS                                                              | MIN                                     | TYP  | MAX  | UNIT |   |

|-------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------|------|------|------|---|

| <b>DC SPECIFICATIONS</b>                                          |                                                                              |                                         |      |      |      |   |

| DAC resolution                                                    |                                                                              | 14                                      |      |      | Bits |   |

| <b>REFERENCE OUTPUT</b>                                           |                                                                              |                                         |      |      |      |   |

| Reference voltage                                                 |                                                                              | 1.14                                    | 1.2  | 1.26 | V    |   |

| <b>POWER SUPPLY</b>                                               |                                                                              |                                         |      |      |      |   |

| IOVDD                                                             | I/O supply voltage                                                           | 1.71                                    | 3.6  |      | V    |   |

| DVDD18                                                            | Digital supply voltage                                                       | 1.71                                    | 1.8  | 1.89 | V    |   |

| CLKVDD18                                                          | Clock supply voltage                                                         | 1.71                                    | 1.8  | 1.89 | V    |   |

| DACVDD18                                                          | DAC 1.8-V analog supply voltage                                              | 1.71                                    | 1.8  | 1.89 | V    |   |

| LVDSVDD18                                                         | LVDS analog supply voltage                                                   | 1.71                                    | 1.8  | 1.89 | V    |   |

| FUSEVDD18                                                         | FUSE analog supply voltage                                                   | Connect to 1.8-V supply for lower power | 1.71 | 1.8  | 3.6  | V |

| DACVDD33                                                          | DAC 3.3-V analog supply voltage                                              |                                         | 3.15 | 3.3  | 3.45 | V |

| MODVDD33                                                          | Modulator analog supply voltage                                              |                                         | 3.15 | 3.3  | 3.45 | V |

| I <sub>IOVDD</sub>                                                | I/O supply current                                                           |                                         |      |      | mA   |   |

| I <sub>DVDD18</sub>                                               | Digital supply current                                                       |                                         | 18   |      | mA   |   |

| I <sub>CLKVDD18</sub>                                             | Clock supply current                                                         |                                         |      |      | mA   |   |

| I <sub>DACVDD18</sub>                                             | DAC 1.8-V supply current                                                     |                                         |      |      | mA   |   |

| I <sub>LVDSVDD18</sub>                                            | LVDS output supply current                                                   |                                         |      |      | mA   |   |

| I <sub>FUSEVDD18</sub>                                            | FUSE supply current                                                          |                                         | 21   |      | mA   |   |

| I <sub>DACVDD33</sub>                                             | DAC 3.3-V supply current                                                     |                                         |      |      | mA   |   |

| I <sub>MODVDD33</sub>                                             | Modulator supply current                                                     |                                         | 68   |      | mA   |   |

| Power dissipation                                                 | LVDS output: NCO, QMC active, f <sub>DAC</sub> = 40 MHz, IOVDD = 2.5 V       |                                         | 337  | 380  | mW   |   |

|                                                                   | Analog output: NCO off, QMC active, f <sub>DAC</sub> = 65 MHz, IOVDD = 2.5 V |                                         | 335  | 380  | mW   |   |

|                                                                   | Sleep mode with clock, internal reference on, IOVDD = 2.5 V                  |                                         | 80   |      | mW   |   |

|                                                                   | Sleep mode without clock, internal reference off, IOVDD = 2.5 V              |                                         | 5    | 25   | mW   |   |

| <b>POWER SUPPLY vs MODE</b>                                       |                                                                              |                                         |      |      |      |   |

| 3.3-V supplies (DACVDD33, MODVDD33, IOVDD)                        |                                                                              | 72                                      |      |      | mA   |   |

|                                                                   |                                                                              | 47                                      |      |      | mA   |   |

|                                                                   |                                                                              | 322                                     |      |      | mW   |   |

| 1.8-V supplies (DVDD18, CLKVDD18, DACVDD18, FUSEVDD18, LVDSVDD18) | NCO = 1 MHz, LVDS on, RF out off, no input data, 65 MSPS                     |                                         |      |      |      |   |

| Power dissipation                                                 |                                                                              |                                         |      |      |      |   |

## DC ELECTRICAL CHARACTERISTICS (continued)

Typical values at  $T_A = 25^\circ\text{C}$ , full temperature range is  $T_{\text{MIN}} = -40^\circ\text{C}$  to  $T_{\text{MAX}} = 85^\circ\text{C}$ , DAC sampling rate = 65 MSPS, DVDD18 = 1.8 V, CLKVDD18 = 1.8 V, DACVDD18 = 1.8 V, IOVDD = 3.3 V, DACVDD33 = 3.3 V, MODVDD33 = 3.3 V, analog output (unless otherwise noted)

| PARAMETER                                                         | TEST CONDITIONS                                                                 | MIN | TYP | MAX | UNIT |

|-------------------------------------------------------------------|---------------------------------------------------------------------------------|-----|-----|-----|------|

| 3.3-V supplies (DACVDD33, MODVDD33, IOVDD)                        | NCO = 1 MHz, LVDS on, RF out off, no input data, 40 MSPS                        | 71  |     |     | mA   |

| 1.8-V supplies (DVDD18, CLKVDD18, DACVDD18, FUSEVDD18, LVDSVDD18) |                                                                                 | 32  |     |     | mA   |

| Power dissipation                                                 |                                                                                 | 337 |     |     | mW   |

| 3.3-V supplies (DACVDD33, MODVDD33, IOVDD)                        | 1 MHz full-scale input, RF out on, LVDS output off, NCO off, QMC on, 65 MSPS    | 102 |     |     | mA   |

| 1.8-V supplies (DVDD18, CLKVDD18, DACVDD18, FUSEVDD18, LVDSVDD18) |                                                                                 | 36  |     |     | mA   |

| Power dissipation                                                 |                                                                                 | 334 |     |     | mW   |

| 3.3-V supplies (DACVDD33, MODVDD33, IOVDD)                        | 1 MHz full-scale input, RF out on, LVDS output off, NCO off, QMC off, 32.5 MSPS | 101 |     |     | mA   |

| 1.8-V supplies (DVDD18, CLKVDD18, DACVDD18, FUSEVDD18, LVDSVDD18) |                                                                                 | 22  |     |     | mA   |

| Power dissipation                                                 |                                                                                 | 325 |     |     | mW   |

## ELECTRICAL CHARACTERISTICS

Typical values at  $T_A = 25^\circ\text{C}$ , full temperature range is  $T_{\text{MIN}} = -40^\circ\text{C}$  to  $T_{\text{MAX}} = 85^\circ\text{C}$ , DAC sampling rate = 65 MSPS, DVDD18 = 1.8 V, CLKVDD18 = 1.8 V, DACVDD18 = 1.8 V, FUSEVDD18 = 1.8 V, IOVDD = 3.3 V, DACVDD33 = 3.3 V, MODVDD33 = 3.3 V, analog output (unless otherwise noted)

| PARAMETER                                                                                                      | TEST CONDITIONS                                                  | MIN                | TYP                 | MAX | UNIT          |

|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------|---------------------|-----|---------------|

| <b>DIGITAL INPUTS (D[13:0], IQ_FLAG, SDI, SCLK, SDENB, RESETB, SYNC_SLEEP, ALARM_SDO, CLK_IO)</b>              |                                                                  |                    |                     |     |               |

| $V_{IH}$<br>High-level input voltage                                                                           | $IOVDD = 3.3\text{ V}$                                           | 2.3                |                     |     | V             |

|                                                                                                                | $IOVDD = 2.5\text{ V}$                                           | 1.75               |                     |     |               |

|                                                                                                                | $IOVDD = 1.8\text{ V}$                                           | 1.25               |                     |     |               |

| $V_{IL}$<br>Low-level input voltage                                                                            | $IOVDD = 3.3\text{ V}$                                           |                    | 1                   |     | V             |

|                                                                                                                | $IOVDD = 2.5\text{ V}$                                           |                    | 0.75                |     |               |

|                                                                                                                | $IOVDD = 1.8\text{ V}$                                           |                    | 0.54                |     |               |

| $I_{IH}$<br>High-level input current                                                                           | $IOVDD = 3.3\text{ V}$                                           |                    | -80                 | 80  | $\mu\text{A}$ |

| $I_{IL}$<br>Low-level input current                                                                            | $IOVDD = 3.3\text{ V}$                                           |                    | -80                 | 80  | $\mu\text{A}$ |

| $C_I$<br>Input capacitance                                                                                     |                                                                  |                    | 5                   |     | $\text{pF}$   |

| $f_{\text{DAC}}$<br>DAC sample rate                                                                            | Interleaved data, $f_{\text{DAC}} = 1/2 \times f_{\text{INPUT}}$ | 0                  | 65                  |     | MSPS          |

| $f_{\text{INPUT}}$<br>Input data rate                                                                          | Interleaved data, $f_{\text{INPUT}} = 2 \times f_{\text{DAC}}$   | 0                  | 130                 |     | MSPS          |

| <b>DIGITAL OUTPUTS (ALARM_SDO, SDIO, CLK_IO)</b>                                                               |                                                                  |                    |                     |     |               |

| $V_{OH}$<br>High-level output voltage                                                                          | $I_{\text{LOAD}} = -100\text{ }\mu\text{A}$                      | IOVDD - 0.2        |                     |     | V             |

|                                                                                                                | $I_{\text{LOAD}} = -2\text{ mA}$                                 | 0.8 $\times$ IOVDD |                     |     | V             |

| $V_{OL}$<br>Low-level output voltage                                                                           | $I_{\text{LOAD}} = 100\text{ }\mu\text{A}$                       |                    | 0.2                 |     | V             |

|                                                                                                                | $I_{\text{LOAD}} = 2\text{ mA}$                                  |                    | 0.22 $\times$ IOVDD |     | V             |

| <b>CLOCK INPUT (DACCLKP/DACCLKN)</b>                                                                           |                                                                  |                    |                     |     |               |

| DACCLKP/N duty cycle                                                                                           |                                                                  | 40%                | 60%                 |     |               |

| DACCLKP/N differential voltage                                                                                 |                                                                  | 0.4                | 1                   | V   |               |

| <b>Timing Parallel Data Input (D[13:0], IQ_FLAG, SYNC_SLEEP) – Dual Input Clock Mode</b>                       |                                                                  |                    |                     |     |               |

| $t_{SU}$<br>Input setup time                                                                                   | Relative to CLK_IO rising edge                                   | 1                  |                     |     | ns            |

| $t_H$<br>Input hold time                                                                                       | Relative to CLK_IO rising edge                                   | 1                  |                     |     | ns            |

| $t_{LPH}$<br>Input clock pulse high time                                                                       |                                                                  | 3                  |                     |     | ns            |

| <b>Timing Parallel Data Input (D[13:0], IQ_FLAG, SYNC_SLEEP) – Dual Output Clock Mode</b>                      |                                                                  |                    |                     |     |               |

| $t_{SU}$<br>Input setup time                                                                                   | Relative to CLK_IO rising edge                                   | 1                  | 0.2                 |     | ns            |

| $t_H$<br>Input hold time                                                                                       | Relative to CLK_IO rising edge                                   | 1                  | 0.2                 |     | ns            |

| <b>Timing Parallel Data Input (D[13:0], IQ_FLAG, SYNC_SLEEP) – Single Differential DDR and SDR Clock Modes</b> |                                                                  |                    |                     |     |               |

| $t_{SU}$<br>Input setup time                                                                                   | Relative to DACCLKP/N rising edge                                | 0                  | -0.8                |     | ns            |

| $t_H$<br>Input hold time                                                                                       | Relative to DACCLKP/N rising edge                                | 2                  | 1                   |     | ns            |

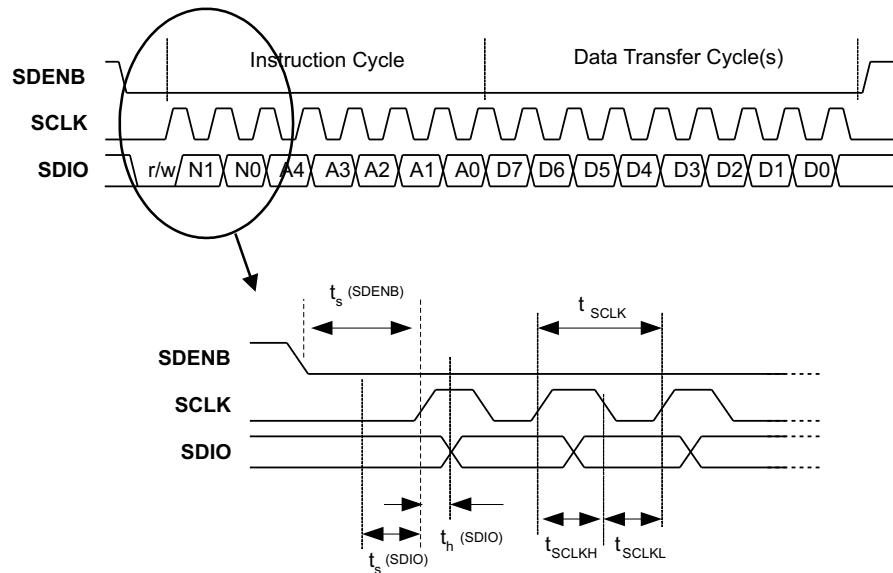

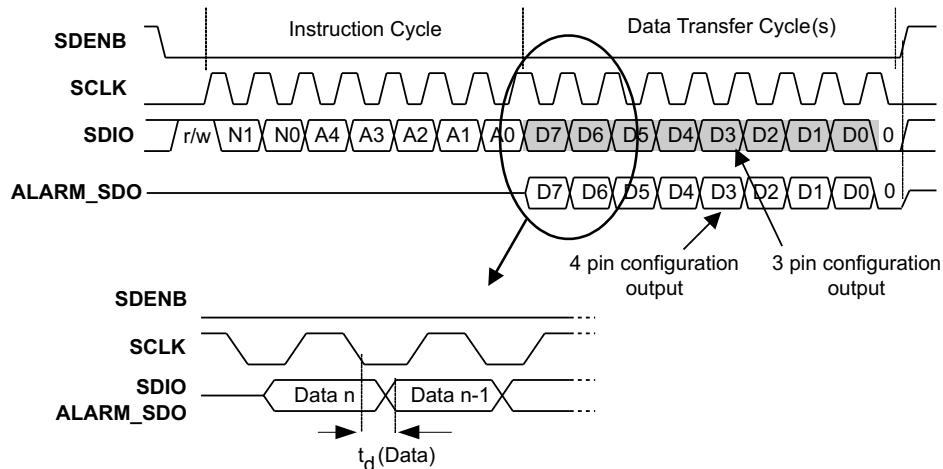

| <b>Timing – Serial Data Interface</b>                                                                          |                                                                  |                    |                     |     |               |

| $t_{S(SDENB)}$<br>Setup time, SDENB to rising edge of SCLK                                                     |                                                                  | 20                 |                     |     | ns            |

| $t_{S(SDIO)}$<br>Setup time, SDIO valid to rising edge of SCLK                                                 |                                                                  | 10                 |                     |     | ns            |

| $t_{H(SDIO)}$<br>Hold time, SDIO valid to rising edge of SCLK                                                  |                                                                  | 5                  |                     |     | ns            |

| $t_{SCLK}$<br>Period of SCLK                                                                                   |                                                                  | 100                |                     |     | ns            |

| $t_{SCLKH}$<br>High time of SCLK                                                                               |                                                                  | 40                 |                     |     | ns            |

| $t_{SCLKL}$<br>Low time of SCLK                                                                                |                                                                  | 40                 |                     |     | ns            |

| $t_{D(DATA)}$<br>Data output delay after falling edge of SCLK                                                  |                                                                  | 10                 |                     |     | ns            |

| $t_{RESET}$<br>Minimum RESETB pulse duration                                                                   |                                                                  | 25                 |                     |     | ns            |

## AC ELECTRICAL CHARACTERISTICS

Typical values at  $T_A = 25^\circ\text{C}$ , full temperature range is  $T_{\text{MIN}} = -40^\circ\text{C}$  to  $T_{\text{MAX}} = 85^\circ\text{C}$ , DAC sampling rate = 65 MSPS, DVDD18 = 1.8 V, CLKVDD18 = 1.8 V, DACVDD18 = 1.8 V, FUSEVDD18 = 1.8 V, IOVDD = 3.3 V, DACVDD33 = 3.3 V, MODVDD33 = 3.3 V, analog output (unless otherwise noted)

| PARAMETER                                                                                 | TEST CONDITIONS                                                                     | MIN                                                                     | TYP | MAX | UNIT    |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----|-----|---------|

| <b>LO INPUT</b>                                                                           |                                                                                     |                                                                         |     |     |         |

| $f_{\text{LO}}$                                                                           | LO frequency range                                                                  | 0.1                                                                     | 2.7 |     | GHz     |

| $P_{\text{LO\_IN}}$                                                                       | LO input power                                                                      | -5                                                                      | 5   |     | dBm     |

|                                                                                           | LO port return loss                                                                 | 15                                                                      |     |     |         |

| <b>LVDS OUTPUT</b>                                                                        |                                                                                     |                                                                         |     |     |         |

| $f_{\text{LVDS\_OUT}}$                                                                    | LVDS output frequency                                                               | 100                                                                     | 800 |     | MHz     |

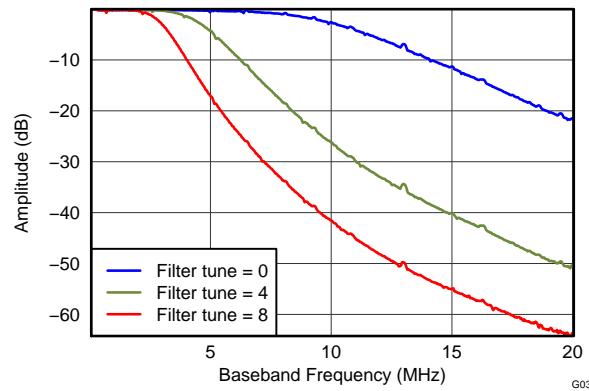

| <b>INTEGRATED BASEBAND FILTER</b>                                                         |                                                                                     |                                                                         |     |     |         |

| Baseband attenuation at setting<br>Filtertune = 8 relative to low-frequency<br>signal     | 2.5 MHz                                                                             | 1                                                                       |     |     | dB      |

|                                                                                           | 5 MHz                                                                               | 18                                                                      |     |     |         |

|                                                                                           | 10 MHz                                                                              | 42                                                                      |     |     |         |

|                                                                                           | 20 MHz                                                                              | 65                                                                      |     |     |         |

| Baseband attenuation at setting<br>Filtertune = 0 relative to low-frequency<br>signal     | 10 MHz                                                                              | 1                                                                       |     |     | dB      |

|                                                                                           | 20 MHz                                                                              | 18                                                                      |     |     |         |

|                                                                                           | 40 MHz                                                                              | 42                                                                      |     |     |         |

|                                                                                           | 55 MHz                                                                              | 58                                                                      |     |     |         |

| Baseband filter phase linearity                                                           | RMS phase deviation from linear phase across<br>minimum or maximum cutoff frequency | 2                                                                       |     |     | Degrees |

| Baseband filter amplitude ripple                                                          | Frequency $< 0.9 \times$ nominal cutoff frequency                                   | 0.5                                                                     |     |     | dB      |

| <b>RF Output Parameters – <math>f_{\text{LO}} = 100 \text{ MHz}</math>, Analog Output</b> |                                                                                     |                                                                         |     |     |         |

| $P_{\text{OUT\_FS}}$                                                                      | Full-scale RF output power                                                          | Full-scale 50-kHz digital sine wave                                     | -1  |     | dBm     |

| IP2                                                                                       | Output IP2                                                                          | Maximum LPF BW setting, $f_{\text{BB}} = 4.5, 5.5 \text{ MHz}$          | 63  |     | dBm     |

| IP3                                                                                       | Output IP3                                                                          | Maximum LPF BW setting, $f_{\text{BB}} = 4.5, 5.5 \text{ MHz}$          | 18  |     | dBm     |

| Carrier feedthrough                                                                       | Unadjusted, $f_{\text{BB}} = 50 \text{ kHz}$ , full scale                           | 45                                                                      |     |     | dBc     |

| Sideband suppression                                                                      | Unadjusted, $f_{\text{BB}} = 50 \text{ kHz}$ , full scale                           | 27                                                                      |     |     | dBc     |

| Output noise floor                                                                        | $\geq 30 \text{ MHz}$ offset, $f_{\text{BB}} = 50 \text{ kHz}$ , full scale         | 137                                                                     |     |     | dBc/Hz  |

| Output return loss                                                                        |                                                                                     | 8.5                                                                     |     |     | dB      |

| <b>RF Output Parameters – <math>f_{\text{LO}} = 450 \text{ MHz}</math>, Analog Output</b> |                                                                                     |                                                                         |     |     |         |

| $P_{\text{OUT\_FS}}$                                                                      | Full-scale RF output power                                                          | Full-scale 50-kHz digital sine wave                                     | 0.2 |     | dBm     |

| IP2                                                                                       | Output IP2                                                                          | Max LPF BW setting, $f_{\text{BB}} = 4.5, 5.5 \text{ MHz}$              | 67  |     | dBm     |

| IP3                                                                                       | Output IP3                                                                          | Max LPF BW setting, $f_{\text{BB}} = 4.5, 5.5 \text{ MHz}$              | 19  |     | dBm     |

| Carrier feedthrough                                                                       | Unadjusted, $f_{\text{BB}} = 50 \text{ kHz}$ , full scale                           | 45                                                                      |     |     | dBc     |

| Sideband Suppression                                                                      | Unadjusted, $f_{\text{BB}} = 50 \text{ kHz}$ , full scale                           | 38                                                                      |     |     | dBc     |

| Output noise floor                                                                        | $\geq 30 \text{ MHz}$ offset, $f_{\text{BB}} = 50 \text{ kHz}$ , full scale         | 143                                                                     |     |     | dBc/Hz  |

| Output return loss                                                                        |                                                                                     | 8.5                                                                     |     |     | dB      |

| <b>RF Output Parameters – <math>f_{\text{LO}} = 850 \text{ MHz}</math>, Analog Output</b> |                                                                                     |                                                                         |     |     |         |

| $P_{\text{OUT\_FS}}$                                                                      | Full-scale RF output power                                                          | Full-scale 50-kHz digital sine wave                                     | 0.3 |     | dBm     |

| IP2                                                                                       | Output IP2                                                                          | Max LPF BW setting, $f_{\text{BB}} = 4.5, 5.5 \text{ MHz}$              | 64  |     | dBm     |

| IP3                                                                                       | Output IP3                                                                          | Max LPF BW setting, $f_{\text{BB}} = 4.5, 5.5 \text{ MHz}$              | 19  |     | dBm     |

| Carrier feedthrough                                                                       | Unadjusted, $f_{\text{BB}} = 50 \text{ kHz}$ , full scale                           | 41                                                                      |     |     | dBc     |

| Sideband suppression                                                                      | Unadjusted, $f_{\text{BB}} = 50 \text{ kHz}$ , full scale                           | 37                                                                      |     |     | dBc     |

| Output noise floor                                                                        | $\geq 30 \text{ MHz}$ offset, $f_{\text{BB}} = 50 \text{ kHz}$ , full scale         | 143                                                                     |     |     | dBc/Hz  |

| Output return loss                                                                        |                                                                                     | 8.5                                                                     |     |     | dB      |

| ACPR                                                                                      | Adjacent-channel power ratio                                                        | 1 WCDMA TM1 signal, PAR = 10 dB,<br>$P_{\text{OUT}} = -10 \text{ dBFS}$ | 65  |     | dBc     |

|                                                                                           |                                                                                     | 10-MHz LTE, PAR = 10 dB, $P_{\text{OUT}} = -10 \text{ dBFS}$            | 61  |     | dBc     |

**AC ELECTRICAL CHARACTERISTICS (continued)**

Typical values at  $T_A = 25^\circ\text{C}$ , full temperature range is  $T_{\text{MIN}} = -40^\circ\text{C}$  to  $T_{\text{MAX}} = 85^\circ\text{C}$ , DAC sampling rate = 65 MSPS, DVDD18 = 1.8 V, CLKVDD18 = 1.8 V, DACVDD18 = 1.8 V, FUSEVDD18 = 1.8 V, IOVDD = 3.3 V, DACVDD33 = 3.3 V, MODVDD33 = 3.3 V, analog output (unless otherwise noted)

| PARAMETER                                                                                                    |                               | TEST CONDITIONS                                                             | MIN   | TYP  | MAX   | UNIT   |

|--------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------------|-------|------|-------|--------|

| ALT1 Alternate-channel power ratio                                                                           |                               | 1 WCDMA TM1 signal, PAR = 10 dB, $P_{\text{OUT}} = -10 \text{ dBFS}$        |       | 66   |       | dBc    |

| <b>RF Output Parameters – <math>f_{\text{LO}} = 2.1 \text{ GHz}</math>, Analog Output</b>                    |                               |                                                                             |       |      |       |        |

| $P_{\text{OUT\_FS}}$                                                                                         | Fullscale RF output power     |                                                                             |       | -1.5 |       | dBm    |

| IP2                                                                                                          | Output IP2                    |                                                                             |       | 50   |       | dBm    |

| IP3                                                                                                          | Output IP3                    |                                                                             |       | 19   |       | dBm    |

|                                                                                                              | Carrier feedthrough           |                                                                             |       | 38   |       | dBc    |

|                                                                                                              | Sideband suppression          |                                                                             |       | 42   |       | dBc    |

|                                                                                                              | Output noise floor            | $\geq 30 \text{ MHz}$ offset, $f_{\text{BB}} = 50 \text{ kHz}$ , full scale |       | 141  |       | dBc/Hz |

|                                                                                                              | Output return loss            |                                                                             |       | 8.5  |       | dB     |

| ACPR                                                                                                         | Adjacent-channel power ratio  | 1 WCDMA TM1 signal, PAR = 10 dB, $P_{\text{OUT}} = -10 \text{ dBFS}$        |       | 65   |       | dBc    |

|                                                                                                              |                               | 20 MHz LTE, PAR = 10 dB, $P_{\text{OUT}} = -10 \text{ dBFS}$                |       | 61   |       | dBc    |

| ALT1                                                                                                         | Alternate-channel power ratio | 1 WCDMA TM1 signal, PAR = 10 dB, $P_{\text{OUT}} = -10 \text{ dBFS}$        |       | 65   |       | dBc    |

| <b>RF Output Parameters – <math>f_{\text{LO}} = 2.7 \text{ GHz}</math>, Analog Output</b>                    |                               |                                                                             |       |      |       |        |

| $P_{\text{OUT\_FS}}$                                                                                         | Full-scale RF output power    |                                                                             |       | -3.6 |       | dBm    |

| IP2                                                                                                          | Output IP2                    |                                                                             |       | 48   |       | dBm    |

| IP3                                                                                                          | Output IP3                    |                                                                             |       | 17   |       | dBm    |

|                                                                                                              | Carrier feedthrough           |                                                                             |       | 36   |       | dBc    |

|                                                                                                              | Sideband suppression          |                                                                             |       | 35   |       | dBc    |

|                                                                                                              | Output noise floor            | $\geq 30 \text{ MHz}$ offset, $f_{\text{BB}} = 50 \text{ kHz}$ , full scale |       | 139  |       | dBc/Hz |

|                                                                                                              | Output return loss            |                                                                             |       | 8.5  |       | dB     |

| <b>RF Output Parameters – <math>f_{\text{LO}} = 622 \text{ MHz}</math>, LVDS Output, <math>\div 4</math></b> |                               |                                                                             |       |      |       |        |

| $V_{\text{OD}}$                                                                                              | Differential output voltage   | Assumes a 100- $\Omega$ differential load                                   | 247   | 350  | 454   | mV     |

| $V_{\text{OC}}$                                                                                              | Common-mode output voltage    |                                                                             | 1.125 | 1.25 | 1.375 | V      |

|                                                                                                              | Output noise floor            | $\geq 13 \text{ MHz}$ offset, $f_{\text{BB}} = 1 \text{ MHz}$               |       |      |       |        |

|                                                                                                              | Carrier feedthrough           | Unadjusted, $f_{\text{BB}} = 50 \text{ kHz}$ , full scale                   |       | 40   |       | dBc    |

|                                                                                                              | Sideband suppression          | Unadjusted, $f_{\text{BB}} = 50 \text{ kHz}$ , full scale                   |       | 40   |       | dBc    |

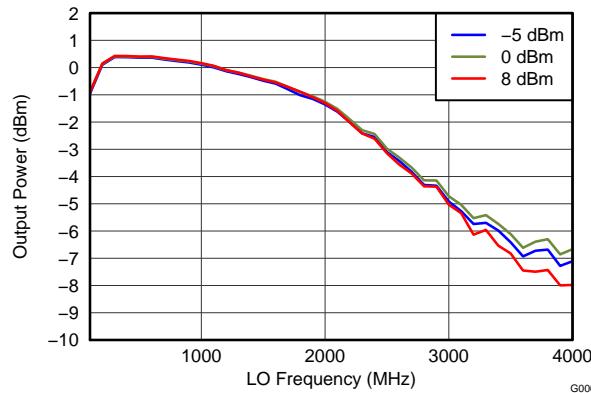

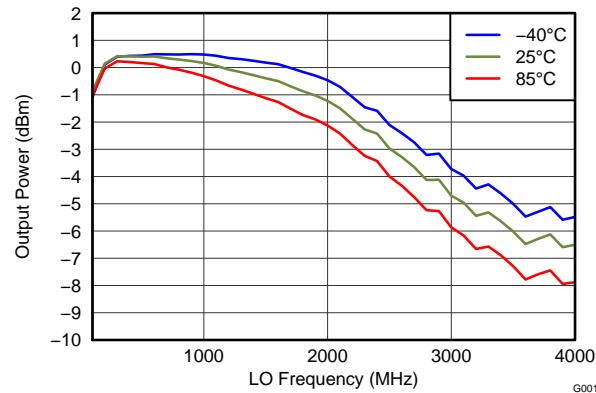

## TYPICAL PERFORMANCE PLOTS

$T_A = 25^\circ\text{C}$ , DAC sampling rate = 65 MSPS, single-tone IF = 1.1 MHz, two-tone IF = 1 MHz and 2 MHz, DVDD18 = 1.8 V, CLKVDD18 = 1.8 V, DACVDD18 = 1.8 V, FUSEVDD18 = 1.8 V, IOVDD = 3.3 V, DACVDD33 = 3.3 V, MODVDD33 = 3.3 V, analog output, unless otherwise noted

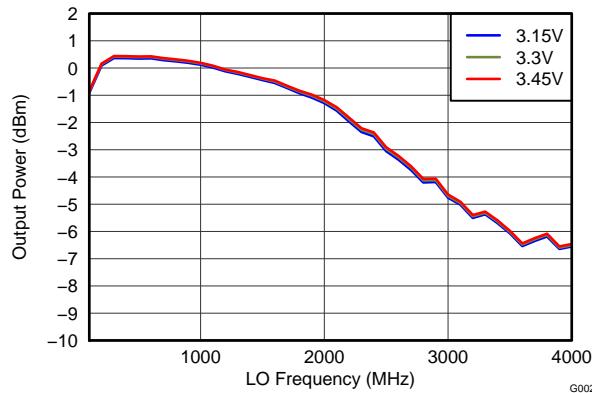

Figure 1. Output Power vs LO Frequency and LO Power

Figure 2. Output Power vs LO Frequency and Temperature

Figure 3. Output Power vs LO Frequency and Supply Voltage

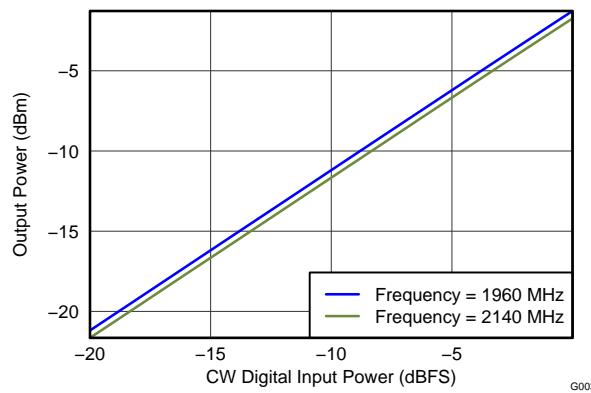

Figure 4. Output Power vs Input Power and LO Frequency

Figure 5. OIP3 vs LO Frequency and LO Power

**TYPICAL PERFORMANCE PLOTS (continued)**

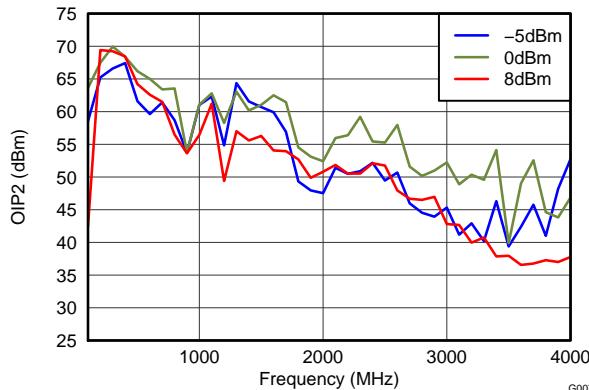

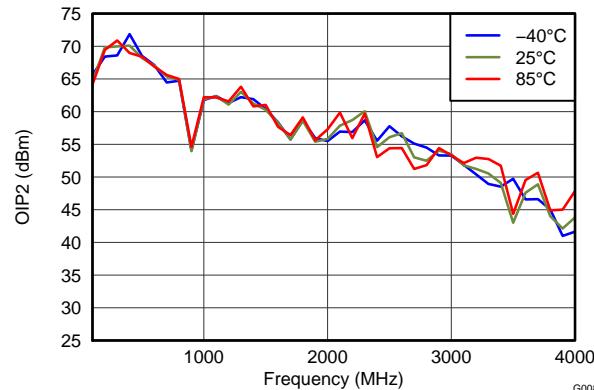

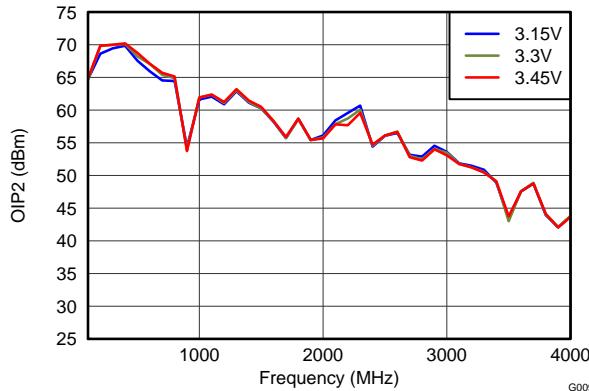

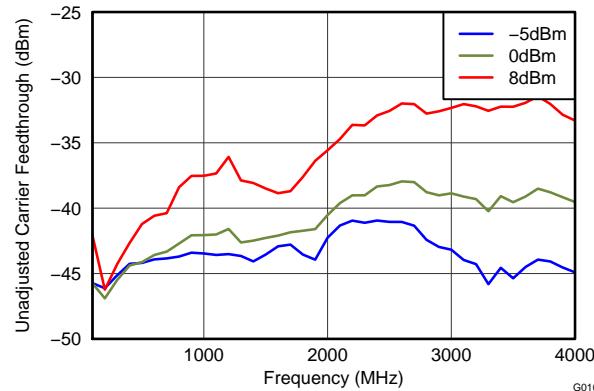

$T_A = 25^\circ\text{C}$ , DAC sampling rate = 65 MSPS, single-tone IF = 1.1 MHz, two-tone IF = 1 MHz and 2 MHz, DVDD18 = 1.8 V, CLKVDD18 = 1.8 V, DACVDD18 = 1.8 V, FUSEVDD18 = 1.8 V, IOVDD = 3.3 V, DACVDD33 = 3.3 V, MODVDD33 = 3.3 V, analog output, unless otherwise noted

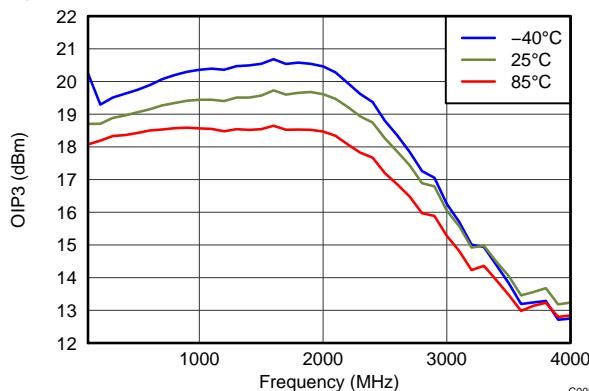

Figure 6. OIP3 vs LO Frequency and Temperature

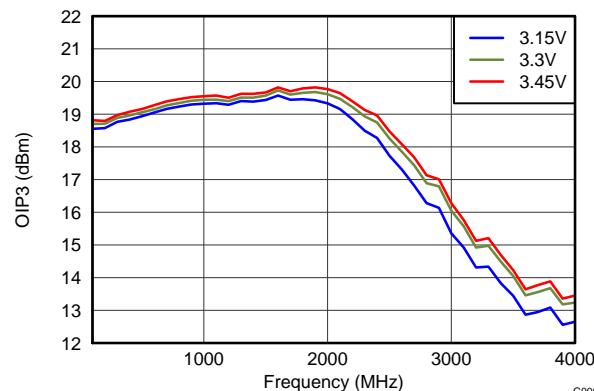

Figure 7. OIP3 vs LO Frequency and Supply Voltage

Figure 8. OIP2 vs LO Frequency and LO Power

Figure 9. OIP2 vs LO Frequency and Temperature

Figure 10. OIP2 vs LO Frequency and Supply Voltage

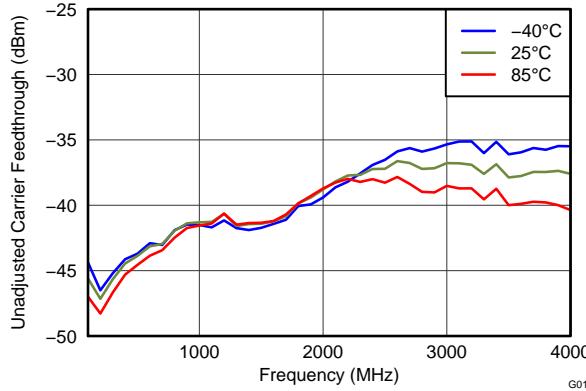

Figure 11. Unadjusted Carrier Feethrough vs LO Frequency and LO Power

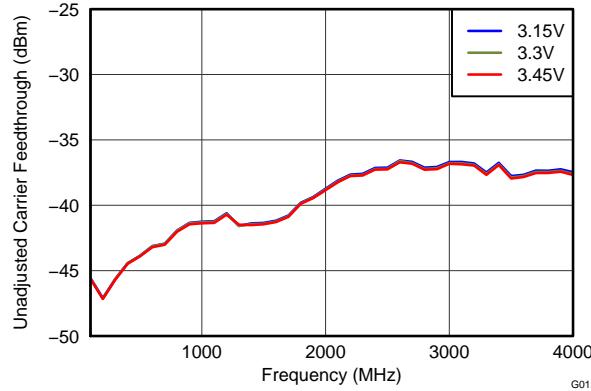

### TYPICAL PERFORMANCE PLOTS (continued)

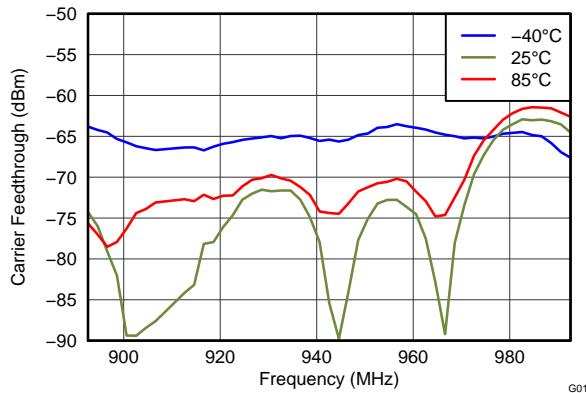

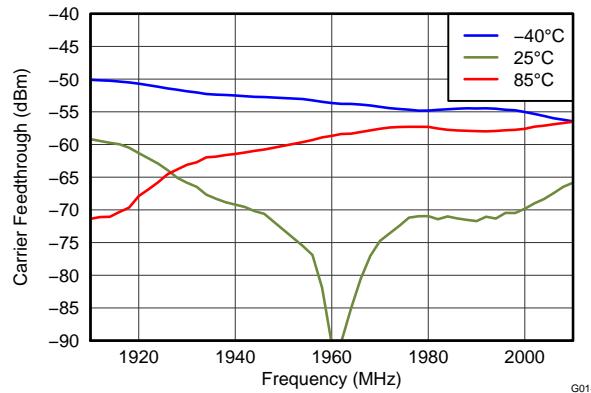

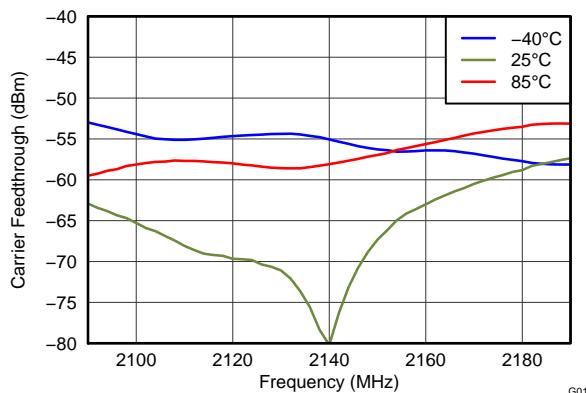

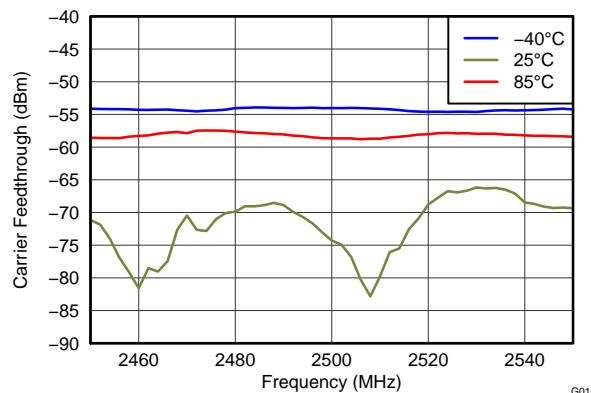

$T_A = 25^\circ\text{C}$ , DAC sampling rate = 65 MSPS, single-tone IF = 1.1 MHz, two-tone IF = 1 MHz and 2 MHz, DVDD18 = 1.8 V, CLKVDD18 = 1.8 V, DACVDD18 = 1.8 V, FUSEVDD18 = 1.8 V, IOVDD = 3.3 V, DACVDD33 = 3.3 V, MODVDD33 = 3.3 V, analog output, unless otherwise noted

Figure 12. Unadjusted Carrier Feethrough vs LO Frequency and Temperature G011

Figure 13. Unadjusted Carrier Feethrough vs LO Frequency and Supply Voltage G012

Figure 14. Adjusted Carrier Feethrough vs LO Frequency and Temperature at 940 MHz G013

Figure 15. Adjusted Carrier Feethrough vs LO Frequency and Temperature at 1960 MHz G014

Figure 16. Adjusted Carrier Feethrough vs LO Frequency and Temperature at 2140 MHz G015

Figure 17. Adjusted Carrier Feethrough vs LO Frequency and Temperature at 2500 MHz G016

### TYPICAL PERFORMANCE PLOTS (continued)

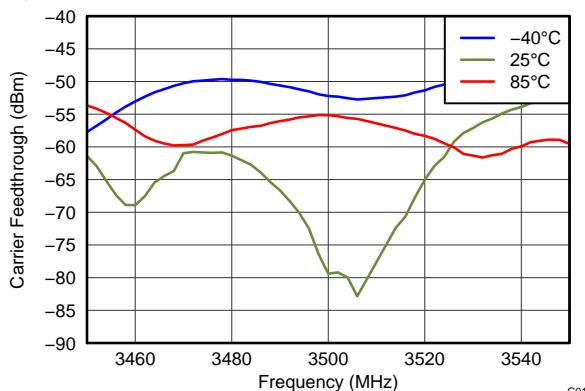

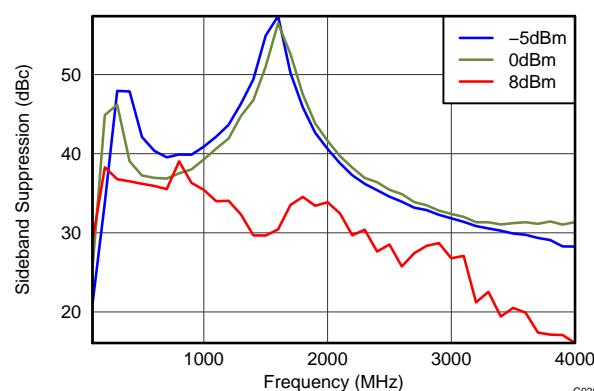

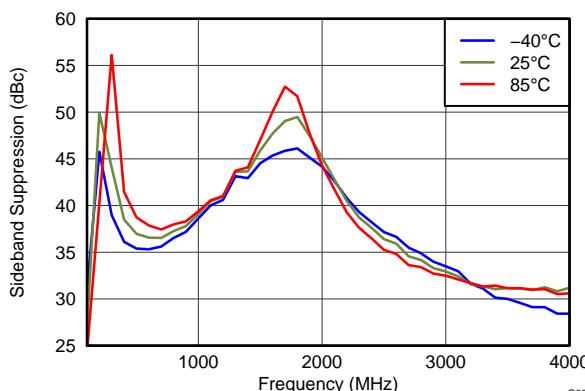

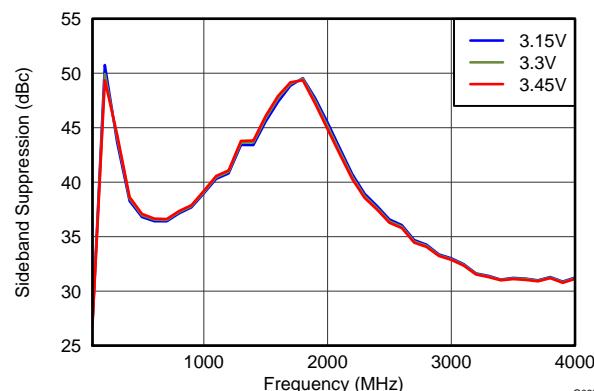

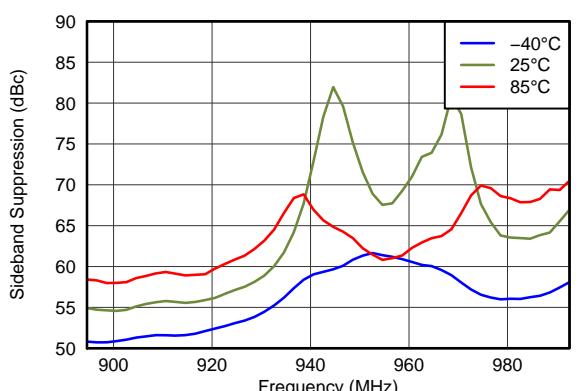

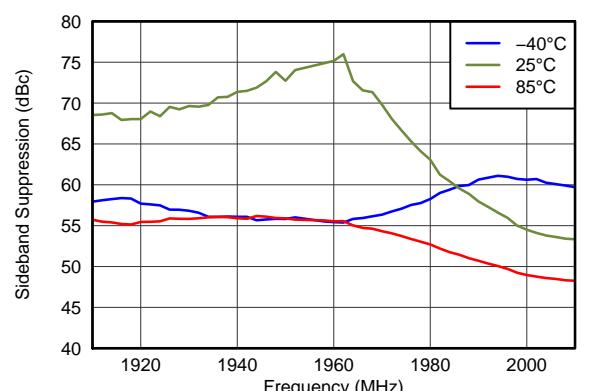

$T_A = 25^\circ\text{C}$ , DAC sampling rate = 65 MSPS, single-tone IF = 1.1 MHz, two-tone IF = 1 MHz and 2 MHz, DVDD18 = 1.8 V, CLKVDD18 = 1.8 V, DACVDD18 = 1.8 V, FUSEVDD18 = 1.8 V, IOVDD = 3.3 V, DACVDD33 = 3.3 V, MODVDD33 = 3.3 V, analog output, unless otherwise noted

Figure 18. Adjusted Carrier Feethrough vs LO Frequency and Temperature at 3500 MHz G017

Figure 19. Unadjusted Sideband Suppression vs LO Frequency and LO Power G029

Figure 20. Unadjusted Sideband Suppression vs LO Frequency and Temperature G028

Figure 21. Unadjusted Sideband Suppression vs LO Frequency and Supply Voltage G027

Figure 22. Adjusted Sideband Suppression vs LO Frequency and Temperature at 940 MHz G018

Figure 23. Adjusted Sideband Suppression vs LO Frequency and Temperature at 1960 MHz G019

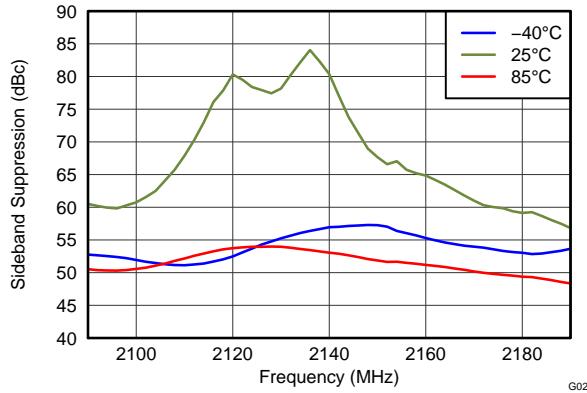

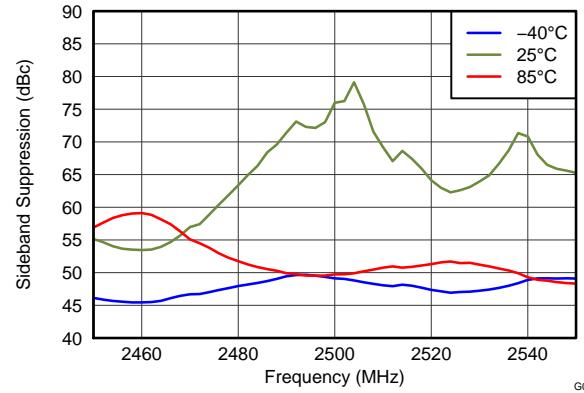

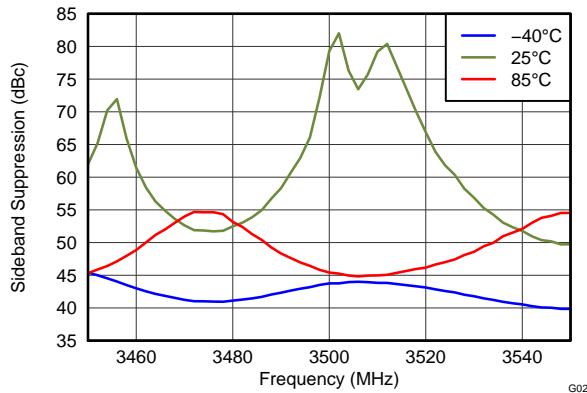

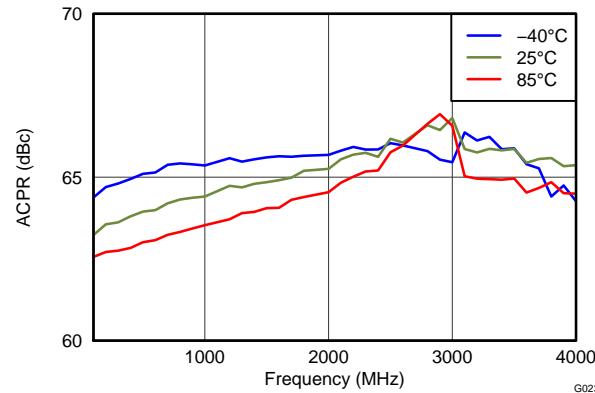

### TYPICAL PERFORMANCE PLOTS (continued)

$T_A = 25^\circ\text{C}$ , DAC sampling rate = 65 MSPS, single-tone IF = 1.1 MHz, two-tone IF = 1 MHz and 2 MHz, DVDD18 = 1.8 V, CLKVDD18 = 1.8 V, DACVDD18 = 1.8 V, FUSEVDD18 = 1.8 V, IOVDD = 3.3 V, DACVDD33 = 3.3 V, MODVDD33 = 3.3 V, analog output, unless otherwise noted

Figure 24. Adjusted Sideband Suppression vs LO Frequency and Temperature at 2140 MHz

Figure 25. Adjusted Sideband Suppression vs LO Frequency and Temperature at 2500 MHz

Figure 26. Adjusted Sideband Suppression vs LO Frequency and Temperature at 3500 MHz

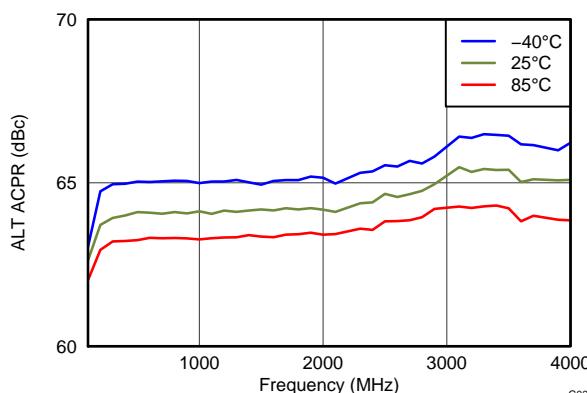

Figure 27. WCDMA Adjacent-Channel Power Ratio (ACPR) vs Temperature

Figure 28. WCDMA Adjacent-Channel Power Ratio (Alt-ACPR) vs Temperature

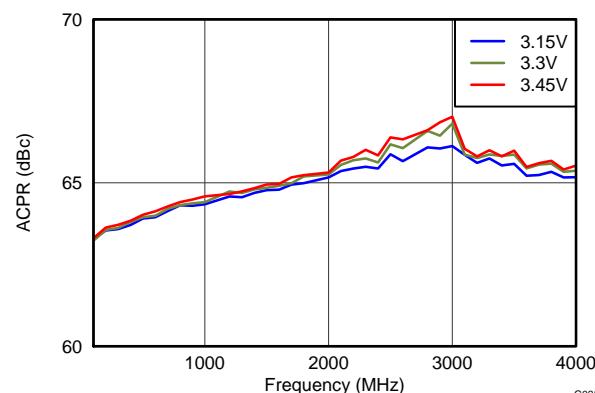

Figure 29. WCDMA Adjacent-Channel Power Ratio (ACPR) vs Supply Voltage

### TYPICAL PERFORMANCE PLOTS (continued)

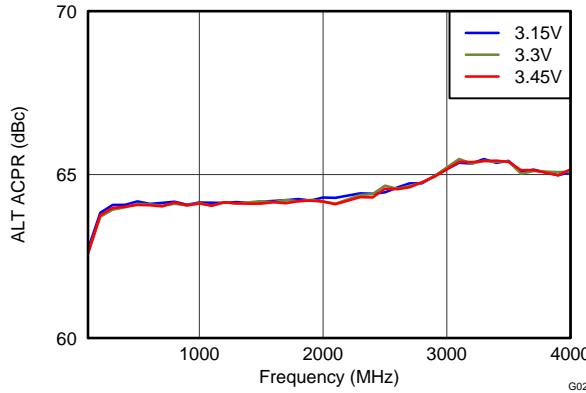

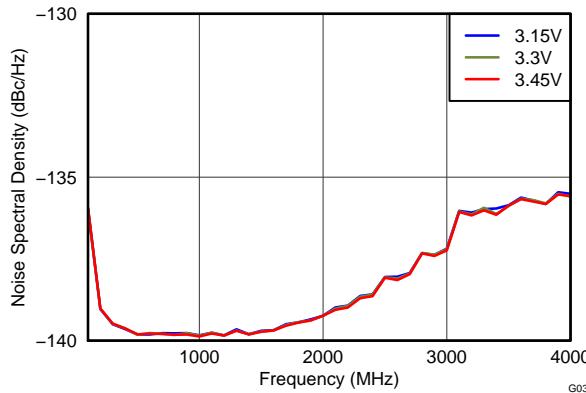

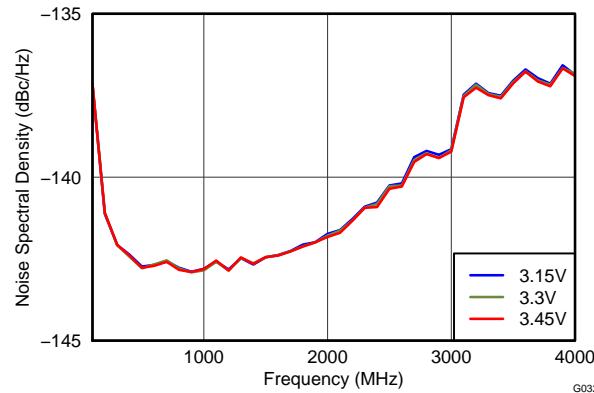

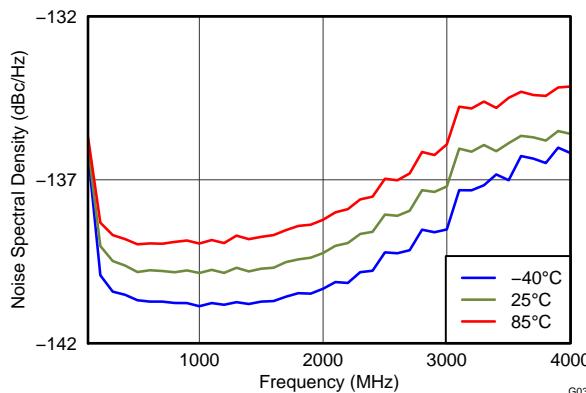

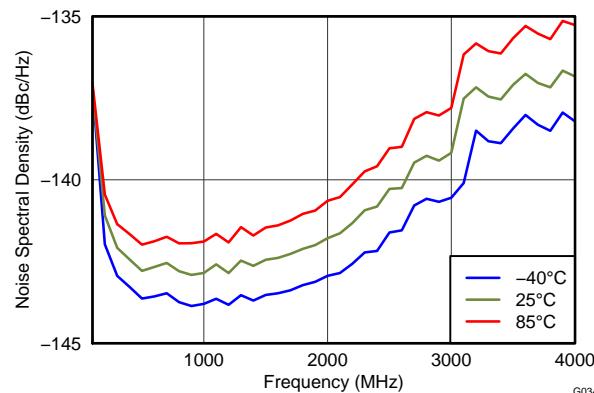

$T_A = 25^\circ\text{C}$ , DAC sampling rate = 65 MSPS, single-tone IF = 1.1 MHz, two-tone IF = 1 MHz and 2 MHz, DVDD18 = 1.8 V, CLKVDD18 = 1.8 V, DACVDD18 = 1.8 V, FUSEVDD18 = 1.8 V, IOVDD = 3.3 V, DACVDD33 = 3.3 V, MODVDD33 = 3.3 V, analog output, unless otherwise noted

Figure 30. WCDMA Adjacent-Channel Power Ratio (Alt-ACPR) vs Supply Voltage

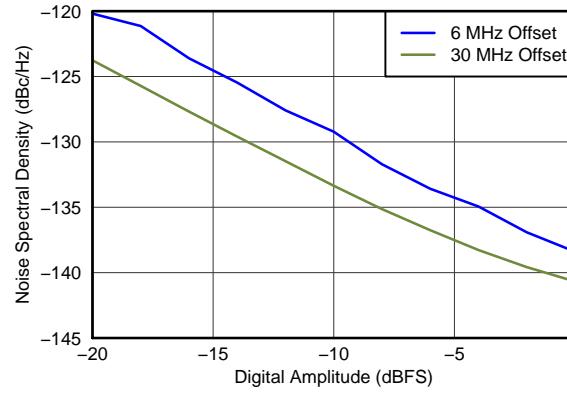

Figure 31. Noise Spectral Density (NSD) vs Input Power and LO Frequency

Figure 32. Noise Spectral Density (NSD) at 6-MHz Offset vs LO Frequency and Supply Voltage

Figure 33. Noise Spectral Density (NSD) at 30-MHz Offset vs LO Frequency and Supply Voltage

Figure 34. Noise Spectral Density (NSD) at 6-MHz Offset vs LO Frequency and Temperature

Figure 35. Noise Spectral Density (NSD) at 30-MHz Offset vs. LO Frequency and Temperature

**TYPICAL PERFORMANCE PLOTS (continued)**

$T_A = 25^\circ\text{C}$ , DAC sampling rate = 65 MSPS, single-tone IF = 1.1 MHz, two-tone IF = 1 MHz and 2 MHz, DVDD18 = 1.8 V, CLKVDD18 = 1.8 V, DACVDD18 = 1.8 V, FUSEVDD18 = 1.8 V, IOVDD = 3.3 V, DACVDD33 = 3.3 V, MODVDD33 = 3.3 V, analog output, unless otherwise noted

**Figure 36. Baseband Filter Response**

## SERIAL INTERFACE

The serial port of the AFE7070 is a flexible serial interface which communicates with industry-standard microprocessors and microcontrollers. The interface provides read/write access to all registers used to define the operating modes of the AFE7070. The serial port is compatible with most synchronous transfer formats and can be configured as a 3- or 4-pin interface by **sif\_4pin** in **CONFIG3 (bit6)**. In both configurations, **SCLK** is the serial interface input clock and **SDENB** is serial interface enable. For the 3-pin configuration, **SDIO** is a bidirectional pin for both data in and data out. For the 4-pin configuration, **SDIO** is data-in only and **ALARM\_SDO** is data-out only. Data is input into the device with the rising edge of **SCLK**. Data is output from the device on the falling edge of **SCLK**.

Each read/write operation is framed by signal **SDENB** (serial data-enable bar) asserted low for 2 to 5 bytes, depending on the data length to be transferred (1–4 bytes). The first frame byte is the instruction cycle, which identifies the following data transfer cycle as read or write, how many bytes to transfer, and the address to which to transfer the data. **Table 1** indicates the function of each bit in the instruction cycle and is followed by a detailed description of each bit. Frame bytes 2 through 5 comprise the data transfer cycle.

**Table 1. Instruction Byte of the Serial Interface**

|             | MSB |    |    |    |    |    |    |    | LSB |

|-------------|-----|----|----|----|----|----|----|----|-----|

| Bit         | 7   | 6  | 5  | 4  | 3  | 2  | 1  | 0  |     |

| Description | R/W | N1 | N0 | A4 | A3 | A2 | A1 | A0 |     |

R/W Identifies the following data transfer cycle as a read or write operation. A high indicates a read operation from the AFE7070, and a low indicates a write operation to the AFE7070.

[N1 : N0] Identifies the number of data bytes to be transferred, as listed in **Table 2**. Data is transferred MSB first.

**Table 2. Number of Transferred Bytes Within One Communication Frame**

| N1 | N0 | DESCRIPTION      |

|----|----|------------------|

| 0  | 0  | Transfer 1 byte  |

| 0  | 1  | Transfer 2 bytes |

| 1  | 0  | Transfer 3 bytes |

| 1  | 1  | Transfer 4 bytes |

[A4 : A0] Identifies the address of the register to be accessed during the read or write operation. For multi-byte transfers, this address is the starting address. Note that the address is written to the AFE7070 MSB first and counts down for each byte.

**Figure 37** shows the serial interface timing diagram for an AFE7070 write operation. **SCLK** is the serial interface clock input to AFE7070. Serial data enable **SDENB** is an active-low input to the AFE7070. **SDIO** is serial data in. Input data to the AFE7070 is clocked on the rising edges of **SCLK**.

Figure 37. Serial Interface Write Timing Diagram

Figure 38 shows the serial interface timing diagram for an AFE7070 read operation. **SCLK** is the serial interface clock input to AFE7070. Serial data enable **SDENB** is an active-low input to the AFE7070. **SDIO** is serial data-in during the instruction cycle. In the 3-pin configuration, **SDIO** is data-out from the AFE7070 during the data transfer cycle(s), while **ALARM\_SDO** is in a high-impedance state. In the 4-pin configuration, **ALARM\_SDO** is data-out from the AFE7070 during the data transfer cycle(s). At the end of the data transfer, **ALARM\_SDO** outputs low on the final falling edge of **SCLK** until the rising edge of **SDENB**, when it enters the high-impedance state.

Figure 38. Serial Interface Read Timing Diagram

## REGISTER DESCRIPTIONS

In the SIF interface there are three types of registers, *NORMAL*, *READ\_ONLY*, and *WRITE\_TO\_CLEAR*. The *NORMAL* register type allows data to be written and read from the register. All 8 bits of the data are registered at the same time, but there is no synchronizing with an internal clock. All register writes are asynchronous with respect to internal clocks. *READ\_ONLY* registers only allow reading of the registers—writing to them has no effect. *WRITE\_TO\_CLEAR* registers are just like *NORMAL* registers in that they can be written and read; however, when the internal signals set a bit high in these registers, that bit stays high until it is written to 0. This way, interrupts are captured and constant until dealt with and cleared.

## Register Map

| Name     | Address | Default | (MSB) bit 7      | bit 6          | bit 5          | bit 4             | bit 3          | bit 2                   | bit 1            | (LSB) bit 0       |

|----------|---------|---------|------------------|----------------|----------------|-------------------|----------------|-------------------------|------------------|-------------------|

| CONFIG0  | 0x00    | 0x10    | div2_dacclk_ena  | div2_sync_ena  | clkio_sel      | clkio_out_ena_n   | data_clk_sel   | data_type               | fifo_ena         | sync_lorQ         |

| CONFIG1  | 0x01    | 0x10    | twos             | iqswap         |                | trim_clk_rc_fltr  |                | daca_complement         | dacb_complement  | lvds_clk_div      |

| CONFIG2  | 0x02    | 0xXX    | Unused           | Unused         | Unused         | Unused            | Unused         | Unused                  | Alarm_fifo_2away | Alarm_fifo_1away  |

| CONFIG3  | 0x03    | 0x10    | alarm_or_sdo_ena | sif_4pin       | SLEEP          | TXENABLE          | SYNC           | sync_sleep_txenable_sel |                  | msb_out           |

| CONFIG4  | 0x04    | 0x0F    | fuse_pd          | mixer_gain     | pd_clkrcvr     | pd_clkrcvr_mask   |                |                         |                  | coarse_dac(3:0)   |

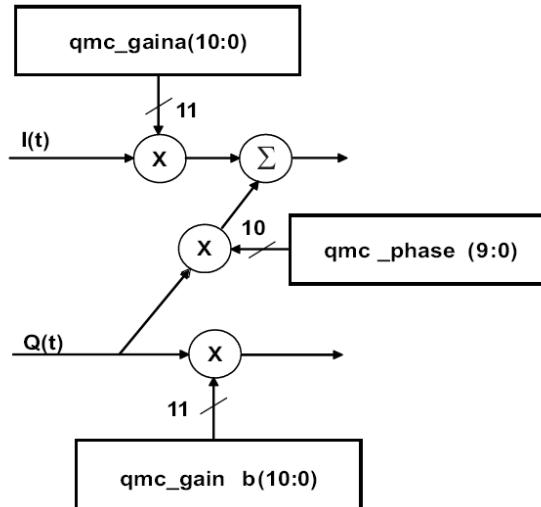

| CONFIG5  | 0x05    | 0x00    | offset_ena       | qmc_corr_ena   | mixer_ena      |                   |                |                         |                  | filter_tune(4:0)  |

| CONFIG6  | 0x06    | 0x00    | pd_lvds          | pd_rf_out      | pd_dac         | pd_analogout      | pd_lvds_mask   | pd_tf_out_mask          | pd_dac_mask      | pd_analogout_mask |

| CONFIG7  | 0x07    | 0x13    | mask_2away       | mask_1away     | fifo_sync_mask | fifo_offset       | alarm2away_ena |                         |                  | alarm_1away_ena   |

| CONFIG8  | 0x08    | 0x00    |                  |                |                | qmc_offseta(7:0)  |                |                         |                  |                   |

| CONFIG9  | 0x09    | 0x7A    |                  |                |                | qmc_offsetb(7:0)  |                |                         |                  |                   |

| CONFIG10 | 0x0A    | 0xB6    |                  |                |                | qmc_offseta(12:8) |                | Unused                  | Unused           | Unused            |

| CONFIG11 | 0x0B    | 0xEA    |                  |                |                | qmc_offsetb(12:8) |                | Unused                  | Unused           | Unused            |

| CONFIG12 | 0x0C    | 0x45    |                  |                |                | qmc_gaina(7:0)    |                |                         |                  |                   |

| CONFIG13 | 0x0D    | 0x1A    |                  |                |                | qmc_gainb(7:0)    |                |                         |                  |                   |

| CONFIG14 | 0x0E    | 0x16    |                  |                |                | qmc_phase(7:0)    |                |                         |                  |                   |

| CONFIG15 | 0x0F    | 0xAA    |                  | qmc_phase(9:8) |                | qmc_gaini(10:8)   |                |                         |                  | qmc_gainq(10:8)   |

| CONFIG16 | 0x10    | 0xC6    |                  |                |                | freq(7:0)         |                |                         |                  |                   |

| CONFIG17 | 0x11    | 0x24    |                  |                |                | freq(15:8)        |                |                         |                  |                   |

| CONFIG18 | 0x12    | 0x02    |                  |                |                | freq(23:16)       |                |                         |                  |                   |

| CONFIG19 | 0x13    | 0x00    |                  |                |                | freq(31:24)       |                |                         |                  |                   |

| CONFIG20 | 0x14    | 0x00    |                  |                |                | phase(7:0)        |                |                         |                  |                   |

| CONFIG21 | 0x15    | 0x00    |                  |                |                | phase(15:8)       |                |                         |                  |                   |

| CONFIG22 | 0x16    | 0x00    |                  |                |                | Reserved          |                |                         |                  |                   |

| CONFIG23 | 0x17    | 0xXX    |                  |                |                | Reserved          |                |                         |                  |                   |

| CONFIG24 | 0x18    | 0xXX    |                  |                |                | Reserved          |                |                         |                  |                   |

| CONFIG25 | 0x19    | 0xXX    |                  |                |                | Reserved          |                |                         |                  |                   |

| CONFIG26 | 0x1A    | 0xXX    |                  |                |                | Reserved          |                |                         |                  |                   |

| CONFIG27 | 0x1B    | 0xXX    |                  |                |                | Reserved          |                |                         |                  |                   |

| CONFIG28 | 0x1C    | 0xXX    |                  |                |                | Reserved          |                |                         |                  |                   |

| CONFIG29 | 0x1D    | 0xXX    |                  |                |                | Reserved          |                |                         |                  |                   |

| CONFIG30 | 0x1E    | 0xXX    |                  |                |                | Reserved          |                |                         |                  |                   |

| CONFIG31 | 0x1F    | 0x82    | titest_voh       | titest_vol     |                |                   |                |                         |                  | Version(5:0)      |

**Register name: CONFIG0; Address: 0x00**

|                 |               |           |                 |              |           |          |           | BIT 7 |  |  |  |  |  |  |  |   | BIT 0 |

|-----------------|---------------|-----------|-----------------|--------------|-----------|----------|-----------|-------|--|--|--|--|--|--|--|---|-------|

| div2_dacclk_ena | div2_sync_ena | clkio_sel | clkio_out_ena_n | data_clk_sel | data_type | fifo_ena | sync_lorQ |       |  |  |  |  |  |  |  |   |       |

| 0               | 0             | 0         | 1               | 0            | 0         | 0        | 0         |       |  |  |  |  |  |  |  | 0 |       |

**Table 3. Clock Mode Memory Programming**

| Mode                               | div2_dacclk_ena | div2_sync_ena | clkio_sel | clkio_out_ena_n | data_clk_sel |

|------------------------------------|-----------------|---------------|-----------|-----------------|--------------|

| Dual input clock(00)               | 1               | 0             | 1         | 1               | 0            |

| Dual output clock (01)             | 1               | 1             | 0         | 0               | 0            |

| Single differential DDR clock (10) | 0               | 0             | 0         | 1               | 1            |

| Single differential SDR clock (11) | 0               | 0             | 1         | 1               | 1            |

**div2\_dacclk\_ena:** When set to 1, this enables the divide-by-2 in the DAC clock path. This must be set to 1 when in dual-input clock mode or dual-output clock mode.

**div2\_sync\_ena:** When set to 1, the divide-by-2 is synchronized with the iq\_flag. It is only useful in the dual-clock modes when the divide-by-2 is enabled. Care must be taken to ensure the input data and DAC clocks are correctly aligned.

**clkio\_sel:** This bit is used to determine which clock is used to latch the input data. This should be set according to [Table 3](#).

**clkio\_out\_ena\_n:** When set to 0, the clock CLK\_IO is an output. Depending on the mode, it should be set according to [Table 3](#).

**data\_clk\_sel:** This bit is used to determine which clock is used to latch the input data. This should be set according to [Table 3](#).

**data\_type:** When asserted, the phase data is presented at the data interface. The phase data is then updated with each clock. The phase register then holds the value of the I and Q data to be used with the mix operation.

**fifo\_ena:** When asserted, the FIFO is enabled. Used in dual-input clock mode only. In all other modes, the FIFO is bypassed.

**sync\_lorQ:** When set to 0, sync is latched on the I phase of the input clock. When set to 1, sync is detected on the Q phase of the clock and is sent to the rest of the chip when the next I data is presented.

## AFE7070

SLOS761D – FEBRUARY 2012–REVISED JANUARY 2013

[www.ti.com](http://www.ti.com)

**Register name: CONFIG1; Address: 0x01**

| BIT 7 |        |                  |                 |                 |              | BIT 0 |   |

|-------|--------|------------------|-----------------|-----------------|--------------|-------|---|

| twos  | iqswap | trim_clk_rc_fltr | daca_complement | dacb_complement | lvds_clk_div |       |   |

| 0     | 0      | 0                | 1               | 0               | 0            | X     | X |

twos: When asserted, the input to the chip is 2s complement, otherwise offset binary.

iqswap: When asserted, the DACA data is driven onto DACB and reverse.