# **Excellent Integrated System Limited**

Stocking Distributor

Click to view price, real time Inventory, Delivery & Lifecycle Information:

NXP Semiconductors M68MULTILINK08

For any questions, you can email us directly: <u>sales@integrated-circuit.com</u>

# Freescale Semiconductor, Inc.

January 2003

# MON08 MULTILINK USER MANUAL

©P&E Microcomputer Systems, Inc., 2001, 2002; All Rights Reserved

For More Information On This Product, Go to: www.freescale.com

#### **Freescale Semiconductor, Inc.**

#### **Purchase Agreement**

P&E Microcomputer Systems, Inc. reserves the right to make changes without further notice to any products herein to improve reliability, function, or design. P&E Microcomputer Systems, Inc. does not assume any liability arising out of the application or use of any product or circuit described herein.

This software and accompanying documentation are protected by United States Copyright law and also by International Treaty provisions. Any use of this software in violation of copyright law or the terms of this agreement will be prosecuted.

All the software described in this document is copyrighted by P&E Microcomputer Systems, Inc. Copyright notices have been included in the software.

P&E Microcomputer Systems authorizes you to make archival copies of the software and documentation for the sole purpose of back-up and protecting your investment from loss. Under no circumstances may you copy this software or documentation for the purpose of distribution to others. Under no conditions may you remove the copyright notices from this software or documentation.

This software may be used by one person on as many computers as that person uses, provided that the software is never used on two computers at the same time. P&E expects that group programming projects making use of this software will purchase a copy of the software and documentation for each user in the group. Contact P&E for volume discounts and site licensing agreements.

P&E Microcomputer Systems does not assume any liability for the use of this software beyond the original purchase price of the software. In no event will P&E Microcomputer Systems be liable for additional damages, including any lost profits, lost savings or other incidental or consequential damages arising out of the use or inability to use these programs, even if P&E Microcomputer Systems has been advised of the possibility of such damage.

By using this software, you accept the terms of this agreement.

MS-DOS & Windows are registered trademarks of Microsoft Corporation. Motorola is a registered trademark of Motorola, Inc. IBM is a registered trademark of IBM corporation.

P&E Microcomputer Systems, Inc. P.O. Box 2044 Woburn, MA 01888 617-353-9206 www.pemicro.com

Manual version 1.03

For More Information On This Product, Go to: www.freescale.com

| 1 | INTF | RODUCTION                          | 5  |

|---|------|------------------------------------|----|

| 2 | MON  | 108 MULTILINK HARDWARE             | 5  |

|   | 2.1  | MON08 MULTILINK Power Supply       | 5  |

|   | 2.2  | Optional Oscillator                |    |

|   | 2.3  | Target MON08 Connector             | 6  |

|   | 2.4  | Ribbon Cable                       | 8  |

|   | 2.5  | Target Power Management            | 8  |

|   | 2.6  | Parallel Port                      | 8  |

| 3 | TAR  | GET MON08 HEADER PINOUTS           | 9  |

|   | 3.1  | 68HC908AB                          | 9  |

|   | 3.2  | 68HC908AP                          | 10 |

|   | 3.3  | 68HC908AS                          | 11 |

|   | 3.4  | 68HC908AT                          | 11 |

|   | 3.5  | 68HC908AZ                          | 12 |

|   | 3.6  | 68HC908BD                          | 13 |

|   | 3.7  | 68HC908EY                          | 14 |

|   | 3.8  | 68HC908GP                          | 14 |

|   | 3.9  | 68HC908GR16                        | 15 |

|   | 3.10 | 68HC908GR4/8                       | 16 |

|   | 3.11 | 68HC908GT                          | 17 |

|   | 3.12 | 68HC908GZ                          | 17 |

|   | 3.13 | 68HC908JB1/8                       | 18 |

|   | 3.14 | 68HC908JB16                        | 19 |

|   | 3.15 | 68HC908JG                          | 20 |

|   | 3.16 | 68HC908JK                          | 20 |

|   | 3.17 | 68HC908JL                          | 21 |

|   | 3.18 | 68HC908KX                          | 22 |

|   | 3.19 | 68HC908LD                          | 23 |

|   | 3.20 | 68HC908LJ                          | 23 |

|   | 3.21 | 68HC908MR4/8                       | 24 |

|   | 3.22 | 68HC908MR16/32                     | 25 |

|   | 3.23 | 68HC908QT                          | 26 |

|   | 3.24 | 68HC908QY                          | 26 |

|   | 3.25 | 68HC908RF                          | 27 |

|   | 3.26 | 68HC908RK                          |    |

|   | 3.27 | 68HC908SR                          | 29 |

| 4 | PC-H | IOSTED DEBUG/PROGRAMMING SOFTWARE  |    |

|   | 4.1  | P&E Microcomputer Systems Software |    |

|   | 4.2  | Metrowerks Software                |    |

# Freescale Semiconductor, Inc. P&E Microcomputer Systems, Inc.

| 12  | Torget Connection And Security | y Dialog | 20   |

|-----|--------------------------------|----------|------|

| 4.5 | Target Connection And Security | y Dialog | - 30 |

MON08 Multilink User Manual

## **Freescale Semiconductor, Inc.** Microcomputer Systems, Inc.

#### **MON08 MULTILINK**

# **1** INTRODUCTION

The MON08 MULTILINK is an interface cable whose purpose is to allow debug and programming of 68HC08 devices via the MON08 debug port. The MON08 MULTILINK connects the target to the PC via a standard parallel port.

Some of the features that make the MON08 MULTILINK versatile are:

a. Software configurable port pin settings for Monitor ROM entrance.

b. Works with 2V, 3V, and 5V targets with internal bus frequency ranges from 1MHz to 8MHz.

c. Automatically detects target internal bus frequency and sets communications baud rate.

d. May optionally provide either 2,3, or 5V power @ 125mA to the target via Pin 15 of the MON08 header.

e. Provides 5V 4.9152 MHz oscillator signal to overdrive target crystal and RC clock circuitry.

### 2 MON08 MULTILINK HARDWARE

#### 2.1 MON08 MULTILINK Power Supply

The MON08 MULTILINK requires a regulated 9V DC Center Positive power supply with 1.3/3.5mm female plug. The MON08 MULTILINK derives its power from the Power Jack located beside the MON08 connector. When the cable is powered up, the Green LED will be on. If the target is powered, the Yellow LED will be on.

#### 2.2 Optional Oscillator

The MON08 MULTILINK provides a 5V 4.9152 MHz oscillator clock signal to Pin 13 of the MON08 Connector. If the target is a 5V system, the user may use this clock signal to overdrive the target RC or crystal circuitry. If this signal is not used, just leave Pin 13 of the target MON08 header unconnected.

> Freescale Semiconductor, Inc. Microcomputer

Systems, Inc.

MON08 MULTILINK

Please note that if the target already uses an oscillator as its clock, the MON08 MULTILINK will NOT be able to overdrive it. The clock should have sufficient drive to be used with a target system even if the target system has an RC circuit or crystal connected.

### 2.3 Target MON08 Connector

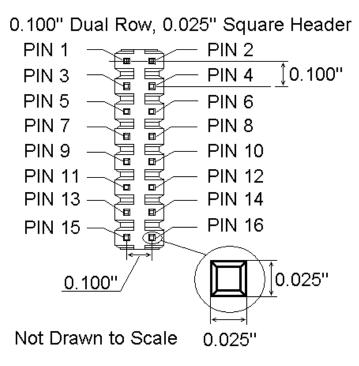

The MON08 MULTILINK requires the target to have a standard 16-position 0.100-inch pitch dual row 0.025-inch square header. The mechanical drawing is shown in **Figure 2-1**.

Figure 2-1: 16-Pin Header Mechanical Drawing

The MON08 Connector adopts the standard pin-out from MON08 debugging (as used on different ICS boards) with some modifications. The general pin-out is as follows:

| PIN 1 - <b>N</b><br>PIN 3 - <b>N</b>   |       | - PIN 2<br>- PIN 4                             |

|----------------------------------------|-------|------------------------------------------------|

| PIN 5 - N                              | C IRQ | <b>-</b> PIN 6                                 |

| PIN 7 - N<br>PIN 9 - N                 |       | <ul><li>I - PIN 8</li><li>J - PIN 10</li></ul> |

| PIN11 - N<br>PIN13 - <b>OS</b>         |       | <b>5</b> - PIN12<br><b>7</b> - PIN14           |

| PIN13 - <b>US</b><br>PIN15 - <b>Vo</b> |       | <b>3</b> - PIN14<br><b>3</b> - PIN16           |

**Freescale Semiconductor, Inc.** Microcomputer Systems, Inc.

MON08 MULTILINK

If viewed right-side-up from the rear (open) end of the cable housing, the MON08 Multilink header looks like this:

Figure 2-2: MON08 Connector Pin Location

Please note that **NC** designates that these pins are reserved for future P&E use. **Make sure you do not connect any signal to these lines**.

The **MON4-MON8** signals are software configurable to support connections to different 68HC908 devices. Depending upon the device, either the MON4 or MON5 pin is the single-wire communications line (which usually corresponds to PORTA0 or PORTB0). The rest of the lines are either no connect or are port lines which must be driven to particular values upon reset. The MON08 MULTILINK software lists the target processor types and their corresponding pin-outs for user references. The software also selects the single-wire communications line according to the target processor type.

#### **MON08 MULTILINK**

#### 2.4 **Ribbon Cable**

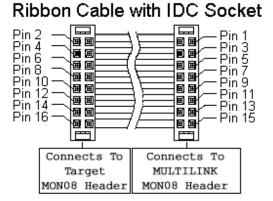

The MON08 MULTILINK communicates with the target through a 16-pin ribbon cable with 0.100-inch centerline dual row socket IDC assembly (not keyed). The ribbon cable is designed such that the MON08 MULTILINK MON08 Connector and the target MON08 Header have the same pinout. i.e. The Pin 1 of the MON08 MULTILINK MON08 Connector is connected to the Pin 1 of the target MON08 Header. Figure 2-3 sketches the connection mechanism (looking down into the sockets).

Figure 2-3: Ribbon Cable Diagram

#### 2.5 **Target Power Management**

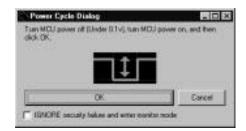

The PC software can be configured to have the MON08 MULTILINK drive 2V, 3V, or 5V power to the target on Pin 15 of the MON08 connector. The "device power" option on the connection dialog specifies the voltage level to source. Figure 2-4 shows the device power settings.

| Class V, VI, VII - CYCLONE and MON08 MULTILINK Settings    | 1 2                                                                                                                               |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Parallel Port: 1                                           | MON08 Pinout: NC $\circ$ $\circ$ GND                                                                                              |

| Device Type: GP 🔻                                          | $NC \diamond \diamond RST$<br>$NC \diamond \diamond IRO = HighV$                                                                  |

|                                                            | $NC \circ \circ PTA0 = COM$                                                                                                       |

| Device Power: 3 Volts, Generated/Switched by P&E Interface | $\bullet \mathbf{NC} \diamond \mathbf{PTA7} = 0$                                                                                  |

| Device Clock: 1Mhz-32Mhz, Target self-clocked              | $\blacksquare \qquad \qquad \mathbf{NC} \diamond \diamond \mathbf{PTC0} = 1 \\ \mathbf{OSC} \diamond \diamond \mathbf{PTC1} = 0 $ |

| Clock Divider: 2                                           | Vout $\circ \circ$ PTC3 = 1                                                                                                       |

| , <u> </u>                                                 | 15 16                                                                                                                             |

Figure 2-4: MON08 MULTILINK Pinout Example

#### 2.6 **Parallel Port**

The MON08 MULTILINK connects to the PC via the 25-pin female parallel port connector. The BIOS settings for the parallel port should be one of the

MON08 Multilink User Manual

## Freescale Semiconductor, Inc. Microcomputer Systems, Inc.

#### MON08 MULTILINK

following: SPP, Normal, Standard, Output Only, Unidirectional, AT. Try to avoid ECP, EPP, or PS/2 bi-directional.

If a parallel port extension cable is used, the parallel cable connecting the PC parallel port and the MON08 MULTILINK cable must be IEEE1284 compliant.

# 3 TARGET MON08 HEADER PINOUTS

This chapter details the MON08 connector signals according to the individual target MCU types.

#### 3.1 68HC908AB

| Port Pins Settings During Reset |                  |       |                                                      |       |  |  |

|---------------------------------|------------------|-------|------------------------------------------------------|-------|--|--|

|                                 | ngs During Reser | Pin l | $NC \square \circ GND$                               | Pin 2 |  |  |

| Target Type                     | AB               |       | $NC \circ \circ RST$                                 |       |  |  |

| Targer Type 310                 |                  |       | NC 🜼 🗠 IRQ = Hi                                      | ghV   |  |  |

|                                 |                  |       | $NC \circ \circ NC$                                  |       |  |  |

|                                 |                  |       | $\mathbf{NC} \circ \mathbf{OPTA0} = \mathbf{C}$      | OM    |  |  |

|                                 |                  |       | $NC \circ OPTC0 = 1$                                 |       |  |  |

|                                 |                  |       | $\mathbf{OSC} \ \circ \ \ \circ \ \mathbf{PTC1} = 0$ |       |  |  |

|                                 |                  | Pin15 | <b>Vout</b> $\circ$ $\circ$ <b>PTC3 = 0</b>          | Pinl6 |  |  |

Figure 3-1: 68HC908AB Family MON08 Pinout

The target GND is connected to the Pin 2 of the target MON08 Header.

The target RESET line is directly connected to the Pin 4 of the target MON08 Header.

Alternatively, the user may pull up the RESET line to target VDD. In which case the user does not need to connect this signal to the target MON08 Header.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTA0 from the target processor is connected to the target MON08 Header Pin 10, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

PORTC0, PORTC1 and PORTC3 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

Alternatively, the user may pull up PORTC0 and pull down PORTC1, and pull up/down PORTC3 for clock division. In which case the user does not need to connect these signals to the target MON08 Header.

**MON08 MULTILINK**

# Freescale Semiconductor, Inc. Microcomputer

L Systems, Inc.

#### 3.2 68HC908AP

| - Dave Dive Satt                | nga Duning Pacat |                  |                         |                |

|---------------------------------|------------------|------------------|-------------------------|----------------|

| Port Pins Settings During Reset |                  | Pin l            | NC $\square$ $\diamond$ | GND Pin 2      |

| Target Type AP                  |                  | $NC \circ \circ$ | RST                     |                |

| Targer Type Min                 |                  |                  | $NC \circ \circ$        | IRQ = HighV    |

|                                 |                  |                  | $NC \circ \ \circ$      | NC             |

|                                 |                  |                  | $NC \circ \ \circ$      | PTA0 = COM     |

|                                 |                  |                  | $NC \circ \ \circ$      | PTA2 = 0       |

|                                 |                  | (                | osc ∘ ∘                 | PTA1 = 1       |

|                                 |                  | Pin15 V          | Vout $\circ$ $\circ$    | PTB0 = 0 Pin16 |

#### Figure 3-2: 68HC908AP Family MON08 Pinout

The target GND is connected to the Pin 2 of the target MON08 Header.

The target RESET line is directly connected to the Pin 4 of the target MON08 Header.

Alternatively, the user may pull up the RESET line to target VDD. In which case the user does not need to connect this signal to the target MON08 Header.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTA0 from the target processor is connected to the target MON08 Header Pin 10, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

PORTA2, PORTA1 and PORTB0 are used for entering monitor mode. By default the user may bring these signals out to the target MON08 Header.

Alternatively, the user may pull down PORTA2 and pull up PORTA1, and pull up/down PORTB0 for clock division. In which case the user does not need to connect these signals to the target MON08 Header.

# **Freescale Semiconductor, Inc.** Microcomputer Systems, Inc.

MON08 MULTILINK

#### 3.3 68HC908AS

| Port Pins Settings During Reset |  |       | NC $\square \circ$ GND Pin 2        |

|---------------------------------|--|-------|-------------------------------------|

| Towned Trans                    |  | 1001  | $NC \circ \circ RST$                |

| Target Type As                  |  |       | $NC \circ \circ IRQ = HighV$        |

|                                 |  |       | $\mathbf{NC} \circ \mathbf{ONC}$    |

|                                 |  |       | $NC \circ \circ PTA0 = COM$         |

|                                 |  |       | $NC \circ \circ PTC0 = 1$           |

|                                 |  |       | $OSC \circ \circ PTC1 = 0$          |

|                                 |  | Pin15 | Vout $\circ$ $\circ$ PTC3 = 0 Pin16 |

#### Figure 3-3: 68HC908AS Family MON08 Pinout

The target GND is connected to the Pin 2 of the target MON08 Header.

The target RESET line is directly connected to the Pin 4 of the target MON08 Header.

Alternatively, the user may pull up the RESET line to target VDD. In which case the user does not need to connect this signal to the target MON08 Header.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTA0 from the target processor is connected to the target MON08 Header Pin 10, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

PORTC0, PORTC1 and PORTC3 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

Alternatively, the user may pull up PORTC0 and pull down PORTC1, and pull up/down PORTC3 for clock division. In which case the user does not need to connect these signals to the target MON08 Header.

#### 3.4 68HC908AT

| - Port Pine Setti | nge During Pocot                |                       |                       |                             |

|-------------------|---------------------------------|-----------------------|-----------------------|-----------------------------|

| TOTT IS SEE       | Port Pins Settings During Reset |                       | NC 🗆                  | ○ GND Pin 2                 |

| Target Type AT    |                                 | $\mathbf{NC} \ \circ$ | ○ RST                 |                             |

| - anger - ype     | <u></u>                         |                       | $\mathbf{NC} \ \circ$ | ◇ IRQ = HighV               |

|                   |                                 |                       | $\mathbf{NC} \ \circ$ | • NC                        |

|                   |                                 |                       | NC $\diamond$         | $\circ$ <b>PTA0 = COM</b>   |

|                   |                                 |                       | NC $\diamond$         | • <b>PTC0 = 1</b>           |

|                   |                                 |                       | osc 🜼                 | • PTC1 = 0                  |

|                   |                                 | Pin15                 | Vout $\circ$          | <pre>o PTC3 = 0 Pin16</pre> |

Figure 3-4: 68HC908AT Family MON08 Pinout

eescale Semiconductor, Inc.

#### **MON08 MULTILINK**

The target GND is connected to the Pin 2 of the target MON08 Header.

The target RESET line is directly connected to the Pin 4 of the target MON08 Header.

Alternatively, the user may pull up the RESET line to target VDD. In which case the user does not need to connect this signal to the target MON08 Header.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTA0 from the target processor is connected to the target MON08 Header Pin 10, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

PORTC0, PORTC1 and PORTC3 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

Alternatively, the user may pull up PORTC0 and pull down PORTC1, and pull up/down PORTC3 for clock division. In which case the user does not need to connect these signals to the target MON08 Header.

#### 3.5 68HC908AZ

| - Dout Ding Sotti               | ngo Duning Pocot |       |                                     |

|---------------------------------|------------------|-------|-------------------------------------|

| Port Pins Settings During Reset |                  | Pin l | NC □ ◇ GND Pin 2                    |

| Target Type                     | A7.              | 7 NO  | NC $\circ$ $\circ$ RST              |

| Target Type 147                 |                  |       | $NC \circ \circ IRQ = HighV$        |

|                                 |                  |       | $NC \circ \circ NC$                 |

|                                 |                  |       | $NC \diamond \phi PTA0 = COM$       |

|                                 |                  |       | $NC \circ \circ PTC0 = 1$           |

|                                 |                  |       | $OSC \circ \circ PTC1 = 0$          |

|                                 |                  | Pin15 | Vout $\circ$ $\circ$ PTC3 = 0 Pin16 |

Figure 3-5: 68HC908AZ Family MON08 Pinout

The target GND is connected to the Pin 2 of the target MON08 Header.

The target RESET line is directly connected to the Pin 4 of the target MON08 Header.

Alternatively, the user may pull up the RESET line to target VDD. In which case the user does not need to connect this signal to the target MON08 Header.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTA0 from the target processor is connected to the target MON08 Header Pin 10, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

## Freescale Semiconductor, Inc. Microcomputer Systems, Inc.

#### MON08 MULTILINK

PORTC0, PORTC1 and PORTC3 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

Alternatively, the user may pull up PORTC0 and pull down PORTC1, and pull up/down PORTC3 for clock division. In which case the user does not need to connect these signals to the target MON08 Header.

#### 3.6 68HC908BD

| - Dout Ding Sotti | ngo Duning Pocot                |                          |                                                  |          |

|-------------------|---------------------------------|--------------------------|--------------------------------------------------|----------|

| FULLTINS SELL     | Port Pins Settings During Reset |                          | $\mathbf{NC}\ \Box\ \diamond\ \mathbf{GND}$      | Pin 2    |

| Target Type BD    |                                 | $NC \circ   \circ RST  $ |                                                  |          |

| Target Type 100   |                                 |                          | $NC \circ \sigma IRQ =$                          | HighV    |

|                   |                                 |                          | $NC \circ \circ NC$                              |          |

|                   |                                 |                          | $\mathbf{NC} \circ \ \circ \ \mathbf{PTA0}$      | = COM    |

|                   |                                 |                          | $\mathbf{NC} \circ \mathbf{\circ} \mathbf{PTC0}$ | = 1      |

|                   |                                 | C                        | SC o o PTC1                                      | = 0      |

|                   |                                 | Pinl5 V                  | ∕out ∘ ∘ PTC3                                    | =0 Pinl6 |

#### Figure 3-6: 68HC908BD Family MON08 Pinout

The target GND is connected to the Pin 2 of the target MON08 Header.

The target RESET line is directly connected to the Pin 4 of the target MON08 Header.

Alternatively, the user may pull up the RESET line to target VDD. In which case the user does not need to connect this signal to the target MON08 Header.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTA0 from the target processor is connected to the target MON08 Header Pin 10, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

PORTC0, PORTC1 and PORTC3 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

Alternatively, the user may pull up PORTC0 and pull down PORTC1, and pull up/down PORTC3 for clock division. In which case the user does not need to connect these signals to the target MON08 Header.

MON08 MULTILINK

# Freescale Semiconductor, Inc. DX, H Microcomputer

# P&E Systems, Inc.

#### 3.7 68HC908EY

| 🗆 Port Pins Setti               | ngs Nuring Reset |                      |                                                             |       |

|---------------------------------|------------------|----------------------|-------------------------------------------------------------|-------|

| Port Pins Settings During Reset |                  | Pin l                | $NC \square \circ GND$                                      | Pin 2 |

| Target Type                     |                  | $NC \circ \circ RST$ |                                                             |       |

|                                 |                  |                      | $\mathbf{NC} \circ \mathbf{IRQ} = \mathbf{Hi}_{\mathbf{i}}$ | ghV   |

|                                 |                  |                      | $\mathbf{NC} \circ \mathbf{O} \mathbf{PTA0} = \mathbf{C}$   | OM    |

|                                 |                  |                      | $\mathbf{NC} \diamond \mathbf{PTA1} = 0$                    |       |

|                                 |                  |                      | <b>NC</b> $\circ$ $\circ$ <b>PTB3 = 0</b>                   |       |

|                                 |                  |                      | $OSC \circ \circ PTB4 = 1$                                  |       |

|                                 |                  | Pin15                | <b>Vout</b> $\diamond$ $\diamond$ <b>PTB5</b> = <b>0</b>    | Pinló |

#### Figure 3-7: 68HC908EY Family MON08 Pinout

The target GND is connected to the Pin 2 of the target MON08 Header.

The target RESET line is directly connected to the Pin 4 of the target MON08 Header.

Alternatively, the user may pull up the RESET line to target VDD. In which case the user does not need to connect this signal to the target MON08 Header.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTA0 from the target processor is connected to the target MON08 Header Pin 10, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

PORTA1, PORTB3, PORTB4 and PORTB5 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

Alternatively, the user may pull down PORTA1 and PORTB3, and pull up PORTB4, and pull up/down PORTB5 for clock division. In which case the user does not need to connect these signals to the target MON08 Header.

#### 3.8 68HC908GP

| □ Port Pins Settings During Reset |                                |       |                                                           |         |  |  |  |

|-----------------------------------|--------------------------------|-------|-----------------------------------------------------------|---------|--|--|--|

|                                   | Tourne serie of a stand resort |       | $NC \square \circ GND$                                    | Pin 2   |  |  |  |

| Target Type                       | GP 🔽                           |       | $NC \circ \circ RST$                                      |         |  |  |  |

|                                   |                                |       | $\mathbf{NC} \circ \mathbf{RQ} = \mathbf{H}$              | ighV    |  |  |  |

|                                   |                                |       | $\mathbf{NC} \circ \mathbf{OPTA0} = \mathbf{O}$           | СОМ     |  |  |  |

|                                   |                                |       | $\mathbf{NC} \circ \mathbf{OPTA7} = 0$                    | 1       |  |  |  |

|                                   |                                |       | $\mathbf{NC} \circ \mathbf{O} \mathbf{PTC0} = \mathbf{I}$ | L       |  |  |  |

|                                   |                                |       | $OSC \circ \circ PTC1 = 0$                                | )       |  |  |  |

|                                   |                                | Pin15 | <b>Vout</b> $\circ$ $\circ$ <b>PTC3</b> = 0               | ) Pinl6 |  |  |  |

MON08 Multilink User Manual

# **Freescale Semiconductor, Inc.** Microcomputer Systems, Inc.

#### **MON08 MULTILINK**

The target GND is connected to the Pin 2 of the target MON08 Header.

The target RESET line is directly connected to the Pin 4 of the target MON08 Header.

Alternatively, the user may pull up the RESET line to target VDD. In which case the user does not need to connect this signal to the target MON08 Header.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTA0 from the target processor is connected to the target MON08 Header Pin 8, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

PORTA7, PORTC0, PORTC1 and PORTC3 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

Alternatively, the user may pull down PORTA7 and PORTC1, pull up PORTC0, and pull up/down PORTC3 for clock division. In which case the user does not need to connect these signals to the target MON08 Header.

#### 3.9 68HC908GR16

|                | D Pin 2                                                                                                             |

|----------------|---------------------------------------------------------------------------------------------------------------------|

| > • RSI        | [                                                                                                                   |

| > ○ IRQ        | ) = HighV                                                                                                           |

| > > PTA        | 0 = COM                                                                                                             |

| o o pta        | <b>1</b> = 0                                                                                                        |

| o o pte        | 0 = 1                                                                                                               |

| o o pte        | 1 = 0                                                                                                               |

| ○ <b>○ PTB</b> | 4=0 Pinl6                                                                                                           |

|                | <ul> <li>0 RST</li> <li>0 IRQ</li> <li>0 PTA</li> <li>0 PTA</li> <li>0 PTA</li> <li>0 PTE</li> <li>0 PTE</li> </ul> |

Figure 3-9: 68HC908GR16 MON08 Pinout

The target GND is connected to the Pin 2 of the target MON08 Header.

The target RESET line is directly connected to the Pin 4 of the target MON08 Header.

Alternatively, the user may pull up the RESET line to target VDD. In which case the user does not need to connect this signal to the target MON08 Header.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTA0 from the target processor is connected to the target MON08 Header Pin 8, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

**MON08 MULTILINK**

Freescale Semiconductor, Inc. Microcomputer L Systems, Inc.

PORTA1, PORTB0, PORTB1 and PORTB4 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

Alternatively, the user may pull up PORTB0, pull down PORTA1 and PORTB1, and pull up/down PORTB4 for clock division. In which case the user does not need to connect these signals to the target MON08 Header.

#### 3.10 68HC908GR4/8

| Port Pins Setti | ngs During Reset | Pin l | NC 🗆 🛛 GNI                             | ) Pin 2 |

|-----------------|------------------|-------|----------------------------------------|---------|

| Target Type     | CR4/8            |       | $\mathbf{NC} \circ \mathbf{\circ RST}$ |         |

| TalgetType      | (31(4/0          |       | $NC \circ \circ IRQ$                   | = HighV |

|                 |                  |       | $\mathbf{NC} \circ \mathbf{OPTA}$      | D = COM |

|                 |                  |       | $\mathbf{NC} \circ \mathbf{OPTA}$      | 1 = 0   |

|                 |                  |       | $\mathbf{NC} \circ \mathbf{OPTB}$      | 0 = 1   |

|                 |                  |       | $OSC \circ \circ PTB$                  | 1 = 0   |

|                 |                  | Pin15 | Vout $\circ$ $\circ$ NC                | Pinl6   |

#### Figure 3-10: 68HC908GR4/8 MON08 Pinout

The target GND is connected to the Pin 2 of the target MON08 Header.

The target RESET line is directly connected to the Pin 4 of the target MON08 Header.

Alternatively, the user may pull up the RESET line to target VDD. In which case the user does not need to connect this signal to the target MON08 Header.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTA0 from the target processor is connected to the target MON08 Header Pin 8, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

PORTA1, PORTB0, and PORTB1 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

Alternatively, the user may pull up PORTB0, pull down PORTA1 and PORTB1. In which case the user does not need to connect these signals to the target MON08 Header. The clock division is fixed Div 4.

MON08 Multilink User Manual

# **Freescale Semiconductor, Inc.** Microcomputer Systems, Inc.

**MON08 MULTILINK**

#### 3.11 68HC908GT

| Port Pins Settings During Reset |    |       |                                       | - |

|---------------------------------|----|-------|---------------------------------------|---|

|                                 |    | Pin l | NC $\square \diamond$ GND Pin 2       |   |

| Target Type                     | GT |       | $NC \circ \circ RST$                  |   |

|                                 |    |       | NC $\diamond$ $\diamond$ IRQ = HighV  |   |

|                                 |    |       | $NC \circ \circ PTA0 = COM$           |   |

|                                 |    |       | $\mathbf{NC} \circ \circ \mathbf{NC}$ |   |

|                                 |    |       | $NC \circ \circ PTC0 = 1$             |   |

|                                 |    |       | $OSC \circ \circ PTC1 = 0$            |   |

|                                 |    | Pin15 | Vout $\circ$ $\circ$ PTC3 = 0 Pinl6   | i |

#### Figure 3-11: 68HC908GT Family MON08 Pinout

The target GND is connected to the Pin 2 of the target MON08 Header.

The target RESET line is directly connected to the Pin 4 of the target MON08 Header.

Alternatively, the user may pull up the RESET line to target VDD. In which case the user does not need to connect this signal to the target MON08 Header.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTA0 from the target processor is connected to the target MON08 Header Pin 8, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

PORTC0, PORTC1 and PORTC3 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

Alternatively, the user may pull up PORTC0 and pull down PORTC1, and pull up/down PORTC3 for clock division. In which case the user does not need to connect these signals to the target MON08 Header.

#### 68HC908GZ 3.12

| _ | Dant Ding Catt | nga Duning Pagat  |       |                                                    |       |

|---|----------------|-------------------|-------|----------------------------------------------------|-------|

|   | FULLE SELL     | ings During Reset | Pin l | NC 🗆 $\diamond$ GND ]                              | Pin 2 |

|   | Target Type    | GZ                |       | $NC \circ \circ RST$                               |       |

|   | - Ber - Me     |                   |       | $NC \circ \circ IRQ = High$                        | v     |

|   |                |                   |       | $\mathbf{NC} \diamond \mathbf{PTA0} = \mathbf{CO}$ | M     |

|   |                |                   |       | $NC \circ OPTA1 = 0$                               |       |

|   |                |                   |       | $NC \circ OPTB0 = 1$                               |       |

|   |                |                   |       | $OSC \circ OTB1 = 0$                               |       |

|   |                |                   | Pin15 | <b>Vout</b> $\circ$ $\circ$ <b>PTB4 = 0</b>        | Pinl6 |

| Figure 3-12: 68HC908GZ Fa | amily MON08 Pinout |

|---------------------------|--------------------|

|---------------------------|--------------------|

**MON08 MULTILINK**

The target GND is connected to the Pin 2 of the target MON08 Header.

The target RESET line is directly connected to the Pin 4 of the target MON08 Header.

Alternatively, the user may pull up the RESET line to target VDD. In which case the user does not need to connect this signal to the target MON08 Header.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTA0 from the target processor is connected to the target MON08 Header Pin 8, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

PORTA1, PORTB0, PORTB1 and PORTB4 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

Alternatively, the user may pull up PORTB0, pull down PORTA1 and PORTB1, and pull up/down PORTB4 for clock division. In which case the user does not need to connect these signals to the target MON08 Header.

#### 3.13 68HC908JB1/8

| Port Pins Setti    | ings During Reset | Pin l                        | NC $\square \circ$ GND Pin 2                      |

|--------------------|-------------------|------------------------------|---------------------------------------------------|

| Target Type JB1/8  |                   | NC $\circ$ $\circ$ RST       |                                                   |

| Target Type Junito |                   | $NC \circ \circ IRQ = HighV$ |                                                   |

|                    |                   |                              | $\mathbf{NC} \circ \mathbf{ONC}$                  |

|                    |                   |                              | $NC \circ \circ PTA0 = COM$                       |

|                    |                   |                              | $NC \circ \circ PTA1 = 1$                         |

|                    |                   |                              | $OSC \circ OPTA2 = 0$                             |

|                    |                   | Pin15                        | <b>Vout</b> $\circ$ $\circ$ <b>PTA3 = 0 Pin16</b> |

Figure 3-13: 68HC908JB1/8 MON08 Pinout

The target GND is connected to the Pin 2 of the target MON08 Header.

The target RESET line is directly connected to the Pin 4 of the target MON08 Header.

Alternatively, the user may pull up the RESET line to target VDD. In which case the user does not need to connect this signal to the target MON08 Header.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTA0 from the target processor is connected to the target MON08 Header Pin 10, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

### **Freescale Semiconductor, Inc.** Microcomputer Systems, Inc.

#### MON08 MULTILINK

PORTA1, PORTA2 and PORTA3 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

Alternatively, the user may pull up PORTA1 and pull down PORTA2, and pull up/down PORTA3 for clock division. In which case the user does not need to connect these signals to the target MON08 Header.

#### 3.14 68HC908JB16

| Port Pins Settings During Reset |      |       |                                   |

|---------------------------------|------|-------|-----------------------------------|

|                                 |      | Pin l | NC $\square \diamond$ GND Pin 2   |

| Target Type                     | JB16 |       | $NC \circ \circ RST$              |

|                                 |      |       | $NC \circ \circ IRQ = HighV$      |

|                                 |      |       | $NC \diamond \phi PTE3 = 1$       |

|                                 |      |       | $NC \diamond \phi PTA0 = COM$     |

|                                 |      |       | $NC \circ \circ PTA1 = 1$         |

|                                 |      |       | $OSC \circ \circ PTA2 = 0$        |

|                                 |      | Pin15 | $Vout \circ \circ PTA3 = 0 Pin16$ |

#### Figure 3-14: 68HC908JB16 MON08 Pinout

The target GND is connected to the Pin 2 of the target MON08 Header.

The target RESET line is directly connected to the Pin 4 of the target MON08 Header.

Alternatively, the user may pull up the RESET line to target VDD. In which case the user does not need to connect this signal to the target MON08 Header.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTA0 from the target processor is connected to the target MON08 Header Pin 10, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

PORTA1, PORTA2, PORTA3 and PORTE3 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

Alternatively, the user may pull up PORTA1 and PORTE3, pull down PORTA2, and pull up/down PORTA3 for clock division. In which case the user does not need to connect these signals to the target MON08 Header.

L Systems, Inc.

Freescale Semiconductor, Inc. Microcomputer

#### MON08 MULTILINK

#### 3.15 68HC908JG

| Port Pins Settings During Reset |                  |        |                                     |

|---------------------------------|------------------|--------|-------------------------------------|

| FULLENS SELL                    | ngs During Reser | Pin l  | NC□ ◇ GND Pin 2                     |

| Target Type                     | IG               |        | $NC \circ \circ RST$                |

|                                 |                  |        | $NC \circ \circ IRQ = HighV$        |

|                                 |                  |        | $NC \circ \circ PTE3 = 1$           |

|                                 |                  |        | $NC \circ \circ PTA0 = COM$         |

|                                 |                  |        | $NC \circ \circ PTA1 = 1$           |

|                                 |                  |        | $OSC \circ \circ PTA2 = 0$          |

|                                 |                  | Pin15  | Vout $\circ$ $\circ$ PTA3 = 0 Pin16 |

|                                 |                  | 1 1112 |                                     |

#### Figure 3-15: 68HC908JG Family MON08 Pinout

The target GND is connected to the Pin 2 of the target MON08 Header.

The target RESET line is directly connected to the Pin 4 of the target MON08 Header.

Alternatively, the user may pull up the RESET line to target VDD. In which case the user does not need to connect this signal to the target MON08 Header.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTA0 from the target processor is connected to the target MON08 Header Pin 10, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

PORTA1, PORTA2, PORTA3 and PORTE3 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

Alternatively, the user may pull up PORTA1 and PORTE3, pull down PORTA2, and pull up/down PORTA3 for clock division. In which case the user does not need to connect these signals to the target MON08 Header.

#### 3.16 68HC908JK

| Port Pins Settings During Reset |                   |            |                                             |

|---------------------------------|-------------------|------------|---------------------------------------------|

| I UITI IIS SELL                 | ligs During Reser | Pin l NC   | $\Box \circ GND$ Pin 2                      |

| Target Type                     | JK                | NC         | • • <b>RST</b>                              |

| 6/1-                            |                   | NC         | $\circ \circ \mathbf{IRQ} = \mathbf{HighV}$ |

|                                 |                   | NC         | • • NC                                      |

|                                 |                   | NC         | $\circ \circ \mathbf{PTB0} = \mathbf{COM}$  |

|                                 |                   | NC         | ○ ○ <b>PTB1 = 1</b>                         |

|                                 |                   | OSC        | $\circ \circ \mathbf{PTB2} = 0$             |

|                                 |                   | Pin15 Vout | $\circ \circ PTB3 = 0 Pin16$                |

MON08 Multilink User Manual

# **Freescale Semiconductor, Inc.** Microcomputer Systems, Inc.

#### **MON08 MULTILINK**

The target GND is connected to the Pin 2 of the target MON08 Header.

The target RESET line is directly connected to the Pin 4 of the target MON08 Header.

Alternatively, the user may pull up the RESET line to target VDD. In which case the user does not need to connect this signal to the target MON08 Header.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTB0 from the target processor is connected to the target MON08 Header Pin 10, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

PORTB1, PORTB2 and PORTB3 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

Alternatively, the user may pull up PORTB1 and pull down PORTB2, and pull up/down PORTB3 for clock division. In which case the user does not need to connect these signals to the target MON08 Header.

#### 3.17 68HC908JL

| - Port Pins Setti | ngs During Reset                       |       |                                     |

|-------------------|----------------------------------------|-------|-------------------------------------|

|                   |                                        | Pin l | NC $\square \circ$ GND Pin 2        |

| Target Type       | Π                                      |       | NC $\circ$ $\circ$ RST              |

|                   | )::::::::::::::::::::::::::::::::::::: |       | $NC \circ \circ IRQ = HighV$        |

|                   |                                        |       | $NC \circ \circ NC$                 |

|                   |                                        |       | $NC \diamond \phi PTB0 = COM$       |

|                   |                                        |       | $NC \circ OPTB1 = 1$                |

|                   |                                        |       | $OSC \circ OTB2 = 0$                |

|                   |                                        | Pin15 | Vout $\circ$ $\circ$ PTB3 = 0 Pin16 |

Figure 3-17: 68HC908JL Family MON08 Pinout

The target GND is connected to the Pin 2 of the target MON08 Header.

The target RESET line is directly connected to the Pin 4 of the target MON08 Header.

Alternatively, the user may pull up the RESET line to target VDD. In which case the user does not need to connect this signal to the target MON08 Header.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTB0 from the target processor is connected to the target MON08 Header Pin 10, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

**MON08 MULTILINK**

Freescale Semiconductor, Inc. Microcomputer L Systems, Inc.

PORTB1, PORTB2 and PORTB3 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

Alternatively, the user may pull up PORTB1 and pull down PORTB2, and pull up/down PORTB3 for clock division. In which case the user does not need to connect these signals to the target MON08 Header.

#### 3.18 68HC908KX

| Port Pins Settings During Reset |                  |       |                                                           |       |

|---------------------------------|------------------|-------|-----------------------------------------------------------|-------|

|                                 | ngs Daring reser | Pin l | $NC \square \circ GND$                                    | Pin 2 |

| Target Type                     | KX 🔽             |       | $\mathbf{NC} \circ \mathbf{ONC}$                          |       |

|                                 |                  |       | $\mathbf{NC} \circ \mathbf{RQ} = \mathbf{H}$              | lighV |

|                                 |                  |       | $\mathbf{NC} \circ \mathbf{O} \mathbf{PTA0} = \mathbf{O}$ | СОМ   |

|                                 |                  |       | $\mathbf{NC} \diamond \mathbf{PTA1} = 0$                  | )     |

|                                 |                  |       | $\mathbf{NC} \circ \mathbf{O} \mathbf{PTB0} = \mathbf{I}$ | 1     |

|                                 |                  |       | $OSC \circ OTB1 = 0$                                      | )     |

|                                 |                  | Pin15 | Vout $\circ$ $\circ$ NC                                   | Pinló |

#### Figure 3-18: 68HC908KX Family MON08 Pinout

The target GND is connected to the Pin 2 of the target MON08 Header.

The user must pull up the RESET line to target VDD with an external resistor.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTA0 from the target processor is connected to the target MON08 Header Pin 8, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

PORTA1, PORTB0 and PORTB1 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

Alternatively, the user may pull up PORTB0 and pull down PORTA1 and PORTB1. In which case the user does not need to connect these signals to the target MON08 Header. The clock division is fixed Div 4.

# **Freescale Semiconductor, Inc.** Microcomputer Systems, Inc.

MON08 MULTILINK

#### 3.19 68HC908LD

| Port Pins Settings During Reset |      |       |                                                       |

|---------------------------------|------|-------|-------------------------------------------------------|

|                                 |      | Pin l | $\mathbf{NC} \Box \circ \mathbf{GND}  \mathbf{Pin 2}$ |

| Target Type                     | LD 🔽 |       | $\mathbf{NC} \circ \mathbf{\circ} \mathbf{RST}$       |

|                                 |      |       | NC $\diamond$ $\diamond$ IRQ = HighV                  |

|                                 |      |       | $NC \circ \circ PTA0 = COM$                           |

|                                 |      |       | $NC \circ \circ PTA7 = 0$                             |

|                                 |      |       | $NC \circ \circ PTC0 = 1$                             |

|                                 |      |       | $OSC \circ \circ PTC1 = 0$                            |

|                                 |      | Pin15 | Vout $\circ \circ$ PTC3 = 0 Pin16                     |

#### Figure 3-19: 68HC908LD Family MON08 Pinout

The target GND is connected to the Pin 2 of the target MON08 Header.

The target RESET line is directly connected to the Pin 4 of the target MON08 Header.

Alternatively, the user may pull up the RESET line to target VDD. In which case the user does not need to connect this signal to the target MON08 Header.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTA0 from the target processor is connected to the target MON08 Header Pin 8, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

PORTA7, PORTC0, PORTC1 and PORTC3 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

Alternatively, the user may pull up PORTC0, pull down PORTA7 and PORTC1, and pull up/down PORTC3 for clock division. In which case the user does not need to connect these signals to the target MON08 Header.

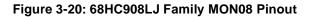

#### 3.20 68HC908LJ

| 🗆 Port Pins Setti | ings During Reset | D' 1  |                                                     | _ |

|-------------------|-------------------|-------|-----------------------------------------------------|---|

|                   |                   | Pin l | NC□ ◇ GND Pin 2                                     |   |

| Target Type       | LJ 🔽              |       | $NC \circ \circ RST$                                |   |

|                   |                   |       | $NC \circ \circ IRQ = HighV$<br>$NC \circ \circ NC$ |   |

|                   |                   |       | $NC \circ \circ PTA0 = COM$                         |   |

|                   |                   |       | $NC \circ \circ PTAI = 1$                           |   |

|                   |                   |       | $OSC \circ \circ PTA2 = 0$                          |   |

|                   |                   | Dialf | $Vout \circ \circ PTC1 = 0$ Pinl(                   | 5 |

|                   |                   | P1015 | vout ~ ~ FICI=0 PIMI                                | , |

> Freescale Semiconductor, Inc. Microcomputer

#### MON08 MULTILINK

**FXE** Systems, Inc.

The target GND is connected to the Pin 2 of the target MON08 Header.

The target RESET line is directly connected to the Pin 4 of the target MON08 Header.

Alternatively, the user may pull up the RESET line to target VDD. In which case the user does not need to connect this signal to the target MON08 Header.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTA0 from the target processor is connected to the target MON08 Header Pin 10, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

PORTA1, PORTA2 and PORTC1 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

Alternatively, the user may pull up PORTA1 and pull down PORTA2, and pull up/down PORTC1 for clock division. In which case the user does not need to connect these signals to the target MON08 Header.

#### 3.21 68HC908MR4/8

| Class V, VI, VII - CYCLONE and MON08 MULTILINK Settings                             | 1.2                                         |

|-------------------------------------------------------------------------------------|---------------------------------------------|

| Parallel Port: 1  Close Port  MON08 H                                               | Pinout: NC $\circ$ $\circ$ GND              |

|                                                                                     | PTB1 ◇ ◇ RST                                |

| Device Type: MR4/8 💌 Note : MR4/8 devices work only with the MON08 Multilink Interf | ace. NC $\diamond$ $\diamond$ IRQ = HighV   |

| Device Rever EV-lts Revided to R*E laterface                                        | $NC \circ \circ PTB0$                       |

| Device Power: 5 Volts, Provided by P&E Interface                                    | $\mathbf{NC} \diamond \diamond \mathbf{NC}$ |

| Device Clock: Target self-clocked, P&E Output Clock Disabled                        | $\mathbf{NC} \diamond \diamond \mathbf{NC}$ |

|                                                                                     | $OSC \circ \circ NC$                        |

| Clock Divider: 4                                                                    | Vout $\circ \circ \mathbf{NC}$              |

| ,                                                                                   | 15 16                                       |

#### Figure 3-21: 68HC908MR4/8 Family MON08 Pinout

The target GND is connected to the Pin 2 of the target MON08 Header.

The target RESET line is directly connected to the Pin 4 of the target MON08 Header.

Alternatively, the user may pull up the RESET line to target VDD. In which case the user does not need to connect this signal to the target MON08 Header.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTB0 from the target processor is connected to Pin 8 of the target MON08 Header. PORTB1 of the target processor is connected to Pin 3 of the target MON08 header. Together they serve as the data communication lines. The user

## **Freescale Semiconductor, Inc.** Microcomputer Systems, Inc.

#### MON08 MULTILINK

should pull down PORTB1 with a 4.7K Ohm resistor.

Please note that the MR4/8 is not currently supported by the MON08 CYCLONE.

### 3.22 68HC908MR16/32

| – Port Pins Setti | ings During Reset |       |                                   |

|-------------------|-------------------|-------|-----------------------------------|

|                   |                   | Pin l | NC $\square \diamond$ GND Pin 2   |

| Target Type       | MR16/32           |       | $NC \circ \circ RST$              |

| Tanget Type       |                   |       | $NC \circ \circ IRQ = HighV$      |

|                   |                   |       | $NC \circ \circ PTA0 = COM$       |

|                   |                   |       | $NC \circ \circ PTC2 = 0$         |

|                   |                   |       | $NC \circ \circ PTC3 = 1$         |

|                   |                   |       | $OSC \circ \circ PTC4 = 0$        |

|                   |                   | Pin15 | Vout $\circ \circ$ PTA7 = 0 Pin16 |

#### Figure 3-22: 68HC908MR16/32 Family MON08 Pinout

The target GND is connected to the Pin 2 of the target MON08 Header.

The target RESET line is directly connected to the Pin 4 of the target MON08 Header.

Alternatively, the user may pull up the RESET line to target VDD. In which case the user does not need to connect this signal to the target MON08 Header.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTA0 from the target processor is connected to the target MON08 Header Pin 8, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

PORTA7, PORTC2, PORTC3 and PORTC4 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

Alternatively, the user may pull up PORTC3, pull down PORTA7 and PORTC4, and pull up/down PORTC2 for clock division. In which case the user does not need to connect these signals to the target MON08 Header.

L Systems, Inc.

Freescale Semiconductor, Inc. Microcomputer

#### MON08 MULTILINK

#### 3.23 68HC908QT

| 🗆 Port Pins Setti | ngs During Reset |       |                                                  |       |

|-------------------|------------------|-------|--------------------------------------------------|-------|

|                   |                  | Pin l | $\mathbf{NC} \square \diamond \mathbf{GND}$      | Pin 2 |

| Target Type       | ОТ               |       | $\mathbf{NC} \circ \mathbf{ONC}$                 |       |

|                   |                  |       | $\mathbf{NC} \diamond \mathbf{IRQ} = \mathbf{H}$ | lighV |

|                   |                  |       | $NC \circ PTA0 =$                                | COM   |

|                   |                  |       | $\mathbf{NC} \circ \mathbf{OPTA4} = 0$           | 0     |

|                   |                  |       | $\mathbf{NC} \circ \mathbf{OPTA1} = 1$           | 1     |

|                   |                  |       | $OSC \circ \circ NC$                             |       |

|                   |                  | Pin15 | $\mathbf{Vout} \circ \mathbf{\circ NC}$          | Pinl6 |

#### Figure 3-23: 68HC908QT Family MON08 Pinout

The target GND is connected to the Pin 2 of the target MON08 Header.

The user must pull up the RESET line to target VDD with an external resistor.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTA0 from the target processor is connected to the target MON08 Header Pin 8, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

PORTA1 and PORTA4 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

Alternatively, the user may pull up PORTA1 and pull down PORTA4. In which case the user does not need to connect these signals to the target MON08 Header. The clock division is fixed Div 4.

Please note that the MON08 MULTILINK will calculate the proper trim value for the device being programmed and program this trim value to \$FFC0.

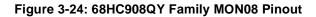

#### 3.24 68HC908QY

| - Port Dine Sett | ings During Reset |       |                                         |         |

|------------------|-------------------|-------|-----------------------------------------|---------|

| I OITI LIS SELL  | ngs Daring Keser  | Pin l | NC 🗆 🔆 GNI                              | ) Pin 2 |

| Target Type      | ov                |       | $NC \circ \circ NC$                     |         |

|                  | iger type Q1      |       | $NC \circ \circ IRQ$                    | = HighV |

|                  |                   |       | NC $\circ$ $\circ$ PTA                  | 0 = COM |

|                  |                   |       | $NC \circ \circ PTA$                    | 4 = 0   |

|                  |                   |       | $\mathbf{NC} \circ \mathbf{OPTA}$       | 1 = 1   |

|                  |                   |       | $OSC \circ \circ NC$                    |         |

|                  |                   | Pin15 | $\mathbf{Vout} \circ \mathbf{\circ NC}$ | Pinló   |

|                  |                   |       |                                         |         |

The target GND is connected to the Pin 2 of the target MON08 Header.

MON08 Multilink User Manual

# **Freescale Semiconductor, Inc.** Microcomputer Systems, Inc.

#### **MON08 MULTILINK**

The user must pull up the RESET line to target VDD with an external resistor.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTA0 from the target processor is connected to the target MON08 Header Pin 8, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

PORTA1 and PORTA4 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

Alternatively, the user may pull up PORTA1 and pull down PORTA4. In which case the user does not need to connect these signals to the target MON08 Header. The clock division is fixed Div 4.

Please note that in Stand-Alone programming mode the MON08 MULTILINK will calculate the proper trim value for the device being programmed and program this trim value to \$FFC0.

#### 3.25 68HC908RF

| - Port Pine Setti | ngo During Pocot                |         |                                                                                                                                                     |       |

|-------------------|---------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| FOILT DIS SELU    | Port Pins Settings During Reset |         | $NC \square \circ GND$                                                                                                                              | Pin 2 |

| Target Type       | RF                              | Pin l   | $\mathbf{NC} \diamond \diamond \mathbf{RST}$ $\mathbf{NC} \diamond \diamond \mathbf{IRQ} = \mathbf{Hi}$ $\mathbf{NC} \diamond \diamond \mathbf{NC}$ |       |

|                   |                                 |         | $NC \circ \circ PTA0 = C$<br>$NC \circ \circ PTB0 = 1$                                                                                              | OM    |

|                   |                                 | Pin15   | $OSC \circ \circ PTB2 = 0$<br>Vout $\circ \circ NC$                                                                                                 | Pinló |

|                   |                                 | T III 3 | tour • • ne                                                                                                                                         | 1 MIO |

Figure 3-25: 68HC908RF Family MON08 Pinout

The target GND is connected to the Pin 2 of the target MON08 Header.

The target RESET line is directly connected to the Pin 4 of the target MON08 Header.

Alternatively, the user may pull up the RESET line to target VDD. In which case the user does not need to connect this signal to the target MON08 Header.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTA0 from the target processor is connected to the target MON08 Header Pin 10, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

PORTB0 and PORTB2 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

MON08 MULTILINK

Alternatively, the user may pull up PORTB0 and pull down PORTB2. In which case the user does not need to connect these signals to the target MON08 Header. The clock division is fixed Div 4.

# 3.26 68HC908RK

| - Dowt Ding Cotti               | nga Duning Decet |                              |                                                |    |

|---------------------------------|------------------|------------------------------|------------------------------------------------|----|

| Port Pins Settings During Reset |                  | Pin l                        | NC □ ◇ GND Pin                                 | 2  |

| Target Type                     | RK               |                              | $NC \circ \circ RST$                           |    |

| Talger Type                     |                  | $NC \circ \circ IRQ = HighV$ |                                                |    |

|                                 |                  |                              | $\mathbf{NC} \circ \mathbf{\circ} \mathbf{NC}$ |    |

|                                 |                  |                              | $NC \circ \circ PTA0 = COM$                    |    |

|                                 |                  |                              | $NC \circ \circ PTB0 = 1$                      |    |

|                                 |                  |                              | $OSC \circ \circ PTB2 = 0$                     |    |

|                                 |                  | Pin15                        | Vout $\circ$ $\circ$ NC Pin                    | 16 |

|                                 |                  |                              |                                                |    |

Figure 3-26: 68HC908RK Family MON08 Pinout

The target GND is connected to the Pin 2 of the target MON08 Header.

The target RESET line is directly connected to the Pin 4 of the target MON08 Header.

Alternatively, the user may pull up the RESET line to target VDD. In which case the user does not need to connect this signal to the target MON08 Header.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTA0 from the target processor is connected to the target MON08 Header Pin 10, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

PORTB0 and PORTB2 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

Alternatively, the user may pull up PORTB0 and pull down PORTB2. In which case the user does not need to connect these signals to the target MON08 Header. The clock division is fixed Div 4.

# **Freescale Semiconductor, Inc.** Microcomputer Systems, Inc.

MON08 MULTILINK

#### 3.27 68HC908SR

| - Dowt Diver Cotti | ngs During Reset |       |                                                |

|--------------------|------------------|-------|------------------------------------------------|

| TOTTEDS SCL        | ngs During Keser | Pin l | NC $\square \diamond$ GND Pin 2                |

| Target Type        | SR 🔽             |       | NC $\circ$ $\circ$ RST                         |

| Targer Type        |                  |       | $NC \circ \circ IRQ = HighV$                   |

|                    |                  |       | $\mathbf{NC} \circ \mathbf{\circ} \mathbf{NC}$ |

|                    |                  |       | $NC \circ \circ PTA0 = COM$                    |

|                    |                  |       | $NC \circ \circ PTA2 = 0$                      |

|                    |                  |       | $OSC \circ \circ PTA1 = 1$                     |

|                    |                  | Pin15 | Vout $\circ \circ$ PTC1 = 0 Pin16              |

#### Figure 3-27: 68HC908SR Family MON08 Pinout

The target GND is connected to the Pin 2 of the target MON08 Header.

The target RESET line is directly connected to the Pin 4 of the target MON08 Header.

Alternatively, the user may pull up the RESET line to target VDD. In which case the user does not need to connect this signal to the target MON08 Header.

The target IRQ line is directly connected to the Pin 6 of the target MON08 Header.

PORTA0 from the target processor is connected to the target MON08 Header Pin 10, acting as the communications line. The MON08 MULTILINK pulls up this signal with a 10K Ohm resistor to the target VDD.

PORTA1, PORTA2 and PORTC1 are used for entering monitor mode. By default the user may directly bring these signals out to the target MON08 Header.

Alternatively, the user may pull up PORTA1 and pull down PORTA2, and pull up/down PORTC1 for clock division. In which case the user does not need to connect these signals to the target MON08 Header.

Freescale Semiconductor,

#### MON08 MULTILINK

# 4 PC-HOSTED DEBUG/PROGRAMMING SOFTWARE

Free or low-cost software options for interactively programming and debugging 68HC08 MCUs from the PC are available from P&E Microcomputer Systems (www.pemicro.com) and Metrowerks (www.metrowerks.com). P&E's ICS08 interface software packages are available at no charge from their web site. Metrowerks' CodeWarrior Development Studio for 68HC08, Special Edition, is available at no charge from the Motorola MCU Web site (www.motorola.com/semiconductors/mcu). You must register for the license key for this software.

Note: The user should make sure they have the most recent version of these software kits. The latest updates can be downloaded from the web pages listed in Section 4.1.1 Latest Updates - P&E Software and Section 4.2.1 Latest Updates - Metrowerks Software.

### 4.1 P&E Microcomputer Systems Software

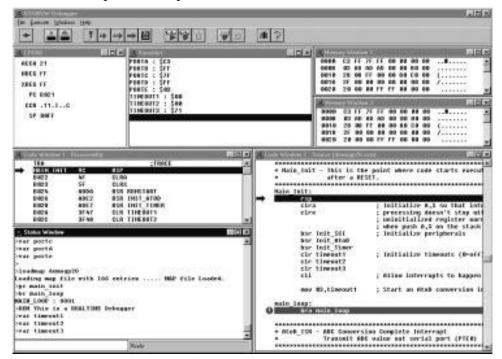

P&E's ICS08 software packages contain the WinIDE integrated development environment, which pulls together an assembler, in-circuit simulator, flash memory programmer, and in-circuit debugger. The programmer and debugger work with any MON08 hardware interface, including P&E's dedicated hardware interfaces. The MON08 MULTILINK is a Class V device, and the MON08 MULTILINK is Class VII.

| Attempting to contact target and pass security                                                                                                                                                                                                                                             |                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Target Hardware Type                                                                                                                                                                                                                                                                       |                             |

| Class V - P&E CYCLONE Interface connected to target via ribbon cable. Auto-Baud and Auto-Power.                                                                                                                                                                                            | Advanced                    |

| Class I - Motorola ICS Board with processor installed. Emulation connection ok. (Power controlled via DTR)<br>Class II - Motorola ICS Board without processor. Connected to target via 16-pin ribbon Cable.<br>Class III - Direct serial to target w/MON08 serial port circuitry built in. |                             |

| Class IV - Direct serial to target w/MON08 serial port circuitry and additional auto-reset circuit built in.                                                                                                                                                                               | GND                         |