Trion® T55/T85/T120 Field Programmable Gate Array (FPGA) Devices

Author: EIS Release Date: Jan 24, 2021

Efinix's FPGA soft processors provide the flexibility to support customized peripheral sets for any need

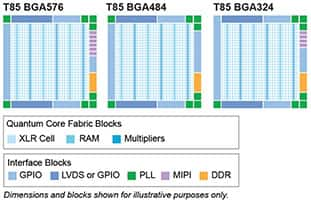

The Efinix Trion T55, T85, and T120 are I/O rich, low-power FPGAs with a disruptive core architecture. Depending on the package, the FPGAs include multiple TX/RX CSI-2 hard cores with each RX/TX capable of simultaneous 4 Gbps x 1.5 Gbps and DDR3 DRAM cores at 1066 Mbps. In addition to typical I/O expansion, system on a chip (SoC), bridging, and control, the Trion family is perfect for creating image processing functions while directly interfacing with the latest camera sensors available today.

The Efinix Trion T55, T85, and T120 are I/O rich, low-power FPGAs with a disruptive core architecture. Depending on the package, the FPGAs include multiple TX/RX CSI-2 hard cores with each RX/TX capable of simultaneous 4 Gbps x 1.5 Gbps and DDR3 DRAM cores at 1066 Mbps. In addition to typical I/O expansion, system on a chip (SoC), bridging, and control, the Trion family is perfect for creating image processing functions while directly interfacing with the latest camera sensors available today.

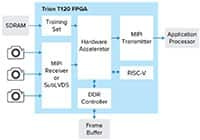

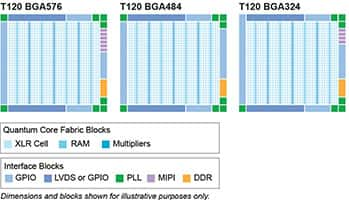

The Efinix Trion T55, T85, and T120 FPGAs feature the Quantum™ fabric wrapped with an I/O interface that incorporates two or three pre-engineered MIPI D-PHY/CSI-2 transmit and receive hard blocks, fully enabled for concurrent access. These family members are ideal for applications that need to interface with the latest MIPI CSI-2 v1.3 camera sensors and pack in enough programmable logic to handle image processing functions, merging/overlay, or image analysis in a single device. With an integrated hardened DDR3 DRAM controller, frame buffers are made simple.

Additionally, the device is large enough to handle SoC applications using a soft RISC-V core and the DDR3 controller for interface to system memory. An FPGA soft processor provides the flexibility to support customized peripheral sets for any needs. Users can implement additional co-processing blocks internally or develop specialized instruction sets to optimize price, power, and package.

The Trion family is supported by the Efinity® integrated development environment. The Efinity software provides a complete tool flow from RTL design to bitstream generation, including synthesis, place-and-route, and timing analysis. The Efinity IDE is included with a year of maintenance with the purchase of any Efinix evaluation kits. The T120 BGA324 and T120 BGA576 development kits are great test beds for debugging architecture and implementation vehicles for vision-specific or processing designs.

- 54K to 112K logic elements

- 150 to 320 18 x 18 multipliers

- 2,765 to 5,407 (kb) embedded block RAM

- 7 or 8 PLLs

- Up to 3 TX/RX - 4 lane at 1.5 Gps for D-PHY/CSI-2 v1.3

- DDR3, LPDDR3, LPDDR2 hard block (all packages)

- Footprint: BGA324 12 mm x 12 mm, BGA400 16 mm x 16 mm, BGA484 18 mm x 18 mm

- Machine vision

- Drones

- Robotics

- Surveillance

- Wide field cameras (180/360)

- IoT

- Thermal cameras

- Presence detection

- Control plane

- Consumer

- Edge intelligence

- MIPI CSI-2 bridging

- I/O expansion

- SoC edge

- Computing

- Industrial

- Communications

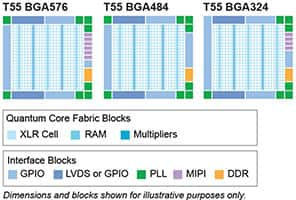

Efinix's Trion® T55 Dimensions and Blocks Diagrams